Académique Documents

Professionnel Documents

Culture Documents

Tema 4 - Sistemas Secuenciales I

Transféré par

wh0caresCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Tema 4 - Sistemas Secuenciales I

Transféré par

wh0caresDroits d'auteur :

Formats disponibles

E.T.S.

de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

FUNDAMENTOS DE ELECTRNICA

TEMA 4 SISTEMAS SECUENCIALES I: Biestables

Tema 4 - 1

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

En este tema se inicia el estudio de los fundamentos f de la lgica secuencial. Se estudiarn los circuitos biestables. Los biestables poseen SET dos estados y estables, RESET

denominados

(activacin)

(desactivacin), ( ), en los cuales se p pueden mantener indefinidamente, lo que les hace muy tiles como di dispositivos iti d almacenamiento. de l i t

Tema 4 - 2

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Utilizar puertas lgicas para construir biestables bsicos. Comprender la diferencia entre un biestable R-S, un biestable D y un biestable J-K

Comprender la diferencia entre los biestables asncronos (latch), los biestables sncronos (clocked latch) y los biestables sncronos por flanco (flip flip-flops flops)

Comprender el significado de: retardo de propagacin, ti tiempo d de establecimiento t bl i i t (hold time), ( t (setup ti ) time), ti tiempo mxima d de de mantenimiento frecuencia

funcionamiento ancho mnimo del impulso del reloj, funcionamiento, reloj y disipacin de potencia en las aplicaciones de los flip-flops.

Tema 4 - 3

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Contenidos

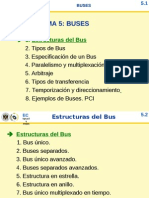

1. INTRODUCCIN A LOS SISTEMAS SECUENCIALES 1 1 Sistemas Secuenciales Asncronos 1.1. 1.2. Sistemas Secuenciales Sncronos 2. BIESTABLES 2.1. Tipos de Biestables (funcin instante de actuacin de las entradas en el estado del biestable) 2.1.1. Asncronos. 2.1.2. Sincronizados por nivel (latch) 2.1.3. Sincronizados por flanco (flip-flop) 2 2 Biestable R-S 2.2. 2.2.1. Biestable R-S Asncrono con entrada activa a nivel alto 2.2.2. Biestable R-S Asncrono con entrada activa a nivel bajo 2.2.3. Biestable R-S S de con entrada activa a nivel alto sincronizado por Nivel Uno 2.3. Biestable D 2.3.1. Biestable D sincronizado p por nivel uno 2.3.2. Biestable D sincronizado por flanco de bajada 2.4. Biestable J-K 2.4.1. Biestable J-K sincronizado por flanco de subida 2.4.2. Biestable J-K sincronizado por flanco con entradas asncronas 2.5. Caractersticas de operacin de los flips-flops 2.6. Aplicaciones de los flip-flops

Bibliografa de referencia

Mandado, Tema 4, , apt. p 4.1: Sistemas Secuenciales. Definicin

Para los biestables sincronizados: Mandado, Tema 4, apt.4.3.2.1. Biestables sincronizados. Introduccin.

Floyd, Tema 7, apt. 7.1: Latches: El Latch S-R (SETRESET), El Latch S-R con entrada de habilitacin.

Tambin se p puede ver en Mandado: 4.2.2.2. Biestables asncronos activados p por niveles. Biestable R-S asncrono, 4.3.2.2. Biestable R-S sincronizado por nivel.

Para Biestable D sincronizado por nivel: Floyd, Tema 7, apt. 7.1: Latches: El latch D con entrada de habilitacin. Para Biestable D sincronizado por flanco de bajada: Floyd, Tema 7, apt. 7.2: Flip-Flops disparados por flanco. Floyd, Tema 7, apt. 7.2: Flip-Flops disparados por flanco. El Flip-flop J-K disparado por flanco. Entradas asncronas de inicializacin y borrado. Floyd, Tema 7 7, apt. apt 7.3: 7 3: Caractersticas de operacin de los flips-flops Floyd, Tema 7, apt. 7.4: Aplicaciones de los flip-flops Tema 4 - 5

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

1. INTRODUCCIN A LOS SISTEMAS SECUENCIALES

COMBINACIONAL VS SECUENCIAL

SISTEMAS COMBINACIONALES

SISTEMAS SECUENCIALES

Tema 4 - 6

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

SISTEMA SECUENCIAL

El estado lgico de sus salidas en un instante determinado p no slo del estado de sus entradas en ese instante, depende sino tambin de los valores que hayan podido tomar dichas entradas anteriormente.

Todo sistema secuencial posee:

n variables de entrada (X1, X2, , Xn) 2n estados de entrada m variables de estado interno (Y1, Y2, , Ym) 2m estados internos p variables de salida (Z1, Z2, , Zp) 2p estados de salida

Tema 4 - 7

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

CLASIFICACIN (1)

(segn cmo generan las variables de salida)

Autmata de Moore: la salida es nicamente funcin del estado interno

Autmata de Mealy: la salida es funcin del estado interno y las entradas

Tema 4 - 8

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

CLASIFICACIN (2)

(segn el funcionamiento de los elementos de memoria)

1. SISTEMAS SECUENCIALES ASNCRONOS (SSA) Cambian el valor del estado y las salidas siempre que hay un cambio en los valores de entrada

1.1. Por realimentacin directa 1.2. Utilizando clulas de memoria asncronas

2. SISTEMAS SECUENCIALES SNCRONOS (SSS) Slo cambian el valor del estado y las salidas en instantes de tiempo fijos determinados por una seal l de d reloj l j

2.1. Totalmente sncronos 2.2. Sncronos asincronizados (parcialmente sincronizados)

Tema 4 - 9

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

1. SISTEMAS SECUENCIALES ASNCRONOS (SSA) 1.1. SSA de realimentacin directa Aprovechan los tiempos de propagacin (retardos) como clula de memoria Son muy inestables Dificiles de disear de forma sistemtica. 1.2. SSA con clulas de memoria asncronas El estado cambia en cuanto cambia las entradas Puede dar lugar a sistemas inestables (si las entradas cambian rpido y el estado no se estabiliza)

Tema 4 - 10

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2. SISTEMAS SECUENCIALES SNCRONOS (SSS) Las variables de entrada y las de estado interno slo actan sobre el sistema cuando sobre l acta un generador de impulsos o Reloj (Clock). Son ms estables Diseo Di sistemtico i t ti Presentan diferentes alternativas de realizacin en u c de del e elemento e e o de funcin memoria sncrono utilizado. Necesitan sincronizacin entre las variables de entrada y el reloj.

Tema 4 - 11

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2. BIESTABLES

Dispositivos de almacenamiento temporal de dos estados estables (0 y 1). Pueden ser:

a) ASNCRONOS (Latch) (L t h)

(cerrojo)

b) SINCRONIZADOS por nivel (clocked Latch) c) SINCRONIZADOS por cambio de nivel(Flip-flop)

Latch sincronizado por nivel: Las entradas de informacin actan sobre el biestable cuando la entrada de control adopta cierto nivel lgico Flip-flop: Las entradas de informacin actan sobre el biestable cuando en la entrada de control hay y un cambio de nivel ( (flancos de subida o flanco de bajada)

Tema 4 - 12

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

b) SINCRONIZADOS por nivel (Clocked latch, gated latch or latch) La entrada de control funciona como entrada de inhibicin

c) SNCRONIZADOS por flanco (Ed (Edge-triggered t i d fli flip-flop) fl )

Tema 4 - 13

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.1. BIESTABLE R-S

Circuito con dos entradas (R (R, S) y dos salidas (Q (Q, Q) que consta de dos puertas NOR conectadas de forma cruzada

Entrada activa a nivel ALTO

Tema 4 - 15

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Entrada activa a nivel ALTO

Tabla de transiciones

Tema 4 - 16

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Entrada activa a nivel ALTO

Tabla de transiciones

T bl de Tabla d excitacin it i

Tema 4 - 17

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

3

Entrada activa a nivel ALTO

Diagrama de estados

Tema 4 - 18

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.1.1. Biestable R-S Asncrono (entrada activa a nivel alto)

S

Latch RR-S

S (Set) R

Q Q

>1

S 0

R 0 1 0 1

Qt+1 Qt 0 1 0

Qt+1 Qt 1 0 0

>1

R (Reset)

Q

No valida:

0 1 1

Entrada activa a nivel ALTO

Tabla de transiciones

Problema si se produce un cambio simultneo de las entradas de nivel 11 a 00 estado impredecible (funcin del retardo de propagacin de las puertas). La puerta ms lenta permanecer a nivel 0. Cuando se produce esta situacin, no se puede predecir el siguiente estado. Tema 4 - 19 Sistemas secuenciales I: Biestables

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

2.1.2. Biestable R-S Asncrono (entrada activa a nivel bajo)

S

Latch RR-S

S

&

Q Q

R Q

S 1 0 R 1 1 0 0

R

Qt+1 Qt 1 0 1

Qt+1 Qt 0 1 1

&

1

No valida: 0

R

Entrada activa a nivel BAJO

Tabla de transiciones

&

&

Tema 4 - 20

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 1: Si se aplican las formas de onda S y R de la figura a las entradas del biestable R-S con entrada activa a nivel bajo, determinar la forma de onda que se observar en la salida Q. Suponer que Q se encuentra inicialmente a nivel BAJO.

Tema 4 - 21

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Cadruple biestable R-S

Tema 4 - 23

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.1.3. Biestable R-S Sincronizado por Nivel Uno

S

&

>1

Smbolo lgico normalizado

S

CLK

1S

Q Q

CLK

>1 &

R

R

Q

C1 1R

S

Smbolo lgico no normalizado

R 0 1 0 1

Qt+1 Qt 0 1 0

Qt+1 Qt 1 0 0

0 0 1

No valida:

(CLK=1)

Tema 4 - 24

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 2: Determinar la forma de onda de salida Q, Q si se aplican las seales de entrada mostradas en la figura a un biestable R-S sincronizado por nivel uno, que se encuentra inicialmente en estado de RESET.

S

1S

Q Q

S R

CLK

C1 1R

CLK

Tema 4 - 25

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.2. BIESTABLE D

D

>1

se activen a la vez

>1

D

Tabla de excitacin Tabla de transiciones

D 0

CLK

Qt+1 0 1

Tema 4 - 27

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2 2 1 Biestable D sincronizado por nivel uno 2.2.1.

D

&

Smbolo lgico g normalizado

>1

D

1D

Q Q

CLK

CLK

C1

>1 &

D

CLK 0 1 1

D X 0 1

Qt+1 Qt 0 1

Smbolo lgico no normalizado

Tabla de transiciones

Tema 4 - 28

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 3: Determinar la forma de onda de la salida Q, Q si se aplican las entradas que se muestran en la figura a un biestable D sincronizado por nivel que, inicialmente est en estado RESET.

D

CLK

1D C1

Q Q

CLK

Tema 4 - 29

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Cadruple biestable D sincronizado con nivel 1

Tema 4 - 31

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Problemas de la Activacin por Nivel

Tema 4 - 32

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Problemas de la Activacin por Nivel

Tema 4 - 33

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Smbolos lgicos de los biestables activados por flanco

Flanco o positiv vo

1 1 1

1 1

1 1 1

Flanc co negat tivo

1 1 1

1 1

1 1 1

Tema 4 - 34

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 4: Determinar la forma de onda de la salida Q y Q del biestable de la figura para las entradas S, R y CLK indicadas. Suponer que el biestable disparado por flanco positivo se encuentra, inicialmente, en estado RESET.

1 1 1

Tema 4 - 35

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.2.2. Biestable D sincronizado por flanco positivo (de subida)

D

D &

1D

Q Q

>1

CLK

C1

CLK

>1 &

D

CLK Resto

D X 0 1

Qt+1 Qt 0 1

CLK: Salida de un circuito de Deteccin de flanco:

(ns)

1 & 1

Qt+1 = D

Deteccin flanco negativo (de bajada): se invierte p primero el impulso p de reloj, j, de forma que se origina un pico muy estrecho en el flanco de bajada Tema 4 - 37

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 5: Dadas las formas de onda de la figura para la entrada D y el reloj, reloj determinar la onda de salida Q si el biestable D parte del estado RESET.

1 1

Tema 4 - 38

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

J-K en honor a Jack Kilby (Inventor CI)

2.3. BIESTABLE J-K

&

Set

CLK

Biestable RS

&

&

K

&

Reset

Qt+1 = JQt + KQt

Tema 4 - 40 E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.3.1. Biestable J J-K K sincronizado por flanco de subida

J

1J J

Q Q

&

CLK

&

K

J

C1 1J

CLK

K 0 1 0 1

Qt+1 Qt 0 1 Qt

&

K

0

Q

&

0 1 1

(CLK )

CLK Deteccin CLK: D t i de d flanco fl de d subida bid de d CLK

Qt+1 = JQt + KQt

Tema 4 - 41

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 6: Las formas de onda de entrada de la figura se aplican a las entradas J, J K y de reloj, tal y como se muestra. Determinar la salida Q suponiendo que el biestable se encuentra inicialmente en estado RESET.

1 1 1

Tema 4 - 42

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 7: Las formas de onda de entrada de la figura se aplican al biestable que se muestra. Determinar la salida Q suponiendo que el biestable se encuentra inicialmente en estado RESET.

Tema 4 - 44

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Entradas asncronas de inicializacin (preset) y borrado (clear):

Tema 4 - 46

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.3.2. Biestable J-K sincronizado por flanco con entradas asncronas de inicializacin y borrado

S 1J C1 1K R S 1J C1 1K R

Tema 4 - 47

En caso de conflicto, predomina el efecto de las asncronas

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 8: En el biestable J-K J K activado por flanco positivo de la figura, figura con entradas de Inicializacin (PRESET) y borrado (CLEAR), determinar la salida Q para las entradas mostradas en el diagrama de tiempos de la figura si Q est inicialmente a nivel BAJO.

1 1

Tema 4 - 48

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Doble biestable (flip-flop) D disparado por flanco positivo

1 1

1 1

Tema 4 - 50

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Doble biestable (flip-flop) J-K disparado por flanco negativo

1 1 1

1 1 1

Tema 4 - 51

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 9: Las formas de onda para 1J, 1J 1K, 1K 1CLK y 1PRE y 1CLK de la figura se aplican a uno de los flip-flops disparados por flanco negativo del circuito 75HC112. Determinar la onda de salida 1Q.

Tema 4 - 52

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.5. CARACTERSTICAS DE OPERACIN DE LOS FLIPS-FLOPS

El funcionamiento, requisitos de operacin y limitaciones de los flip-flops se especifican mediante varias caractersticas de funcionamiento o parmetros que se encuentran en las HOJAS DE CARACTERSTICAS DEL DISPOSITIVO

(generalmente, las especificaciones son aplicables a todos los flip-flops CMOS y TTL)

1 1. 2. 3 3. 4. 5. 6.

Retardos de propagacin (tP) Tiempo de establecimiento (tS) Ti Tiempo de d mantenimiento t i i t (th) Frecuencia mxima de reloj Anchura de los impulsos Disipacin de potencia

Tema 4 - 54

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.5.1. Retardo de propagacin

Intervalo de tiempo requerido para que se produzca un cambio en la salida una vez que se ha aplicado una seal en la entrada.

a) Retardos de propagacin entre el reloj y la salida 1. Retardo de propagacin tPLH: se mide desde el flanco de disparo del reloj hasta la transicin de nivel BAJO a nivel ALTO de la salida

2. Retardo de propagacin tPHL: se mide desde el flanco de disparo del reloj hasta la transicin de nivel ALTO a nivel BAJO de la salida

Tema 4 - 55

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

b) Retardos de propagacin entre la entrada de inicializacin (PRESET) y la salida y la entrada de borrado (CLEAR) y la salida

Ejemplo para entrada de inicializacin (PRESET) activa a nivel BAJO:

3. Retardo de propagacin tPLH: se mide desde la entrada de inicializacin (PRESET) hasta la transicin de nivel BAJO a nivel ALTO de la salida.

Ejemplo para entrada de borrado (CLEAR) activa a nivel BAJO:

4 Retardo 4. R t d de d propagacin i tPHL: se mide id desde d d la entrada de borrado hasta la transicin de nivel ALTO a nivel BAJO de la salida. salida

Tema 4 - 56

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.5.2. Tiempo de establecimiento (setup time, tS)

Intervalo mnimo que los niveles lgicos deben mantenerse constantes en las entradas (J y K, S y R, D) antes de que llegue el flanco de disparo del impulso de reloj, de modo que dichos niveles se sincronicen

correctamente en el flip-flop.

Ejemplo para flip-flop D:

El nivel lgico debe estar presente en la entrada D durante un perodo de tiempo p mayor y o igual g que tS antes de q q que se p produzca el flanco de disparo del impulso de reloj para tener una entrada de datos correcta. Tema 4 - 57

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.5.3. Tiempo de mantenimiento (hold time, th)

Intervalo mnimo que los niveles lgicos deben mantenerse constantes en las entradas (J y K, S y R, D) despus de que haya pasado el flanco de disparo del impulso de reloj, de modo que dichos niveles se sincronicen correctamente en el flip-flop.

Ejemplo para flip-flop D:

El nivel lgico debe permanecer en la entrada D durante un perodo de tiempo p mayor y o igual g que th despus q p de q que se p produzca el flanco de disparo del impulso de reloj para tener una entrada de datos correcta. Tema 4 - 58

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.5.4. Frecuencia mxima de reloj (fmax)

Mayor velocidad a la que se puede disparar el flip-flop de manera fiable.

Para frecuencias de reloj por encima de la mxima, el flip-flop puede ser incapaz de responder los suficientemente rpido y su funcionamiento se vera deteriorado.

2.5.5. Anchura de los impulsos (tW)

Anchura mnima de los impulsos (tW) para un funcionamiento adecuado de las entradas de reloj, inicializacin y borrado.

Tpicamente, el reloj se especifica mediante sus intervalos de tiempo mnimo para los niveles ALTO y BAJO

Tema 4 - 59

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.5.6. Disipacin de potencia

La disipacin de potencia de cualquier circuito digital se define como la potencia total consumida por el dispositivo.

Ejemplo: si el flip f flop f f funciona con una fuente f de continua de +5V y circula por l una corriente de 5mA, la disipacin de potencia es: P VCC x ICC = 5V x 5 P= 5mA A = 25 25mW W

Tema 4 - 60

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Comparacin de flips-flops especficos

Comparacin para cuatro flip-flops TTL y CMOS del mismo tipo, en funcin de los parmetros de funcionamiento vistos

Tema 4 - 61

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.6. APLICACIONES DE LOS FLIP-FLOPS 2.6.1. Almacenamiento de datos paralelo

Utilizacin de flip flip-flops flops en un registro bsico para almacenamiento paralelo de datos

Tema 4 - 62

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

2.6.2. Divisin de frecuencia

a) Flip-flop J-K como dispositivo divisor por 2.

La frecuencia de Q es la mitad de la de la seal CLK

b)

Utilizacin de dos flip-flops J-K para dividir la frecuencia de reloj por 4.

La frecuencia de QA es la mitad de la seal CLK, CLK y la frecuencia QB es un cuarto de la frecuencia de CLK.

Tema 4 - 63

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 10: Desarrollar la forma de onda fout para el circuito de la figura cuando se aplica una seal cuadrada de 8KHz en la entrada de reloj del flip-flop A.

Cuntos C t fli fl flips-flops se requieren i para dividir di idi una frecuencia f i entre t treinta y dos?

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica Tema 4 - 64

Sistemas secuenciales I: Biestables

2.6.3. Contadores

Fli fl Flip-flops J K utilizados J-K tili d para generar una secuencia i de d cuenta t binaria. bi i Se muestran dos repeticiones (00, 01, 10, 11)

Tema 4 - 66

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 11 (para casa): Determinar las formas de onda de salida en funcin del reloj para QA, QB y QC en el circuito de la figura y mostrar la secuencia binaria representada por estas seales.

Cuntos C t fli fl flips-flops se requieren i para generar una secuencia i que represente los nmeros decimales de 0 a 15?

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica Tema 4 - 67

Sistemas secuenciales I: Biestables

2.6.4. Elementos de Memoria en Circuitos Secuenciales

Tema 4 - 69

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Un circuito secuencial est formado por un parte de lgica combinacional y una seccin de memoria (flip-flops). (flip flops) En un CIRCUITO SECUENCIAL SNCRONO, hay una entrada de reloj en la seccin de memoria.

Tema 4 - 70

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Para un correcto funcionamiento del circuito se requiere: La informacin almacenada en los elementos de memoria Las entradas del circuito conectadas a la lgica combinacional

Tema 4 - 71

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

En cualquier instante de t, la memoria se encuentra en un estado denominado estado actual, y avanza al estado siguiente con un impulso de reloj.

El estado actual de la memoria se representa por las Variables de Estado (Q0, Q1, , Qx).

Tema 4 - 72

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Las Variables de Estado ( (Q0, Q1, , , Qx) )., , j junto con las Entradas (I0, I1,, Im) determinan las Salidas sistema (O0, O1, , On)

Tema 4 - 73

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

No todos los circuitos secuenciales tienen variables de entrada y salida. salida

Sin embargo, g , todos tienen variables de excitacin y variables de estado. estado.

Tema 4 - 74

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

DISEO DE SISTEMAS SECUENCIALES SNCRONOS Pasos a realizar 1. Escribir las especificaciones en lenguaje general 2 Realizar 2. R li l especificacin la ifi i formal f l Diagrama Di d estados de t d

estados) (grafo de

3 Elegir 3. El i los l elementos l d memoria de i a utilizar ili 4. Codificar los estados 5. Realizar las tablas de excitacin y salida 6 Simplificar por Karnaugh 6. 7. Disear el circuito

Tema 4 - 75

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 12 (Ejemplo de Diseo de un Sistema Secuenciales Sncrono)

1. Escribir las especificaciones en lenguaje general 2. Realizar la especificacin formal Diagrama de estados

estados) (grafo de

3. Elegir los elementos de memoria a utilizar 4. Codificar los estados 5. Realizar las tablas de excitacin y salida 6. Simplificar por Karnaugh 7. Disear el circuito

Obtener el diagrama o grafo de estados, estados y disear el circuito utilizado biestables D y puertas lgicas.

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica Tema 4 - 76

Sistemas secuenciales I: Biestables

Ejercicio 13

Sea un sistema secuencial sncrono que posee una variable de entrada X1, y cuyo estado interno evoluciona entre cuatro estados E0, E1, E2 y E3, de acuerdo con el diagrama de estados de la figura. Obtener el esquema del circuito utilizando como elementos de memoria biestables J-K activados por flancos de subida.

Tema 4 - 78

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 14 (para casa):

Repetir el ejercicio anterior utilizando como elementos de memoria biestables D activados por flancos de subida en lugar de biestables J-K.

Tema 4 - 79

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

EJERCICIOS PROPUESTOS PARA CASA: Ejercicio 15. Si se aplican las seales de la figura a un , dibujar j la biestable RS con entradas activas a nivel alto, forma de onda de salida Q resultante en funcin de las entradas Suponer que inicialmente Q est a nivel bajo. entradas. bajo

Tema 4 - 80

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 16. En un biestable D sincronizado por nivel se observan las formas de onda de la figura. Dibujar el diagrama de tiempos, mostrando la forma de onda de la salida que esperaramos observar en Q si el biestable inicialmente est a nivel bajo. D

1D

Q Q

CLK

C1

Tema 4 - 81

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 17. Si se aplican las seales de la figura a los dos biestables RS activado por flancos, dibujar la forma de onda de salida Q resultante en p que inicialmente Q est a nivel bajo. q j funcin de las entradas. Suponer

1 1 1 1 1 1

Tema 4 - 82

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 18. En la siguiente figura se muestra la salida de un biestable RS activado por flancos en funcin de la seal de reloj. Determinar las formas de onda que se necesitan en las entradas S y R para producir esta salida.

1 1 1

Tema 4 - 83

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 19. Si se aplican las seales de la figura a un biestable D activado por flancos positivos, dibujar la forma de onda de salida Q resultante en funcin de las entradas. Suponer que inicialmente Q est a nivel bajo.

Tema 4 - 84

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 20. Si se aplican las seales de la figura a un biestable JK activado ti d por flancos fl positivos, iti dib j dibujar l forma la f d onda de d de d salida lid Q resultante en funcin de las entradas. Suponer que inicialmente Q est a nivel bajo.

Tema 4 - 85

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 21. Si se aplican las seales de la figura al biestable JK representado dibujar la forma de onda de salida Q resultante en funcin de representado, las entradas. Suponer que inicialmente Q est a nivel bajo.

1 1

Tema 4 - 86

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 22. Completar el diagrama de tiempos de la figura para el circuito representado, t d dibujando dib j d la l salida lid Q que inicialmente i i i l t Q est t a nivel i l bajo. b j Suponer que PRE y CLR permanecen a nivel ALTO.

S

1 1 R

Tema 4 - 87

E.T.S. de Ingenieros de Telecomunicacin de Vigo Departamento de Tecnologa Electrnica

Sistemas secuenciales I: Biestables

Ejercicio 23. Resolver el problema anterior con las mismas entradas J y K pero con las entradas PRE y CLR que se muestran en la figura en funcin j del reloj..

Tema 4 - 88

Vous aimerez peut-être aussi

- UF1966 - Operaciones auxiliares en el mantenimiento de equipos electrónicosD'EverandUF1966 - Operaciones auxiliares en el mantenimiento de equipos electrónicosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Tema 4 Circuitos Secuenciales 2020-2021pdfDocument83 pagesTema 4 Circuitos Secuenciales 2020-2021pdferos.llorensPas encore d'évaluation

- Logica Secuencial 2020Document37 pagesLogica Secuencial 2020Diego V-aPas encore d'évaluation

- Informe Previo #1aDocument13 pagesInforme Previo #1aDiego Gutierrez AyalaPas encore d'évaluation

- Latch, Flip Flops, Maquinas de Estados FinitosDocument28 pagesLatch, Flip Flops, Maquinas de Estados FinitosItaloCardenasPas encore d'évaluation

- FLIP FLOP Marco Teorico + 2pregDocument17 pagesFLIP FLOP Marco Teorico + 2pregrobertitoPas encore d'évaluation

- Sistemas Lógicos SecuencialesDocument34 pagesSistemas Lógicos SecuencialesAlejandro MontoyaPas encore d'évaluation

- Informe Final IIDocument25 pagesInforme Final IIJunior Solis MiñanoPas encore d'évaluation

- Sistemas SecuencialesDocument18 pagesSistemas SecuencialesAlejandro ProañoPas encore d'évaluation

- Cto. SecuencialDocument32 pagesCto. SecuencialAlonso HernándezPas encore d'évaluation

- Bie StablesDocument18 pagesBie Stableslady67lauraPas encore d'évaluation

- Fibonacci 2 PDF FreeDocument4 pagesFibonacci 2 PDF FreeJuanPablodelaRegueraPas encore d'évaluation

- Previo N°1 Digitales IiDocument15 pagesPrevio N°1 Digitales IiMervin TCPas encore d'évaluation

- Informe Final 1Document13 pagesInforme Final 1samuel guardiaPas encore d'évaluation

- Puertas LogicasDocument18 pagesPuertas LogicasBadass OverPowerPas encore d'évaluation

- Informe Previo N°1Document15 pagesInforme Previo N°1hhenrirPas encore d'évaluation

- Tema3 PDFDocument47 pagesTema3 PDFCésar DiazPas encore d'évaluation

- Labo 1 SistdigDocument11 pagesLabo 1 SistdigIrbin DelgadoPas encore d'évaluation

- Informe Logicas SecuencialDocument17 pagesInforme Logicas SecuencialYhared CaprilesPas encore d'évaluation

- Lach y Flip FlopsDocument8 pagesLach y Flip FlopsMiguel Roberto Vazquez ParraPas encore d'évaluation

- Informe Final 1 UtrillaDocument10 pagesInforme Final 1 UtrillaCaptain Underoos0% (1)

- cd2 Final1Document8 pagescd2 Final1Eleazar CastilloPas encore d'évaluation

- Basculas Sincronas y AsincronasDocument11 pagesBasculas Sincronas y Asincronastitominas7511Pas encore d'évaluation

- Flip FlopDocument8 pagesFlip FlopPaola GarciaPas encore d'évaluation

- PrevioDocument16 pagesPrevioFranck JonhsonPas encore d'évaluation

- UT 03 Analisis de Circuitos Secuenciales by FranDocument11 pagesUT 03 Analisis de Circuitos Secuenciales by FranFrancisco BaenaPas encore d'évaluation

- Circuitos Combinacionales y SecuancialesDocument39 pagesCircuitos Combinacionales y SecuancialesJosé Miguel AvalosPas encore d'évaluation

- Trabajo Investigación Tema 4 (N°c.18500311)Document32 pagesTrabajo Investigación Tema 4 (N°c.18500311)Jason ClementePas encore d'évaluation

- Compuertas LogicasDocument7 pagesCompuertas LogicasJordanPozoPas encore d'évaluation

- Flip Flop JKDocument6 pagesFlip Flop JKMigue PicazoPas encore d'évaluation

- Manual Del Laboratorio de Electrónica Digital IDocument211 pagesManual Del Laboratorio de Electrónica Digital IMadeline ReynosoPas encore d'évaluation

- Estudio de Flip FlopDocument30 pagesEstudio de Flip Flopargie27Pas encore d'évaluation

- Problemas Resueltos de Sistemas DigitalesDocument13 pagesProblemas Resueltos de Sistemas DigitalesManuel TapiaPas encore d'évaluation

- Flip FlopsDocument7 pagesFlip FlopsJuan LainaPas encore d'évaluation

- Caracteristicas BiestablesDocument47 pagesCaracteristicas BiestablesJuan Camilo NaranjoPas encore d'évaluation

- TE 2 CompletoDocument95 pagesTE 2 CompletoMarco Abel Quispe SoccaPas encore d'évaluation

- ¿Qué Es Un Flip Flop?Document6 pages¿Qué Es Un Flip Flop?OLIVER ALVARADO MART�NEZPas encore d'évaluation

- Practica Del SemaforoDocument14 pagesPractica Del SemaforoCristian EscobarPas encore d'évaluation

- Bies TableDocument8 pagesBies TableZarate BismkPas encore d'évaluation

- S04. PLC LadderDocument63 pagesS04. PLC Ladderesmeralda100% (1)

- Circuitos SecuencialesDocument4 pagesCircuitos SecuencialesL LawlietPas encore d'évaluation

- Latches 100209091220 Phpapp02Document9 pagesLatches 100209091220 Phpapp02Cläü SäläsPas encore d'évaluation

- Logica SecuencialDocument9 pagesLogica SecuencialBruno Hernández MartínezPas encore d'évaluation

- Sistema Lógico Secuencial Asincrónico y SincrónicoDocument38 pagesSistema Lógico Secuencial Asincrónico y SincrónicoNemessis Pacheco100% (1)

- Preparatorio 12 LoayzaDocument13 pagesPreparatorio 12 LoayzaLuis LoayzaPas encore d'évaluation

- 3 MODULO Registro de DesplazasamientoDocument62 pages3 MODULO Registro de DesplazasamientoFrancisco ChangoPas encore d'évaluation

- Flip-Flops Circuitos Sincronos y AsincronosDocument2 pagesFlip-Flops Circuitos Sincronos y AsincronosSebastian Rodriguez PovedaPas encore d'évaluation

- Previo 7 MedicionDocument13 pagesPrevio 7 MedicionLeslie Vp67% (3)

- EtcDocument34 pagesEtcSonia JiangPas encore d'évaluation

- Evaluacion #2, Electricidad y ElectronicaDocument16 pagesEvaluacion #2, Electricidad y ElectronicaÁlvaro Adrián Bahamonde BahamondePas encore d'évaluation

- Iesnumero 1 RibeiraDocument4 pagesIesnumero 1 RibeiraFernando Sobrino-Manzanares MasPas encore d'évaluation

- Sistemas Eléctricos y Electrónicos Tarea 2Document11 pagesSistemas Eléctricos y Electrónicos Tarea 2Cristian LopezPas encore d'évaluation

- INFORME DE PRAC. ELEC digitalUNIDAD4Document28 pagesINFORME DE PRAC. ELEC digitalUNIDAD4myhuxPas encore d'évaluation

- Practica 3 Contador de DecadasDocument20 pagesPractica 3 Contador de DecadasJ Rodrigo Castro HPas encore d'évaluation

- Registros FinalDocument8 pagesRegistros Finalceleste claroPas encore d'évaluation

- PEyAD 15161337 CIRCUITOS SECUENCIALES U3Document14 pagesPEyAD 15161337 CIRCUITOS SECUENCIALES U3Nancy TendoPas encore d'évaluation

- ContadorDocument13 pagesContadorEdwin GavilanezPas encore d'évaluation

- Flip FlopDocument23 pagesFlip FlopJoseph JesusPas encore d'évaluation

- Informe Proyecto - Reloj BinarioDocument10 pagesInforme Proyecto - Reloj BinarioAlex TipantuñaPas encore d'évaluation

- Tema 8 ContadoresDocument17 pagesTema 8 ContadoresMiguel AnaluisaPas encore d'évaluation

- MOBOTIX Compact Guide Activity Sensor SPANISH 130606Document17 pagesMOBOTIX Compact Guide Activity Sensor SPANISH 130606wh0caresPas encore d'évaluation

- ESESP CG3630 Focus Og 201409Document448 pagesESESP CG3630 Focus Og 201409wh0caresPas encore d'évaluation

- Es-De Lehrbuch2009Document590 pagesEs-De Lehrbuch2009530YERPas encore d'évaluation

- Tema 3 - Sistemas Combinacionales IIDocument60 pagesTema 3 - Sistemas Combinacionales IIwh0caresPas encore d'évaluation

- Tema 2 - Sistemas Combinacionales IDocument38 pagesTema 2 - Sistemas Combinacionales Iwh0caresPas encore d'évaluation

- Como ExamenesDocument22 pagesComo Exameneswh0caresPas encore d'évaluation

- 08 01 NuevolagunaberlinaDocument24 pages08 01 Nuevolagunaberlinawh0caresPas encore d'évaluation

- Teoria de EEE SimplificadaDocument7 pagesTeoria de EEE Simplificadawh0caresPas encore d'évaluation

- Practica03 - SREG y Operaciones AritmeticasDocument5 pagesPractica03 - SREG y Operaciones AritmeticasEsthefaniPas encore d'évaluation

- Mantenimiento de MonitoresDocument9 pagesMantenimiento de MonitorestumalkePas encore d'évaluation

- TroceadorDocument4 pagesTroceadorcristianPas encore d'évaluation

- Manual INEL4211Document104 pagesManual INEL4211diego fuentesPas encore d'évaluation

- 1826na PDFDocument2 pages1826na PDFjorgeoscar1Pas encore d'évaluation

- Antologia de Arquitectura de ComputadorasDocument95 pagesAntologia de Arquitectura de ComputadorasCésar Vicente Morales Morales100% (1)

- Información PLCs Siemens y Allen BradleyDocument8 pagesInformación PLCs Siemens y Allen BradleykevmorenoPas encore d'évaluation

- Practica 4 Amplificador OperacionalDocument7 pagesPractica 4 Amplificador OperacionalKenshin Ancona PerezPas encore d'évaluation

- MB240 SP Datasheet A4Document2 pagesMB240 SP Datasheet A4Julio AriasPas encore d'évaluation

- MEMORIADocument11 pagesMEMORIARvth JiménezhPas encore d'évaluation

- SsssDocument53 pagesSsssAndrés Llanos SánchezPas encore d'évaluation

- Panasonic tc-20g9 CH br1lDocument27 pagesPanasonic tc-20g9 CH br1lrinaldo felixPas encore d'évaluation

- Reporte Semanal ActividadesDocument44 pagesReporte Semanal ActividadesVladimir ParrasPas encore d'évaluation

- Arquitectura Harvard - FinalDocument10 pagesArquitectura Harvard - FinalOrlandoPas encore d'évaluation

- Definición de PLCDocument10 pagesDefinición de PLCJose FloresPas encore d'évaluation

- Examen Parcial de Sistemas Digitales 2021 - 0Document3 pagesExamen Parcial de Sistemas Digitales 2021 - 0petiojpPas encore d'évaluation

- Lineas TXDocument2 pagesLineas TXj_salazar20Pas encore d'évaluation

- Taller No. 1 Taller Sobre Compuertas Lógicas y Tablas de VerdadDocument5 pagesTaller No. 1 Taller Sobre Compuertas Lógicas y Tablas de VerdadmilenaPas encore d'évaluation

- Guia de Simulacion Tres. Circuitos de Segundo OrdenDocument5 pagesGuia de Simulacion Tres. Circuitos de Segundo OrdenMiguel LandaverdePas encore d'évaluation

- Problemas Propuestos TelecomunicacionesDocument2 pagesProblemas Propuestos TelecomunicacionesjoserxPas encore d'évaluation

- Símbolos Eléctricos Control IndustrialDocument44 pagesSímbolos Eléctricos Control IndustrialVíctor Flores AndinoPas encore d'évaluation

- Generaciones ComputadorasDocument8 pagesGeneraciones Computadorasj0k3rb4ckPas encore d'évaluation

- Uso Del MicrocomputadorDocument5 pagesUso Del MicrocomputadorDANELISPas encore d'évaluation

- Evaluacion Final - Escenario 8 - Arquitectura Del Computador - (Grupo1)Document9 pagesEvaluacion Final - Escenario 8 - Arquitectura Del Computador - (Grupo1)Laura GutierrezPas encore d'évaluation

- Universidad Nacional de IngenieriaDocument15 pagesUniversidad Nacional de IngenieriaHollmandavid VasquezPas encore d'évaluation

- LM339Document2 pagesLM339Renny DavidPas encore d'évaluation

- Mezclador de Audio-1Document5 pagesMezclador de Audio-1Ricardo Ramírez AngelesPas encore d'évaluation

- Buses de DatosDocument98 pagesBuses de DatosKing AuxPas encore d'évaluation

- Alcad Catálogo Videoporteros Ctrol Accesos Hogar Digital 2020Document100 pagesAlcad Catálogo Videoporteros Ctrol Accesos Hogar Digital 2020VEMATELPas encore d'évaluation

- Práctica3 2019BDocument4 pagesPráctica3 2019Bbryan zuritaPas encore d'évaluation