Académique Documents

Professionnel Documents

Culture Documents

p4 VHDL Full

Transféré par

Martinez Rivera HermesTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

p4 VHDL Full

Transféré par

Martinez Rivera HermesDroits d'auteur :

Formats disponibles

MATERIA

Diseo Digital con VHDL

SERIE

5IE6

PRACTICA No.4

NOMBRE DE LA PRACTICA Mquina de Estados en VHDL

NOMBRE DEL ALUMNO Martnez Rivera Hermes Julio Adrin Alcaraz Valds

FECHA DE ELABORACION 22/ABRIL/13

NOMBRE DEL MAESTRO M.CJazmin Maldonado Robles.

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

I.

INDICE GENERAL

I. Indice general .................................................................................................................................................. 2 II. Indice de figuras.............................................................................................................................................. 2 III.Indice de tablas ............................................................................................................................................... 2 IV. Introduccin ................................................................................................................................................... 3 V. Objetivos ........................................................................................................................................................ 3 VI. Marco Terico................................................................................................................................................ 4 6.1 Diseo lgico secuencial .............................................................................................................................. 4 6.2 Flip-flops .................................................................................................................................................. 4 6.3 Diseo de sistemas secuenciales sncronos ......................................................................................... 7 VII.Material y Equipo ......................................................................................................................................... 11 VIII. Procedimiento y metodologa .................................................................................................................... 12 8.1 Maquina de estados Mealy ......................................................................................................................... 12 8.2 Maquina de estados tipo Moore ................................................................................................................. 16 IX. Discusin de resultados experimentales .................................................................................................... 20 X. Conclusiones ................................................................................................................................................ 21 XI. Bibliografa .................................................................................................................................................. 21 XII. Anexos ....................................................................................................................................................... 22

II.

INDICE DE FIGURAS

Figura 6. 1 Estructura de un sistema secuencial ..................................................................... 4 Figura 6. 2 Flip-flops y tablas de verdad caractersticas .......................................................... 5 Figura 6.3 a) Diagrama y tabla de verdad del flip-flop D, b) Flujo de informacin en el dispositivo. ........................................................................................................................................................... 5 Figura 6. 4 Simulacin del flip-flop D . ........................................................................................... 6 Figura 6. 5 Arquitectura secuencial de Mealy .............................................................................. 8 Figura 6. 6 Arquitectura secuencial de Moore . ........................................................................ 8 Figura 6.7 Detector de secuencia ............................................................................................. 9 Figura 6.8 Transicin de un estado a otro ................................................................................. 9 Figura 6.9 a) Diagrama de Estados, b) Tabla de estados. .................................................. 10 Figura 8.1 Problema inciso a-- Diagrama de estados ..................................................................... 12 Figura 8.2 Problema inciso b---- Diagrama de estados ................................................................... 16 Figura 9.1 Asignacin de pines del problema 8.1a .......................................................................... 20 Figura 9.2 Asignacin de pines del problema 8.2b .......................................................................... 20

III.

INDICE DE TABLAS

Tabla I. Tabla de estados del problema a ........................................................................................................ 13

Tabla II. Tabla de estados del problema b) ...................................................................................................... 17

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

IV.

INTRODUCCIN

En esta prctica se utilizar VHDL para sintetizar mquinas de estados de Mealy y Moore, para ello presentamos en la seccion 8.1 y 8.2 dos ejemplos implementados en VHDL, en donde teniendo el diagrama y la tabla de estados , lo codificamos al lenguaje de descripcin de hardware. Adems tambin se presenta en la seccin 6 la teora bsica para la comprensin de las maquinas de estado, las cuales son bsicamente sistemas secuenciales con un numero finito de estados, las cuales tienen aplicaciones, como el sistema de un semforo, elevador, el televisor, contadores, etc.

V.

OBJETIVOS

Disear mquinas de estados Mealy y Moore en cdigo VHDL.

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

VI.

MARCO TERICO

6.1 Diseo lgico secuencial Un sistema secuencial est formado por un circuito combinacional y un elemento de memoria encargado de almacenar de forma temporal la historia del sistema. En esencia, la salida de un sistema secuencial no slo depende del valor presente de las entradas, sino tambin de la historia del sistema, segn se observa en la figura 6.1

Figura 6. 1 Estructura de un sistema secuencial

Bsicamente hay dos tipos de sistemas secuenciales : sncronos y asin- cronos; el comportamiento de los primeros se encuentra sincronizado mediante el pulso de reloj del sistema, mientras que el funcionamiento de los sistemas asincronos depende del orden y momento en el cual se aplican sus seales de entrada, por lo que no requieren un pulso de reloj para sincronizar sus acciones . 6.2 Flip-flops

El elemento de memoria utilizado indistintamente en el diseo de los sistemas sncronos o asincronos se conoce como flip-flop o celda binaria. La caracterstica principal de un flip-flop es mantener o almacenar un bit de manera indefinida hasta que a travs de un pulso o una seal cambie de estado. Los flip-flops ms conocidos son los tipos SR , JK, T y D. En la figura 6.2 se presenta cada uno de estos elementos y la tabla de verdad que describe su comportamiento.

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Figura 6. 2 Flip-flops y tablas de verdad caractersticas .

Es importante recordar el significado de la notacin Q y Q( +i); Q = estado presente o actual Q +1 = estado futuro o siguiente t Por ejemplo, consideremos la tabla de verdad que describe el funcionamiento del flip-flop tipo D, mostrado en la figura 6.2c) y que se muestra de nuevo en la figura 6.3a) .

Figura 6.3 a) Diagrama y tabla de verdad del flip-flop D, b) Flujo de informacin en el dispositivo.

Cuando el valor de la entrada D es igual a 1, figura 6.3b), la salida Q t + i adopta el valor de 1: Q t+i =1 siempre y cuando se genere un pulso de reloj. Es importante resaltar que el

5

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

valor actual en la entrada D es transferido a la salida Q t + sin importar cul sea el valor previo que haya tenido la salida Q en el estado presente. En el diseo secuencial con VHDL las declaraciones If-then*else son las ms utilizadas; por ejemplo, el programa del listado 6.1 usa estas declaraciones. La ejecucin del proceso es sensible a los cambios en clk (pulso de reloj); esto es, cuando clk cambia de valor de una transicin de 0 a 1 (clk 1), el valor de D se asigna a Q y se conserva hasta que se genera un nuevo pulso. A la inversa, si clk no presenta dicha transicin, el valor de Q se mantiene igual. Esto puede observarse con claridad en la simulacin del circuito, fig. 6.4.

Listado 6.1 Descripcin de un flip-flop disparado por flanco

Figura 6. 4 Simulacin del flip-flop D .

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Notemos que la salida Q toma el valor de la entrada D slo cuando la transicin del pulso de reloj es de 0 a 1 y se mantiene hasta que se ejecuta de nuevo el cambio de valor de la entrada clk. Atributo event En el lenguaje VHD L los atributos sirven para definir caractersticas que se pueden asociar con cualquier tipo de datos, objeto o entidades . El atributo event1 (evento) se utiliza para describir un hech o u ocurrencia de una seal en particular. En el cdigo del listado 4-1 podemos observar que la condicin if clk'event es cierta slo cuando ocurre un cambio de valor; es decir, un suceso (event) de la seal clk. Como se puede apreciar, la declaracin (if-then) no maneja la condicin else, debido a que el compilador mantiene el valor de Q hasta que no exista un cambio de valor en la seal clk. 6.3 Diseo de sistemas secuenciales sncronos Como ya se mencion, la estructura de los sistemas secuenciales sncronos basa su funcionamiento en los elementos de memoria conocidos como flip-flops . La palabra sincrona se refiere a que cada uno de estos elementos de memoria que interactan en un sistema se encuentran conectados a la misma seal de reloj, de forma tal que slo se producir un cambio de estado en el sistema cuando ocurra un flanco de disparo o un pulso en la seal de reloj . Existe una divisin en el diseo de los sistemas secuenciales que se refiere momento en que se producir la salida del sistema . al

En la estructura de Mealy (Fig. 6.5) las seales de salida dependen tanto del estado en que se encuentra el sistema, como de la entrada que se aplica en determinado momento . En la estructura de Moore (Fig. 6.6) la seal de salida slo depende del estado en que se encuentra .

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Figura 6. 5 Arquitectura secuencial de Mealy.

Figura 6. 6 Arquitectura secuencial de Moore .

Un sistema secuencial se desarrolla a travs de una serie de pasos generalizados que comprenden el enunciado del problema, diagrama de estados, tabla de estados, asignacin de estados, ecuaciones de entrada a los elementos de memoria y diagrama electrnico del circuito . Como ejemplo consideremos el diseo del siguiente sistema secuencial (Fig, 6.7) , en el cual se emite un pulso de salida Z( Z = l ) cuando en la lnea de entrada (X ) se reciben cuatro unos en forma consecutiva en caso contrario, la salida Z es igual a cero .

8

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Figura 6.7 Detector de secuencia .

Diagramas de estado El uso de diagramas de estados en la lgica programable facilita de manera significativa la descripcin de un diseo secuencial, ya que no es necesario seguir la metodologa tradicional de diseo . En VHD L se puede utilizar un modelo funcional en que slo se indica la transicin que siguen los estados y las condiciones que controlarn el proceso . De acuerdo con nuestro ejemplo (Fig. 6.9), vemos que el sistema secuencial se puede representar por medio del diagrama de estados de la figura 6.9a) : arquitectura Mealy. En este diagrama se advierte que el sistema cuenta con una seal de entrada denominada X y una seal de salida Z . En la figura 6.9b) se muestra la tabla de estados que describe el comportamiento del circuito . Cuando se est en el estado dO y la seal de entrada X es igual a uno, se avanza al estado di y la salida Z durante esta transicin es igual a cero; en caso contrario, cuando la entrada X es igual a cero, el circuito se mantiene en el estado dO y la salida tambin es cero (Fig. 6.8) .

Figura 6.8 Transicin de un estado a otro .

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Con un poco de lgica se puede intuir el comportamiento del diagrama de estados . Observe como slo la secuencia de cuatro unos consecutivos provoca que la salida Z = 1.

Figura 6.9 a) Diagrama de Estados, b) Tabla de estados.

Este diagrama se puede codificar con facilidad mediante una descripcin de alto nivel en VHDL . Esta descripcin supone el uso de declaraciones case-when las cuales determinan, en un caso particular, el valor que tomar el siguiente estado . Por otr o lado, la transicin entre estados se realiza por medio de declaraciones ifthen'else , de tal forma que stas se encargan de establecer la lgica que seguir el programa para realizar la asignacin del estado.

10

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

VII.

MATERIAL Y EQUIPO

1. Tarjeta Spartan XC3S700A 2. Software Xilinx v13.4 3. Libro: El arte de programar en VHDL

11

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

VIII.

PROCEDIMIENTO Y METODOLOGA

En la presente seccin, nos enfocaremos en los pasos que se llevan a cabo para el diseo en VHDL de una maquina autmata finita: Moore y Mealy. Esta seccin se subdivide en dos: 8.1 y 8.2, en la primera explicaremos la implementacin de una maquina de Mealy en VHDL empleando un ejemplo, y en la segunda parte se presenta el cdigo para una maquina de tipo moore. 8.1 Maquina de estados Mealy Para la implementacin en vhdl, se utilizar el siguiente ejemplo: a) Un circuito secuencial tiene una entrada X y una salida Z, dibuje un diagrama de estados que cumpla con lo siguiente, la salida es Z=1 s y slo si el nmero total de unos es divisible por 3. Como primer paso para su resolucin, dibujaremos el diagrama y la tabla de estados .

Figura 8.1 Problema inciso a-- Diagrama de estados

12

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

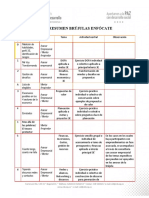

Tabla I. Tabla de estados del problema a

Edo Presente S0 S1 S2

Edo Siguiente X=0 S0 S1 S1 S2 S2 S0

X=1

Salida X=0 0 0 0

X=1 0 0 1

El segundo paso corresponde en su codificacin en el lenguaje de descripcin de hardware(VHDL), para ello empezamos declarando los puerto de entrada y salida dentro del cuerpo de la entidad (lneas 4 a la 9), en donde se observa que se define como entrada CLK,X e INI, las cuales son el reloj de pulsos, la entrada de excitacin y el habilitador respectivamente. Para poder representar los estados (S0,S1 Y S2) en VHDL, hay que definirlos dentro de un tipo de datos enumerados mediante la declaracin type (lnea 12). As tambin se declara en la lnea 15 las seales del estado actual y estado siguiente. Las lneas 13 y 16 se enfocan en las seales auxiliares que se utilizaran para la transicin de los estados. Tal vez cabe aclarar que se emplea la seal CLK_1hz para definir el ciclo de un pulso.

Antes de declarar la transicin entre estados hay que definir un reset, el divisor de frecuencia y la inicializacin de la memoria de los biestables. Empezamos por definir en la lnea 19, el reset, para que posteriormente se defina el divisor de frecuencia, el cual en nuestro caso ser de un 1hz, esto para que se pueda percibir el cambio de un estado a otro, para ello se usa un process el cual est definido dentro de las lneas 21 a la 31.

13

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Para el proceso process de inicializacin de la memoria de los biestables se declara dentro de las lneas 37 a la 45, el cual tiene la condicin: si el reset es uno, entonces que le asigne el estado S0 al estado actual, si en cambio detecta un flanco ascendente en el pulso de reloj que el estado siguiente pase a ser el estado actual.

La transicin de un estado a otro emplearemos el process que esta definido dentro de las lneas 43-68, el cual usa la instruccin case para cuando el estado actual se encuentre en S0,S1 o S2, y una vez que se determina el estado se evalua el valor de la entrada,ya sea 0 o 1 , y una vez que el process verifique estas condiciones, le asigna al estado siguiente el valor determinado por las entradas.

14

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

La salida estar determina por la lnea 69, en donde se le asigna un 1 cuando el estado actual sea igual a S2, en el caso contrario que el estado actual no se encuentre en S2 el valor de la salida ser 0.

15

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

8.2 Maquina de estados tipo Moore Para ilustrar la implementacin de una maquina moore en vhdl, nos basamos del siguiente ejemplo: b) Disee un circuito secuencial que proporcione una salida Z=1 durante exactamente cuatro ciclos de reloj cada vez que una persona pulse un botn (X=1). Tenga en cuenta que el reloj de un circuito digital es usualmente mucho ms rpido que el dedo de una persona. La persona probablemente no haya podido todava soltar el botn en el instante en el que ya han transcurrido los cuatro ciclos de reloj, por lo que X puede continuar valiendo 1 despus de haberse generado las cuatro salidas Z=1. Por tanto, despus de que Z sea 1 durante cuatro ciclos de reloj, Z debe pasar a valer 0, hasta que Z vuelva a 0 y pase a 1 de nuevo. Disee un diagrama de de Mealy para este circuito. La resolucin de la mquina de estados se presenta en la figura 8.2

Figura 8.2 Problema inciso b---- Diagrama de estados

16

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Tabla II. Tabla de estados del problema b)

Edo presente S0 S1 S2 S3 S4

Edo Siguiente X=0 X=1 S0 S1 S2 S2 S3 S3 S4 S4 S0 S0

Salida 0 0 0 1 0

Una vez que tenemos la resolucin del problema en la fig.7.2, se procede a implementarlo en cdigo VHDL, y para ello empezamos declarando los puertos de entrada y salida (lneas 4-9). Las entradas son: el pulso de reloj CLK , la entrada de excitacin X, el reset ~INI, y el puerto de salida Z. Todas ellas de tipo std_logic.

Ahora se procede a definir la arquitectura de la entidad definida en las lneas 11-101, en la cual declaramos el comportamiento de nuestra maquina secuencial, y para ello se requiere declarar en primer lugar el estado actual y siguiente como seales de tipo std_logic_vector de tres componentes, y las seales: clk_1hz,cuenta e iniciar se declaran para su uso en el divisor de frecuenciay el estado de memoria.

17

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Quizs la diferencia ms notable en el listado anterior con el cdigo de una maquina mealy es la manera en que se declaran los estados, en donde ya no se declaran como tipo de datos, sino como constantes y se les asigna su valor como un vector de tres componentes de tipo std_logic_vector. Para el proceso del divisor de frecuencia es equivalente al visto en la seccin 7.1, en donde se usa el divisor para una frecuencia de 1 hertz, aunque si se desea que el ciclo del pulso sea otra, el diseador la puede modificar en las lneas 30 a la lnea 40.

En el proceso Memoria (lneas 42-50) se establecen las condiciones inciales de la mquina de estados para el problema del inciso b, en donde se puede observar en listado inferior, que cuando la senal iniciar adquiere el valor de 1 el estado SO es asignado como el estado actual, o sino cuando detecte un flanco ascendente que el estado siguiente venga a valer el estado actual.

Para determinar el estado siguiente de la maquina en cdigo, se tiene que declarar primeramente un process (lneas 52 a la 97), la cual se construye en base a la tabla de estado de la figura 7.2 b. para determinar el edo siguiente se usa la declaracin case-when, y para las entradas

18

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

se emplea if-else ,as por ejemplo cuando el estado actual se encuentre en S0, y en la entrada tenga un valor x=1 que el estado siguiente se le asigne el valor de S5 sino S1.

Para el cdigo de la salida se utiliza la siguiente asignacin:

19

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

IX.

DISCUSIN DE RESULTADOS EXPERIMENTALES

Para el ejercicio visto en la seccin 8.1, los pines que se utilizaron fueron los que se ilustran en la figura 9.1.

Figura 9.1 Asignacin de pines del problema 8.1a

E12 Para el pulso de reloj, U10 para el INI, U8 para la variable de entrada y R20 el indicador de la salida, los resultados obtenidos fueron satisfactorios, debido a que cuando se deja en uno el sw2 una vez que pasen 3 segundos la salida se hace uno, con esto se confirma el diseo exitoso de la maquina secuencial mealy. Para el ejercicio de la seccin 7.2 se asignaron los pines como se muestra en la figura 9.2, siendo E12 al pulso de reloj , T15 la variable de entrada x, U10 como INI y por ultimo R20 como la salida Z.

20

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Figura 9.2 Asignacin de pines del problema 8.2b

X.

CONCLUSIONES

Hermes Martinez Rivera

Para el diseo de una maquina secuencial autmata; ya sea moore o mealy, se debe de tener en cuenta los siguientes pasos: disear el diagrama de estados, la tabla de transiciones, la codificacin de la tabla , los mapas de karnaugh, las ecuaciones del estado siguiente y el logigrama. La implementacin del cdigo en vhdl, se baso del ejemplo hecho en clase, para el cual es necesario tener presente que se requieren 3 procesos para poder llevar a cabo un correcto funcionamiento; el primer proceso es para el divisor de frecuencia, el segundo es para la memorizacin o inicializacin de los estados, y el tercer proceso se emplea para determinar el valor del estado siguiente. La diferencia en la implementacin de las dos maquinas en VHDL fue el tipo de datos que se empleo para asignar los estados, en el cual para la mquina de mealy se utilizo la instruccin type, y en la maquina de moore la declaracin de los estados como constant de tipo std_logic_vector. Julio Alcaraz

XI.

BIBLIOGRAFA

[1] VHDL El arte de programar sistemas digitales, David G. Maxinez ,Jessica Alcal Jar a, 1ra edicin, editorial continental, imprimido en Mexico 2002. [2] Manual Spartan 3.

21

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

XII.

ANEXOS

Cdigo del problema de la seccin 7.1

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Maq_Mealy_a is Port ( CLK : in STD_LOGIC; X : in STD_LOGIC; INI : in STD_LOGIC; Z : out STD_LOGIC); end Maq_Mealy_a; architecture Behavioral of Maq_Mealy_a is type Estado is (S0,S1,S2); signal Edo_A, Edo_S: Estado; signal Iniciar: STD_LOGIC; signal CLK_1hz: STD_LOGIC:= '0'; signal cuenta: integer:= 0; begin Iniciar<= not INI; divisor: process(CLK,Iniciar) begin if(CLK='1' and CLK'EVENT) then if(cuenta= 25000000) then cuenta<= 0; CLK_1hz <= not CLK_1hz; else cuenta<= cuenta +1; end if; end if; end process divisor;

Memoria: process(CLK_1hz,Iniciar) begin if(Iniciar='1') then Edo_A <= S0; elsif(rising_edge(CLK_1hz))then Edo_A <= Edo_S; end if;

22

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

end process Memoria; Edo_siguiente: process(X, Edo_A) begin Case Edo_A is when S0 => if(X='1') then Edo_S <= S1; else Edo_S <= S0; end if; when S1 => if(X='1') then Edo_S <= S2; else Edo_S <= S1; end if; when S2 => if (X='1') then Edo_S <= S0; else Edo_S <= S2; end if; when others => Edo_S <= S0; end case; end process Edo_siguiente; Z <= '1' when Edo_A = S2 else '0'; end Behavioral;

Cdigo del problema de la seccion 7.2

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Maq_Moore is Port ( CLK : in STD_LOGIC; X : in STD_LOGIC; INI : in STD_LOGIC; Z : out STD_LOGIC);

23

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

end Maq_Moore; architecture Behavioral of Maq_Moore is --type Estado is (S0,S1,S2,S3); signal Edo_A, Edo_S: std_logic_vector(2 downto 0):="000"; signal Iniciar: STD_LOGIC; signal CLK_1hz: STD_LOGIC:= '0'; signal cuenta: integer:= 0; constant S0: std_logic_vector(2 downto 0):= "001"; constant S1: std_logic_vector(2 downto 0):= "010"; constant S2: std_logic_vector(2 downto 0):= "011"; constant S3: std_logic_vector(2 downto 0):= "100"; constant S4: std_logic_vector(2 downto 0):= "101"; constant S5: std_logic_vector(2 downto 0):= "110"; begin Iniciar<= not INI; divisor: process(CLK,Iniciar) begin if(CLK='1' and CLK'EVENT) then if(cuenta= 25000000) then cuenta<= 0; CLK_1hz <= not CLK_1hz; else cuenta<= cuenta +1; end if; end if; end process; Memoria: process(CLK_1hz,Iniciar) begin if(Iniciar='1') then Edo_A <= S0; elsif(rising_edge(CLK_1hz))then Edo_A <= Edo_S; end if; end process; Edo_siguiente: process(X, Edo_A) begin Case Edo_A is when S0 => if(X='1') then Edo_S <= S5; else Edo_S <= S1; end if;

24

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

when S1 => if(X='1') then Edo_S <= S4; else Edo_S <= S2; end if; when S2 => if (X='1') then Edo_S <= S3; else Edo_S <= S1; end if; when S3 => if(X= '1') then Edo_S <= S2; else Edo_S <= S4; end if; when S4 => if(X= '1') then Edo_S <= S1; else Edo_S <= S3; end if; when S5 => if(X= '1') then Edo_S <= S0; else Edo_S <= S4; end if; when others => Edo_S <= S0; end case; end process; Z <= '1' when Edo_A = S3 else '0'; end Behavioral;

25

Instituto Tecnolgico de Tijuana

Departamento de Ingeniera Elctrica y Electrnica

Vous aimerez peut-être aussi

- Luminaria Decorativa Colgante 87WDocument1 pageLuminaria Decorativa Colgante 87WMartinez Rivera HermesPas encore d'évaluation

- Cotizacion IsraelitaDocument2 pagesCotizacion IsraelitaMartinez Rivera HermesPas encore d'évaluation

- Cotizacion Miriam v5Document1 pageCotizacion Miriam v5Martinez Rivera HermesPas encore d'évaluation

- Preparatoria Federal Lázaro Cárdenas - Google MapsDocument1 pagePreparatoria Federal Lázaro Cárdenas - Google MapsMartinez Rivera HermesPas encore d'évaluation

- 02 Adverbios (Como Se Forman)Document5 pages02 Adverbios (Como Se Forman)Martinez Rivera HermesPas encore d'évaluation

- Lesson 4. 0 Comparativos y Superlativos.Document12 pagesLesson 4. 0 Comparativos y Superlativos.Martinez Rivera Hermes0% (1)

- Analisis FodaDocument30 pagesAnalisis FodaMartinez Rivera HermesPas encore d'évaluation

- 01 British Council-Present TenseDocument5 pages01 British Council-Present TenseMartinez Rivera HermesPas encore d'évaluation

- rt115 CaidadetensionDocument5 pagesrt115 CaidadetensionAmonRohPas encore d'évaluation

- Practica Filtros ActivosDocument10 pagesPractica Filtros ActivosMartinez Rivera HermesPas encore d'évaluation

- Temario de Taller de Investigacion 2Document16 pagesTemario de Taller de Investigacion 2Martinez Rivera HermesPas encore d'évaluation

- Cuota de Pantalla Obras de Cine - Analisis Comparado - Final - v3Document9 pagesCuota de Pantalla Obras de Cine - Analisis Comparado - Final - v3Tripolina ZukPas encore d'évaluation

- Analisis ElectricaDocument12 pagesAnalisis ElectricaorlandoPas encore d'évaluation

- Qué Es El ComieDocument2 pagesQué Es El ComieSusy AmayaPas encore d'évaluation

- PROSPECTIVA ESTRATEGICA - Fase 3 - Construir El Escenario ApuestaDocument14 pagesPROSPECTIVA ESTRATEGICA - Fase 3 - Construir El Escenario ApuestaKarolina OrtizPas encore d'évaluation

- Guia de Taller Motor de ArranqueDocument12 pagesGuia de Taller Motor de ArranquerobertoPas encore d'évaluation

- 1.2.2 Meiosis PDFDocument29 pages1.2.2 Meiosis PDFKarlita MariaPas encore d'évaluation

- Fines TributariosDocument43 pagesFines TributariosCristhian Diego Alvites HuizaPas encore d'évaluation

- Resolución de Problema de Destilación Por El Método de PonchonDocument14 pagesResolución de Problema de Destilación Por El Método de PonchonAnahi Montiel100% (1)

- Generador de Acero en Pilas - Torre Sur (Revisión 4)Document4 pagesGenerador de Acero en Pilas - Torre Sur (Revisión 4)German Binzha GonzalezPas encore d'évaluation

- Dda Aumento de AlimentosDocument6 pagesDda Aumento de AlimentosvanessaPas encore d'évaluation

- Doce Hombres Sin PiedadDocument14 pagesDoce Hombres Sin PiedadAntia Couto ArcaPas encore d'évaluation

- Buenos Dias Mina Justa 2022.07.08Document5 pagesBuenos Dias Mina Justa 2022.07.08Eloy Ayna AduviriPas encore d'évaluation

- Relaciones A La Luz de La AlteridadDocument7 pagesRelaciones A La Luz de La AlteridadYennifer LlanosPas encore d'évaluation

- Características de La Educación VirtualDocument3 pagesCaracterísticas de La Educación VirtualYoselyn LaricoPas encore d'évaluation

- Tarea Logistica (2 - 4)Document6 pagesTarea Logistica (2 - 4)Anonymous FezJJ6bIPas encore d'évaluation

- Stat 1203 221 2 T3Document5 pagesStat 1203 221 2 T3Karolina Hermoza100% (1)

- 001 HMA El tu00EDtulo Valor IncompletoDocument8 pages001 HMA El tu00EDtulo Valor IncompletoMónica TejeroPas encore d'évaluation

- Informe Geotecnico 60+700Document24 pagesInforme Geotecnico 60+700Fabian MarcialesPas encore d'évaluation

- PDF Informe Composicion y Descomposicion de Vectores CompressDocument13 pagesPDF Informe Composicion y Descomposicion de Vectores CompressChristian FuentesPas encore d'évaluation

- Septiembre 27 Victoria 2013 DefDocument25 pagesSeptiembre 27 Victoria 2013 DefPagina web Diario elsigloPas encore d'évaluation

- NOVACERO CATALOGO A4 9abrilDocument20 pagesNOVACERO CATALOGO A4 9abrilJohanna100% (1)

- O.M.T MAICKOL TRUJILLO (Autoguardado)Document23 pagesO.M.T MAICKOL TRUJILLO (Autoguardado)Maikol TrujilloPas encore d'évaluation

- Separata N°1 - Biología PDFDocument2 pagesSeparata N°1 - Biología PDFYessy Quispe100% (1)

- WencdorDocument30 pagesWencdorKevin SilvaPas encore d'évaluation

- 02.enero 2022.geografía - El Universo y El Sistema Planetario SolarDocument4 pages02.enero 2022.geografía - El Universo y El Sistema Planetario Solarbelu_jhansiniPas encore d'évaluation

- Proceso Constructivo de Un Sistema de AlcantarilladoDocument20 pagesProceso Constructivo de Un Sistema de AlcantarilladoMarcelino Dzul UcanPas encore d'évaluation

- Diseño Del Sistema de Puesta A Tierra de Una Planta Termoeléctrica de Generación PDFDocument110 pagesDiseño Del Sistema de Puesta A Tierra de Una Planta Termoeléctrica de Generación PDFAlbertoCedeñoPas encore d'évaluation

- Guía Resumen BrújulasDocument4 pagesGuía Resumen BrújulasPabloPas encore d'évaluation

- Coaching Personalizado de Peligros y Riesgos Conasurmin RDocument44 pagesCoaching Personalizado de Peligros y Riesgos Conasurmin RalterPas encore d'évaluation

- Ensayo-Plan Cuaternal GRCDocument8 pagesEnsayo-Plan Cuaternal GRCLucy GallardoPas encore d'évaluation