Académique Documents

Professionnel Documents

Culture Documents

14-Bit Registered Buffer With SSTL I-O

Transféré par

ScribdspaceDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

14-Bit Registered Buffer With SSTL I-O

Transféré par

ScribdspaceDroits d'auteur :

Formats disponibles

IDT74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL I/O

INDUSTRIAL TEMPERATURE RANGE

14-BIT REGISTERED BUFFER WITH SSTL I/O

IDT74SSTV16857

FEATURES:

1:1 registered buffer Meets or exceeds JEDEC standards for SSTV16857 and SSTVN16857 2.3V to 2.7V operation for PC1600, PC2100, and PC2700 2.5V to 2.7V operation for PC3200 SSTL_2 Class II style data inputs/outputs Differential CLK input RESET control compatible with LVCMOS levels Flow-through architecture for optimum PCB design Drive up to equivalent of 18 SDRAM loads Latch-up performance exceeds 100mA ESD >2000V per MIL-STD-883, Method 3015; >200V using machine model (C = 200pF, R = 0) Available in TSSOP package

DESCRIPTION:

The SSTV16857 is a 14-bit registered buffer designed for 2.3V-2.7V VDD for PC1600-PC2700, and 2.5V-2.7V VDD for PC3200, and supports low standby operation. All data inputs and outputs are SSTL_2 level compatible with JEDEC standard for SSTL_2. RESET is an LVCMOS input since it must operate predictably during the power-up phase. RESET, which can be operated independent of CLK and CLK, must be held in the low state during power-up in order to ensure predictable outputs (low state) before a stable clock has been applied. RESET, when in the low state, will disable all input receivers, reset all registers, and force all outputs to a low state, before a stable clock has been applied. With inputs held low and a stable clock applied, outputs will remain low during the Low-to-High transition of RESET.

APPLICATIONS:

Along with CSPT857C/D, Zero Delay PLL Clock buffer, provides complete solution for DDR1 DIMMs

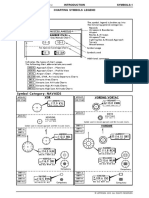

FUNCTIONAL BLOCK DIAGRAM

RESET 34

CK CK

38 39

VREF D1

35 48 1D C1 R 1 Q1

TO 13 OTHER CHANNELS

INDUSTRIAL TEMPERATURE RANGE

1

c 2003 Integrated Device Technology, Inc.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

February 2009

DSC-5737/8

IDT74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL I/O

INDUSTRIAL TEMPERATURE RANGE

PIN CONFIGURATION

Q1 Q2 GND VDDQ Q3 Q4 Q5 GND VDDQ Q6 Q7 VDDQ GND Q8 Q9 VDDQ GND Q10 Q11 Q12 VDDQ GND Q13 Q14 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 D1 D2 GND VDD D3 D4 D5 D6 D7 CLK CLK VDD

GND

ABSOLUTE MAXIMUM RATINGS(1)

Symbol VI

(2)

Description Input Voltage Range Output Voltage Range Input Clamp Current, VI < 0 Output Clamp Current, VO < 0 or VO > VDDQ Continuous Output Current, VO = 0 to VDDQ Continuous Current through each VDD, VDDQ or GND Storage Temperature Range

Max. 0.5 to 3.6 0.5 to VDD +0.5 0.5 to VDDQ +0.5 50 50 50 100 65 to +150

Unit V V V mA mA mA mA C

VDD or VDDQ Supply Voltage Range VO(3) IIK IOK IO VDD TSTG

NOTES: 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability. 2. The input and output negative voltage ratings may be exceeded if the ratings of the I/P and O/P clamp current are observed. 3. The output current will flow if the following conditions are observed: a) Output in HIGH state b) VO = VDDQ

VREF RESET D8 D9 D10 D11 D12 VDD GND D13 D14

FUNCTION TABLE(1)

Input RESET H H H L CLK L or H X CLK L or H X D L H X X Q Outputs L H Q(2) L

NOTES: 1. H = HIGH Voltage Level L = LOW Voltage Level X = Dont Care = LOW to HIGH = HIGH to LOW 2. Q = Output level before the indicated steady-state conditions were established.

TSSOP TOP VIEW

IDT74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL I/O

INDUSTRIAL TEMPERATURE RANGE

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (PC1600-PC2700)

Following Conditions Apply Unless Otherwise Specified: Operating Condition: TA = 40C to +85C, VDD = 2.5V 0.2V, VDDQ = 2.5V 0.2V

Symbol VIK VOH VOL II IDD IDDD All Inputs Static Standby Static Operating Dynamic Operating (Clock Only) Dynamic Operating (Per Each Data Input) rOH rOL rO() CI Output HIGH Output LOW | rOH- rOL| each separate bit Data Inputs CLK and CLK RESET Parameter Control Inputs Test Conditions VDD = 2.3V, II = 18mA VDD = 2.3V to 2.7V, IOH = -100A VDD = 2.3V, IOH = -16mA VDD = 2.3V to 2.7V, IOL = 100A VDD = 2.3V, IOL = 16mA VDD = 2.7V, VI = VDD or GND IO = 0, VDD = 2.7V, RESET = GND IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC) IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC), CLK and CLK Switching 50% Duty Cycle. IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC), CLK and CLK Switching 50% Duty Cycle. One Data Input Switching at Half Clock Frequency, 50% Duty Cycle. VDD = 2.3V to 2.7V, IOH = -20mA VDD = 2.3V to 2.7V, IOH = 20mA VDD = 2.5V, TA = 25C, IOH = -20mA VDD = 2.5V, VI = VREF 310mV VICR = 1.25V, VI (PP) = 360mV VI = VDD or GND 7 7 2.5 2.5 20 20 4 3.5 3.5 pF Min. VDD 0.2 1.95 Typ. Max. 1.2 0.2 0.35 5 0.01 A/Clock MHz A/Clock MHz/Data Input A mA V Unit V V

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (PC3200)

Following Conditions Apply Unless Otherwise Specified: Operating Condition: TA = 40C to +85C, VDD = 2.6V 0.1V, VDDQ = 2.6V 0.1V

Symbol VIK VOH VOL II IDD IDDD All Inputs Static Standby Static Operating Dynamic Operating (Clock Only) Dynamic Operating (Per Each Data Input) rOH rOL rO() CI Output HIGH Output LOW | rOH- rOL| each separate bit Data Inputs CLK and CLK RESET Parameter Control Inputs Test Conditions VDD = 2.5V, II = 18mA VDD = 2.5V to 2.7V, IOH = -100A VDD = 2.5V, IOH = -16mA VDD = 2.5V to 2.7V, IOL = 100A VDD = 2.5V, IOL = 16mA VDD = 2.7V, VI = VDD or GND IO = 0, VDD = 2.7V, RESET = GND IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC) IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC), CLK and CLK Switching 50% Duty Cycle. IO = 0, VDD = 2.7V, RESET = VDD, VI = VIH (AC) or VIL (AC), CLK and CLK Switching 50% Duty Cycle. One Data Input Switching at Half Clock Frequency, 50% Duty Cycle. VDD = 2.5V to 2.7V, IOH = -20mA VDD = 2.5V to 2.7V, IOH = 20mA VDD = 2.6V, TA = 25C, IOH = -20mA VDD = 2.6V, VI = VREF 310mV VICR = 1.3V, VI (PP) = 360mV VI = VDD or GND 7 7 2.5 2.5 20 20 4 3.5 3.5 pF Min. VDD 0.2 1.95 Typ. Max. 1.2 0.2 0.35 5 0.01 A/Clock MHz A/Clock MHz/Data Input A mA V Unit V V

IDT74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL I/O

INDUSTRIAL TEMPERATURE RANGE

OPERATING CHARACTERISTICS (PC1600-PC2700), TA = 25C(1)

Symbol VDD VDDQ VREF V TT VI VIH VIL VIH VIL VIH VIL VICR VI (PP) IOH IOL TA

NOTE: 1. The RESET input of the device must be held at VDD or GND to ensure proper device operation.

Parameter Supply Voltage Output Supply Voltage Reference Voltage (VREF= VDDQ/2) Termination Voltage Input Voltage AC High-Level Input Voltage AC Low-Level Input Voltage DC High-Level Input Voltage DC Low-Level Input Voltage High-Level Input Voltage Low-Level Input Voltage Common-Mode Input Range Peak-to-Peak Input Voltage High-Level Output Current Low-Level Output Current Operating Free-Air Temperature Data Inputs Data Inputs Data Inputs Data Inputs RESET RESET CLK, CLK CLK, CLK

Min. VDDQ 2.3 1.15 VREF 40mV 0 VREF+ 310mV VREF+ 150mV 1.7 0.97 360 40

Typ. 2.5 1.25 VREF

Max. 2.7 2.7 1.35 VREF+ 40mV VDD VREF 310mV VREF 150mV 0.7 1.53 20 20 +85

Unit V V V V V V V V V V V V mV mA C

OPERATING CHARACTERISTICS (PC3200), TA = 25C(1)

Symbol VDD VDDQ VREF V TT VI VIH VIL VIH VIL VIH VIL VICR VI (PP) IOH IOL TA

NOTE: 1. The RESET input of the device must be held at VDD or GND to ensure proper device operation.

Parameter Supply Voltage Output Supply Voltage Reference Voltage (VREF= VDDQ/2) Termination Voltage Input Voltage AC High-Level Input Voltage AC Low-Level Input Voltage DC High-Level Input Voltage DC Low-Level Input Voltage High-Level Input Voltage Low-Level Input Voltage Common-Mode Input Range Peak-to-Peak Input Voltage High-Level Output Current Low-Level Output Current Operating Free-Air Temperature Data Inputs Data Inputs Data Inputs Data Inputs RESET RESET CLK, CLK CLK, CLK

Min. VDDQ 2.5 1.25 VREF 40mV 0 VREF+ 310mV VREF+ 150mV 1.7 0.97 360 40

Typ. 2.5 1.3 VREF

Max. 2.7 2.7 1.35 VREF+ 40mV VDD VREF 310mV VREF 150mV 0.7 1.53 20 20 +85

Unit V V V V V V V V V V V V mV mA C

IDT74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL I/O

INDUSTRIAL TEMPERATURE RANGE

TIMING REQUIREMENTS OVER RECOMMENDED OPERATING FREE-AIR TEMPERATURE RANGE

PC1600 - PC2700 Symbol

CLOCK

PC3200 Min. 2.5 0.65 0.75 0.75 0.9 Max. 220 22 22 Unit MHz ns ns ns ns ns ns ns

Parameter Clock Frequency Pulse Duration, CLK, CLK HIGH or LOW Differential Inputs Active Time(1) Differential Inputs Inactive Time

(2)

Min. 2.5 Data Before CLK, CLK Data Before CLK, CLK 0.65 0.75 0.75 0.9

Max. 200 22 22

tw tACT tINACT tSU tH

Setup Time, Fast Slew Rate(3, 5) Setup Time, Slow Slew Rate(4, 5) Hold Time, Fast Slew Rate(3,5) Hold Time, Slow Slew Rate

(2,5)

NOTES: 1. Data inputs must be low a minimum time of tACT max., after RESET is taken HIGH. 2. Data and clock inputs must be held at valid levels (not floating) a minimum time of tINACT max., after RESET is taken LOW. 3. For data signal input slew rate is 1V/ns. 4. For data signal input slew rate is 0.5V/ns and <1V/ns. 5. CLK, CLK signal input slew rates are 1V/ns.

SWITCHING CHARACTERISTICS OVER RECOMMENDED FREE-AIR OPERATING RANGE (UNLESS OTHERWISE NOTED)

PC1600 - PC2700 Symbol fMAX tPDM tPDMSS tPHL Parameter CLK and CLK to Q CLK and CLK to Q (simultaneous switching) RESET to Q Min. 200 1.1 Max. 2.8 5 Min. 220 1.1 PC3200 Max. 2.4(1) 2.7 5 Unit MHz ns ns ns

NOTE: 1. 2.8ns for parts assembled and tested prior to WW14, 2004.

IDT74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL I/O

INDUSTRIAL TEMPERATURE RANGE

TEST CIRCUITS AND WAVEFORMS FOR PC1600-PC2700, VDD = 2.5V 0.2V FOR PC3200, VDD = 2.6V 0.1V

VTT RL = 50 From Output Under Test Test Point CL = 30 pF (see note 1)

Load Circuit

LVCMOS RESET Input tINACT IDD (see note 2)

VDD VDD/2 VDD/2 tACT 10% 90% 0V

Timing Input tPLH Output

VICR

VICR tPHL

VI(PP)

VOH VTT VTT VOL

Voltage and Current Waveforms Inputs Active and Inactive Times

Voltage Waveforms - Propagation Delay Times

LVCMOS RESET Input tW VIH Input VREF VREF Output VIL

VIH VDD/2 VIL tPHL VOH VTT VOL

Voltage Waveforms - Pulse Duration

Voltage Waveforms - Propagation Delay Times

Timing Input tSU Input VREF

VICR

VI(PP)

tN VIH VREF VIL

Voltage Waveforms - Setup and Hold Times

NOTES: 1. CL includes probe and jig capacitance. 2. IDD tested with clock and data inputs held at VDD or GND, and IO = 0mA. 3. All input pulses are supplied by generators having the following characteristics: PRR 10MHz, ZO = 50, input slew rate = 1 V/ns 20% (unless otherwise specified). 4. The outputs are measured one at a time with one transition per measurement. 5. VTT = VREF = VDDQ/2 6. VIH = VREF + 310mV (AC voltage levels) for differential inputs. VIH = VDD for LVCMOS input. 7. VIL = VREF - 310mV (AC voltage levels) for differential inputs. VIL = GND for LVCMOS input. 8. tPLH and tPHL are the same as tPD.

IDT74SSTV16857 14-BIT REGISTERED BUFFER WITH SSTL I/O

INDUSTRIAL TEMPERATURE RANGE

ORDERING INFORMATION

IDT XX SSTV XX Family Temp. Range XX XXXX Device Type Package

PA PAG 857

Thin Shrink Small Outline Package TSSOP - Green 14-Bit Registered Buffer with SSTL I/O

16 74

Double-Density 40C to +85C

CORPORATE HEADQUARTERS San Jose, CA 95138

for SALES: fax: 408-284-2775 www.idt.com

Vous aimerez peut-être aussi

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Lecture #1 Header Format: IP Version 6Document2 pagesLecture #1 Header Format: IP Version 6ScribdspacePas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5795)

- Internet: Chalmers University of TechnologyDocument7 pagesInternet: Chalmers University of TechnologyScribdspacePas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Plasma ParametersDocument4 pagesPlasma ParametersScribdspacePas encore d'évaluation

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Ee-Times ElectronicsDocument52 pagesEe-Times ElectronicsScribdspacePas encore d'évaluation

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- AGE10503, Gas ProcessingDocument34 pagesAGE10503, Gas ProcessingiranmortezaPas encore d'évaluation

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- SWP Grinder Bench AS520Document1 pageSWP Grinder Bench AS520Tosif AliPas encore d'évaluation

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Zener DiodeDocument3 pagesZener DiodeAde MurtalaPas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Cooling Coil SizingDocument4 pagesCooling Coil SizingRanu JanuarPas encore d'évaluation

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- AcetophenoneDocument1 pageAcetophenoneDinda Melissa ArdiPas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- LAPORAN PRAKTIK KERJA LAPANGAN - Id.enDocument25 pagesLAPORAN PRAKTIK KERJA LAPANGAN - Id.enAhmad JupriPas encore d'évaluation

- Jeppesen Charts LegendsDocument34 pagesJeppesen Charts LegendsFatih OguzPas encore d'évaluation

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- iQ-WEBX 6 2 3 Installation Guide INT EN - 001RDocument51 pagesiQ-WEBX 6 2 3 Installation Guide INT EN - 001RDoug KolkowPas encore d'évaluation

- R05411101 ImageprocessingandpatternrecognitionDocument4 pagesR05411101 ImageprocessingandpatternrecognitionSamiullah MohammedPas encore d'évaluation

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Irgb 4064 DPBFDocument11 pagesIrgb 4064 DPBFKrista TranPas encore d'évaluation

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Project Management Resume ExampleDocument2 pagesProject Management Resume ExampleGuino VargasPas encore d'évaluation

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Little Book of RubyDocument104 pagesLittle Book of RubynoboPas encore d'évaluation

- Hercules Engines c2 90d Engine Service ManualDocument7 pagesHercules Engines c2 90d Engine Service ManualRicardoPas encore d'évaluation

- Apple Value ChainDocument3 pagesApple Value ChainKeng Keat Lim100% (2)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Carbon Nanotube: Properties and ApplicationsDocument22 pagesCarbon Nanotube: Properties and ApplicationsmanuPas encore d'évaluation

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Datalogic Gryphon GM4100 User GuideDocument52 pagesDatalogic Gryphon GM4100 User Guidebgrabbe92540% (1)

- FrictionDocument4 pagesFrictionMuzafar ahmadPas encore d'évaluation

- Anandarup Ray CVDocument4 pagesAnandarup Ray CVsrihariPas encore d'évaluation

- Chap 3 HW AssignmentDocument3 pagesChap 3 HW AssignmentBren OngPas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- d1 - Evaluation - Justify Content Designs and Formats - FinalDocument5 pagesd1 - Evaluation - Justify Content Designs and Formats - Finalapi-466034593Pas encore d'évaluation

- Trebuchet Coursework For Website PDFDocument75 pagesTrebuchet Coursework For Website PDFkeraizPas encore d'évaluation

- Fire Risk of Cold Room PanelDocument6 pagesFire Risk of Cold Room Paneldarby1028Pas encore d'évaluation

- Cable Ties CatalogDocument60 pagesCable Ties CatalogRvPas encore d'évaluation

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Manesar AutomotiveDocument101 pagesManesar Automotiveshriya shettiwarPas encore d'évaluation

- Cmus Cheat SheetDocument1 pageCmus Cheat Sheetvoll macuserPas encore d'évaluation

- PTWDocument3 pagesPTWAngel Silva VicentePas encore d'évaluation

- TRM34 Preparation of Calculations Rev5Document5 pagesTRM34 Preparation of Calculations Rev5TuanPas encore d'évaluation

- PSD Coarse AggregateDocument3 pagesPSD Coarse AggregateMohd Syafiq AkmalPas encore d'évaluation

- PipeDocument30 pagesPipepudumai100% (1)

- ColorCells CC784 ProgrammingGuideDocument20 pagesColorCells CC784 ProgrammingGuideTom SteinhauerPas encore d'évaluation

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)