Académique Documents

Professionnel Documents

Culture Documents

74AC245

Transféré par

nevdullDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

74AC245

Transféré par

nevdullDroits d'auteur :

Formats disponibles

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

January 2008

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Features

ICC and IOZ reduced by 50% Non-inverting buffers Bidirectional data path A and B outputs source/sink 24mA ACT245 has TTL-compatible inputs

General Description

The AC/ACT245 contains eight non-inverting bidirectional buffers with 3-STATE outputs and is intended for bus-oriented applications. Current sinking capability is 24mA at both the A and B ports. The Transmit/Receive (T/R) input determines the direction of data flow through the bidirectional transceiver. Transmit (active-HIGH) enables data from A ports to B ports; Receive (activeLOW) enables data from B ports to A ports. The Output Enable input, when HIGH, disables both A and B ports by placing them in a HIGH Z condition.

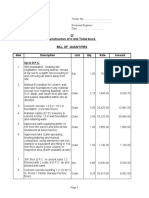

Ordering Information

Order Number

74AC245SC 74AC245SJ 74AC245MTC 74AC245PC 74ACT245SC 74ACT245SJ 74ACT245MSA 74ACT245MTC 74ACT245PC

Package Number

M20B M20D MTC20 N20A M20B M20D MSA20 MTC20 N20A

Package Description

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Device also available in Tape and Reel. Specify by appending suffix letter X to the ordering number. All packages are lead free per JEDEC: J-STD-020B standard.

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Connection Diagram

Logic Symbol

IEEE/IEC

Pin Description

Pin Names

OE T/R A0A7 B0B7

Description

Output Enable Input Transmit/Receive Input Side A 3-STATE Inputs or 3-STATE Outputs Side B 3-STATE Inputs or 3-STATE Outputs

Truth Table

Inputs OE

L L H

T/R

L H X

Outputs

Bus B Data to Bus A Bus A Data to Bus B HIGH-Z State

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 2

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 3

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

DC Electrical Characteristics for AC

TA = +25C Symbol

VIH

TA = 40C to +85C Units

V 2.1 3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 2.46 3.76 4.76 0.1 0.1 0.1 0.44 0.44 0.44 1.0 75 75 A mA mA A A V V V

Parameter

Minimum HIGH Level Input Voltage

VCC (V)

3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5

Conditions

VOUT = 0.1V or VCC 0.1V VOUT = 0.1V or VCC 0.1V IOUT = 50A

Typ.

1.5 2.25 2.75 1.5 2.25 2.75 2.99 4.49 5.49 2.1

Guaranteed Limits

3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 2.56 3.86 4.86

VIL

Maximum LOW Level Input Voltage

VOH

Minimum HIGH Level Output Voltage

VIN = VIL or VIH, IOH = 12mA VIN = VIL or VIH, IOH = 24mA VIN = VIL or VIH, IOH = 24mA(1) 0.002 0.001 0.001 VIN = VIL or VIH, IOL = 12mA VIN = VIL or VIH, IOL = 24mA VIN = VIL or VIH, IOL = 24mA(1) VI = VCC, GND VOLD = 1.65V Max. VOHD = 3.85V Min. VIN = VCC or GND VI (OE) = VIL, VIH; VI = VCC, GND; VO = VCC, GND IOUT = 50A

VOL

Maximum LOW Level Output Voltage

3.0 4.5 5.5 3.0 4.5 5.5

0.1 0.1 0.1 0.36 0.36 0.36 0.1

IIN(2) IOLD IOHD ICC

(2)

Maximum Input Leakage Current Minimum Dynamic Output Current(3) Maximum Quiescent Supply Current Maximum I/O Leakage Current

5.5 5.5 5.5 5.5 5.5

4.0 0.3

40.0 3.0

IOZT

Notes: 1. All outputs loaded; thresholds on input associated with output under test. 2. IIN and ICC @ 3.0V are guaranteed to be less than or equal to the respective limit @ 5.5V VCC. 3. Maximum test duration 2.0ms, one output loaded at a time.

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 4

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

DC Electrical Characteristics for ACT

Notes: 4. All outputs loaded; thresholds on input associated with output under test. 5. Maximum test duration 2.0ms, one output loaded at a time.

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 5

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

AC Electrical Characteristics for AC

TA = +25C, CL = 50pF Symbol

tPLH tPHL tPZH tPZL tPHZ tPLZ

TA = 40C to +85C, CL = 50pF Min.

1.0 1.0 1.0 1.0 2.0 1.0 2.0 1.0 1.0 1.0 1.5 1.0

Parameter

Propagation Delay, An to Bn or Bn to An Propagation Delay, An to Bn or Bn to An Output Enable Time Output Enable Time Output Disable Time Output Disable Time

VCC (V)(6)

3.3 5.0 3.3 5.0 3.3 5.0 3.3 5.0 3.3 5.0 3.3 5.0

Min.

1.5 1.5 1.5 1.5 2.5 1.5 2.5 1.5 2.0 1.5 2.0 1.5

Typ. Max.

5.0 3.5 5.0 3.5 7.0 5.0 7.5 5.5 6.5 5.5 7.0 5.5 8.5 6.5 8.5 6.0 11.5 8.5 12.0 9.0 12.0 9.0 11.5 9.0

Max.

9.0 7.0 9.0 7.0 12.5 9.0 13.5 9.5 12.5 10.0 13.0 10.0

Units

ns ns ns ns ns ns

Note: 6. Voltage range 3.3 is 3.3V 0.3V. Voltage range 5.0 is 5.0V 0.5V.

AC Electrical Characteristics for ACT

TA = +25C, CL = 50pF Symbol

tPLH tPHL tPZH tPZL tPHZ tPLZ

TA = 40C to +85C, CL = 50pF Min.

1.5 1.0 1.5 1.5 1.0 1.5

Parameter

Propagation Delay, An to Bn or Bn to An Propagation Delay, An to Bn or Bn to An Output Enable Time Output Enable Time Output Disable Time Output Disable Time

VCC (V)(7)

5.0 5.0 5.0 5.0 5.0 5.0

Min.

1.5 1.5 1.5 1.5 1.5 2.0

Typ.

4.0 4.0 5.0 5.5 5.5 5.0

Max.

7.5 8.0 10.0 10.0 10.0 10.0

Max.

8.0 9.0 11.0 12.0 11.0 11.0

Units

ns ns ns ns ns ns

Note: 7. Voltage range 5.0 is 5.0V 0.5V.

Capacitance

Symbol

CIN CI/O CPD

Parameter

Input Capacitance Input/Output Capacitance Power Dissipation Capacitance

Conditions

VCC = OPEN VCC = 5.0V VCC = 5.0V

Typ.

4.5 15.0 45.0

Units

pF pF pF

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 6

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 7

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Physical Dimensions (Continued)

Figure 2. 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions, specically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductors online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 8

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 9

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 10

74AC245, 74ACT245 Octal Bidirectional Transceiver with 3-STATE Inputs/Outputs

Physi4 aimensions

(Continued)

Figure 5. 20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specications do not expand the terms of Fairchilds worldwide terms and conditions, specically the warranty therein, which covers Fairchild products. Always visit Fairchild Semiconductors online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 11

TRADEMARKS Th

1988 Fairchild Semiconductor Corporation 74AC245, 74ACT245 Rev. 1.5.0

www.fairchildsemi.com 12

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Ad 22100Document12 pagesAd 22100nevdullPas encore d'évaluation

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Cds 1Document4 pagesCds 1nevdullPas encore d'évaluation

- AD7814Document8 pagesAD7814nevdullPas encore d'évaluation

- 74LVC1G04 1Document12 pages74LVC1G04 1nevdullPas encore d'évaluation

- sn54hc251 SPDocument23 pagessn54hc251 SPnevdullPas encore d'évaluation

- 699412fb TimerBloxDocument26 pages699412fb TimerBloxnevdullPas encore d'évaluation

- AD7314Document8 pagesAD7314nevdullPas encore d'évaluation

- Ad 22105Document8 pagesAd 22105nevdullPas encore d'évaluation

- LTC3588 1Document20 pagesLTC3588 1loliveir8556Pas encore d'évaluation

- 35882-Piezoelectric and Alternative Energy Harvesting Power SupplyDocument18 pages35882-Piezoelectric and Alternative Energy Harvesting Power SupplynevdullPas encore d'évaluation

- Hcf4017 Data Sheet 2Document8 pagesHcf4017 Data Sheet 2Filipe CoimbraPas encore d'évaluation

- Adt 7310Document24 pagesAdt 7310nevdullPas encore d'évaluation

- FeDocument32 pagesFenevdullPas encore d'évaluation

- 4071fc-Li-Ion-Poly Battery Charger System With Low Batt DiscoDocument18 pages4071fc-Li-Ion-Poly Battery Charger System With Low Batt DisconevdullPas encore d'évaluation

- Issue2Document1 pageIssue2nevdullPas encore d'évaluation

- Arduino Amani SRAM Expansion v1d0Document11 pagesArduino Amani SRAM Expansion v1d0nevdull100% (1)

- 43AR104 Antenna: Dimensions (In.)Document1 page43AR104 Antenna: Dimensions (In.)nevdullPas encore d'évaluation

- 59050Document1 page59050nevdullPas encore d'évaluation

- 8582 FDocument36 pages8582 FnevdullPas encore d'évaluation

- 4011 BDocument7 pages4011 BGayanDissanayakePas encore d'évaluation

- Cd4013 One-Shot and Latch Circuits: Size Document Number RevDocument1 pageCd4013 One-Shot and Latch Circuits: Size Document Number RevnevdullPas encore d'évaluation

- 4046Document14 pages4046dayvidmedeirosPas encore d'évaluation

- Mt8870, DTMF Decoder (Application Notes)Document24 pagesMt8870, DTMF Decoder (Application Notes)anmol9100% (1)

- Features Description: Ltc3536 1A Low Noise, Buck-Boost DC/DC ConverterDocument28 pagesFeatures Description: Ltc3536 1A Low Noise, Buck-Boost DC/DC ConverternevdullPas encore d'évaluation

- Features Description: Ltm8062/Ltm8062A 32V, 2A Μmodule Power Tracking Battery ChargersDocument24 pagesFeatures Description: Ltm8062/Ltm8062A 32V, 2A Μmodule Power Tracking Battery ChargersnevdullPas encore d'évaluation

- 3625f-High Efficiency 2-Cell Supercap ChargerDocument16 pages3625f-High Efficiency 2-Cell Supercap ChargernevdullPas encore d'évaluation

- 3212fb-RGB LED DriverDocument12 pages3212fb-RGB LED DrivernevdullPas encore d'évaluation

- Cmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LADocument14 pagesCmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LAnevdullPas encore d'évaluation

- Cmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LADocument14 pagesCmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LAnevdullPas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Volvo B13R Data SheetDocument2 pagesVolvo B13R Data Sheetarunkdevassy100% (1)

- Apst GraduatestageDocument1 pageApst Graduatestageapi-253013067Pas encore d'évaluation

- Brush Seal Application As Replacement of Labyrinth SealsDocument15 pagesBrush Seal Application As Replacement of Labyrinth SealsGeorge J AlukkalPas encore d'évaluation

- Part A Plan: Simple Calculater Using Switch CaseDocument7 pagesPart A Plan: Simple Calculater Using Switch CaseRahul B. FerePas encore d'évaluation

- Questionnaire: ON Measures For Employee Welfare in HCL InfosystemsDocument3 pagesQuestionnaire: ON Measures For Employee Welfare in HCL Infosystemsseelam manoj sai kumarPas encore d'évaluation

- ACC403 Week 10 Assignment Rebecca MillerDocument7 pagesACC403 Week 10 Assignment Rebecca MillerRebecca Miller HornePas encore d'évaluation

- Enumerator ResumeDocument1 pageEnumerator Resumesaid mohamudPas encore d'évaluation

- Dbms UPDATED MANUAL EWITDocument75 pagesDbms UPDATED MANUAL EWITMadhukesh .kPas encore d'évaluation

- Civil NatureDocument3 pagesCivil NatureZ_Jahangeer100% (4)

- Type BOQ For Construction of 4 Units Toilet Drawing No.04Document6 pagesType BOQ For Construction of 4 Units Toilet Drawing No.04Yashika Bhathiya JayasinghePas encore d'évaluation

- 7373 16038 1 PBDocument11 pages7373 16038 1 PBkedairekarl UNHASPas encore d'évaluation

- The Fundamentals of Investing PPT 2.4.4.G1Document36 pagesThe Fundamentals of Investing PPT 2.4.4.G1Lùh HùñçhòPas encore d'évaluation

- Hoja Tecnica Item 2 DRC-9-04X12-D-H-D UV BK LSZH - F904804Q6B PDFDocument2 pagesHoja Tecnica Item 2 DRC-9-04X12-D-H-D UV BK LSZH - F904804Q6B PDFMarco Antonio Gutierrez PulchaPas encore d'évaluation

- Auto Report LogDocument3 pagesAuto Report LogDaniel LermaPas encore d'évaluation

- 1.2 The Main Components of Computer SystemsDocument11 pages1.2 The Main Components of Computer SystemsAdithya ShettyPas encore d'évaluation

- Business Occupancy ChecklistDocument5 pagesBusiness Occupancy ChecklistRozel Laigo ReyesPas encore d'évaluation

- Chapter03 - How To Retrieve Data From A Single TableDocument35 pagesChapter03 - How To Retrieve Data From A Single TableGML KillPas encore d'évaluation

- Brother Fax 100, 570, 615, 625, 635, 675, 575m, 715m, 725m, 590dt, 590mc, 825mc, 875mc Service ManualDocument123 pagesBrother Fax 100, 570, 615, 625, 635, 675, 575m, 715m, 725m, 590dt, 590mc, 825mc, 875mc Service ManualDuplessisPas encore d'évaluation

- Spare Parts ManagementDocument21 pagesSpare Parts Managementdajit1100% (1)

- Troubleshooting For Rb750Glr4: Poe Does Not WorkDocument7 pagesTroubleshooting For Rb750Glr4: Poe Does Not Workjocimar1000Pas encore d'évaluation

- Alphacenter Utilities: Installation GuideDocument24 pagesAlphacenter Utilities: Installation GuideJeffersoOnn JulcamanyanPas encore d'évaluation

- CENT - Company Presentation Q1 2020 PDFDocument22 pagesCENT - Company Presentation Q1 2020 PDFsabrina rahmawatiPas encore d'évaluation

- Criminal Law I Green Notes PDFDocument105 pagesCriminal Law I Green Notes PDFNewCovenantChurchPas encore d'évaluation

- Andrews C145385 Shareholders DebriefDocument9 pagesAndrews C145385 Shareholders DebriefmrdlbishtPas encore d'évaluation

- MDC PT ChartDocument2 pagesMDC PT ChartKailas NimbalkarPas encore d'évaluation

- Unit List MUZAFFARPUR - Feb 18 PDFDocument28 pagesUnit List MUZAFFARPUR - Feb 18 PDFPawan Kumar100% (1)

- CasesDocument4 pagesCasesNaveen Stephen LoyolaPas encore d'évaluation

- Pharmaceutical Microbiology NewsletterDocument12 pagesPharmaceutical Microbiology NewsletterTim SandlePas encore d'évaluation

- SyllabusDocument9 pagesSyllabusrr_rroyal550Pas encore d'évaluation

- ADS Chapter 303 Grants and Cooperative Agreements Non USDocument81 pagesADS Chapter 303 Grants and Cooperative Agreements Non USMartin JcPas encore d'évaluation