Académique Documents

Professionnel Documents

Culture Documents

Mode Configuration

Transféré par

Dharsan SathyaDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Mode Configuration

Transféré par

Dharsan SathyaDroits d'auteur :

Formats disponibles

8/10/2012

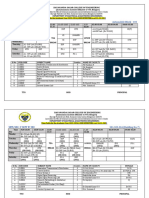

8086 Pin diagram

Pin Description

AD15-AD0 Pin no. 2-16, 39 Type I/O

8086 is a 40 pin DIP using MOS t echnology . It has 2 GNDs as cir cu it complexity dem ands a large amount of current flowing through the circuits , and mult iple grounds help in dis sipat ing the accumul ated hea t et c . 8086 works on two modes of operation name ly, Maximum Mode and Minimum Mode.

A17/S4 0 (LOW) 0 1(HIGH)

A16/S3 0 1 0

Characteristics Alternate Data Stack Code or None

Ad dress Da ta bu s: These lines constitute the time multiplexed memory/ IO address (T 1) and data (T 2, T 3, T W , T 4) bus. A0 is analogous to BHE* for the lower byte of the data bus, pins D7D0. It is low when a byte is to be transferred on the lower portion of the bus in memory or I/O operations. Eight bit oriented devices tied to the lower half would normally use A0 to condition chip select functions. These lines are active HIGH and float to 3state OFF during interrupt acknowledge and local bus hold acknowledge .

1

S6 is 0 (LOW)

Data

This information indicates which relocation register is presently being used for data accessing. These lines float to 3-state OFF during local bus hold acknowledge .

Power Connections

GND 1 40 VCC

Address Lines

A14 2 3 4 5 6 7 8 9 10 37

A 17

Status Pins S0-S7

39 A15

A 16

8086

CLK GND 19 20

Pin Description: GND Pin no. 1, 20 Ground CLK Pin no. 19 Type I Clock: provides the basic timing for the processor and bus controller. It is asymmetric with a 33% duty cycle to provide optimized internal timing. VCC Pin no. 40 VCC: +5V power supply pin

A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

38 37

S3 S4 S5 S6 S7

S2 S1

38

36 35

8086

36 35

8086

A 18 A 19

34 28 27 26

(M/IO )

(DT /R )

11

12 13 14 15 16

DEN) S0 (

Continued

Continued

Address/ Data Lines

Pin Description

AD14

AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 2 3 39 AD15

4

5 6 7 8 9 10 11 12 13 14 15 16

S 2 , S1 , S 0

- Pin no. 26, 27, 28 Type O

A19/S6, A18/S5, A17/S4, A16/S3 Pin no. 35-38 Type O

8086

Continued

Ad dress / Status: Durin g T 1 these are the four most significant address lines for memory operations. During I/O operations these lines are low. During memory and I/O operations, status information is available on these lines during T 2, T 3, T W and T 4. The status of the interrupt enable FLAG bit (S5) is updated at the beginning of each CLK cycle. A17/S4 and A16/S3 are encoded as shown.

Continued

Status: act ive dur ing T4, T1 and T2 an d is r etur ned to th e pas sive state (1,1,1) du ring T3 o r du ring TW wh en READY is HIGH. This status i s use d by th e 8 288 Bu s Contr ol ler to generate al l memory and I/O access contro l signa ls. Any cha nge by , or dur ing T4 is used t o i ndicate t he b egin ning of a b us cycle an d the retur n to the pas sive stat e in T3 o r TW i s us ed to ind icate t he end of a b us cycle.

Continued

8/10/2012

Min mode signals

These signals float to 3-state OFF in hold acknowledge . These status lines are encoded as shown. S2* S1* S0* Characteristics 0(LOW) 0 0 Interrupt acknowledge 0 0 1 Read I/O Port 0 1 0 Write I/O Port 0 1 1 Halt 1(HIGH) 0 0 Code Access 1 0 1 Read Memory 1 1 0 Write Memory 1 1 1 Passive

S5

S6

----- Value of Interrupt Enable flag ----- Always low (logical) indicating 8086 is on the bus. If it is tristated another bus master has taken control of the system bus. ----- Used by 8087 numeric coprocessor to determine whethe r the CPU is a 8086 or 8088

33 31 30 29

VCC MN/ MX HOLD HLDA

WR

M/I O

DT/ R

8086

28 27

S7

26

DEN

ALE

INTA

25

24

Continued

Continued

Status Details

S2

0 0

Interrupts

S 0 Indication

Interrupt Acknowledge

Pin Description: NMI Pin no. 17 Type I Non Maskable Interrupt: an edge triggered input which causes a type 2 interrupt. A subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is not maskable internally by software. A transition from a LOW to HIG H initiates the interrupt at the end of the current instruction. This input is internally synchronized.

Continued

Pin Description

HOLD, HLDA Pin no. 31, 30 Type I/O HOLD: indicates that an other ma ster is re que sting a local bus hold. To be ackno wl edged, HOLD mu st be act ive HIGH. The proces sor rece iving t he ho ld req uest wi ll is sue HLDA (HIGH) as an ackno wl edgemen t in th e m id dle of a T1 cl ock cycle. Simulta neou s with the is sua nce of HLDA t he p roces sor will float the l ocal b us a nd co ntro l l ine s. Afte r HOLD i s d etected a s b eing LOW , the pr ocess or wi ll LOWer the HLDA, an d whe n t he proces sor needs to run anot her cycle, i t w il l agai n dr ive t he local bus and control lines. The same r ule s a s app ly regard ing w hen th e local bus wi ll be released. HOLD is not an asynchr ono us i nput. Exte rnal sy nchron izat ion shou ld be pr ovide d if t he system can not oth erw is e guar antee the setup time. Continued

S1

0

0

0 0 1 1

0

1 1 0 0

1

0 1 0 1

Read I/O port

Write I/O port Halt Code access Read memory

NMI 17

8086

I NTR

18

1

1

1

1

0

1

Write memory

Passive

Continued

S4 0 0 1 1

S3 0 1 0 1

Indications Alternate data Stack Code or none Data

Continued

INTR Pin No. 18 Type I Interrupt Request: is a level triggered input which is sampled during the last clock cycle of each instruction to determine if the processor s hould enter into an interrupt acknowledge operation. A subroutine is vectored to via an interrupt vector lookup table located in system memory. It can be internally masked by software resetting the interrupt enable bit. INTR is internally synchronized. This signal is active HIGH.

WR* - Pin no. 29 Type O Write: i ndicate s that the proces sor is pe rformi ng a wr ite memory or w rite I/O cycle, d epen ding o n th e s tate of the M /IO* signa l. WR* i s act ive fo r T 2, T3 and TW of any wri te cycle. It i s act ive LO W , and floats to 3-state OFF in local bus hold acknowledge. M/IO* - Pin no. 28 type O Status line: logically equ ivale nt to S 2 in th e maximum m ode. It is used to d ist ingu is h a mem ory acces s from a n I/O acces s. M/IO* becomes va lid in the T4 preced ing a bu s cycle and remai ns va lid unti l t he fina l T4 of t he cycle (M=HIGH), IO=LOW). M/IO* fl oats to 3-state OFF in local bus hold acknowledge.

Continued

8/10/2012

DT/R* - Pin no. 27 Type O Data Transm it / Receive: need ed in mi nim um system that de sir es to use an 828 6/82 87 data bu s t ransce iver. It i s use d to contro l the directi on of data flo w thr ough the tra nsceive r. Log ically DT/R* is equiva lent to S 1* i n t he maximum mo de, a nd it s t iming is th e same as f or M /IO*. (T=HIGH, R=LOW). T hi s s ignal f loat s to 3-stat e OFF in local bus hold acknowledge. DEN* - Pin no. 26 Type O Data Enable: p rovi ded a s an o utpu t enab le for the 8 286/ 8287 in a minim um system wh ich use s t he tra nsceive r. DEN* i s active LOW duri ng each m emory an d I/ O acces s and for INTA cycles. F or a read or INTA* cycle i t is act ive fr om the m idd le of T2 u nti l the m idd le of T4, w hil e for a wr ite cycle it is active fro m the beg in ning of T 2 unt il the mid dle of T4. DEN* float s to 3-stat e OFF in local b us ho ld acknowledge. Continued

Pin Description: RQ*/GT0*, RQ*/GT1* - Pin no. 30, 31 Type I/O Reque st /G rant: p ins are use d by o ther local bu s mast ers t o force the proces sor t o relea se the local bu s at the en d of the pr oces sors current bus cycle. Each p in is b idir ection al wit h RQ*/GT 0* having higher pri ority tha n RQ* /GT1*. RQ* /GT* ha s a n inte rnal p ul l up resistor s o may be left uncon nected. T he req uest /grant se que nce is as follows:

Continued

LOCK* - Pin no. 29 Type O LOCK* : outp ut ind icates that othe r system bu s ma sters are not to gain control of the syst em b us w hile LOC K* is active LOW . The LOCK* s ignal is activate d by th e LOCK prefix inst ructi on an d rema ins active un til the compl etio n of th e next i nstr uctio n. Thi s s ignal is act ive LOW , and floats to 3-state OFF in hold acknowledge. QS1, QS 0 Pin no. 24, 25 Type O Queue Statu s: t he qu eue stat us i s vali d dur ing th e CLK cycle after which the queue operation is performed. QS 1 and QS 0 prov ide statu s to all ow exte rnal tracking of the inte rnal 8086 instruction queue.

Continued

ALE Pin no. 25 Type O Addr es s Latch Enab le: provi ded by the proce ss or t o latch the addres s i nto th e 8282 /8283 a ddre ss latch. It is a HIGH pul se active during T1 of any bus cycle. Note that ALE is never floated. INTA* - Pin no. 24 Type O INTA* i s u sed as a read str obe for int erru pt ackno wledge cycles. It is active LOW d uri ng T2, T3 a nd TW of each inte rrup t ackn ow ledge cycle.

1. A pu lse of 1 CLK w ide from a noth er loca l bu s m aster ind icates a local bus request (hold) to the 8086 (pulse 1)

QS1 0(LOW) 0

QS0 0 1

Characteristics No operation First Byte of Op Code from Queue

2. During a T4 or T1 clock cycle, a p ulse 1 CLK w ide fr om the 8 086 to the requ est ing ma ster ( pul se 2), ind icates t hat t he 80 86 ha s allo wed the local bu s t o f loat an d t hat it w ill e nter the ho ld acknowle dge s tate at t he next CLK. Th e CPUs bu s interface un it is disconn ected logica lly f rom the local b us du ring ho ld acknowledge. 3. A pu lse 1 CLK wid e from th e req uest ing ma ster ind icates to t he 8086 (pu lse 3) that t he ho ld req uest is a bout t o en d and that the 8086 can reclaim the local bus at the next CLK. Continued

1 (HIGH)

1

0

1

Empty the Queue

Subsequent byte from Queue

Max mode signals

33 31 GND

RQ/ GT0

Common Signals

Each master-ma ster exchange of the loca l b us is a seq uence of 3 pul ses. There mu st be o ne dead CLK cycle after each bu s exchang e. Pulses are active LOW . If the requ est i s ma de wh ile t he CPU i s perform ing a m emory cycle, it wi ll re lea se the l ocal bu s du ring T4 of the cycle wh en al l the following conditions are met: Request occurs on or before T2. Current cycle is not the low byte of a word (on an odd address) C urrent cycle i s no t the fir st ackno wle dge of an i nterr upt acknowledge sequence. A locked instruction is not currently executing.

Continued Continued Continued

30

29

RQ/ GT 1

LOCK

S2 S1 S0

8086

28 27 26 25 24

QS0

QS1

8/10/2012

Pin Description: RD* - Pin no. 34 , Type O Read: R ead strobe indica tes that the processor is performing a memory of I/O read cycle, depending on the sta te of the S2 pin. This s ignal is used to re ad devices which reside on the 8086 local bus. RD* is act ive LOW during T2 , T3 and TW of any read cycle , and is guarante ed to rema in HIGH in T2 until the 8086 loc al bus has floated . This signal floats to 3-state OFF in hold acknowledge. READY Pin no . 22, Type I READY: is the acknowledgement from the addressed memory or I/O devic e tha t it will complet e the da ta transfer. The READY signal from memory / IO is synchronized by the 8284A Clock Generator to form R EADY. This signal is ac tive HIGH. The 8086 READY input is not synchronized . Correct opera tion is no t guaranteed if the setup and hold times are not met. Continued

Read Cycle timing Diagram for Minimum Mode

MN/MX* - Pin no. 33 Type - I Minimum / Maxim um: indicates what mode the proces sor is to operate in. If the local bus is idle when the request is made the two possible events will follow: Local bus will be released during the next clock. A memory cycle will start within 3 clocks. Now the four rules for a currently active memory cycle apply with condition number 1 already satisfied.

Minimum Mode 8086 System

MRD MW R IORD IOW R

DMUX

TEST* - Pin No 23 Type I TEST* : input is examined by the Wait instruct ion . If the TEST* input is LOW execution cont inues, otherwis e the processor wai ts in an id le st ate . This input is synchronized internally during each clock cycle on the leading edge of CLK. RESET Pin no . 21 Type I Rese t: cause s the processor to imm edia tely term inate its present ac tivi ty . The signal must be ac tive HIGH for at l east four clock cycl es. It r estar ts execution, as described in the instruction s et descript ion, when R ESET r eturns LOW. RESET is internally synchronized . Continued

In the bus timing diagram, data transmit / receiv e signal goes low (RECEIV E) for Read operation. T o validate th e data, DEN* signal goes low. The Address/ Status bus carries A16 to A19 address lines during BHE* (low) and fo r the rem aining time carries S tatus information. Th e Address/Data bus carries A0 to A15 address information during ALE going high and for th e remaining tim e it carri es data. Th e RD* line going low indicates that this is a Read operation. The cu rv ed arrows indicate the relationship Continued between valid data and RD* signal.

The TW is Wait time n eeded to synchronize the f ast processor wi th slow memory etc. The R eady pin is check ed to see wh eth er any p eripheral needs more time for data transmission.

Write Cycle timing Diagram for Minimum Operation

BHE*/S7- Pin No . 34 Type O Bus H igh Enabl e / Status: During T1 the Bus High Enable signal (BHE*) should be used to enable da ta onto the most signific ant ha lf of the da ta bus, pins D15-D8. Eight bit oriented devi ces tied to the upper half of the bus would normally use BHE* to condition chip se le ct functions. BHE* is LOW during T1 for read, wri te, and interrupt acknowledge cyc les when a byte is to be transferred on the high portion of the bus. The S,7 sta tus informat ion is ava ilab le during T2, T3 and T4. The signal is ac tive LOW and floats to 3-stat e OFF in hold. I t is LOW during T1 for the first interrupt acknowledge cycle. BHE* 0 A0 0 Characteristics Whole word

0

1 1

1

0 1

Upper byte from / to odd address

Lower byte from / to even address None

Continued

A minimum mode of 8086 configuration depicts a stand alone system of computer where no other processo r is connected. This is similar to 8085 block diagram with the following difference. The Data transc eiv er block which helps the signals traveling a longer distanc e to get boosted up. Two con trol signals data transmit/ rec eiv e are connected to th e direction input of transceiv er (Transmitter/Rec eiver) and DEN* signal works as enable for this block.

8/10/2012

RQ*/ GT* Timings in Maximum Mode

This is the same as Read cycle Timing Diagram exc ept that th e DT/R* line goes high indicating it is a Data

In the maxim um mo de of op erati on of 808 6, wh erei n e ither a numer ic coproce ss or of th e type 80 87 or a noth er proces sor i s interfaced with 8 086. The Mem ory, Addre ss Bus, Data Bu se s a re shared re source s b etwee n t he t wo proce ssor s. The contr ol sig nal s for Maxim um m ode of o perat ion are ge nerated by the Bu s Contr oll er ch ip 8 788. Th e th ree statu s o utput s S0*, S 1*, S2* fr om the pr ocess or are in put t o 878 8. The o utpu ts of the bus contro lle r are the Contr ol S ignal s, name ly DEN, DT/R*, IORC *, IOWTC*, MWTC *, MRD C*, ALE etc. Th ese contro l signa ls perfo rm th e sa me task a s t he m in imum mod e o perat ion. H owever th e DEN i s a n act ive HIGH signa l which ha s to be converte d t o active LOW by mea ns of a n inverter.

Transmission operation for the processor to memo ry /

peripheral. Again DEN * line goes low to validate data and WR* line goes low, indicating a Write operation.

Request / Grant pin may appear that both signals are active low. But in reality, Request signal goes low first (input to processor), and then the processor grants the request by outputting a low on the same pin.

Memory Read timing in Maximum Mode

Bus Request & Bus Grant Timings in Minimum Mode System

The HO LD and HL DA timing diagra m indicates in Time Space H OLD (input) occu rs fi rst and then the p rocessor outputs HLDA (Hold Acknowledge).

the data bus .

Here the maxim um mo de write s ignals are s hown. Pleas e note tha t the T s tates corres pond to t he ti me during whic h DEN* is LOW, WRI TE Control goes LOW , DT/R* is HI GH and da ta ou tpu t in avai lable from the proces s or on

Maximum Mode 8086 System

Memory Write Timing in Maximum Mode

Vous aimerez peut-être aussi

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- WISOLAppNote WSSFM10R HW Design Guide R03 170320 PDFDocument6 pagesWISOLAppNote WSSFM10R HW Design Guide R03 170320 PDFRegis DantasPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- A Planar Waveguide Nd:YAG Laser Using Active Q-Switching of A Hybrid Unstable ResonatorDocument10 pagesA Planar Waveguide Nd:YAG Laser Using Active Q-Switching of A Hybrid Unstable ResonatorzaidlateefPas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Exploded View Part ListDocument9 pagesExploded View Part ListJosé MacedoPas encore d'évaluation

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- How To Perform iSTEP UPDATES On NBTEVO PDFDocument22 pagesHow To Perform iSTEP UPDATES On NBTEVO PDFkenjyaitc100% (1)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Analysis and Detection of Single-Line-ground Fault in Ungrounded Solar PlantDocument4 pagesThe Analysis and Detection of Single-Line-ground Fault in Ungrounded Solar PlantGundeboyina GopiPas encore d'évaluation

- A Single-Switch Transformerless DC-DC Converter With Universal Input Voltage For Fuel Cell Vehicles Analysis and DesignDocument12 pagesA Single-Switch Transformerless DC-DC Converter With Universal Input Voltage For Fuel Cell Vehicles Analysis and Designreza mohajeryPas encore d'évaluation

- Modbus GWDocument2 pagesModbus GWKhaled KadryPas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Arduino-Based Automatic Sliding Door DesignDocument8 pagesArduino-Based Automatic Sliding Door DesignNizar Noer InsanPas encore d'évaluation

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Transformer: Professor Mohamed A. El-SharkawiDocument87 pagesTransformer: Professor Mohamed A. El-SharkawiImran AbdullahPas encore d'évaluation

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Mi 10T Lite: User GuideDocument10 pagesMi 10T Lite: User GuideMUHAMMED RASHIDPas encore d'évaluation

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Transformer Protection 2012-1Document43 pagesTransformer Protection 2012-1muaz_aminu1422100% (2)

- Digital Predistortion For RF Power AmplifiersDocument4 pagesDigital Predistortion For RF Power AmplifiersxinlivuPas encore d'évaluation

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- (2nd Sem - Eee Mid Semester 2022 Question PaperDocument2 pages(2nd Sem - Eee Mid Semester 2022 Question PaperProf. Shyam KumarPas encore d'évaluation

- 1-Port Gigabit GPON/EPON Wireless-N ONU Router: Model No: iB-FONG11GWDocument1 page1-Port Gigabit GPON/EPON Wireless-N ONU Router: Model No: iB-FONG11GWFilesPas encore d'évaluation

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- HP 11000 G2 Series Racks - QuickSpecsDocument18 pagesHP 11000 G2 Series Racks - QuickSpecsFelipe AraujoPas encore d'évaluation

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- Radio WaveDocument35 pagesRadio WaveMuruganPas encore d'évaluation

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- Unit: Data Link Layer (Marks 5) Computer Network BSC 6 Semester Sub: Computer Science (General) Data Link LayerDocument3 pagesUnit: Data Link Layer (Marks 5) Computer Network BSC 6 Semester Sub: Computer Science (General) Data Link LayerNur ZuraidaPas encore d'évaluation

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- 8300 Datasheet - ModuleDocument6 pages8300 Datasheet - Module김경우Pas encore d'évaluation

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- CPI 400W KU Band AmpDocument2 pagesCPI 400W KU Band Amp8dfwgfj4kyPas encore d'évaluation

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- TestcieeDocument7 pagesTestcieefallonPas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- KNX ArchitectureDocument1 pageKNX ArchitectureNoman KhalidPas encore d'évaluation

- Two Stage AmplifierDocument8 pagesTwo Stage AmplifierTharakaKaushalyaPas encore d'évaluation

- Rip and Play Music Instantly: With USB Rip-AllDocument2 pagesRip and Play Music Instantly: With USB Rip-AllMircea FrantPas encore d'évaluation

- Design of A 10 W High-Efficiency Balanced Power Amplifier Using A Combination of Load-Pull and Load-Line Methods For ISM BandDocument13 pagesDesign of A 10 W High-Efficiency Balanced Power Amplifier Using A Combination of Load-Pull and Load-Line Methods For ISM BandmahdiPas encore d'évaluation

- Cyient Transmit and Receive Module For Radar SystemsDocument4 pagesCyient Transmit and Receive Module For Radar SystemsPercy100% (1)

- Channel Estimation PDFDocument4 pagesChannel Estimation PDFHuy Nguyễn QuốcPas encore d'évaluation

- (Catalogue) Mikro ReactorDocument4 pages(Catalogue) Mikro ReactorayuPas encore d'évaluation

- Sensors: Measuring Torque and Temperature in A Rotating Shaft Using Commercial SAW SensorsDocument23 pagesSensors: Measuring Torque and Temperature in A Rotating Shaft Using Commercial SAW Sensorslaugusto7Pas encore d'évaluation

- V SEMESTER Class TT - 2023-24Document2 pagesV SEMESTER Class TT - 2023-24Pranjal singhPas encore d'évaluation

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Everyday Electronics 1972-02Document60 pagesEveryday Electronics 1972-02Toni TursićPas encore d'évaluation

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)