Académique Documents

Professionnel Documents

Culture Documents

Sistemas Secuenciales

Transféré par

Marco Quispe PalaciosTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Sistemas Secuenciales

Transféré par

Marco Quispe PalaciosDroits d'auteur :

Formats disponibles

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

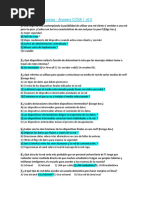

SISTEMAS SECUENCIALES Definiciones En un sistema secuencial las salidas dependen de las entradas presentes y de los valores de las entradas anteriores. En un sistema combinacional las salidas slo dependen de las entradas presentes o actuales. En caso de existir mltiples variables lgicas de entrada, al valor de la combinacin(o vector) se lo denomina palabra de entrada; y ms simplemente: entrada. Los distintos valores que toma la entrada, a medida que transcurre el tiempo, se denomina secuencia temporal de entrada. En forma anloga se define una secuencia temporal de salida. Grficamente, para un sistema combinacional con n entradas y m salidas, se tiene el siguiente diagrama en bloques: Entonces, en un sistema combinacional, la palabra de salida es una funcin booleana de la palabra de entrada: Sj (t) = fj (e1(t), e2(t), , en(t) ) para j = de 1 a m. Cuando se deja explcita la variacin temporal, se desea destacar que se est describiendo una secuencia de valores. Una secuencia de valores puede anotarse: xi = {xi(t0), xi(t1), xi(t2), ..., xi(tn)...} Si: ti = t0 + i t, los valores de la secuencia se dan a intervalos regulares de tiempo. Si t es constante, se denomina secuencia sincrnica al caso anterior. Si t es variable, entonces ti describe los valores que toma una variable aleatoria; en este caso se dice que la secuencia es asincrnica. Observaciones. Debido a que las variables xi, toman valores discretos (0 y 1), se suele considerar al tiempo como una variable discreta. Por ejemplo, podra ser de inters conocer el tiempo cuando se producen cambios (en secuencias asincrnicas) o a intervalos regulares (intervalos de reloj, en secuencias sincrnicas). Ejemplos de Secuencias. a) Secuencia sincrnica de niveles. Se dice que la seal xn es una secuencia sincrnica de niveles, con respecto a un reloj, ya que sta slo cambia en cantos de bajada(o de subida) del reloj, y adems permanece constante el nivel de la seal entre cantos de bajada(o de subida) del reloj. b) Secuencia sincrnica de pulsos. xp es una secuencia sincrnica de pulsos. Los valores de la secuencia se interpretan cuando el reloj est alto. No toma valores entre pulsos. c) Secuencia asincrnica de niveles

Los intervalos ti tienen una duracin aleatoria. d) Secuencia Asincrnica de pulsos. Los pulsos, de igual ancho, presentan con intervalo aleatorio. 9.3. Modelo Secuencial

Ing. Luis Pacheco Cribillero

se

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

En un sistema combinacional, la salida es generada simultneamente; es decir, en forma concurrente o paralela y slo depende de la entrada. Los cambios individuales de cada una de las seales se producen en una secuencia temporal. Tambin se dice serial en el tiempo. En un sistema secuencial, para poder generar la salida en un tiempo dado, es preciso conocer valores previos de algunas variables. No bastan los valores presentes de la entrada. Es decir, debe almacenarse informacin concerniente a los valores de las entradas pasadas, para poder generar la salida a partir de la entrada presente y los valores almacenados. La informacin anteriormente mencionada, se almacena en estados internos. Los valores que deben registrarse para recordar la situacin, debida a los valores de las entradas pasadas, se almacena en variables de estado. Podemos considerar que las variables de estado son salidas de elementos con memoria (flip-flops, registros, latches, retardos). En cualquier instante, una mquina secuencial est en uno de un nmero finito de estados; stos quedan determinados por el valor de las variables de estado. Por ejemplo, si hay cuatro estados, se requieren 2 variables de estado para registrar que el sistema se encuentra en uno de los cuatro estados posibles: 00, 01, 10, 11. La secuencia de estados internos resume la historia temporal del sistema secuencial. A veces se emplea el trmino: estado total, para referirse a la combinacin de los estados internos con la entrada. Figura.- Modelo mquina secuencial. Si se aplica una secuencia de entrada, la mquina generar una secuencia de salida, y pasar por una secuencia de estados internos. La memoria queda modelada por: Es decir, en el futuro, y tomar el valor actual de Y. Puede representarse la secuencia de valores temporales en trminos de nmeros enteros, segn: La memoria debe ser capaz de almacenar los Yk(j) y sostener estos valores durante el intervalo j+1. En el modelo planteado, la salida y el prximo estado interno son funciones del estado total. A estas mquinas se las denomina determinsticas. Es decir, con n entradas, m variables de estado, y p variables de salida, se tienen: zi= Ci( x1,.. xn, y1,.. ym) con i desde 1 a p. Yk= Sk( x1,.. xn, y1,.. ym) con k desde 1 a m. Las funciones Ci son combinacionales. Las funciones Sk son secuenciales. Ecuaciones que indican que tanto la salida como el prximo estado dependen de la entrada y el estado actual. Eliminando la variable Y, se logra: yk(j+1) = Sk( x1,.. xn, y1,.. ym) Donde las variables x1,.. xn, y1,.. ym son evaluadas en el instante j. Ecuacin de recurrencia que permite determinar el prximo estado, a partir de la entrada y el estado presente. Para resolverla, es preciso conocer el valor del estado inicial y la secuencia de entrada a partir del tiempo inicial. Grficamente: Para conocer y(1) se requiere conocer y(0) y x(0). Para conocer y(2) se requiere conocer y(1) y x(1). Para conocer y(3) se requiere conocer y(2) y x(2). Y as sucesivamente.

Ing. Luis Pacheco Cribillero

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

Si el prximo estado es igual al actual y la entrada se mantiene constante, se dice que es un estado estable: Y(j+ 1)= y(j) Si el prximo estado es diferente al actual, se dice que habr una transicin o cambio de estado. Ese estado actual se denomina inestable: Y(j + 1) y(j) Lo anterior implica que una de las variables de estado conmuta, o cambia, su valor lgico. Los elementos de almacenamiento pueden ser simplemente lneas de realimentacin, en este caso se tienen sistemas secuenciales asincrnicos. En sistemas secuenciales sincrnicos los elementos de almacenamiento sern flip-flops, comandados por un reloj. Figura. Compuertas y flip-flops. La lgica combinacional puede ser separada en dos sistemas, uno que implementa la funcin para la lgica de salida (la funcin C) y otro que calcula el prximo estado (la funcin S). En el siguiente diagrama se representa un sistema secuencial sincrnico, en el que se indica una seal de reloj, para el dispositivo que registra o memoriza el estado presente o actual. Figura. Modelo de Mealy. Representacin de mquinas secuenciales Se entiende por representacin la descripcin de cmo se pasa de un estado a otro, debido a los cambios de las entradas. Las representaciones deben describir en forma precisa y completa a la mquina. Adems, deben ser adecuadas para una manipulacin formal. Modelo de Mealy Es un modelo secuencial en el cual la salida est asociada a las transiciones entre estados. Las salidas y el prximo estado cambian instantneamente con los cambios de las entradas. El diagrama se ilustr antes. i) Diagrama de estados de Mealy Los estados se representan mediante crculos, y por lneas rotuladas y orientadas las transiciones. El rtulo indica la entrada y la salida que provoca la transicin. Se separan con una pleca (slash, en ingls). En general se lee: Estando en el estado y, cuando llega la entrada x se pasa al estado Y, con salida z. ii) Figura Tabla de transicin de estados de Mealy. A esta tabla tambin se la llama matriz de transiciones. En las columnas se indican los diferentes valores que puede tomar la entrada. En los renglones se indican los estados internos actuales. En cada casillero de la matriz, se indica el prximo estado y la salida asociada. Esquemticamente: Las representaciones son equivalentes, puede lograrse una a partir de la otra; y viceversa. Es decir, la matriz de transiciones y el diagrama de estado suministran la misma informacin. Pueden emplearse tablas separadas para Y y para z. Figura.- Matriz de transiciones y matriz de salida. Modelo de Moore Modelo secuencia en el cual la salida slo est asociada al estado presente. Las salidas cambian slo en cantos de sincronizacin del reloj. Figura.

Ing. Luis Pacheco Cribillero

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

i) Diagrama de estados Diagrama de estados de Moore. Estando en estado y, con salida z1; cuando ocurre la entrada x se pasa al estado Y, con salida z2. La salida no cambia en la transicin. Por esta razn, las salidas se asocian a los estados. ii) Tabla de transiciones El modelo de Mealy es ms general que el de Moore. Este ltimo es un caso particular del primero. Las representaciones anteriores permiten analizar una mquina dada. Entendemos por anlisis, al proceso de determinar el funcionamiento de la mquina a partir del diagrama de estados. El anlisis de una mquina secuencial nos permite obtener la secuencia de salida a partir de la secuencia de entrada; tambin determinar la secuencia de estados a partir de la secuencia de entrada. Ejemplo 1 Determinar la secuencia de salida para la siguiente matriz de transiciones: Estando en A, con entrada 0, se pasa al estado D con salida 0. Estando en D, con entrada 1, se pasa al estado B con salida 1. Figura. Secuencia de salida. La mquina de Mealy anterior, se comporta como un generador de secuencias. Figura.- Esquema generador de secuencias. Se ingresa la secuencia de valores: x0, x1, x2,.. y se genera la secuencia de valores de salida: z0, z1, z2, z3,... Puede obtenerse el diagrama de estados, a partir de la matriz de transiciones: Figura.- Diagrama de Estados del ejemplo 1. Ejemplo 2. Determinar la secuencia de estados para la siguiente mquina de Moore: Con estado inicial C y secuencia de entrada: {0,0,0,1,1,1,...} Se tiene: Figura. Secuencia salida ejemplo Las mquinas de Moore suelen emplearse como reconocedores de secuencias. Es decir, que entreguen una determinada salida cuando ocurre una determinada secuencia en la entrada. Puede obtenerse la tabla de transiciones y la tabla con la lgica de salida, a partir del diagrama de estados:

Ing. Luis Pacheco Cribillero

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

Figura. Tabla de transiciones ejemplo Existen procedimientos sistemticos para representar un diagrama de Mealy mediante uno de Moore. Debe considerarse la representacin de Mealy como ms general que la de Moore. Ejemplo. Detectar la secuencia 110 cada vez que se presente: El diagrama de Moore, requiere 4 estados: Diagrama de Moore ejemplo.

El diagrama de Mealy requiere tres estados: Figura.- Diagrama de Mealy ejemplo. Algunas observaciones sobre las representaciones: Las salidas de Moore son sincrnicas con el reloj, las de Mealy son asincrnicas. Es decir, se genera el prximo estado y se genera la salida sin esperar el canto del reloj. En las de Mealy, las salidas pueden cambiar inmediatamente cuando ocurre un cambio en las entradas. Si esto no se desea, pueden sincronizarse las salidas asincrnicas, de una mquina de Mealy, pasndolas por un flip-flop. En general los modelos de Mealy pueden generar las mismas secuencias de salidas que una mquina de Moore, pero con menos estados. En diseos de mquinas secuenciales de estados finitos completamente sincrnicas, debe preferirse el modelo de Moore. As tambin cuando se empleen dispositivos lgico programables(PLD) para la implementacin. Ejemplo. Los siguientes diagramas ilustran la diferencia entre el nmero de estados para un detector de la secuencia de dos unos seguidos, cada vez que se presente.

Figura. Diagramas de Mealy y Moore ejemplo. Ejemplo. Modelado de diagrama de estados. Lavadora. En situaciones reales puede concebirse el funcionamiento de un sistema mediante la elaboracin de un diagrama de estados. Supongamos que disponemos de una lavadora, que externamente tiene tres botones: Encender, Detener, Lavar; de un indicador luminoso L, y de un interruptor ubicado en la puerta. La figura ilustra la mquina:

Ing. Luis Pacheco Cribillero

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

Figura. Lavadora. Se consideran eventos (entradas) la activacin de los botones de la consola y del interruptor de la puerta. El indicador luminoso es una accin (salida) que debe ejecutarse. Se visualizan tres estados asociados a la lavadora: apagada, detenida y lavando. La deteccin de cules son los estados, est basada en la visualizacin de situaciones distinguibles que se mantienen un determinado tiempo. Los eventos producen cambios de estado. Estando apagada, el evento encender dispara una transicin al estado detenida (o encendida). Estando en el estado detenida, la ocurrencia del evento lavar produce la transicin al estado lavando. Si est lavando, la presin del botn detener gatilla la conmutacin al estado detenida. Al producirse el evento abrir la puerta, la lavadora debe pasar al estado apagada. La luz L debe encenderse cuando hay potencia aplicada a la lavadora. Es decir, desde que se pasa de apagada a encendida y mantenerse iluminada hasta que se abra la puerta, cuando se pasa a apagada. Las especificaciones anteriores permiten dibujar un diagrama de estados, el que se muestra en la figura arriba. Los eventos producen cambios de estado. Cada transicin o cambio de estado, est asociada a un (y slo un) evento. Un evento puede desencadenar varias transiciones, en el ejemplo, la entrada o evento puerta produce dos transiciones, dependiendo del estado en que se encuentra la lavadora. La nica accin de salida L se ilustra asociada a las transiciones (Mealy). Tambin es posible asociarla a los estados (Moore): la luz L debe estar encendida mientras la lavadora est encendida o lavando; debe apagarse cuando est en el estado apagada. Figura. Diagrama de estados de la Lavadora. El estado inicial para esta mquina es el estado apagada. A partir del diagrama puede escribirse un programa Abel, para disear la mquina secuencial, en un dispositivo programable. module Lavadora clock, Encender, Lavar, Detener, Puerta pin ; L pin istype 'com'; q1, q0 pin istype 'reg'; registroestado = [q1, q0]; "Estados. Apagada = 0; Encendida = 1; Lavando = 2; equations [q1,q0].clk = clock; state_diagram registroestado; State Apagada: IF (Encender) THEN Encendida WITH L= 1; ELSE Apagada WITH L= 0; State Encendida: IF (Puerta) THEN Apagada WITH L= 0; ELSE IF (Lavar) THEN Lavando WITH L = 1; State Lavando:

Ing. Luis Pacheco Cribillero

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

IF (Detener) THEN Encendida WITH L= 1; ELSE IF(Puerta) THEN Apagada WITH L= 0; End Se emplean dos elementos con memoria (q1 y q0), que se declaran de tipo reg (por registro), a los cuales se les especifica una seal de reloj, con la ecuacin [q1,q0] .clk = clock. Se le coloca un nombre simblico al registro de estado con: registroestado = [q1, q0]. Luego se inicia la descripcin del diagrama mediante: state_diagram registroestado. Mediante sentencias If-then-else se especifican los cambios de estado, debido a la ocurrencia de eventos. Sub-mquinas. La descripcin de la lavadora puede seguir especificndose con mayor detalle, si se define con mayor precisin el estado lavando. Esto significa observar seales internas de la lavadora. Si se define el evento rotar, que produce que el motor de una vuelta, y de la seal de salida giro (G=1 a la izquierda, y G=0 a la derecha) y se define que el proceso de lavar sea dar dos vueltas a la izquierda seguidas por dos vueltas a la derecha, en el diagrama aparecen cuatro nuevos estados para describir el estado lavando. Figura. Diagrama de estados ampliado de la Lavadora. La descripcin permite diferentes niveles de abstraccin, en el ejemplo, lavando se ha descrito como una sub-mquina digital. Transformacin de Mealy a Moore. a) En el diagrama de Mealy deben separarse aquellos estados, para los cules existan transiciones con diferentes valores de salida, para igual entrada: Figura. Separacin de estados. Luego cada estado tendr slo un valor de salida asociado. Y se transforma a representacin de Moore, segn: Figura. Conversin a Moore. b) Para el estado inicial pueden presentarse dos casos: b1) Estado inicial con salida 0. No requiere modificacin. Figura. Estado inicial con salida cero. b2) Estado inicial con salida diferente de cero.

Ing. Luis Pacheco Cribillero

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

Figura. Estado inicial con salida uno. En este caso debera haber entrada. Se corrige agregando

salida, sin haber aplicado una un estado adicional: Figura. Agregar estado inicial.

Ejemplo.Transformacin unos seguidos.

para el reconocedor de dos

Figura. Separacin de estado S1. No es necesario corregir el estado inicial. Luego puede asociarse la salida al estado y no a la transicin hacia el estado.

Figura. No es necesario corregir S0. Finalmente puede plantearse: Figura. Diagrama de Moore ejemplo. Que resulta igual al diagrama de Moore planteado antes en el ejemplo 9.4. La transformacin explica el mayor nmero de estados que tiene generalmente un diagrama de Mealy. Ejemplo.

Detector de las secuencias 01 10, cada vez que se presenten. Para un modelo de Moore, se especifican las salidas asociadas al estado. Figura. Representacin de Moore ejemplo. En un diagrama de Mealy, se especifican las salidas asociadas a las transiciones.

Figura.- Representacin Mealy ejemplo.

Ing. Luis Pacheco Cribillero

de

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

ndice de Figuras. Figura 9.1. Secuencia sincrnica de niveles. ...........................................................173 Figura 9.2. Secuencia sincrnica de pulsos.............................................................173 Figura 9.3. Secuencia asincrnica de niveles. .........................................................173 Figura 9.4. Secuencia asincrnica de pulsos...........................................................174 Figura 9.5. Modelo mquina secuencial. .................................................................174 Figura 9.6. Compuertas y flip-flops. .........................................................................176 Figura 9.7. Modelo de Mealy....................................................................................176 Figura 9.8. Diagrama de Estados de Mealy.............................................................177 Figura 9.9. Tabla de transicin de estados de Mealy...............................................177

Ing. Luis Pacheco Cribillero

Circuitos Digitales II

Facultad de Ingeniera Electrnica

EEV

UTP

Figura 9.10. Matriz de transiciones y matriz de salida. ............................................178 Figura 9.11. Modelo de Moore.................................................................................178 Figura 9.12. Diagrama de estados de Moore...........................................................178 Figura 9.13. Tabla de transiciones de Moore...........................................................179 Figura 9.14. Matriz de transiciones ejemplo 9.1.......................................................180 Figura 9.15. Secuencia de salida.............................................................................180 Figura 9.16. Esquema generador de secuencias.....................................................180 Figura 9.17. Diagrama de Estados ejemplo 9.1. ......................................................181 Figura 9.18. Diagrama de estados ejemplo 9.2. ......................................................181 Figura 9.19. Secuencia salida ejemplo 9.2. .............................................................181 Figura 9.20. Tabla de transiciones ejemplo 9.2 .......................................................182 Figura 9.21. Diagrama de Moore ejemplo 9.3..........................................................182 Figura 9.22 Diagrama de Mealy ejemplo 9.3. ..........................................................182 Figura 9.23. Diagramas de Mealy y Moore ejemplo 9.4...........................................183 Figura 9.24. Lavadora..............................................................................................184 Figura 9.25. Diagrama de estados de la Lavadora. .................................................185 Figura 9.26. Diagrama de estados ampliado de la Lavadora...................................186 Figura 9.27. Separacin de estados. .......................................................................187 Figura 9.28. Conversin a Moore.............................................................................187 Figura 9.29. Estado inicial con salida cero...............................................................187 Figura 9.30. Estado inicial con salida uno................................................................187 Figura 9.31. Agregar estado inicial. .........................................................................188 Figura 9.32. Separacin de estado S1.....................................................................188 Figura 9.33. Separacin de estado S1.....................................................................189 Figura 9.34. Diagrama de Moore ejemplo 9.6..........................................................189 Figura 9.35. Representacin de Moore ejemplo 9.7. ...............................................190 Figura 9.36. Representacin de Mealy ejemplo 9.7.................................................190

Ing. Luis Pacheco Cribillero

Vous aimerez peut-être aussi

- Demostración de Identidades VectorialesssDocument4 pagesDemostración de Identidades VectorialesssMarco Quispe Palacios77% (13)

- Optimizacion 1Document14 pagesOptimizacion 1Fabricio WfblPas encore d'évaluation

- C220 Silabo Tecnologia para El Comercio Electronico EIEDocument4 pagesC220 Silabo Tecnologia para El Comercio Electronico EIEMarco Quispe PalaciosPas encore d'évaluation

- Am PL If Diferencia LesDocument0 pageAm PL If Diferencia LesjorgeramosvasPas encore d'évaluation

- Introducción Al ANSI CDocument31 pagesIntroducción Al ANSI CMarco Quispe PalaciosPas encore d'évaluation

- Diferencia Entre El Pic16f84a y El Pic16f628a - Marco Quispe PalaciosDocument9 pagesDiferencia Entre El Pic16f84a y El Pic16f628a - Marco Quispe PalaciosMarco Quispe Palacios50% (2)

- 1 Prueba Math 6°Document1 page1 Prueba Math 6°Consuelo Gomez OrtizPas encore d'évaluation

- Curriculum Vitae 2017 PaulaDocument2 pagesCurriculum Vitae 2017 PaulaAndrea MartinezPas encore d'évaluation

- Ensayo Acerca de Comunicaciones ÓpticasDocument2 pagesEnsayo Acerca de Comunicaciones ÓpticasgardomyPas encore d'évaluation

- Ejercicios Prog DinamDocument12 pagesEjercicios Prog DinammaarcoPas encore d'évaluation

- Qué Es Un Kibibyte y Un KilobyteDocument2 pagesQué Es Un Kibibyte y Un KilobyteEsterAlonsoPas encore d'évaluation

- Examen Parcial Propuesto Sistemas Operativos 2011 1 UsmpDocument2 pagesExamen Parcial Propuesto Sistemas Operativos 2011 1 UsmpAlex MercerPas encore d'évaluation

- Site Survey Enlace Microondas SENA - CDVDocument8 pagesSite Survey Enlace Microondas SENA - CDVjhonex28Pas encore d'évaluation

- Ficha de PreinscripcionDocument1 pageFicha de Preinscripcionabdiuwu7Pas encore d'évaluation

- 3 - Manual de Usuario Final PSDocument90 pages3 - Manual de Usuario Final PSAntonio De Jesús Martínez100% (1)

- Auditoria de AplicacionesDocument7 pagesAuditoria de AplicacionesJose H.Pas encore d'évaluation

- Codificacion ExpoDocument21 pagesCodificacion ExpoAlexis RamírezPas encore d'évaluation

- Cisco CcnaDocument108 pagesCisco CcnaMarcelo DuraznoPas encore d'évaluation

- Manual IntouchDocument84 pagesManual IntouchMarisol SalvadorPas encore d'évaluation

- Reconocimiento de Rosotros Mediante EigenfacesDocument6 pagesReconocimiento de Rosotros Mediante EigenfacesPedro InfantesPas encore d'évaluation

- Verbos para Redactar Los Aprendizajes EsperadosDocument5 pagesVerbos para Redactar Los Aprendizajes EsperadosJaime Valencia Santander50% (2)

- Cómo Calcular El PromedioDocument3 pagesCómo Calcular El Promediogabriel matienzo semperteguuPas encore d'évaluation

- PolinomiosDocument3 pagesPolinomiosKevin TtitoPas encore d'évaluation

- Compuertas Logicas PDFDocument10 pagesCompuertas Logicas PDFCamilo Ernesto Blanco Pérez100% (1)

- WP - Hostalia Servidores Dedicados PDFDocument5 pagesWP - Hostalia Servidores Dedicados PDFTania VivianaPas encore d'évaluation

- Microsoft Office PublisherDocument13 pagesMicrosoft Office PublisherYago C. Guillen100% (1)

- La Necesidad de Un Router CNCDocument3 pagesLa Necesidad de Un Router CNCMiller Ccanccapa MacedoPas encore d'évaluation

- 05 Grado QuintoDocument4 pages05 Grado QuintoJUDITH BURBANO MUÑOZPas encore d'évaluation

- Redes Telefonos Propietarios Analogicos Panasonic Serie KX-T7700 WWW - Logantech.com - MX Mérida, Yuc.Document4 pagesRedes Telefonos Propietarios Analogicos Panasonic Serie KX-T7700 WWW - Logantech.com - MX Mérida, Yuc.LogantechPas encore d'évaluation

- Lab 5 FortalezasDocument7 pagesLab 5 FortalezasClaudia PeñalozaPas encore d'évaluation

- Algebra de Boole y Funciones Booleanas 1101499Document4 pagesAlgebra de Boole y Funciones Booleanas 1101499seb wood21Pas encore d'évaluation

- Cuestionario Toma de DecisionesDocument35 pagesCuestionario Toma de DecisionesMelissa Vásquez Trujillo100% (1)

- Análisis Del EnunciadoDocument8 pagesAnálisis Del EnunciadoSETHXPPas encore d'évaluation

- B Asr 920 12 SZ IM QSG Es ESDocument30 pagesB Asr 920 12 SZ IM QSG Es ESDanielPas encore d'évaluation

- El Cálculo A Través de La HistoriaDocument4 pagesEl Cálculo A Través de La HistoriajcbarcenaPas encore d'évaluation