Académique Documents

Professionnel Documents

Culture Documents

Practical 4

Transféré par

Louis StephenCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Practical 4

Transféré par

Louis StephenDroits d'auteur :

Formats disponibles

CSSE3010 Embedded Systems Design & Interfacing

Practical 4 SPI / Radio control

Objectives

To learn the fundamentals of the SPI bus, including data transmission and the conceptual understanding of a multiple slave configuration. Become familiar with the basic operation of the nRF24l01+ radio package including configuring the radios registers for TX/RX transmission. To understand the complications that may arise when setting up and communicating on an RF network.

The main objective of this practical is to introduce or strengthen your knowledge in one of the most widely used communication protocols; the SPI bus. Although a summary of the bus is presented here, it is recommended that before starting on this practical that you do some extra background reading on the topics covered here (see references for some good resources). Throughout this practical you will setup SPI communication with the radio and configure the radio, creating a RF communication link between multiple microcontrollers.

Introduction

The Serial Peripheral Interface (SPI) [1] is a high speed bus that connects a master to one or more slave devices such as the nRF24l01+ [2]. The bus operates using a 4 wire interface which includes: SPI Clock (SCLK, SCK, CLK) this line is used for the clock signal sent by the master to synchronise the data sent between the master and the slave. The speed of data transactions depend on the speed of the clock signal. Master Out Slave In (MOSI, SIMO) - this carries data from the master to the slave. Master In Slave Out (MISO, SOMI) this carries data from the slave to the master. Slave Select (SS, CSN) As previously mentioned, the bus can support multiple slave devices, each sharing the above three connections. Furthermore, each slave can be selected by holding the SS at active low. Only one slave can be selected at a time.

Notice that the bus is bidirectional such that the master can send data whilst the slave can simultaneously send data back to the master, perhaps sending data from a previous request or simply status information. The master controls the communication, such that the slave cannot initiate data communication, and for this reason some devices make use of an external interrupt

Practical 4 SPI and the nRF24l01+ radio

Page 1

CSSE3010 Embedded Systems Design & Interfacing

mechanism. Transmissions often occur in 8-bit words, however, it should be noted many other word sizes are common. The SPI bus is similar to a circular ring shift register as depicted below, with the slave and master holding a single word. The words are shifted out via the MOSI/MISO lines ticking the clock 8 times to complete a data transfer.

The phase and polarity of data signals must be configured to match the slave device. This is configured using two options CPOL (clock polarity) and CPHA (clock phase), resulting in the below 4 configurations: CPOL=0, CPHA=0: Data is captured on the clocks rising edge and propagated on a falling edge. CPOL=0, CPHA=1: Data is captured on the clocks falling edge and propagated on a rising edge. CPOL=1, CPHA=0: Data is captured on the clocks falling edge and propagated on a rising edge CPOL=1, CPHA=1: Data is captured on the clocks rising edge and propagated on a falling edge.

The nRF24l01+ uses mode 0 (CPOL=0, CPHA=0) and supports up to 8Mbps transfer rate (note this is the transfer rate on the SPI bus, the radio transmission itself is limited to 2Mbps). The code provided in rf.c shows how the SPI is configured for the nrf24l01+. The AT91SAM7 has an SPI controller handled by the Peripheral DMA Controller (PDC). This handles SPI transactions using operations not under the control of the central processor; resulting in quicker transfers and more CPU time for other tasks (this will become more important when using an operating system, such as FreeRTOS). The nRF24l01+ has a set of registers defining the firmware interface. This register map can be found in section 9.1 of the datasheet [3]. It is recommended you familiarise yourself with these few registers, especially CONFIG, RF_CH, STATUS, RF_SETUP, EN_RXADDR. In order to send / receive data or issue commands to the device from the SPI port we first ensure the CSN pin is high. We then bring the CSN pin low to alert the nRF24l01+ that an SPI transaction is going

Practical 4 SPI and the nRF24l01+ radio

Page 2

CSSE3010 Embedded Systems Design & Interfacing

to take place. When writing to the device, firstly the command byte is sent followed by the data. When reading, we must send the register we would like to read, and then in order for the device to send its response we must send another (arbitrary) byte to receive the response. The STATUS register can be read to check whether something important has happened, such as a packet being received. When a packet is successfully received (with CE held high), the CE pin must be brought low and the R_RX_PAYLOAD operation can be executed, followed by dummy bytes (corresponding to the payload width configured). After successfully receiving the data, hold the CE pin high again to continue listening. Similarly for transmission, the CE pin is brought low, executing the W_TX_PAYLOAD command followed by the data you wish to send, followed by bringing the CE pin high again. There are three interrupts that can be generated by the nRF24l01+; RX_DR, TX_DS and MAX_RT. These can be detected on the devices IRQ pin, or by reading the STATUS register. RX_DR is triggered when the radio has received a packet. TX_DS is triggered when a packet has been successfully transmitted. The MAX_RT is set when the maximum number of retries for sending a packet has exceeded the preconfigured amount. Note that the TX FIFO must be cleared in this case in order to continue receiving packets. Refer to page 20 of the datasheet to see a state diagram of radio modes and recommended operating mode paths. The nRF24l01+ has 6 pipes which can be configured to receive data. Each of these pipes can have their own address as defined by RX_ADDR_PX registers, on which the radio can receive data. As well as this the device has two packet queues for RX and TX. Each queue can hold up to three packets and are read on a First in First Out (FIFO) basis. There are many inherit issues of having a class full of nRF24l01+s. There are only a limited number of channels available to use and therefore many radios may be on the same channel. So there must be a way to differentiate between packets that you and others send as well as handling packet collisions and noise. On a radio level this is done via the RX_ADDR / TX_ADDR and a packet checksum. In this prac we will define source and destination address in our protocol. We will also make use of a 16 bit checksum on each transmitted packet. Although the radio already performs its own checksum, for the purposes of this prac we will re-implement it for completeness. When selecting a channel please limit yourself to the lower 50 channels to be compliant with the Australian radio frequency regulations [4]. Do note that if you decide to configure the nRF24l01+ at 2Mbps, the channel spacing is 2MHz, rather than 1MHz, limiting the possible channels further. The SPI bus and nRF24l01+ are covered broadly here. It is highly recommended to read more information from sources found at the end of the document [5].

Practical 4 SPI and the nRF24l01+ radio

Page 3

CSSE3010 Embedded Systems Design & Interfacing

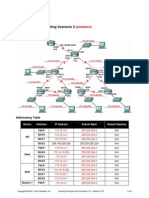

We will connect the radio to the AT91s SPI channel 0. The pin layout we will be using is shown in the figure below.

Make sure you have checked out the source files accompanying this practical. Note that additional files have been included which contain methods for some of the low level radio calls you will be using. FIRST: update your source files using subversion: 1. 2. 3. 4. Open a terminal window and navigate to /home/user/svn Type svn update If prompted for a password: csse3010 DO NOT store the password in the gnome keyring, if prompted.

The Design Task

For this prac we will configure the radios to channel 40. Before we begin sending packets we first define our communications protocol. Packet Type 1 Byte Destination Address 4 Bytes Source Address 4 Bytes Payload 21 Bytes Checksum byte 2 Byte

The destination and source addresses with a width of 4 will define to whom you are sending your packet to. For the purpose of this practical, it will consist of your student number formatted in hex. (i.e. s41234123 will have address 0x41234123). One of the tutors will be running a base station to which you will be communicating with. This base station has address 0x12345678. The packet type field for this practical is 0x20. Be sure to set this field as well as the destination field correctly, otherwise the base station will not respond to your request. You are required to send a packet of the format above to the base station. The payload must be filled via Putty by typing characters and submitting the packet by pressing the return key (or exceeding the maximum payload length). The base station will receive your request and send back a packet. This packet will contain a capitalised form of your initial payload which you must print back to the terminal over the USB interface. Be sure to filter any incoming packets for your student ID address, otherwise you will display other peoples packets.

Practical 4 SPI and the nRF24l01+ radio

Page 4

CSSE3010 Embedded Systems Design & Interfacing

Response from Base Station In main.c a data structure has been included to help you structure your packets according to the protocol defined above. User input

typedefstruct { char type; chardest[4]; charsrc[4]; char payload[PAYLOAD_WIDTH]; shortcrc; }__attribute__((packed)) Packet; // 32 bytes long. Data structure for packets.

The packed attribute is a hint to the compiler that we do not want padding within the data structure, meaning we can operate on the data pointed to by the Packet structure as if it is 32 consecutive bytes. A checksum can be performed on the packet before it is sent by using the following function;

crc16(0, tx_buf, 30);

Some helpful comments in the main function should help you to get started. Make sure you examine the radio functions defined in nrf24l01plus.c. The radio driver will send and receive packets through tx_buf and rf_buf. The base station will send a request back fairly quickly, therefore make sure you switch your radio back to receive mode straight after transmission. Remember, you can use the USB interface as a feedback mechanism for debugging. When finished, you should be able to explain your code to the tutor. And demonstrate a functioning program to receive marks for this practical. Leave the checksum till last. The base station will still send a (different) packet if you cant get the checksum working. Challenge: Your packet may not get through the first time if the base station is processing another request. Write your code such that if a response is not received within 500milliseconds to resend the request. Make sure to keep any new input from the terminal in the buffer for the next request.

Practical 4 SPI and the nRF24l01+ radio

Page 5

CSSE3010 Embedded Systems Design & Interfacing

Marking criteria

The practicals in this course are marked on a pass / fail basis. This means you must demonstrate to your tutor sufficient understanding and functionality before progressing. If you fail to demonstrate sufficient understanding through completing the design task you will be required to show a tutor you are competent at another time to pass this practical. Do note that if you did not pass the requirements the first time, tutors will be more thorough in checking your understanding. Each practical has a set of specific questions you need to be able to answer to pass. The questions can vary from very detailed to more theoretical. You will be asked just one question (or two at most) and if your answer is not satisfactory you fail. BE PREPARED.

Sample questions for this practical (Hint - Read the NRF24l01+ datasheet and the nrf24l01plus.c

file):

0. 1. 2. 3. 4. 5.

WORKBOOK

What SPI mode (master or slave) must the ARM processor be in? What does the CSN pin do? What radio frequency does the NRF24l01+ transmit/receive on? How do you change the radio channel that he NRF24l01+ uses? What does the CE pin do?

References / Further Readings

1. 2. 3. 4. 5. http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus http://www.sparkfun.com/products/691 http://www.nordicsemi.com/eng/nordic/download_resource/8041/1/77976879 http://www.acma.gov.au http://www.diyembedded.com/tutorials/nrf24l01_0/nrf24l01_tutorial_0.pdf

Practical 4 SPI and the nRF24l01+ radio

Page 6

Vous aimerez peut-être aussi

- Wiznet CompilationDocument7 pagesWiznet CompilationjachawkPas encore d'évaluation

- Serial CommunicationsDocument23 pagesSerial CommunicationsPhuoc Trung Tran100% (1)

- VSATDocument11 pagesVSATShashwat TiwariPas encore d'évaluation

- Chapter-6 IO InterfacesDocument49 pagesChapter-6 IO InterfacesBhawna SinghPas encore d'évaluation

- CCNA Interview Questions You'll Most Likely Be AskedD'EverandCCNA Interview Questions You'll Most Likely Be AskedPas encore d'évaluation

- An Introduction To IEC 60870-5-101 - GBC Report 011-2Document10 pagesAn Introduction To IEC 60870-5-101 - GBC Report 011-2Kalyan RanjanPas encore d'évaluation

- Notes On LonWorks-1Document8 pagesNotes On LonWorks-1mughees_itcompPas encore d'évaluation

- Chapter 5 Yearwise MarkingDocument20 pagesChapter 5 Yearwise MarkingHonor SwiftPas encore d'évaluation

- IEEE Standards4Document29 pagesIEEE Standards4Ruchi AgrawalPas encore d'évaluation

- TCP Ip NotesDocument14 pagesTCP Ip Notesjoshwaaa_hotmailcomPas encore d'évaluation

- By Vinayashree: Serial Communication ConceptsDocument18 pagesBy Vinayashree: Serial Communication ConceptsvinayashreePas encore d'évaluation

- Fprintf Fprintf ( PHYS352') PHYS352 Fopen Id Fopen ( Datafile - TXT','W') R' W' Fopen IdDocument5 pagesFprintf Fprintf ( PHYS352') PHYS352 Fopen Id Fopen ( Datafile - TXT','W') R' W' Fopen IdbaruaeeePas encore d'évaluation

- Computer Networks Midsems 17074004Document8 pagesComputer Networks Midsems 17074004Kumar shivamPas encore d'évaluation

- Untitled DocumentDocument8 pagesUntitled DocumentMUHAMMAD SHAHEERPas encore d'évaluation

- DCCDocument9 pagesDCCSyed MansoorPas encore d'évaluation

- CAN TutorialDocument22 pagesCAN TutorialNaveen BasavarajacharPas encore d'évaluation

- CAN TutorialDocument22 pagesCAN TutorialApoorva BhattPas encore d'évaluation

- Es IiiDocument12 pagesEs IiiGopinathan MPas encore d'évaluation

- CN Unit 2Document13 pagesCN Unit 2SS The BrandPas encore d'évaluation

- The Universal Serial BusDocument11 pagesThe Universal Serial BusHiba AbdulwahedPas encore d'évaluation

- UNIT-1 Serial BusesDocument67 pagesUNIT-1 Serial BusesJalal WadoodPas encore d'évaluation

- The Switch Book by Rich Seifert-NotesDocument51 pagesThe Switch Book by Rich Seifert-NotesharinijPas encore d'évaluation

- Osi Layer and Communication Between Two Node in A NetworkDocument11 pagesOsi Layer and Communication Between Two Node in A NetworkAbhishek BohraPas encore d'évaluation

- Advanced Computer Networks: The Network LayerDocument17 pagesAdvanced Computer Networks: The Network Layersrinivasulu thiruveedulaPas encore d'évaluation

- Serial Communication Protocols and RTCDocument15 pagesSerial Communication Protocols and RTCMukesh PatidarPas encore d'évaluation

- Serial Communication Interview Questions and AnswersDocument9 pagesSerial Communication Interview Questions and AnswerszhangyiliPas encore d'évaluation

- Synchronous Optical NetworkDocument5 pagesSynchronous Optical Networkdeepaknath2200Pas encore d'évaluation

- Sonet/Sdh: Channel 1 Channel 1Document7 pagesSonet/Sdh: Channel 1 Channel 1rthrbyPas encore d'évaluation

- Input Output InterfacesDocument21 pagesInput Output InterfacesBlackk SpydoPas encore d'évaluation

- Experiment-6: Ishaan AggarwalDocument6 pagesExperiment-6: Ishaan Aggarwalvishal sharmaPas encore d'évaluation

- Embedded Systems Lab04 USARTDocument12 pagesEmbedded Systems Lab04 USARTAimanPas encore d'évaluation

- CN Lab ProgramsDocument36 pagesCN Lab ProgramsKavitha SAPas encore d'évaluation

- S7 Ethernet-Local Area Network: GROUP: 4960 Members: William Obaco Alexander Méndez Raúl SaltosDocument47 pagesS7 Ethernet-Local Area Network: GROUP: 4960 Members: William Obaco Alexander Méndez Raúl SaltosByron Xavier Lima CedilloPas encore d'évaluation

- Chapter 4Document30 pagesChapter 4udgam pandeyPas encore d'évaluation

- Ktustudents - In: Ec 308 Embedded Systems Module-2Document16 pagesKtustudents - In: Ec 308 Embedded Systems Module-2Vishnu Prasad MPas encore d'évaluation

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksD'EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksPas encore d'évaluation

- cc2500 ConDocument25 pagescc2500 Conprasad357Pas encore d'évaluation

- Chapter 6Document21 pagesChapter 6shadi22Pas encore d'évaluation

- Project Final Report SCADA Attack SystemDocument9 pagesProject Final Report SCADA Attack Systemlmartinez88Pas encore d'évaluation

- Research PaperDocument8 pagesResearch PaperinfydiptiPas encore d'évaluation

- MIL STD 1553 OverviewDocument54 pagesMIL STD 1553 OverviewshyamsundarsrPas encore d'évaluation

- Ethernet 03 PDFDocument7 pagesEthernet 03 PDFrimar027Pas encore d'évaluation

- Straight-Through Wired Cables: 2) A) What Are The Three Types of Ethernet Cables? ExplainDocument6 pagesStraight-Through Wired Cables: 2) A) What Are The Three Types of Ethernet Cables? ExplainRohit RishiPas encore d'évaluation

- How To Use USB-based Applications With PIC MicrocontrollersDocument35 pagesHow To Use USB-based Applications With PIC MicrocontrollersSrinivas Perala100% (3)

- A Design of Network Remote Control SystemDocument4 pagesA Design of Network Remote Control SystemPurush ArunPas encore d'évaluation

- Operation of Pci BusDocument7 pagesOperation of Pci BusRohini JosephPas encore d'évaluation

- Computer Network Long Questions & AnswerDocument12 pagesComputer Network Long Questions & Answersravan123Pas encore d'évaluation

- Router1X3 RTLDesignandVerificationDocument11 pagesRouter1X3 RTLDesignandVerificationSudeep KrishnappaPas encore d'évaluation

- Part 1 Fundamentals of Ethernet LANsDocument16 pagesPart 1 Fundamentals of Ethernet LANsNOVA MAROCPas encore d'évaluation

- Presentation On SDH Vs SS7Document59 pagesPresentation On SDH Vs SS7lvsaruPas encore d'évaluation

- Fundamentals of Microcontroller & Its Application: Unit-IvDocument17 pagesFundamentals of Microcontroller & Its Application: Unit-IvRajan PatelPas encore d'évaluation

- Advanced Computer Networks - CoSc-6111-Lecture-4Document80 pagesAdvanced Computer Networks - CoSc-6111-Lecture-4AhmedPas encore d'évaluation

- Baud Rate Generator:: Homework Assignment # 4Document5 pagesBaud Rate Generator:: Homework Assignment # 4Badrinath Balasubramanian100% (1)

- ASSIGNMENT 1 (Embd&IOmT)Document9 pagesASSIGNMENT 1 (Embd&IOmT)rakesh.jPas encore d'évaluation

- Unit 6 MCDocument44 pagesUnit 6 MCkaustubhPas encore d'évaluation

- WCDMA MAC Project ReportDocument9 pagesWCDMA MAC Project ReportMayank GhoshPas encore d'évaluation

- Router 1X3-RTL Design and Verification: September 2015Document11 pagesRouter 1X3-RTL Design and Verification: September 2015Bhosle Balaji DhondibaPas encore d'évaluation

- Transmission Notes-KLM Mapping in SDHDocument11 pagesTransmission Notes-KLM Mapping in SDHmathurwise100% (1)

- Rtu Exam Solution: Global Institute of Technology, JaipurDocument33 pagesRtu Exam Solution: Global Institute of Technology, JaipurprashantvlsiPas encore d'évaluation

- Exp-3 (Speed Control by V-F MethodDocument4 pagesExp-3 (Speed Control by V-F MethoduttamPas encore d'évaluation

- Ford Everes PDFDocument584 pagesFord Everes PDFTiến Hồ100% (6)

- Language Translation Software Market Industry Size, Share, Growth, Trends, Statistics and Forecast 2014 - 2020Document9 pagesLanguage Translation Software Market Industry Size, Share, Growth, Trends, Statistics and Forecast 2014 - 2020api-289551327Pas encore d'évaluation

- ACI 232.1 Use of Pozzolans in ConcreteDocument24 pagesACI 232.1 Use of Pozzolans in ConcreteSree Nivas100% (1)

- Esc101: Fundamentals of Computing: 2011-12-Monsoon SemesterDocument6 pagesEsc101: Fundamentals of Computing: 2011-12-Monsoon SemesterMukesh Kumar DewraPas encore d'évaluation

- Worksheet # 7 - Free Body DiagramDocument2 pagesWorksheet # 7 - Free Body DiagramyabalabahiyaPas encore d'évaluation

- Shell Spirax S6 Txme: Performance, Features & BenefitsDocument2 pagesShell Spirax S6 Txme: Performance, Features & BenefitsAbdelhadi HoussinPas encore d'évaluation

- Mobil DTE 20 Series - Marketing Asset - Display & POS Support Material - Performance ProfileDocument2 pagesMobil DTE 20 Series - Marketing Asset - Display & POS Support Material - Performance Profilethammarat khruasonkhamPas encore d'évaluation

- Distance Measuring EquipmentDocument12 pagesDistance Measuring Equipmentमेनसन लाखेमरूPas encore d'évaluation

- DATA SHEET Industrial Enamel BlancoDocument4 pagesDATA SHEET Industrial Enamel BlancoAlfredo OrellanaPas encore d'évaluation

- Feild Inspection of Shell and Tube Heat ExchangersDocument4 pagesFeild Inspection of Shell and Tube Heat ExchangersMatthew BennettPas encore d'évaluation

- ASTM E1417 Penetrant Testing - 9 PDFDocument11 pagesASTM E1417 Penetrant Testing - 9 PDFbikaPas encore d'évaluation

- Work at Height Questions For Height PassDocument3 pagesWork at Height Questions For Height PassPravash Mohanty100% (1)

- Bricks ComparisonDocument13 pagesBricks ComparisonMd. Numan HossainPas encore d'évaluation

- Conformity Assessment For The Execution of Steel & Aluminium StructuresDocument14 pagesConformity Assessment For The Execution of Steel & Aluminium StructuresJevgenijsKolupajevsPas encore d'évaluation

- Memristor Modeling in MATLAB®&SimulinkDocument6 pagesMemristor Modeling in MATLAB®&Simulinkjoseamh69062247Pas encore d'évaluation

- Guide To Petrophysical Interpretation PDFDocument147 pagesGuide To Petrophysical Interpretation PDFDwiandaru DarmawanPas encore d'évaluation

- Features General Description: 1.5A Low Dropout Linear Regulator With Programmable Soft-StartDocument15 pagesFeatures General Description: 1.5A Low Dropout Linear Regulator With Programmable Soft-StartSivaPas encore d'évaluation

- 6 3 AnswersDocument4 pages6 3 Answersshiwaisanxian100% (1)

- TYBTech Syllabus MechanicalDocument49 pagesTYBTech Syllabus MechanicalswapnillkPas encore d'évaluation

- Benq mp510 Level1Document212 pagesBenq mp510 Level1Juan Duarte Lopez100% (1)

- Wind Loads - IS 875 - Where Does Our Code of Practice StandDocument11 pagesWind Loads - IS 875 - Where Does Our Code of Practice StandRavi Kiran NandyalaPas encore d'évaluation

- Motorized Hydraulic PressDocument4 pagesMotorized Hydraulic PressDhiraj Shinde100% (2)

- Reducing ValveDocument11 pagesReducing ValveFluidPowerConsultantPas encore d'évaluation

- ReactionsDocument30 pagesReactionskaloibestPas encore d'évaluation

- Design and Evaluation of Inflatable Wings For UavsDocument290 pagesDesign and Evaluation of Inflatable Wings For UavsmegustalazorraPas encore d'évaluation

- Binary Search of Unsorted ArrayDocument3 pagesBinary Search of Unsorted ArrayGobardhan BaralPas encore d'évaluation

- Types of PatternDocument12 pagesTypes of PatternadamPas encore d'évaluation

- IQ RF MappingDocument14 pagesIQ RF Mappingsatcom_77Pas encore d'évaluation

- Resistance WeldingDocument22 pagesResistance WeldingLOKENDRA91100% (2)