Académique Documents

Professionnel Documents

Culture Documents

How A Pentium II Chip Works: Floa Ting Point MA TH Unit

Transféré par

Amar ShahidTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

How A Pentium II Chip Works: Floa Ting Point MA TH Unit

Transféré par

Amar ShahidDroits d'auteur :

Formats disponibles

126

PA R T 3

MICROCHIPS

CHAPTER 12

HOW A MICROPROCESSOR WORKS

127

How a Pentium II Chip Works

1

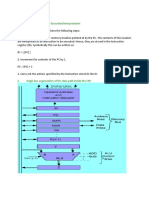

Intels Pentium microprocessor is made up of two slices of silicon. One is the 5.5-9.5-million transistor CPU, where the softwares instructions are executed. The other is a level 2 (L2), custom-designed high-speed memory cache. Its 15.5-million transistors store up to 512 kilobytes of data and code. Earlier processors typically used a cache separate from the processor, usually part of the computers motherboard. Processor

L2 cache

The processor and cache share the same 64-bit interface to the computers information. Program code or data manipulated by that code move in and out of the chip at the PCs maximum bus speed, no more than 100Mhz even for processors that function internally at 200MHz. Much of the Pentium Pro design is structured to alleviate the bus bottleneck by minimizing the times a clock cyclesthe smallest time in which a computer can do anythingticks away without the processor completing an operation.

When information enters the processor through the bus interface unit (BIU), the BIU duplicates the information, sends one copy to the CPUs closely linked L2 cache, and the other to a pair of level 1 (L1) caches, ranging in size from 8-16K, built directly into the CPU. The BIU sends program code to the L1 instruction cache, or I-cache, and sends data to be used by the code to another L1 cache, the data cache (D-cache).

While the fetch/decode unit is pulling in instructions from the I-cache, the branch target buffer (BTB) compares each instruction with a record in a separate set-aside buffer to see if any instruction has been used before. The BTB is looking in particular for instructions that involve branching, a situation where the programs execution could follow one of two paths. If the BTB nds a branch instruction, it predicts, based on past experience, which path the program will take. The predictions are better than 90 percent accurate.

L1 che a I-C

Uo ps

B BT

U BI

Socket connectors

De

12

Meanwhile, the circular buffer also is being inspected by the retirement unit. It rst checks to see if the uop at the head of the buffer has been executed. If it hasnt, the retirement unit keeps checking it until it has been processed. Then the retirement unit checks the second and third uops. If theyre already executed, the units sends all three resultsits maximumto the store buffer. There the prediction unit checks them out one last time before theyre sent to their proper place in system RAM.

Store B

t en t

u ff e r

FE

Tail

CH

cod

ers

Ins

tru

er ff Bu

cti on s

Ret ire Un m i

ALU

Hea der

D O NE D O NE

tch

/Ex

D O NE

B O R

D O NE

DE

D CO

E

L1 che Ca D-

As the fetch/decode unit pulls instructions in the order predicted by the BTB, three decoders working in parallel break up the more complex instructions into uops, which are smaller, 274bit micro-operations. The dispatch/ execution unit processes several uops faster than it processes a single higherlevel instruction.

Jump n utio Exec it Un

ecute

ALU

Di

T I B 64

9

The decode unit sends all uops to the instruction pool, also called the ReOrder Buffer. This contains two arithmetic logic units (ALUs) that handle all calculations involving integers. The ALUs use a circular buffer, with a head and tail, that contains the uops in the order in which the BTB predicted they would be needed.

pa

T IN PO T I NG N TI U OA TH FL MA

11

ach C 2 L

M RA o T

The dispatch/execute unit checks each uop in the buffer to see if it has all the information needed to process it, and when it nds a uop ready to process, the unit executes it, stores the result in the micro-op itself, and marks it as done.

When an uop that had been delayed is nally processed, the execute unit compares the results with those predicted by the BTB. Where the prediction fails, a component called the jump execution unit (JEU) moves the end marker from the last uop in line to the uop that was predicted incorrectly. This signals that all uops behind the end marker should be ignored and may be overwritten by new uops. The BTB is told that its prediction was incorrect, and that information becomes part of its future predictions.

10

If an operation involves oatingpoint numbers, such as 3.14 or .33333, the ALUs hand off the job to the oating-point math unit, which contains processing tools designed to manipulate oating-point numbers quickly.

Instead of sitting in idle while that information is fetched, the execute unit continues inspecting each uop in the buffer. When it nds a micro-op that has all the information needed to process it, the unit executes it, stores the results in the uop itself, marks the code as completed, and moves onto the next uop in line. This is called speculative execution because the order of uops in the circular buffer is based upon the BTBs branch predictions. The unit executes up to ve uops simultaneously. When the execution unit reaches the end of the buffer, it starts at the head again, rechecking all the uops to see if any have nally received the data it needs to be executed.

If a uops needs data from memory, the execute unit skips it, and the processor looks for the information rst in the nearby L-1 cache. If the data isnt there, the processor checks the much larger L2 cache. Because the L-2 cache is integrated with the CPU, information moves between them 2-4 times faster than between the CPU and the external bus. At a chip speed beginning at 150MHz, information is retrieved at the rate of 1.2 gigabytes a second, compared to the 528MB a second if the CPU has to go to external memory to get the information.

Vous aimerez peut-être aussi

- ArchitectureDocument14 pagesArchitectureGopal PawarPas encore d'évaluation

- Bus Interface UnitDocument4 pagesBus Interface UnitVENKATRAMANPas encore d'évaluation

- Component 2Document2 pagesComponent 2karmaPas encore d'évaluation

- Exp 2Document10 pagesExp 2NAFISA ISLAM 1808006Pas encore d'évaluation

- MicroprocessorDocument11 pagesMicroprocessornave101Pas encore d'évaluation

- Study Material Subject: Microprocessor and Microcontroller V Semester Electronics by Prof. Mrs. J. S. GawaiDocument25 pagesStudy Material Subject: Microprocessor and Microcontroller V Semester Electronics by Prof. Mrs. J. S. GawaidukePas encore d'évaluation

- Introduction to Microprocessor Based SystemsDocument30 pagesIntroduction to Microprocessor Based SystemskusumgdasPas encore d'évaluation

- INTERRUPT To Power SupplyDocument3 pagesINTERRUPT To Power SupplyMathematics TutorPas encore d'évaluation

- Chapter 6-Computer ArchitectureDocument34 pagesChapter 6-Computer ArchitectureVongai MubaiwaPas encore d'évaluation

- Central Processing UnitDocument15 pagesCentral Processing Unithussain korirPas encore d'évaluation

- Micro Processor Design-ResumenDocument7 pagesMicro Processor Design-ResumenGuillermo SilvaPas encore d'évaluation

- MicrocontrollersDocument38 pagesMicrocontrollersShashwath kumarPas encore d'évaluation

- Pipelining in Pentium 2Document9 pagesPipelining in Pentium 2amol1agarwalPas encore d'évaluation

- Draw The Block Diagram of Simple Microprocessor-Based System and Explain The Function of Each Block (You Can Use MS Word or Google Docs)Document8 pagesDraw The Block Diagram of Simple Microprocessor-Based System and Explain The Function of Each Block (You Can Use MS Word or Google Docs)Riza Pahama MananaongPas encore d'évaluation

- CO2: 1. Concept of Program Execution/InterpretationDocument22 pagesCO2: 1. Concept of Program Execution/InterpretationYasmeen SyedPas encore d'évaluation

- Computer Organization Lab ManualDocument29 pagesComputer Organization Lab ManualAshis UgetconfusedPas encore d'évaluation

- 2.3 Central Processing UnitDocument8 pages2.3 Central Processing UnitHoodrich PabloPas encore d'évaluation

- Basicfeaturesof Advanced MicroprocessorsDocument15 pagesBasicfeaturesof Advanced MicroprocessorsAMISHAPas encore d'évaluation

- Lecture-1 (Introduction, Hardwired Logic) : MPI Unit 1Document34 pagesLecture-1 (Introduction, Hardwired Logic) : MPI Unit 1Tushar VermaPas encore d'évaluation

- Computer Assgnment For Grade 6aDocument14 pagesComputer Assgnment For Grade 6aDebela TesfayePas encore d'évaluation

- Cse IV Computer Organization (10cs46) SolutionDocument62 pagesCse IV Computer Organization (10cs46) Solutionnbpr0% (1)

- Assembly Language Short Notes by VuDocument16 pagesAssembly Language Short Notes by VuSyed HadiPas encore d'évaluation

- Architecture (MODULE I)Document18 pagesArchitecture (MODULE I)Arka Prava PaulPas encore d'évaluation

- 2 16 1350130228 7. Flexible Wireless DataDocument6 pages2 16 1350130228 7. Flexible Wireless DataSumeet SauravPas encore d'évaluation

- Cpre 381 Processor Project 1Document20 pagesCpre 381 Processor Project 1api-272773251Pas encore d'évaluation

- SAP Report Group 2Document14 pagesSAP Report Group 2Chanel Hooper0% (1)

- Computer Organization & Architecture: Input UnitDocument3 pagesComputer Organization & Architecture: Input UnitTilak JethwaPas encore d'évaluation

- Basic Processing Unit:: Fundamental ConceptsDocument35 pagesBasic Processing Unit:: Fundamental ConceptsJoseph JohnPas encore d'évaluation

- Chapter 6-Computer ArchitectureDocument29 pagesChapter 6-Computer ArchitectureEdzai Nyasha TarupiwaPas encore d'évaluation

- Component of A Digital ComputerDocument15 pagesComponent of A Digital Computerreginaamondi133Pas encore d'évaluation

- ResearchDocument4 pagesResearchNikko PatunganPas encore d'évaluation

- Module 1 of Computer OrganizationDocument27 pagesModule 1 of Computer OrganizationNimmymolManuelPas encore d'évaluation

- Intel 80586 (Pentium)Document24 pagesIntel 80586 (Pentium)Soumya Ranjan PandaPas encore d'évaluation

- New Middle East International Schools, Riyadh Grade: 9 Subject: Computer Science Academic Year: 2022-2023Document5 pagesNew Middle East International Schools, Riyadh Grade: 9 Subject: Computer Science Academic Year: 2022-2023agytePas encore d'évaluation

- Functional units and buses in digital systemsDocument20 pagesFunctional units and buses in digital systemsDivyaanshu AgrawalPas encore d'évaluation

- CO Unit 1Document43 pagesCO Unit 1Dinkesh JainPas encore d'évaluation

- Computer Architecture: Processor StructureDocument6 pagesComputer Architecture: Processor StructureEiEiPustaPas encore d'évaluation

- AC CourseWork MihaiTrofimDocument31 pagesAC CourseWork MihaiTrofimDima VlasPas encore d'évaluation

- Processing DeviceDocument4 pagesProcessing DeviceKundai ChiweshePas encore d'évaluation

- Introduction to Microprocessors and Their ComponentsDocument39 pagesIntroduction to Microprocessors and Their ComponentsSyaz ZanaPas encore d'évaluation

- IT225: Computer Organizations: August 25, 2014 (Monday)Document12 pagesIT225: Computer Organizations: August 25, 2014 (Monday)skiloh1Pas encore d'évaluation

- Q.1) A) - Explain (1) ALU: DefinitionDocument16 pagesQ.1) A) - Explain (1) ALU: DefinitionAmee PandyaPas encore d'évaluation

- Microcontrollers Explained: CPU, Memory, and I/O InterfacesDocument27 pagesMicrocontrollers Explained: CPU, Memory, and I/O InterfacesbalaPas encore d'évaluation

- Computer Architectur1Document31 pagesComputer Architectur1Abigail ChitongoPas encore d'évaluation

- 80486Document21 pages80486Khadar Nawas0% (1)

- Co Notes Module 1Document42 pagesCo Notes Module 1Vinyas M SPas encore d'évaluation

- Lecture 5 - CPU DesignDocument20 pagesLecture 5 - CPU Designnoberth nikombolwePas encore d'évaluation

- COA1Document56 pagesCOA1mayur jagdalePas encore d'évaluation

- Cao U2Document11 pagesCao U2vilasvairagade02Pas encore d'évaluation

- Department of Computer Science and EngineeringDocument32 pagesDepartment of Computer Science and Engineeringjexehif3730% (1)

- COA Chapter 6Document6 pagesCOA Chapter 6Abebe GosuPas encore d'évaluation

- Cse IV Computer Organization (10cs46) SolutionDocument46 pagesCse IV Computer Organization (10cs46) SolutionTasleem Arif100% (1)

- Module 5 - Pentium Processors - FinalDocument43 pagesModule 5 - Pentium Processors - FinalKEVINPas encore d'évaluation

- 1.4.2 The Fetch-Execute CycleDocument4 pages1.4.2 The Fetch-Execute CycleAbbas HaiderPas encore d'évaluation

- Hardware Organisation of Computers and MicroprocessorsDocument33 pagesHardware Organisation of Computers and MicroprocessorsUchenna OgunkaPas encore d'évaluation

- 5.6 Basic Computer Structure: Basic Maintenance Training Manual Module 5 Digital Technology / EISDocument26 pages5.6 Basic Computer Structure: Basic Maintenance Training Manual Module 5 Digital Technology / EISIvomadnessPas encore d'évaluation

- ECE 552 Introduction to Computer Architecture Design Project ReportDocument10 pagesECE 552 Introduction to Computer Architecture Design Project ReportzzzzoobbiiaaPas encore d'évaluation

- COADocument15 pagesCOAprathuasharao2017Pas encore d'évaluation

- A Computer Is An Electronic DeviceDocument10 pagesA Computer Is An Electronic Devicearvinder kaurPas encore d'évaluation

- DR Hamidullah Sai Mula Q atDocument11 pagesDR Hamidullah Sai Mula Q atAmar ShahidPas encore d'évaluation

- Rihla Irihla Ibn e Batootabn e BatootaDocument257 pagesRihla Irihla Ibn e Batootabn e BatootaAmar ShahidPas encore d'évaluation

- Corel Photo-Paint 11 User GuideDocument287 pagesCorel Photo-Paint 11 User GuideAmar ShahidPas encore d'évaluation

- Afla To Onki RepublicDocument64 pagesAfla To Onki RepublicAmar ShahidPas encore d'évaluation

- BC Fehrist Aug 2014Document50 pagesBC Fehrist Aug 2014Amar ShahidPas encore d'évaluation

- Space BackgroundsDocument1 pageSpace BackgroundsAmar ShahidPas encore d'évaluation

- T AgreedDocument1 pageT AgreedAmar ShahidPas encore d'évaluation

- BC Fehrist Aug 2014Document50 pagesBC Fehrist Aug 2014Amar ShahidPas encore d'évaluation

- Space Artworks 19Document1 pageSpace Artworks 19Amar ShahidPas encore d'évaluation

- BC Fehrist Aug 2014Document50 pagesBC Fehrist Aug 2014Amar ShahidPas encore d'évaluation

- Abstract Color BackgroundDocument1 pageAbstract Color BackgroundAmar ShahidPas encore d'évaluation

- Abstract Color BackgroundDocument1 pageAbstract Color BackgroundAmar ShahidPas encore d'évaluation

- Pink Abstract Light BackgroundDocument1 pagePink Abstract Light BackgroundAmar ShahidPas encore d'évaluation

- Green Vector HDTV-HDDocument1 pageGreen Vector HDTV-HDAmar ShahidPas encore d'évaluation

- Light BackgroundDocument1 pageLight BackgroundAmar ShahidPas encore d'évaluation

- He Is First Last 01a 72591.1332962463.1280.1280Document1 pageHe Is First Last 01a 72591.1332962463.1280.1280Amar ShahidPas encore d'évaluation

- Apple Space WallpaperDocument1 pageApple Space WallpaperAmar ShahidPas encore d'évaluation

- Nebula and Stars in Space Wallpaper 3023Document1 pageNebula and Stars in Space Wallpaper 3023Amar ShahidPas encore d'évaluation

- Yellow Background 1920x1200Document1 pageYellow Background 1920x1200Amar ShahidPas encore d'évaluation

- Golden Butterfly Vector Background 600x375Document1 pageGolden Butterfly Vector Background 600x375Amar ShahidPas encore d'évaluation

- Graphics Design WallpaperDocument1 pageGraphics Design WallpaperAmar ShahidPas encore d'évaluation

- Space PathDocument1 pageSpace PathAmar ShahidPas encore d'évaluation

- 16thc Wall TilingDocument1 page16thc Wall TilingAmar ShahidPas encore d'évaluation

- Yellow Rose 3 1920x1080Document1 pageYellow Rose 3 1920x1080Amar ShahidPas encore d'évaluation

- WeOwnTheSky Wallpaper RedDocument1 pageWeOwnTheSky Wallpaper RedAmar ShahidPas encore d'évaluation

- Ultimate Sparkle Background by Computerinkt-D5duo28Document1 pageUltimate Sparkle Background by Computerinkt-D5duo28Amar ShahidPas encore d'évaluation

- WeOwnTheSky WallpaperDocument1 pageWeOwnTheSky WallpaperAmar ShahidPas encore d'évaluation

- Apple Space WallpaperDocument1 pageApple Space WallpaperAmar ShahidPas encore d'évaluation

- Samarskaya PaintingsDocument1 pageSamarskaya PaintingsAmar ShahidPas encore d'évaluation

- Archers Attacking Mid 13th-Early 14th C.Document1 pageArchers Attacking Mid 13th-Early 14th C.Amar ShahidPas encore d'évaluation

- STM32F103R6Document90 pagesSTM32F103R6王米特Pas encore d'évaluation

- MXL Data SheetDocument10 pagesMXL Data SheetMohamed MeeranPas encore d'évaluation

- VT Teddy BearDocument3 pagesVT Teddy BearSanyee DiehPas encore d'évaluation

- Demo Information and Execution Instructions: Gnostice Edocengine Demo NotesDocument7 pagesDemo Information and Execution Instructions: Gnostice Edocengine Demo NotesJavier MuñozPas encore d'évaluation

- Civil 3D 2014 Creating Alignments and ProfilesDocument13 pagesCivil 3D 2014 Creating Alignments and ProfilesBhavsar NilayPas encore d'évaluation

- Sharp Lc32wd1e LCDDocument202 pagesSharp Lc32wd1e LCDMarkPas encore d'évaluation

- Business Intelligence PDFDocument215 pagesBusiness Intelligence PDFBernardo CastilloPas encore d'évaluation

- ECOTOXicology Knowledgebase SystemDocument100 pagesECOTOXicology Knowledgebase SystemHigor LessaPas encore d'évaluation

- Lecture Guide 4 - Transfer Function and State-Space ModelsDocument3 pagesLecture Guide 4 - Transfer Function and State-Space ModelsMariella SingsonPas encore d'évaluation

- ESS reporting & analysis toolDocument9 pagesESS reporting & analysis toolHemavathi Hema100% (1)

- Jiwaji University Gwalior: Self Learning Material FORDocument359 pagesJiwaji University Gwalior: Self Learning Material FORVikas SharmaPas encore d'évaluation

- DLL Design Examples, Design Issues - TipsDocument56 pagesDLL Design Examples, Design Issues - TipsdinsulpriPas encore d'évaluation

- Brought To You By: Lawrence Miller, CISSPDocument86 pagesBrought To You By: Lawrence Miller, CISSPHermes Alejandro Rodríguez JiménezPas encore d'évaluation

- B DP Mail Exc Guide WinDocument254 pagesB DP Mail Exc Guide WinvamsiPas encore d'évaluation

- AZ-303 Exam - Free Actual Q&as, Page 1 - ExamTopicsDocument5 pagesAZ-303 Exam - Free Actual Q&as, Page 1 - ExamTopicsJosé Omar Atayde0% (1)

- Lesson 1 Comprog2Document21 pagesLesson 1 Comprog2api-288708232Pas encore d'évaluation

- Simulating Crop Impact of Climate Change Using DSSATDocument34 pagesSimulating Crop Impact of Climate Change Using DSSATroberta_silva_2100% (1)

- Kerio Control Adminguide en 9.2.8 3061Document352 pagesKerio Control Adminguide en 9.2.8 3061Nushabe CeferovaPas encore d'évaluation

- Types and Methods of Data TransmissionDocument5 pagesTypes and Methods of Data Transmission青木ケイPas encore d'évaluation

- Enforcing Microsoft Active Directory Policies Using LDAP Attribute MapsDocument34 pagesEnforcing Microsoft Active Directory Policies Using LDAP Attribute MapsKaddour El HallaouiPas encore d'évaluation

- Image Enhancement RestorationDocument74 pagesImage Enhancement RestorationDarsh Singh0% (1)

- Sod IvarDocument41 pagesSod IvarSacha's ChannelPas encore d'évaluation

- Philips Pm3295 Service ManualDocument322 pagesPhilips Pm3295 Service Manualglu7833Pas encore d'évaluation

- Civil Engineering Report GuidelinesDocument14 pagesCivil Engineering Report GuidelinesjinshadPas encore d'évaluation

- Aerogen Solo Parts ListingDocument2 pagesAerogen Solo Parts ListingBo ScoobmanPas encore d'évaluation

- The Official SAT Study GuideDocument26 pagesThe Official SAT Study GuideEllis BoatengPas encore d'évaluation

- BRKNMS-2573 (2020)Document120 pagesBRKNMS-2573 (2020)Paul ZetoPas encore d'évaluation

- Sample Camb Igcse Co Sci 001-013-So PDFDocument16 pagesSample Camb Igcse Co Sci 001-013-So PDFali002200Pas encore d'évaluation

- Akhilesh - 00318002719 - SynchronizationDocument7 pagesAkhilesh - 00318002719 - SynchronizationAman NagarkotiPas encore d'évaluation

- SLHT Grade 7 CSS Week 2Document6 pagesSLHT Grade 7 CSS Week 2princeyahwePas encore d'évaluation