Académique Documents

Professionnel Documents

Culture Documents

Embedded Software Design 25

Transféré par

Gamindu UdayangaDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Embedded Software Design 25

Transféré par

Gamindu UdayangaDroits d'auteur :

Formats disponibles

'

;

I

.. ..-:---.... .

,

I

I

.....

r

'

~ ~"~!!!,r.

Sri Lanka Institute of Information Technology

B.Sc. Special Honours Degree

In

Information Technology

(Computer Systems & Networking)

Mid-term Examination Year 2, Semester 2 (2009)

Embedded Software Design (252)

Duration: 1 Hour Thursday, 6th August 2009 (Time 11.00 a.m. - 12.00 noon)

Instructions to Candidates: This paper has 2 questions. Answer All Questions. Total Marks: 20. This paper contains 2 pages with cover page. PIC] 6F84 Instruction set and the SPR summary is provided separately. Retain these for subsequent lectures. Calculators are not allowed.

Page 1

1.

[Total:8 marks]

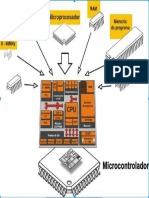

Write concise notes on the following to show your understanding of the function and operation in respect of the PIC 16F84 microcontroller. You may use a diagram to support your description. Hint: You may indicate - What is it? Where is it located? What is its function? a) FSR b) EEPROM c) RPO d) Instruction Pipeline

2.

[Total:12 marks] (a) In a PIC Microcontroller crystal oscillator frequency Jose is divided by 4 in order to calculate the instruction cycle rate. Explain using a diagram, why this is done. [Total:4 marks] (b) Write a program, which will set the memory area from h'20' to h'2f to 0 using indirect addressing. [Total:4 marks]

(c) Explain the difference between SPRs and GPRs.

[Total:2 marks] (d) What are the advantages of mirrored registers? Give at least 2 examples. [Total:2 marks] - End of paper-

Page 2

TABLE 21:

SPECIAL FUNCTION

REGISTER

FILE SUMMARY

Value on

Aclclr

Bank 0 00r01tit\OF

Name

Bit 7

Bit 6

Bit 5

Bit4

Bit 3

Bit 2

Bit 1

Bit 0

Power-On

RESET

Details on paae

Uses cooten.s of FSR 10 acorsss Data Mel'1ory (no: a physical reQister) 8-bit Real-Time ClocklCounter Low Order 8 brts of the Program Counter (PC) IRP RP1 R?O TO RA4lTOCKI RB4 PO

- - -- - - -xxxx xxxx

0000 0000

11 20 11

TMRO PCL STATUS(2) FSR PORTAI"I PORTS(61

021'

03h

Z

RA2 RS2

DC

RA1

04h Ol)h 0511

Indirect Data Mem~ry Address Pointer 0

RB7

RB6

RB5

RA3

RB3

RB1

lxxx xxxx xxxx RAO ---x xxxx RBDIINT XXXX xxxx

0001

,... '-,

e

11 16 18

OTh

EDATA EEADR PCL.l..TI-I INTCON INDF OPTION_REG PCl

STATUS

(2)

Unimptsmanted

location. read as '0'

xxx.x

XXX):

13.14 13.14 11 10 11

OBr

Otm

OA.h aSh

EEPROM Da1a Register =:::PROM Address Register

xxxx xxxx

Wrtte Buffer for upper 5 bits of the INTE RBIE TGIF

GIE

EEIE

TOlE

ce

Ci) RsrF

- --0 OCi00

0000

INTF regIster) PS1

'JOOx

- -- 1111 0000

Bank 1

801'

81r 82n

Uses Contents of FSR to address Dat;] Memory (not RBPU INTEDG TaCS TOSE PSA

a physical

PS2

- --PSO

1111 0000

9

11

low order 8 bits or Program Counter (PC}

IRP RP1 ROO TO PD Z DC C Indirect da:a memory address poi!':er 0

8.2or~,4r

occi

>:XXX - --1 1111

FSR -RISA 7RISB

lXX>: xxxx

1111 1111

e

11 16 18

8:~

85r

87h SSt'

EEIE

PO"T.,), Data Direction Regl$;sr

PORTB Data Direc.ion Register Unimplemented focation. read as '0'

WRERR 'NREN \'VR RD

---0

13 14 11 10

E:::CON1 EECON2 PClATH INTCON

GIE

TOlE

EEIF

xecc

.. ......

01)(,0

89"

OAll aSh

:::EPROM Control Register 2 (not a physical iaglster) Wnte buffer for upper 51lilS of !he PCP) JNTE RBIE TGIF INTF RBfF

..

.. _ .....

- --0 0(1)1)

'JO('X

Legend: x unknown. u uncoanceo. - = unlrnpternented, read as G'. q = value depends on condition Note 1: The oper by~eof the oroqrari counter Is not directly accessible. PCLA.TH is a slave register for PC<-12:8:o, The contents o PCLAJH can be transferred :0 the upper I)yte otthe oroora counter, but the contents of PC<12:8> are never transferred to ::>CLATH. 2: The TO and PO status bits in t ,e STATUS register are not affected b)' a MCLR Reset. 3: Other ( .on POW6Htp) RESETS include: extemal RESET through MC R and the watc dog Timer Reset 4: On any device RESET, these pins are configured as inp is. 5: TI)is Is the value U1a! will t)e JIl the con output latch.

Page 3

TABLE 7-2:

PIC16CXXX INSTRUCT10N

SET

14-Bit Opcocle Status Affected

II

Mnemonic, Operands

Description

Cycles MSb LSb

Notes

BYTEORIENTED ADD'NF A.f\D'/'.'F CL~F CL~'lv' C:JMF 'OECF OECFSZ INCF INCFSZ IOR'NF MOVF

FILE REGISTER

OPERATIONS

00 0111 0101

f. d

t. d

f

Add \IV anc f ."'NO W with f Clear r

Clear .",~

r. d

f.d f. d f. d f. d Cd f. d f

Como-emeut f

Decre'nen: Decremer,! f ', Sl<;;p if

1 1 1 1 1 1 1 (2) 1 1 12) 1 1 1 1 1 1 1 1

00

00 C'O 00

c-io r

0001 1001 0011 1')11 1,nD 1111 C'100 100e'

OOQO

00 00

00 C'O 00 00 00 00

MOV.'.F

il<OP

RL=

.

f. d f. d f.d f..d

RR"

SlB"'''''F S'IV:"PF XO~'I;F

Increment f Increment f. Skip if 0 Inclusive OR W wim f Mo\>e f Move'N to f No ooerauon Rotate Leftf through Carry Rotate Rlgh: f through Carfy Subtract W from f Swap nibbles in r Exdusive OR VI/ wl:h f BITORIENTED FILE REGISTER

dfff ffff c.uff ffff lttf fft!: xxxx 0= dfff fiff drff fftf dfff ffff dftf ffff dfff ffff dfff ffff dfff ffff Iff! tfff

C,OC,l

1.2 1.2

Z

Z

2

1.2 1,2

Z

Z

1.2.3

Z Z

Z

1.2

1.2.3

1.2 1,2

OOOD 1101 1100 0010 1110 011D

oxxo

dffE dfff dfff dfff dfft

(01)0

00

0) 00 00 00

r. d

f.b

Efff ffff fffE fffE ffff

C

C C.DC.l

1,2 1,2 1.2 1,2 1,2

OPERATIONS 1

01 01

BCF 8SF BTfSC BTFSS

f. b

L b

f.1l

Bit Bit Bit Bit

Clear r Set f Test f, Skip if Clear Test t, Skip if Set LITERAL AND CONTROL

1 1 [2J

1 (2)

01

01

CObo olbb lobb

11bb

pfff

bfff bfff

PffE

fHf fiff

ffff

1,2 1.2

ffff

C,DC,l Z TOPO

3 3

OPERATIONS 1

11

ADDL.."V AI\0 L'""

CALL CLR.'NDT GOTO IORLV'; r.Ir)VL'JI . RETFIE RET_.. R~T.JR" SLEEP SLSL"N XORLW Note

~

i<

1.;

1i

~ ~

><:

.

k

Ad~ literal and W AND lite 3' With "f'.' Call subroutine Clear V\,a:chOog T~mer Go to address Inclusive OR. 'iteralwith '."" r''''o~e literal to '/,' RI:i:urn rrorn imerrIJpt Re:u"n with 1i:eraln '1'1 Re:urn from subrocane Go ';1110 standl)Y Mode Subtract .. "'. frOM !rleral Excillsi'/e OR literal with V,,'

lllX

1001

11

10 0'1 10 11 11

2

1

ckkk

0000 1Jd:k 1000

lckkk kkkk kkkk kkkk kkkk kkkk

011Q DI00

2

1 1

2

kkkk

kkkk kr...kk

0000

ooxx

0(1)0 OllO'. 0,)00

kkkk JI'.kkk kkkk

1001

COO

11

2

2

1 1 1

kkkk

0000

kklck

1000

00

00 11 11

oco o 0110 i i ox kkkk

1010

0011

TOPD

kkkk

kkkk kkkk

C,DC.l Z

1: wnen an 110 register JS~odlfled as J functton ()f itself:: e.:;).,NOVE' PORTS. 1), the value used Will be that ... alue oreser: on the oins themselves. For example. if ~r,e oa:a latch is '1' for a p'n configured as inpu and is driven 10\1. I)y an e.<t..:rnal

2: 3: device, ~he oata Will be written bacK with a '0'. If .rns instruction is executed on 1'e TMRO register (and, wr-ere applicable. 0 = 1). the prescaler will oe cleared if Jssigned to :he T.merO MOdule. If .:>:-ogram Counter (PC) is modffied or a conditional test is true. the mstrucuon requires two cycles. The second cycle is executed as a J-!<)P

Page 4

Vous aimerez peut-être aussi

- Laboratory Introduction: 35 Instructions Same As Previous PIC Versions (Eg 16F74)Document12 pagesLaboratory Introduction: 35 Instructions Same As Previous PIC Versions (Eg 16F74)dhivakargunalanPas encore d'évaluation

- Apollo Training Telecommunication ProgramDocument132 pagesApollo Training Telecommunication ProgramuebriccPas encore d'évaluation

- F 818Document9 pagesF 818Eric YangPas encore d'évaluation

- Computer Architecture Questions CollectionDocument49 pagesComputer Architecture Questions CollectionrajshrimohanksPas encore d'évaluation

- MPC555Document27 pagesMPC555Mohammad Gulam AhamadPas encore d'évaluation

- M @-51 Instruction Set: Programmer'SDocument7 pagesM @-51 Instruction Set: Programmer'Swen_galsPas encore d'évaluation

- Questionsfrom PartbDocument2 pagesQuestionsfrom PartbSangeetha BajanthriPas encore d'évaluation

- CO Unit 2-2Document19 pagesCO Unit 2-2Aravinder Reddy Suram0% (2)

- Interrupts and Traps in Oberon-ARMDocument3 pagesInterrupts and Traps in Oberon-ARMmqt99311zwoho.comPas encore d'évaluation

- Pic Microcontroller: Technological University of The PhilippinesDocument15 pagesPic Microcontroller: Technological University of The PhilippinesRonnel Joseph Cooper Renedo100% (1)

- System Software Jan 2007 OldDocument2 pagesSystem Software Jan 2007 OldPrasad C MPas encore d'évaluation

- Computer Architecture: CSCE 350Document41 pagesComputer Architecture: CSCE 350kherberosPas encore d'évaluation

- Block Diagram of Processor (Harvard)Document48 pagesBlock Diagram of Processor (Harvard)Nichita IonutPas encore d'évaluation

- Week 04Document68 pagesWeek 04aroosa naheedPas encore d'évaluation

- PROJECT REPORT (Jan 3rd - Jan 8)Document7 pagesPROJECT REPORT (Jan 3rd - Jan 8)Rahul SampathPas encore d'évaluation

- Coa QaDocument25 pagesCoa QaHimanshu VermaPas encore d'évaluation

- LC3 1 1Document59 pagesLC3 1 1Kevin HarvardPas encore d'évaluation

- L-4rr-l/EEE Date: 25/09/2022Document50 pagesL-4rr-l/EEE Date: 25/09/2022Nure Alam DipuPas encore d'évaluation

- CH 08Document19 pagesCH 08adddataPas encore d'évaluation

- Exercise - 4: EE443 - Embedded SystemsDocument4 pagesExercise - 4: EE443 - Embedded SystemscraticPas encore d'évaluation

- M80C51FB Chmos Single-Chip 8-Bit Microcontroller: MilitaryDocument12 pagesM80C51FB Chmos Single-Chip 8-Bit Microcontroller: Militaryvsc2012Pas encore d'évaluation

- S K K B: Uresh UmarDocument141 pagesS K K B: Uresh UmarAnshu PatelPas encore d'évaluation

- Em 78 P 153 SNDocument53 pagesEm 78 P 153 SNAlonso CoradoPas encore d'évaluation

- Exam 1: EE319K Spring 2013 Exam 1 (Practice 1)Document6 pagesExam 1: EE319K Spring 2013 Exam 1 (Practice 1)SRITHA PPas encore d'évaluation

- Computer Organization July 2005 OldDocument2 pagesComputer Organization July 2005 OldPrasad C MPas encore d'évaluation

- Datasheet 7Document45 pagesDatasheet 7Hedenarol Ramirez RojasPas encore d'évaluation

- An Introduction To The PIC Microcontroller: EE2801 - Lecture 19Document9 pagesAn Introduction To The PIC Microcontroller: EE2801 - Lecture 19Reddy BabuPas encore d'évaluation

- CMC ArmDocument79 pagesCMC ArmMujikeer MohammedPas encore d'évaluation

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocument8 pagesCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhPas encore d'évaluation

- Name 1: Name 2: Name3: Name4: Name5Document2 pagesName 1: Name 2: Name3: Name4: Name5Mei QiiPas encore d'évaluation

- Lec 7 NotesDocument7 pagesLec 7 NotesJafar HussainPas encore d'évaluation

- Datasheet Em78p156epDocument28 pagesDatasheet Em78p156epDirk VandekerckhovePas encore d'évaluation

- Timer 2Document29 pagesTimer 2Cesar Matos100% (2)

- Spartan 2 e 07Document74 pagesSpartan 2 e 07Huzur AhmedPas encore d'évaluation

- uPF1 Monitor Program Listing (Original Scan)Document59 pagesuPF1 Monitor Program Listing (Original Scan)Jose Luis Abasolo MayorPas encore d'évaluation

- Coa Important QuestionsDocument49 pagesCoa Important QuestionsLet's LearnPas encore d'évaluation

- Lecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofDocument7 pagesLecture-31 6. Rcond: This Is A Conditional Return Statement. It Is Also A Part ofWilliamPas encore d'évaluation

- Section 6Document42 pagesSection 6Osvaldo PortoPas encore d'évaluation

- ARM Experiment ProgrammsDocument52 pagesARM Experiment ProgrammsShweta KulkarniPas encore d'évaluation

- Over Current ProctectionDocument25 pagesOver Current ProctectionSarah FrazierPas encore d'évaluation

- 03 PIC16F84A Assembly ProgrammingDocument29 pages03 PIC16F84A Assembly ProgrammingMarcos Marcelon Alcantara Abueva IIIPas encore d'évaluation

- New Embedded Manual 2020Document75 pagesNew Embedded Manual 2020malikabdullah1082Pas encore d'évaluation

- Solution: Computer OrganizationDocument6 pagesSolution: Computer OrganizationDavid Gutierrez AriasPas encore d'évaluation

- Arm7 ArchitectureDocument20 pagesArm7 ArchitectureCharitha CherryPas encore d'évaluation

- 4 Experiment 4 Interrupt and I/O InterfacingDocument17 pages4 Experiment 4 Interrupt and I/O InterfacingSuhas NipanePas encore d'évaluation

- Sap 1Document21 pagesSap 1Ramu AryanPas encore d'évaluation

- Milestone 2-UpdatedDocument13 pagesMilestone 2-UpdatedHưng Nguyễn ThànhPas encore d'évaluation

- Experiment 11 Implementation of Pass 1 of 2 Pass Assembler: Description of The ProblemDocument4 pagesExperiment 11 Implementation of Pass 1 of 2 Pass Assembler: Description of The Problemahmad ahmadPas encore d'évaluation

- CSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionDocument8 pagesCSDVCXVFDXGBVFDGFDFSDFGFDGFCGGCF Gjhghfgjjmgxjgdjpin No. Pin Name Description Alternate FunctionnareshhhhhPas encore d'évaluation

- Ee6008 Fiat QBDocument2 pagesEe6008 Fiat QBAthithyaPas encore d'évaluation

- Ee6008 Fiat QBDocument2 pagesEe6008 Fiat QBAthithyaPas encore d'évaluation

- Unit 4Document108 pagesUnit 4Rasool NayabPas encore d'évaluation

- Microcontroller Lab Manual 2018-19 5th SemDocument68 pagesMicrocontroller Lab Manual 2018-19 5th Semsandeep sPas encore d'évaluation

- PresentacionDocument23 pagesPresentacionMoises MPas encore d'évaluation

- Pic 16F84Document12 pagesPic 16F84Ingwaar RosensonPas encore d'évaluation

- Inside Macintosh Hardware 198502Document38 pagesInside Macintosh Hardware 198502Juan Felipe LondoñoPas encore d'évaluation

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationD'EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationPas encore d'évaluation

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysD'EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysPas encore d'évaluation

- Department of Examinations, Sri LankaDocument15 pagesDepartment of Examinations, Sri LankaGamindu UdayangaPas encore d'évaluation

- Design and Analysis of Algorithms 214.: Introduction To The C Programming LanguageDocument14 pagesDesign and Analysis of Algorithms 214.: Introduction To The C Programming LanguageGamindu UdayangaPas encore d'évaluation

- SlidesDocument115 pagesSlidesGamindu UdayangaPas encore d'évaluation

- Introduction To Algorithms: Design and Analysis of Algorithms 214Document42 pagesIntroduction To Algorithms: Design and Analysis of Algorithms 214Gamindu UdayangaPas encore d'évaluation

- Lecture 1 CMS 165: Introduction To The CourseDocument11 pagesLecture 1 CMS 165: Introduction To The CourseGamindu UdayangaPas encore d'évaluation

- Data Structures Question PaperDocument10 pagesData Structures Question PaperGamindu UdayangaPas encore d'évaluation

- DAA Final Examination 2005enDocument9 pagesDAA Final Examination 2005enGamindu UdayangaPas encore d'évaluation

- Design and Analysis of Algorithms 214.: Introduction To The C Programming LanguageDocument3 pagesDesign and Analysis of Algorithms 214.: Introduction To The C Programming LanguageGamindu UdayangaPas encore d'évaluation

- Design and Analysis of Algorithms 214.: Introduction To The C Programming LanguageDocument12 pagesDesign and Analysis of Algorithms 214.: Introduction To The C Programming LanguageGamindu UdayangaPas encore d'évaluation

- Sri Lanka Institute of Information Technology Unit Outline: Course IdentificationDocument7 pagesSri Lanka Institute of Information Technology Unit Outline: Course IdentificationGamindu UdayangaPas encore d'évaluation

- Tactics EbookDocument37 pagesTactics EbookGamindu Udayanga100% (6)

- Powered by HackerRank11Document3 pagesPowered by HackerRank11Gamindu UdayangaPas encore d'évaluation

- DAA Final Examination 2003enDocument10 pagesDAA Final Examination 2003enGamindu UdayangaPas encore d'évaluation

- DAA Final Examination 2002enDocument11 pagesDAA Final Examination 2002enGamindu UdayangaPas encore d'évaluation

- Giuoco Piano - Two Knights - Fried Liver (C57) : (Richard Westbrook, 2006)Document7 pagesGiuoco Piano - Two Knights - Fried Liver (C57) : (Richard Westbrook, 2006)Gamindu UdayangaPas encore d'évaluation

- IPC LinuxDocument58 pagesIPC LinuxGamindu UdayangaPas encore d'évaluation

- Foundations of The C++ Concurrency Memory Model: John Mellor-Crummey and Karthik MurthyDocument31 pagesFoundations of The C++ Concurrency Memory Model: John Mellor-Crummey and Karthik MurthyGamindu Udayanga100% (1)

- Maranaya Abiyasa Nosali SitinataDocument197 pagesMaranaya Abiyasa Nosali SitinataGamindu UdayangaPas encore d'évaluation

- Create A SocketDocument20 pagesCreate A SocketGamindu UdayangaPas encore d'évaluation

- Koha PluginDocument6 pagesKoha PluginGamindu UdayangaPas encore d'évaluation

- Preparing For Your Python Interview - The Basics - Techwers (Your Technical Interview Book 2) - KT LindemannDocument83 pagesPreparing For Your Python Interview - The Basics - Techwers (Your Technical Interview Book 2) - KT LindemannGamindu UdayangaPas encore d'évaluation

- Dokumen - Tips - Upto 145kv 40ka 3150a Operating Manual 56327f822540fDocument64 pagesDokumen - Tips - Upto 145kv 40ka 3150a Operating Manual 56327f822540fSerik ZhilkamanovPas encore d'évaluation

- Education: Professional ProfileDocument1 pageEducation: Professional ProfileAditya PandeyPas encore d'évaluation

- Congestion Management in Power Transmission Network Under Line Interruption Condition Using TCSCDocument7 pagesCongestion Management in Power Transmission Network Under Line Interruption Condition Using TCSCDr. Gollapalli NareshPas encore d'évaluation

- Piranha P90-1990 ManualDocument48 pagesPiranha P90-1990 Manualtayger0% (1)

- Manual - SS4x4 Stereo Matrix SwitcherDocument20 pagesManual - SS4x4 Stereo Matrix SwitcherDoan Cong NguyenPas encore d'évaluation

- Asus X555LD (Repair Guide) PDFDocument7 pagesAsus X555LD (Repair Guide) PDFMrOne260Pas encore d'évaluation

- Sepic Converter: Prepared ByDocument30 pagesSepic Converter: Prepared BychaitanyaPas encore d'évaluation

- AC Generator Reverse KVAr IssueDocument14 pagesAC Generator Reverse KVAr IssueMURALIPas encore d'évaluation

- PIEAS M.S 2014 QuestionsDocument11 pagesPIEAS M.S 2014 QuestionsZohaib Alam Warraich100% (1)

- Kenwood Car Speaker KDC-MP155U PDFDocument44 pagesKenwood Car Speaker KDC-MP155U PDFRenato FigueroaPas encore d'évaluation

- Lock Picking Hotel RoomsDocument22 pagesLock Picking Hotel Roomsbiffbuff99Pas encore d'évaluation

- Load Center: Safe, Reliable and High QualityDocument36 pagesLoad Center: Safe, Reliable and High Qualitydheyab farajPas encore d'évaluation

- 2551 Blind Rev 17 English ManualDocument16 pages2551 Blind Rev 17 English ManualKadek Dwi PermanaPas encore d'évaluation

- 940 - Lenza Drive User ManualDocument66 pages940 - Lenza Drive User Manualtomjordan12321Pas encore d'évaluation

- Switchsync™ PWC600: Product GuideDocument16 pagesSwitchsync™ PWC600: Product GuideAlan ZanzeriPas encore d'évaluation

- Trident Ltd. Budhni, Madhya Pradesh (Site Analysis) .XLSX (03-07-2023 00-00-00 - 03 - 07 - 2023 23 - 59 - 59)Document19 pagesTrident Ltd. Budhni, Madhya Pradesh (Site Analysis) .XLSX (03-07-2023 00-00-00 - 03 - 07 - 2023 23 - 59 - 59)Gyanesh BhujadePas encore d'évaluation

- Lovit ResumeDocument3 pagesLovit ResumeanmolPas encore d'évaluation

- Physics of Power Dissipation in CMOSDocument24 pagesPhysics of Power Dissipation in CMOSMahendra Babu100% (1)

- Quick Calibration Procedure DHC 100Document4 pagesQuick Calibration Procedure DHC 100oliverttPas encore d'évaluation

- MCDC3006 V2.5 DFFDocument2 pagesMCDC3006 V2.5 DFFSaasiPas encore d'évaluation

- KamruzzamanDocument3 pagesKamruzzamanRezoan Raz0% (1)

- Relay Interlocking (Metal - Carbon Relays)Document276 pagesRelay Interlocking (Metal - Carbon Relays)Aaditya PrakashPas encore d'évaluation

- Mux Demux Encoder DecoderDocument18 pagesMux Demux Encoder Decoderaryan.bhosale002Pas encore d'évaluation

- Noise Reduction For Periodic Signals Using High-Resolution Frequency AnalysisDocument19 pagesNoise Reduction For Periodic Signals Using High-Resolution Frequency Analysismahdi cheginiPas encore d'évaluation

- 3.1.1.1 Video Demonstration - BIOS - UEFI MenusDocument2 pages3.1.1.1 Video Demonstration - BIOS - UEFI Menusillus fitriyahPas encore d'évaluation

- Project OverviewDocument3 pagesProject OverviewtungluongPas encore d'évaluation

- Service Manual: Compact Component SystemDocument93 pagesService Manual: Compact Component Systemsaputra ekaPas encore d'évaluation

- 3 Sampling PDFDocument20 pages3 Sampling PDFWaqas QammarPas encore d'évaluation

- MCB (Miniature Circuit Breaker) : CharacteristicsDocument8 pagesMCB (Miniature Circuit Breaker) : CharacteristicsWael AlmassriPas encore d'évaluation

- Pirith PothaDocument3 pagesPirith PothaAmila Viraj Gunarathna100% (2)