Académique Documents

Professionnel Documents

Culture Documents

Fan9612 Boost Converter Design Tool

Transféré par

Alonso CoradoCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Fan9612 Boost Converter Design Tool

Transféré par

Alonso CoradoDroits d'auteur :

Formats disponibles

FAN9612 Boost Converter Design Tool

This design tool is used for a PFC pre-regulated boost converter design using the FAN9612 Interleaved Dual BCM PFC Controller. It complements the Quick Setup Guide procedure in the FAN9612 datasheet and the design procedure described in AN-8086 the application note for FAN9612. This tool is meant to be used with both documents. The FAN9612 Design Tool consists of three steps. Each step is contained in a separate worksheet that can be accessed from the tabs at the bottom. Step 1: Enter their desired power supply performance specifications. The worksheet then calculates the ideal component values based on the input specifications. Step 2: Select real component values based on the ideal component values calculated in Step 1. The worksheet then calculates the real power supply performance specifications. Final Step: The third and final step provides an overview of the schematic and components selected. A loop gain Bode Plot is shown as well to conclude the design.

DISCLAIMER:

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT, CIRCUIT OR TOOL DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

Note: No macros or code was used in the Design Tool in an effort to provide simple, efficient and safe tools.

Project

For Designer Use Only

Designer Date

2009 Fairchild Semiconductor Corporation. All rights reserved. Rev. 2.0.0 07/24/2009 Smith, Guo

www.fairchildsemi.com

FAN9612 Boost Converter (Ideal Values)

Step 1: Enter power supply parameters and calculate ideal component values. This sheet calculates the ideal component values based on the power supply specifications that are entered. Enter the specifications in the 'From Power Supply Specification' section. The 'Pre-calculated Power Stage Parameters' section allows the user to adjust the estimated conversion efficiency and the turns ratio of the boost inductor to auxiliary winding. This section also displays the power stage components and parameters that result from the specification, and will be used to calculate the remaining component values. The 'Calculated Component Values' section displays the remaining ideal component values that result from the entered power supply specification. These values will be used as a guide in selecting the real component values.

From Power Supply Specification: Min. AC RMS Input (turn-on) Min. AC RMS Input (turn-off) Nominal AC RMS Input Max. AC RMS Input Min. Line Frequency Nominal DC Output Output Voltage Ripple (2 fLINE) Latching Output OVP Full Load Output Power Soft Start dVOUT/dt Desired Hold Up Time Pre-Calculated Parameters: Estimated Conversion Efficiency Turns Ratio (NBOOST / NAUX) Output Capacitance Boost Inductance per Channel Output Power per Channel Max. Output Power per Channel Max. On-Time per Channel Other Variables Used During the Calculations: Peak Inductor Current Max. DC Output Current (to load) Calculated Component Values: Zero Current Detect Resistor Bypass Capacitor for 5V Bias Maximum On-time Set Soft-Start Capacitor Compensation Capacitor Compensation Resistor Compensation Capacitor Feedback Divider Feedback Divider Over Voltage Sense Divider VLINE.ON VLINE.OFF VLINE.Norminal VLINE.MAX fLINE,MIN VOUT VOUT,RIPPLE VOUT,LATCH POUT dVOUT/dt tHOLD N COUT L POUT,CH PMAX,CH tON,MAX 73 V 70 V 110 V 265 V 50 Hz 400 V 8V 468 V 400 W 1.500 V/ms 20.00 ms 0.95 10 398 F 175 H 200 W 260 W 19.565 s Line OVP Voltage Min. Allowable Brown-Out Hysteresis VLINE,OVP Vline,Hyst 280 V 3.1 V Min. DC Output (end of tHOLD) Min. Switching Frequency Max. DC Bias (for FAN9612) Voltage Loop Crossover Frequency Feedback Pole Frequency Feedback Power Dissipation OVP Network Power Dissipation VIN Sense Power Dissipation Power Supply Over design VOUT,MIN fSW,MIN VDDMAX 330 V 50 kHz 15.00 V 6.0 Hz 150 Hz 0.150 W 0.100 W 0.070 W 1.30

fc

fHFP PFB POVP PINSNS KMAX

IL,PK IO,MAX RZCD1, RZCD2 C5VB RMOT CSS CCOMP,LF RCOMP CCOMP,HF RFB1 RFB2 ROV1

11.059 A 1.300 A 46.80 k 0.220 F 85.07 k 444 nF 336 nF 78.85 k 13.5 nF 1058.7 k 8.00 k 2173.9 k Over Voltage Sense Divider Input Voltage Sense Divider Input Voltage Sense Divider Brown-Out Hysteresis Set Input Voltage Sense Filter Capacitor Gate Drive Resistor Bypass Capacitor for VDD - HF Startup Energy Storage for VDD Current Sense Resistor Current Sense Resistor Power ROV2 RIN1 RIN2 RINHYST CINF RG1, RG2 CVDD1 CVDD2 RCS1, RCS2 PRCS1, PRCS2 16.38 k 2219.1 k 20.93 k 0.00 k 9.6 nF 15.00 2.2 F 22 F 0.0181 0.437 W

Note: Cells that have white text on a red background indicate that there is an error. Certain parts of the circuit will not operate properly if these items are not addressed.

Project

For Designer Use Only

Designer Date

2009 Fairchild Semiconductor Corporation. All rights reserved. Rev. 2.0.0 07/24/2009 Smith, Guo

www.fairchildsemi.com

FAN9612 Boost Converter (Actual Values)

Step 2: Select real component values based on the ideal component values calculated in Step 1 and verify the real power supply performance specifications. This sheet calculates the actual parameter values that result from the selected components. Ensure that all parameters were entered properly in the Step 1 worksheet before working on this step. Enter the component values into the column named 'Selection'. Calculated component values from the parameters entered in Step 1 and Step 2 appear in the ' Calculated' column. These values provide a recommended component value to obtain the input parameters desired. The 'Actual Value' column provides the parameter values that result from the components selected in the 'Selection' column. For reference and comparison, the 'Input Value' column displays the parameters that were selected in the Step 1 worksheet.

1 - Select the feedback components

Component RFB1 RFB2 Component ROV1 ROV2 Component RIN1 RIN2 RINHYST CINF Component RMOT Component L Selection 1066.0 k 8.06 k Selection 2190.0 k 16.50 k Selection 2226.0 k 21.00 k 0.00 k 10.0 nF Selection 84.50 k Selection 180 H Calculated 1058.7 k 8.00 k Calculated 2173.9 k 16.38 k Calculated 2219.1 k 20.93 k 0.00 k 9.5 nF Calculated 85.1 k Calculated 175 H Parameter VOUT PFB Parameter VOUTLATCH POVNOM Parameter VLINEOFF VLINEON PINSNSMAXLINE fcINF Parameter tONMAX Parameter PMAXCH IOPK fSWMIN Parameter ILPK Parameter VOUTRIPPLE tHOLD VOUTMIN Parameter fc fHFP Actual Value 399.8 V 0.149 W Actual Value 468.0 V 0.072 W Actual Value 70.0 V 73.1 V 0.063 W 757.9 Hz Actual Value 19.435 s Actual Value 251 W 1.257 A 50.3 kHz Actual Value 10.000 A Actual Value 7.238 V 28.006 ms 351.4 V Actual Value 6.0 Hz 155.8 Hz Input Value 400.0 V 0.150 W Input Value 468.0 V 0.100 W Input Value 70.0 V 73.0 V 0.070 W 795.8 Hz Input Value 19.565 s Input Value 260 W 1.300 A 50 kHz Input Value 11.059 A Input Value 8.000 V 20.000 ms 330.0 V Input Value 6.0 Hz 150.0 Hz

2 - Select the latching output OVP components

3 - Select the input sense components

4 - Select the maximum on time resistor

5 - Select the boost inductors

6 - Select the current sense resistors

Component RCS1, RCS2 Component COUT Selection 0.020 Selection 440 F Calculated 0.0187 Calculated 398 F

7 - Select the output capacitance

8 - Select the compensation network components

Component CCOMP,LF RCOMP CCOMP,HF Component CSS Component RG1, RG2 Component RZCD1, RZCD2 Selection 390 nF 68.1 k 15 nF Selection 470 nF Selection 15.00 Selection 47.50 k Calculated 368 nF 68.01 k 16 nF Calculated 444 nF Calculated 15.00 Calculated 46.80 k Parameter dVOUT/dt Parameter IGD Parameter IZCD Actual Value 1.418 V/ms Actual Value 1.00 A Actual Value 0.985 mA Input Value 1.500 V/ms Input Value 1.00 A Input Value 1.000 mA

9 - Select the soft start capacitor

10 - Select the gate drive resistors

11 - Select the zero current detect resistors

Note: Cells that have white text on a red background indicate that there is an error. Certain parts of the circuit will not operate properly if these items are not addressed. Cells with red text indicate that the parameter values calculated differ greatly from the desired value. Project Designer Date

www.fairchildsemi.com

For Designer Use Only

2009 Fairchild Semiconductor Corporation. All rights reserved. Rev. 2.0.0 07/24/2009 Smith, Guo

FAN9612 Boost Converter (Final Components)

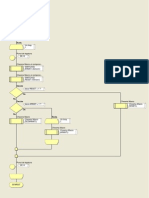

Final Step: Review the final component values. This sheet provides a schematic and an overview of the components selected through Steps 1 and 2. Ensure that both steps have been completed properly before using the component values displayed below.

VIN VLINE RIN1 RZCD2 RZCD1 AC IN FAN9612

1

L2a D2 L2b L1a

VOU

CIN

D1

L1b RFB1

EMI Filter RIN2 C5VB

ZCD1 ZCD2 5VB MOT AGND SS COMP FB

CS1 16 CS2 15 VDD 14 DRV1 13 DRV2 12 PGND 11 VIN 10 OVP

9 RCS1 RCS2

2 3 4

VBIAS

Q1

RFB2

RINHYST

RMOT CSS RCOMP CCOMP,LF CCOMP,HF

8 5 6 7

RG1 RG2

Q2

ROV1

CVDD1 CINF

CVDD2

ROV2

Selected Component Values: Output Capacitance (total) Boost Inductance (per channel) Zero Current Detect Resistor Bypass Capacitor for 5V Bias Maximum On-time Set Soft-Start Capacitor Compensation Capacitor Compensation Resistor Compensation Capacitor Feedback Divider Feedback Divider COUT L1, L2 RZCD1, RZCD2 C5VB RMOT CSS CCOMP,LF RCOMP CCOMP,HF RFB1 RFB2 440 F 180 H 47.5 k 0.220 F 84.5 k 470 nF 390 nF 68.1 k 15.0 nF 1066 k 8.1 k Over Voltage Sense Divider Over Voltage Sense Divider Input Voltage Sense Divider Input Voltage Sense Divider Brown-Out Hysteresis Set Input Voltage Sense Filter Capacitor Gate Drive Resistor Bypass Capacitor for VDD - HF Startup Energy Storage for VDD Current Sense Resistor Current Sense Resistor Power ROV1 ROV2 RIN1 RIN2 RINHYST CINF RG1, RG2 CVDD1 CVDD2 RCS1, RCS2 PRCS1, PRCS2

Note: Cells that have white text on a red background indicate that there is an error and the component value cannot be displayed.

Project

For Designer Use Only

Designer Date

2009 Fairchild Semiconductor Corporation. All rights reserved. Rev. 2.0.0 07/24/2009 Smith, Guo

www.fairchildsemi.c

ost Converter (Final Components)

mponents selected through Steps 1 and 2. e using the component values displayed below.

L2a D2 L2b L1a VOUT

D1 COUT

FAN9612

CS1 16 CS2 15 VDD 14 DRV1 13 DRV2 12 PGND 11 VIN 10 OVP

9

L1b RFB1

VBIAS

Q1

RFB2

RG1 RG2

Q2

ROV1

RCS1

RCS2

CVDD1 CINF

CVDD2

ROV2

Selected Component Values: 2190 k 16.5 k 2226 k 21.0 k 0.0 k 10 nF 15.00 2.2 F 22 F 0.0200 0.395 W

there is an error and the component value cannot be displayed.

www.fairchildsemi.com

FAN9612 Boost Converter

Final Step: Review the loop transmission Bode Plot. This sheet provides colsed-loop gain Bode Plot based on components being calculated in step 1 and 2. DC Output Current 1.0 A

Loop Transmission Bode Plot - Magnitude

60

40 20

Magnitude (dB)

0 -20

-40

-60 -80 -100 -120 0.1 1 10 100 Frequency (Hz) 1000 10000

Loop Transmission Bode Plot - Phase

100 90

80 70 Phase (deg) 60

50 40 30 20 10 0 0.1 1 10 100 Frequency (Hz)

6.31 Hz 59.67 deg

1000

10000

Crossover Frequency Phase Margin

Note: This spreadsheet uses complex number, so Analysis ToolPak installation is required. Project

For Designer Use Only

Designer Date

2009 Fairchild Semiconductor Corporation. All rights reserved. Rev. 2.0.0 07/24/2009 Smith, Guo

www.fairchildsemi.com

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Mercruiser Service Manual GM V6 4.3 CompleteDocument895 pagesMercruiser Service Manual GM V6 4.3 CompletePaul Chuon94% (16)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- TANCET Entrance ME EEE, ECE, CSE Exam Book OnlineDocument3 pagesTANCET Entrance ME EEE, ECE, CSE Exam Book Onlinesura books100% (1)

- Themaclassic F30E and F30E SB Instructions For Use Installation and ServicingDocument52 pagesThemaclassic F30E and F30E SB Instructions For Use Installation and ServicingAlonso CoradoPas encore d'évaluation

- Draw On Google Earth and Export The Objects To AutoCAD - DevCADLispDocument14 pagesDraw On Google Earth and Export The Objects To AutoCAD - DevCADLispAlonso CoradoPas encore d'évaluation

- Panel ATS/AMF (ATSLER) Dengan Menggunakan 3 Sumber Listrik Secara Otomatis Agar Tidak Kehilangan DayaDocument9 pagesPanel ATS/AMF (ATSLER) Dengan Menggunakan 3 Sumber Listrik Secara Otomatis Agar Tidak Kehilangan DayaoppinokioPas encore d'évaluation

- Alarma Garaj Rev1Document2 pagesAlarma Garaj Rev1Alonso CoradoPas encore d'évaluation

- STEP 7 - Function Block Diagram For S7-300 and S7-400Document220 pagesSTEP 7 - Function Block Diagram For S7-300 and S7-400ntrtfPas encore d'évaluation

- Yamaha FZ6-SS (SSC) 2004 Service ManualDocument432 pagesYamaha FZ6-SS (SSC) 2004 Service ManualBivol LeonidPas encore d'évaluation

- Saunier Duval Thema Classic F24e Installation ManualDocument52 pagesSaunier Duval Thema Classic F24e Installation ManualProAndyPas encore d'évaluation

- Yamaha FZ6-SS (SSC) 2004 Service ManualDocument432 pagesYamaha FZ6-SS (SSC) 2004 Service ManualBivol LeonidPas encore d'évaluation

- 4cell Lion Charger-UnprotectedDocument30 pages4cell Lion Charger-UnprotectedAlonso CoradoPas encore d'évaluation

- Lift Control Using Siemen'S PLC: Bachelor of Technology IN Electrical and Electronics EngineeringDocument52 pagesLift Control Using Siemen'S PLC: Bachelor of Technology IN Electrical and Electronics EngineeringConstantin TomuleseiPas encore d'évaluation

- MC 33879Document23 pagesMC 33879Alonso CoradoPas encore d'évaluation

- Yamaha FZ6-SS (SSC) 2004 Service ManualDocument432 pagesYamaha FZ6-SS (SSC) 2004 Service ManualBivol LeonidPas encore d'évaluation

- SD6109Document10 pagesSD6109Alonso Corado100% (1)

- Samsung 713BNDocument46 pagesSamsung 713BNAlonso CoradoPas encore d'évaluation

- Technical Manual Pellet StovesDocument29 pagesTechnical Manual Pellet StovesAlonso CoradoPas encore d'évaluation

- 4DCAPE-70T Datasheet R 1 1Document11 pages4DCAPE-70T Datasheet R 1 1Alonso CoradoPas encore d'évaluation

- Cpe323 AssemblyLanguageProgReaderDocument6 pagesCpe323 AssemblyLanguageProgReaderAlonso CoradoPas encore d'évaluation

- TL866 Programmer Firmware Generator and UpdaterDocument9 pagesTL866 Programmer Firmware Generator and UpdaterAlonso CoradoPas encore d'évaluation

- Installing and configuring a Graphtec MP303-04 plotterDocument5 pagesInstalling and configuring a Graphtec MP303-04 plotterAlonso CoradoPas encore d'évaluation

- 1271a-Oscilador de FuenteDocument21 pages1271a-Oscilador de FuenteOrlando Dumas FrancoPas encore d'évaluation

- Alarma GarajDocument1 pageAlarma GarajAlonso CoradoPas encore d'évaluation

- 4DCAPE-43T Datasheet R 1 4Document10 pages4DCAPE-43T Datasheet R 1 4Alonso CoradoPas encore d'évaluation

- HP Pavilion Dv6 Dv7 Quanta Ut12 Rev 1a SCHDocument48 pagesHP Pavilion Dv6 Dv7 Quanta Ut12 Rev 1a SCHAlonso CoradoPas encore d'évaluation

- Steca PV Off Grid enDocument31 pagesSteca PV Off Grid enAlonso CoradoPas encore d'évaluation

- FSC v5535 z17mDocument31 pagesFSC v5535 z17mAlonso CoradoPas encore d'évaluation

- DeltaSol BS Plus - MonusDocument24 pagesDeltaSol BS Plus - MonusAlonso CoradoPas encore d'évaluation

- Grundfosliterature SP 125 LDocument7 pagesGrundfosliterature SP 125 LAlonso CoradoPas encore d'évaluation

- DeltaSol BS Plus V2.MonenDocument52 pagesDeltaSol BS Plus V2.MonenAlonso CoradoPas encore d'évaluation

- Datakom 309 ManualDocument63 pagesDatakom 309 ManualSalvador Millán Estrada100% (1)

- Manual S7-300Document574 pagesManual S7-300Caloã BoldriniPas encore d'évaluation

- Soft Starters Lovato PDFDocument9 pagesSoft Starters Lovato PDFamdatiPas encore d'évaluation

- Serial Communication Protocols GuideDocument32 pagesSerial Communication Protocols GuideVissu Sweet100% (1)

- SCT7272 PL0115Document2 pagesSCT7272 PL011510aer007Pas encore d'évaluation

- Sony Ta Fe610r ManualDocument20 pagesSony Ta Fe610r ManualbogdanovicPas encore d'évaluation

- Control and Analysis of Unified Power Flow Controller: by K. Vimalagouri HT - NO: 13U01D4308 M. TECH (Power Electronics)Document32 pagesControl and Analysis of Unified Power Flow Controller: by K. Vimalagouri HT - NO: 13U01D4308 M. TECH (Power Electronics)VimalaKattamPas encore d'évaluation

- DSL Repair Dis Cas Codes 2013Document6 pagesDSL Repair Dis Cas Codes 2013Adrian EladPas encore d'évaluation

- KLV S23a10 PDFDocument109 pagesKLV S23a10 PDFmg139Pas encore d'évaluation

- Band Pass Filter Design for 2m Ham RadioDocument5 pagesBand Pass Filter Design for 2m Ham RadioBoban JovanovicPas encore d'évaluation

- 42pfl9903h 10 Pss EnggbDocument3 pages42pfl9903h 10 Pss EnggbtehnotrendPas encore d'évaluation

- CAT-1002 MR-2605 Five Zone Fire Alarm Control PanelDocument6 pagesCAT-1002 MR-2605 Five Zone Fire Alarm Control PanelAlex CristobalPas encore d'évaluation

- Rohit HardiaDocument7 pagesRohit HardiaRohit HardiaPas encore d'évaluation

- Vt-Vrpa2-5 - 1XRTPDocument8 pagesVt-Vrpa2-5 - 1XRTPPanca AriefPas encore d'évaluation

- Fas - Ul.p.3.013 HCP PDFDocument2 pagesFas - Ul.p.3.013 HCP PDFShashish AshuPas encore d'évaluation

- RCA CTC185C2-3 (4219) EfDocument15 pagesRCA CTC185C2-3 (4219) Efapi-19523062Pas encore d'évaluation

- CD54HC74, CD74HC74, CD54HCT74, CD74HCT74: Dual D Flip-Flop With Set and Reset Positive-Edge TriggerDocument12 pagesCD54HC74, CD74HC74, CD54HCT74, CD74HCT74: Dual D Flip-Flop With Set and Reset Positive-Edge TriggerMarcos Sanchez RosalesPas encore d'évaluation

- AIWA 4ZG-1 (Chipset SONY) SvcMnlsDocument18 pagesAIWA 4ZG-1 (Chipset SONY) SvcMnlsavrelecPas encore d'évaluation

- Na555, Ne555, Sa555, Se555Document27 pagesNa555, Ne555, Sa555, Se555faracuvintePas encore d'évaluation

- Magnetic Resonant Coupling Based Wireless PowerDocument7 pagesMagnetic Resonant Coupling Based Wireless PowerHartantoPas encore d'évaluation

- Ece3002 Vlsi System Deign Cocob 2019Document3 pagesEce3002 Vlsi System Deign Cocob 2019Debasis ChandraPas encore d'évaluation

- Chapter 2Document54 pagesChapter 2Ankit SinghPas encore d'évaluation

- EasyRET 18-port 1L4H FDD/3.3-3.8GHz 8T8R TDD Antenna SpecificationsDocument5 pagesEasyRET 18-port 1L4H FDD/3.3-3.8GHz 8T8R TDD Antenna SpecificationsRobert100% (1)

- Soft Start Circuit For Peak Current Mode DC-DC ConverterDocument5 pagesSoft Start Circuit For Peak Current Mode DC-DC ConverterHassan SharghiPas encore d'évaluation

- Manual BMS 16SDocument17 pagesManual BMS 16SPrabha Karan.n100% (1)

- Embedded Controlled Drip Irrigation SystemDocument5 pagesEmbedded Controlled Drip Irrigation SystemInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- Simplex 4100-0005Document4 pagesSimplex 4100-0005vlaya1984100% (1)

- Vented. Box Loudspeaker Systems Part I1: Large-Signal AnalysisDocument7 pagesVented. Box Loudspeaker Systems Part I1: Large-Signal AnalysisEclys MontenegroPas encore d'évaluation

- BB910 PDFDocument5 pagesBB910 PDFAngelica Gómez100% (1)

- LM Micro PLC Hardware ManualDocument122 pagesLM Micro PLC Hardware Manuallalo7812Pas encore d'évaluation