Académique Documents

Professionnel Documents

Culture Documents

CoursPolyLE2012011 2012

Transféré par

aymendabTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

CoursPolyLE2012011 2012

Transféré par

aymendabDroits d'auteur :

Formats disponibles

LE201

Cours dlectronique numrique

C. Dahon

Enseignant-Chercheur

1

re

partie

A.Gensbittel

Enseignant-Chercheur

2

me

partie

2

me

semestre 2011-2012

Enseignants

Cours TD TP

C. Dahon C. Dahon A. Gensbittel

A. Gensbittel F. Valette T. Hezard

J . Denoulet Z. Djeffal

T. Hezard N. Payet

E. Awwad

T. Ann

M. Torres

M. Terosiet

Attention : prsence aux TP obligatoire

1 absence injustifie = interdiction de passer lexamen

au maximum 2 absences justifies tolres

Evaluation des connaissances

2 Examens rpartis

1 le 26 mars 16h (partie combinatoire),

1 la fin de lUE (ensemble du programme)

Le contrle de TP

la fin des 5 sances

Le Mini-Projet

Evaluation durant le TP (prparations)

Soutenance orale

Evaluation des connaissances :

coefficients

Note Finale F :

F = 0,65 Ecr + 0,35 TP

Ecr=(0,3 Ecr1 + 0,35 Ecr2)

Avec : Ecr1 et Ecr2 les notes des 2 examens rpartis

TP est la note des travaux pratiques (mini-projet

+contrle de TP)

Note sur 35 :

10 pour la soutenance orale du mini-projet,

10 pour la prparation des sances de TP et lavancement

du projet,

15 pour le contrle de TP

Polycopis de TD et TP

Disponibles la reprographie

ds cette semaine

2

me

tage - btiment Esclangon

Horaires : 12 h 45 - 14 h 15

Lundi - Mercredi - Vendredi

A avoir avant le TD !

http://www.licence.elec.upmc.fr/fr/01_Licence_

generale/01_L2/CONTENU/documents/le201.p

hp

L2 /Documents et liens pdagogiques/ page

du LE201

Plan du cours

Introduction

Codage et Algbre de Boole

Introduction au vhdl

Fonctions Combinatoire Simples

Fonctions Combinatoires Complexes

Fonctions Squentielles Simples

Fonctions Squentielles Complexes

Pipeline

Technologie des circuits numriques

Les Convertisseurs Analogiques-

Numriques et Numriques-Analogiques

Introduction

Numrique (dfinition de Wikipedia)

L'adjectif numrique qualifie toute donne

ou variable dont les valeurs sont des

nombres. Lorsque l'ensemble des valeurs

n'est pas continu, on dit qu'il est discret.

Dans ce cas, il peut mme tre limit

quelques chiffres

Introduction

Un systme numrique est un systme qui utilise

les nombres, bien souvent le systme binaire,

afin dacqurir, de traiter, de transmettre, de stocker

ou dafficher des informations (ou donnes),

plutt quun spectre continu de valeurs (un systme

analogique).

Systmes numriques historiques :

Une balise lumineuseavec deux tats (marche et arrt).

Les signaux de fumeo un porteur analogique (la fume) est module par

une couverture afin de gnrer un signal numrique qui transporte les informations.

Le code Morseemploie cinq tats numriques : point, trait, petite pause,

moyenne pause, et longue pause, afin denvoyer des messages en utilisant une varit

de porteurs diffrents tels que llectricit, ou la lumire.

Cours delectronique numerique

Introduction

Un peu dhistoire ... Le boulier chinois

Cours delectronique numerique

Introduction

Un peu dhistoire ... La machine de Babbage

Cours delectronique numerique

Introduction

Un peu dhistoire ... Une Lampe Triode

Cours delectronique numerique

Introduction

Un peu dhistoire ... Le transistor de 1947

Cours delectronique numerique

Introduction

Un peu dhistoire ... Le 4004 dIntel

Cours delectronique numerique

Introduction

Un peu dhistoire ... Le 4004 dIntel

Cours delectronique numerique

Introduction

Aujourdhui : Un Monde Numerique ?

Cours delectronique numerique

Introduction

Aujourdhui : Un Monde Numerique ?

Informatique :

Micro-Processeur

Processeur Graphique

Processeur Audio

Internet

Jeux

Bureautique

Calcul Scientifique

...

Cours delectronique numerique

Introduction

Aujourdhui : Un Monde Numerique ?

Tlcommunications :

MicroControleur Basse Consommation

Son

Transmission dimage

Internet

UMTS => Transmission Vido

Radio Logicielle

...

Cours delectronique numerique

Introduction

Aujourdhui : Un Monde Numerique ?

Automobile :

Plusieurs MicroProcesseurs

Scurit Active et Passive

Rendement du Moteur

Confort

MultiMdia

...

Cours delectronique numerique

Introduction

Aujourdhui : Un Monde Numerique ?

Le monde numerique est un monde discretise

Le monde reel est un monde continu

Le monde nest pas numerique

Alors pourquoi lelectronique numerique ?

Discretisation permet de se premunir du bruit

Il est possible de quantier les erreurs

Possibilite de mise en oeuvre dune arithmetique basee sur la

logique

Cours delectronique numerique

Codage

Codage

Codage

Cours delectronique numerique

Codage

Codage

Syst`eme de base : codage decimal

Conversion decimal-binaire et binaire-decimal

n 2

n

= 10, necessite codage octal ou hexadecimal

Codage DCB : Decimal Code Binaire

Code de Gray ou binaire reechi

Code ASCII

Cours delectronique numerique

Codage

Conversion binaire-decimal

La conversion binaire-decimal seectue simplement en

realisant la somme des bits ponderes par leur position

n1

i =0

b

i

2

i

o` u b

i

est la valeur du bit de position i

Nombre Binaire 1 0 1 1 0

Position du bit 4 3 2 1 0

Nombre Decimal 2

4

0 2

2

2

1

0

= 16 + 0 + 4 + 2 + 0 = 22

Cours delectronique numerique

Codage

Conversion decimal-binaire

La conversion decimal-binaire peut seectuer en utilisant la

methode inverse de celle enoncee precedemment. Exemples.

Fastidieux pour de grand nombre.

Realise un division par 2

29 2

1 14 2

0 7 2

1 3 2

1 1 2

1 0

Nombre binaire = 11101

Cours delectronique numerique

Codage

Codage Hexadecimal

Travaille avec des quartets binaires : 1010

Interessant la taille du mot binaire de base est loctet

Un octet = Deux Quartets

Cours delectronique numerique

Codage

Codage Hexadecimal

La base du syst`eme Hexadecimal est la base 16

Il faut donc 16 symboles

0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

Cours delectronique numerique

Codage

Codage Hexadecimal

Hexa Decimal Binaire Hexa Decimal Binaire

0 0 0000 8 8 1000

1 1 0001 9 9 1001

2 2 0010 A 10 1010

3 3 0011 B 11 1011

4 4 0100 C 12 1100

5 5 0101 D 13 1101

6 6 0110 E 14 1110

7 7 0111 F 15 1111

Cours delectronique numerique

Codage

Conversion Hexadecimal-Decimal

De meme que pour la conversion binaire-decimal, il sagit ici

de faire une sommation pondere des symboles

Nombre Hexadecimal A 2 E

Position du symbole 2 1 0

Puissance associee 16

2

16

1

16

0

Nombre Decimal 10 16

2

+2 16

1

+14 16

0

= 2606

Cours delectronique numerique

Codage

Conversion Decimal-Hexadecimal

De meme que pour la conversion decimal-binaire on a recourt

`a la division

311 16

7 19 16

3 1 16

1 0

Nombre Hexadecimal = 137

Cours delectronique numerique

Codage

Conversion Hexadecimal-Binaire

Le nombre binaire est deduit en rempla cant chaque chire

hexadecimal par son quartet binaire

Nombre Hexadecimal E 3 B 1

Nombre Binaire 1110 0011 1011 0001

Cours delectronique numerique

Codage

Conversion Binaire-Hexadecimal

La methode est linverse de la precedente

on regroupe les bits par quartet et on remplace les quartets

par leur equivalent hexadecimal.

Nombre Binaire 0101 1010 1100 1011

Nombre Hexadecimal 5 A C B

Cours delectronique numerique

Codage

Notations

Les symboles 0,1 appartiennent au code binaire, decimal et

hexadecimal

les symboles 0,1,2,3,4,5,6,7,8 et 9 appartiennent au code

decimal et hexadecimal

Necessite dune convention decriture pour dierencier

Binaire 100

B

Decimal 100

Hexadecimal 100

H

Cours delectronique numerique

Codage

Decimal Code Binaire : DCB

Remplacer chaque chire dun nombre decimal par son

equivalent binaire

Faire une correspondance directe entre binaire et decimal

Nombre Decimal 5 3 7 1

Nombre Binaire 0101 0011 0111 0001

Nombre Binaire 0101 1001 1000 0011

Nombre Decimal 5 9 8 3

Cours delectronique numerique

Codage

Decimal Code Binaire

Sous-Utilisation de lespace de representation binaire

6 representations interdites

1010

B

,1011

B

,1100

B

,1101

B

,1110

B

,1111

B

Dierence entre codage binaire et DCB

231 =11100111

B

en binaire

231 =001000110001

B

en DCB

Cours delectronique numerique

Codage

Code de Gray

Une representation ne di`ere de la precedente que dun bit

Decimal Binaire Gray Decimal Binaire Gray

0 0000 0000 8 1000 1100

1 0001 0001 9 1001 1101

2 0010 0011 10 1010 1111

3 0011 0010 11 1011 1110

4 0100 0110 12 1100 1010

5 0101 0111 13 1101 1011

6 0110 0101 14 1110 1001

7 0111 0100 15 1111 1000

Cours delectronique numerique

Codage

Code ASCII

Besoin de traiter de linformation non numerique

Information Alphanumerique : , ? R t j

Mise en place dun codage sur 7 bits : lASCII

American Standard Code for Information Interchange

7 bits : 26 lettres minuscules, 26 lettres majuscules, 10

chires, 7 signes de ponctuation soit 69 signes `a coder. Le

reste sert pour des caract`eres speciaux

ASCII etendu : 8 bits

Cours delectronique numerique

Codage

ASCII

Caract`ere Code Hexadecimal

A 41

H

E 45

H

I 49

H

M 4D

H

N 4E

H

Q 51

H

R 52

H

U 55

H

4E

H

55

H

4D

H

45

H

52

H

49

H

51

H

55

H

45

H

NUMERIQUE

Cours delectronique numerique

Alg`ebre de Boole

Alg`ebre de Boole

Alg`ebre de Boole

Cours delectronique numerique

Alg`ebre de Boole

Mister G. Boole

Mathematicien Anglais du 19

i `eme

si`ecle.

1815 1864

Cours delectronique numerique

Alg`ebre de Boole

La gen`ese

Georges Boole introduit un formalise mathematique de la

logique

The Calculus of Logic

Cambridge and Dublin Mathematical Journal

Vol. III (1848), pp. 1839

(3) That those laws are capable of mathematical expression,

and that they thus constitute the basis of an interpretable

calculus.

Au depart beaucoup utilise dans les jeux de salons

Mais `a larrivee : Veritable revolution qui est devenue le

fondement de lelectronique numerique

Cours delectronique numerique

Alg`ebre de Boole

Lalg`ebre - Les bases - 1

Lalg`ebre de Boole manipule des variables qui ne peuvent

prendre que deux etats : Vrai ou Faux

Une telle variable est appelee variable Booleenne

Il est possible aussi dassocier le chire 1 `a la valeur Vrai et le

chire 0 `a la valeur Faux

Les variables Booleennes dans ce cas sont des variables

Binaires

Cours delectronique numerique

Alg`ebre de Boole

Alg`ebre de Boole - Denitions

Alg`ebre de Boole B

B =< E, +, .,

, 0, 1 >

+, . sont des lois de composition interne

est la loi de complementation

Cours delectronique numerique

Alg`ebre de Boole

Alg`ebre de Boole - Lois de Composition

loi de composition .

. 0 1

0 0 0

1 0 1

loi de composition +

+ 0 1

0 0 1

1 1 1

Cours delectronique numerique

Alg`ebre de Boole

Alg`ebre de Boole - Loi de complementation

Le complement a dune variable a est deni par :

si a = 1 a = 0

si a = 0 a = 1

La variable a, lorsquelle est notee a, est dite sous sa forme

normale

La variable a, lorsquelle est notee a, est dite sous sa forme

complementee

Cours delectronique numerique

Alg`ebre de Boole

Axiomes de bases - 1

Commutativite

(a, b) E

2

a + b = b + a

a.b = b.a

Distributivite

(a, b, c) E

3

a + (b.c) = (a + b).(a + c)

a.(b + c) = (a.b) + (a.c)

Cours delectronique numerique

Alg`ebre de Boole

Axiomes de bases - 2

Elements Neutre

a E

a + 0 = a

a.1 = a

Complementation

a E

a + a = 1

a.a = 0

Cours delectronique numerique

Alg`ebre de Boole

Proprietes - 1

A partir des axiomes de base des proprietes fondamentales

sont deduites.

Elements Absorbants

a E

a + 1 = 1

a.0 = 0

Loi didempotence

a E

a + a = a

a.a = a

Cours delectronique numerique

Alg`ebre de Boole

Proprietes - 2

Loi dinvolution

a E

a = a

Loi dabsorption

(a, b) E

2

a + (a.b) = a

a.(a + b) = a

Cours delectronique numerique

Alg`ebre de Boole

Proprietes - 5

Loi dassociativite

(a, b, c) E

3

a + (b + c) = (a + b) + c

a.(b.c) = (a.b).c

Loi de De Morgan

(a, b) E

2

a + b = a.b

a.b = a + b

Cours delectronique numerique

Alg`ebre de Boole

Lalg`ebre - Ordre et Fonction

Relation dordre :

Ordre Total : 0 < 1

Ordre Lexicographique : 00 < 01 < 10 < 11 Utile pour les

tables de verite

Denition dune fonction logique :

f (x

n1

, x

n2

, . . . , x

1

, x

0

) : 0, 1

n

0, 1, n N

Cours delectronique numerique

Alg`ebre de Boole

Fonctions Logiques `a une variable a

1 variable soit 4 fonctions possibles :

f = 0 : fonction constante nulle

f = 1 : fonction constante `a un

f = a : fonction identite

f = a : fonction complement ou fonction NON

Cours delectronique numerique

Alg`ebre de Boole

Fonctions Logiques `a deux variables a et b

2 variables soit 16 fonctions possibles

f = a.b : fonction ET

f = a + b : fonction OU

f = a b : fonction OU-EXCLUSIF

f = a.b : fonction NON-ET

f = a + b : fonction NON-OU

f = a b : fonction NON-OU-EXCLUSIF

etc...

Cours delectronique numerique

Alg`ebre de Boole

Fonctions Logiques `a n variables

n variables soit 2

2

n

fonctions possibles

3 variables 256 fonctions possibles

4 variables 65536 fonctions possibles

etc ...

Cours delectronique numerique

Alg`ebre de Boole

Representation des fonctions logiques

La Table de Verite

Representation sous forme de tableau des valeurs de la

fonction logique pour toutes les combinaisons de ses variables

a b f

0 0 f

0

0 1 f

1

1 0 f

2

1 1 f

3

Cours delectronique numerique

Alg`ebre de Boole

Representation des fonctions logiques

Le Tableau de Karnaugh

Representation sous forme de matrice des valeurs de la

fonction logique pour toutes les combinaisons de ses variables

en exploitant la propriete dadjacence

b 0 1

a c

0 0 f

0

f

1

0 1 f

2

f

3

1 1 f

6

f

7

1 0 f

4

f

5

Cours delectronique numerique

Alg`ebre de Boole

Representation des fonctions logiques

Diagramme de Veitch

Diagramme de Venn

Arbre de decision binaire

Logigramme Partie technologie

Representation algebrique Ecriture logique

Cours delectronique numerique

Alg`ebre de Boole

Ecriture Algebrique

La representation sous forme de tableau ou de matrice est

limitee 5 variables.

Necessite dutiliser une ecriture algebrique

La fonction logique sexprime alors sous la forme de variables

booleennes reliees entre elles par des operateurs de lalg`ebre

de Boole

f (a) = a Fonction NON

f (a, b, c) = cb + ab

Cours delectronique numerique

Alg`ebre de Boole

Ecriture Algebrique - Minterme et Maxterme

Un produit booleen de variables booleennes est appele p-terme

Une somme booleenne de variables booleennes est appelee

s-terme

Un Minterme est un p-terme de degre n

m

j

=

n1

i =0

a

i

, a

i

(a

i

, a

i

)

Un Maxterme est un s-terme de degre n

M

j

=

n1

i =0

a

i

, a

i

(a

i

, a

i

)

Cours delectronique numerique

Alg`ebre de Boole

Ecriture Algebrique - Minterme et Maxterme

La somme logique de tous les Mintermes est egale `a 1 si la

fonction realisee est dierente de la fonction constante 0

p1

j =0

m

j

= 1

Le produit logique de tous les Maxtermes est egal `a 0 si la

fonction realisee est dierente de la fonction constante 1

p1

j =0

M

j

= 0

Relation entre Minterme et Maxterme

m

j

= M

j

Cours delectronique numerique

Alg`ebre de Boole

Ecriture Algebrique - Forme Canonique

Ecriture algebrique dune fonction logique nutilisant que des

Mintermes ou des Maxtermes.

Il existe deux possibilites decriture :

Forme Canonique Disjonctive ou premi`ere forme canonique :

Elle sexprime sous forme dune somme de Mintermes

Forme Canonique Conjonctive ou seconde forme canonique :

Elle sexprime sous forme dun produit de Maxtermes

Cours delectronique numerique

Alg`ebre de Boole

Ecriture Algebrique - Forme Canonique

Fonction Ou-exclusif : la valeur de la fonction est un si une

et une seule des deux variables a la valeur un.

a b f

0 0 0

0 1 1

1 0 1

1 1 0

Forme Canonique Disjonctive :

f (a, b) = ab + ba Somme des Mintermes tel que f(a,b)=1, lu

directement de la table

Forme Canonique Conjonctive :

f (a, b) = (a + b).(a + b) Produit des Maxtermes tel que

f(a,b)=1, cherche les mintermes pour lesquels f(a,b)=0 et on determine

les valeurs de a et de b liees `a ce minterme qui nie f(a,b)=0

Cours delectronique numerique

Alg`ebre de Boole

Domaine de denition des fonctions

Un fonction logique peut-etre soit completement soit

incompletement denie

Une fonction est completement denie lorsque pour toutes les

combinaisons de ses variables la valeur de la fonction est

denie

Une fonction est completement denie lorsque pour toutes les

combinaisons de ses variables la valeur de la fonction est

denie

a b f

0 0 0

0 1 0

1 0 0

1 1 1

Cours delectronique numerique

Alg`ebre de Boole

Domaine de denition des fonctions

Une fonction est incompletement denie lorsque pour toutes

les combinaisons de ses variables la valeur de la fonction nest

pas denie

Une fonction est incompletement denie lorsque pour toutes

les combinaisons de ses variables la valeur de la fonction nest

pas denie

a b f

0 0 1

0 1 X

1 0 X

1 1 1

Cours delectronique numerique

Alg`ebre de Boole

Minimisation de Fonctions

Utilisation des axiomes de base et des Proprietes qui en

decoulent

f (a, b, c) = ab + bc + c en utilisant la loi dabsorption

bc + c = c on obtient f (a, b, c) = ab + c

f (a, b) = a.(a + b) en utilisant laxiome de la

complementation a.a = 0 on obtient f (a, b) = ab.

f (a, b, c) = (a + bc)ab = aab + abbc = ab + abc = ab en

utilisant successivement la loi didempotence et la loi

dabsorption.

Cours delectronique numerique

Alg`ebre de Boole

Minimisation de Fonctions

Une methode graphique : Les Tableaux de Karnaugh

Les variables sont presentees de fa con `a faire apparatre la loi

dabsorption

a.b + a.b = a

Pour ce faire le code binaire reechi ou code de Gray est utilise

Cours delectronique numerique

Alg`ebre de Boole

Minimisation de Fonctions

Les Tableaux de Karnaugh : etapes

Regroupement densembles de 2

i

cases de meme valeur (en

general de valeur 1) en maximisant i `a chaque fois. Possibilite

de regrouper les cases extremes

Regrouper les cases de meme valeur restantes avec des cases

densembles dej`a etablis pour avoir 2

j

cases en maximisant j

Ecrire lequation booleenne algebrique.

Cours delectronique numerique

Alg`ebre de Boole

Minimisation de Fonctions

Les Tableaux de Karnaugh : remarques

Dans le cas de fonctions incompletement denies, considerer

X comme un 1 an de maximiser les ensembles

Methode limitee `a 5 variables.

Cours delectronique numerique

Introduction ` a VHDL

Conception

Conception

Cours delectronique numerique

Introduction ` a VHDL

Comment Concevoir un Circuit ?

Cela depend du circuit.

petits circuits : A la main, en schematique

circuits moyens : A la main `a laide de composants discrets

gros circuits : A laide de langage de Description de circuits

numeriques

Cours delectronique numerique

Introduction ` a VHDL

Les Langages de description

Langage de type HDL : Hardware Description Language

VHDL : Volonte dIndustriels et de Chercheurs de denir un

langage HDL

Verilog : Issu de la societe Cadence Inc.

System C : Mettre au meme niveau Logiciel et Materiel

Cours delectronique numerique

Introduction ` a VHDL

VHDL

Existe depuis 1987 date de la premi`ere norme. 1993 seconde

norme.

Langage M ur et couramment utilise

3 Niveaux :

Niveau Structurel

Niveau Flot de Donnees

Niveau Comportemental

Cours delectronique numerique

Introduction ` a VHDL

VHDL - RTL

RTL : Register Transfert Level

Description Synthetisable

Utilisable pour fondre un circuit

Utilisee dans ce cours

Cours delectronique numerique

Introduction ` a VHDL

VHDL - Base

3 blocs de base:

Les biblioth`eques

Lentite : Decrit linterfa cage du composant

Larchitecture : Decrit le fonctionnement du composant

Cours delectronique numerique

Introduction ` a VHDL

VHDL - Biblioth`eque

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

Cours delectronique numerique

Introduction ` a VHDL

VHDL - Entite

entity MON-ET is

port( A : in std_logic;

B : in std_logic;

S : out std_logic);

end entity MON-ET;

Cours delectronique numerique

Introduction ` a VHDL

VHDL - Larchitecture

S = A et B

architecture FLOT of MON-ET is

begin

S <= A and B;

end architecture FLOT;

Cours delectronique numerique

Introduction ` a VHDL

ot de conception

De la description au circuit

Decrit en VHDL le circuit

Simule le circuit

Synthetise le circuit

Placement-Routage du circuit

Realise un masque

Cuisson du circuit

Cours delectronique numerique

Introduction ` a VHDL

Langage HDL, a quoi ca sert ?

A la conception dASIC

A la programmation de FPGA (cours SSN)

A la verication fonctionnelle de circuits numeriques.

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Bibliothques

Entity

entity NOM_DE_L_ENTITE is

port ( Description des signaux dentres /sorties );

end NOM_DE_L_ENTITE;

Exemple :

entity sequencement is

port (

A : in std_logic;

B : in std_logic;

Q : out std_logic_vector(1 downto 0)

);

end SEQUENCEMENT;

Remarque : Aprs la

dernire dfinition de

signal de linstruction

port il ne faut jamais

mettre de point virgule.

Le TYPE utilis pour les signaux dentres / sorties est :

le std_logic pour un signal.

le std_logic_vector pour un bus compos de plusieurs

signaux.

Par exemple un bus de sortie de 5 bits scrira :

Q : out std_logic_vector (4 downto 0) ;

O Q(4) correspond au MSB et Q(0) correspond au LSB.

Les valeurs que peuvent prendre un signal de type std_logic sont :

0 ou L : pour un niveau bas.

1 ou H : pour un niveau haut.

X ou W : pour un niveau inconnu.

U : pour non initialis.

Z : pour tat haute impdance.

- : Quelconque, cest dire nimporte quelle valeur.

Larchitecture est relative une entit. Elle dcrit le corps du

design, son comportement, elle tablit travers les instructions

les relations entre les entres et les sorties.

Exemple :

-- Oprateurs logiques de base

entity PORTES is

port (A,B :in std_logic;

Y1,Y2,Y3,Y4,Y5,Y6,Y7:out std_logic);

end PORTES;

architecture DESCRIPTION of PORTES is

begin

Y1 <= A and B;

Y2 <= A or B;

Y3 <= A xor B;

Y4 <= not A;

Y5 <= A nand B;

Y6 <= A nor B;

Y7 <= not(A xor B);

end DESCRIPTION;

Architecture

architecture DESCRIPTION of DECOD is

Begin

-- instructions concurrentes

D0 <= (not(IN1) and not(IN0)); -- premire instruction

D1 <= (not(IN1) and IN0); -- deuxime instruction

end DESCRIPTION;

Entre le BEGIN et le END de larchitecture, on est dans un contexte

dinstructions concurrentes.

Instructions concurrentes :

Lordre dans lequel sont crites les instructions na aucune

importance.

Toutes les instructions sont values et affectent les signaux de

sortie en mme temps.

Cest la diffrence majeure avec un langage informatique.

Larchitecture ci dessous est quivalente :

architecture DESCRIPTION of DECOD is

begin

D1 <= (not(IN1) and IN0); -- deuxime instruction

D0 <= (not(IN1) AND not(IN0)); -- premire instruction

end DESCRIPTION;

VHDL : un langage concurrent

Affectation simple : <=

Exemple avec des portes logiques: S1 <= E2 and E1 ;

Les valeurs numriques que l'on peut affecter un signal sont les

suivantes:

'1' ou 'H' pour un niveau haut avec un signal de 1 bit.

'0' ou 'L' pour un niveau bas avec un signal de 1 bit.

oZ' pour un tat haute impdance avec un signal de 1 bit.

'.' pour un tat quelconque, c'est dire '0' ou '1'.

Pour les signaux composs de plusieurs bits on utilise les guillemets

....... , voir les exemples ci dessous:

Les bases numriques utilises pour les bus peuvent tre:

BINAIRE, exemple: BUS <= "1001" ; BUS =9 en dcimal

HEXA, exemple: BUS <=X"g" ; BUS =9 en dcimalxemple affectation simple

entity AFFEC is

port (

E1,E2: in std_logic;

BU51,BU52,BU53 : out std_logic_vector(3 downto 0);

51,52,53,54: out std_logic);

end AFFEC;

architecture DESCRIPTION of AFFEC is

begin

51 <='1'; 51 = 1

52 <= '0'; -- 52 = 0

53 <= E1; -- 53 = E1

54 <= '1' when (E2 ='1') else 'Z'; -- 54 = 1 si E1=1 sinon 54 prend la valeur haute

impdance

BU51 <= "1000"; BU51 = "1000"

BU52 <= E1 & E2 & "10"; -- BU52 = E1 & E2 & 10

BU53 <= x"A"; -- valeur en HEXA> BU53 = 10(dc)

end DESCRIPTION;

------------,

Oprateur de concatnation : &

Cet oprateur permet de joindre des signaux entre eux.

Exemple:

-- Soit A et B de type 3 bits et S1 de type 8 bits

-- A = "001" et B ="110"

S1 <= A & B & "01" ;

-- S1 prendra la valeur suivante aprs cette affectation

-- S1 = "001 110 01"

~ 0

Oprateurs logiques

- ~ ~ ... "''''.,=.,,"-

NON -7 not

ET -7 and

NON ET -7 nand

OU -7 or

NON OU -7 nor

OU EXCLUSIF -7 xor

NON OU EXCLUSIF -7 xnor

DECALAGE A GAUCHE -7 sil

DECALAGE A DROITE -7 sri

ROTATION A GAUCHE -7 roi

ROTATiaN A DROITE -7 ror

L _

Oprateurs relationnels

-

Ils permettent de modifier l'tat d'un signal ou de signaux

suivant le rsultat d'un test ou d'une condition.

Egal 7 =

Non gal 7 1=

Infrieur 7 <

Infrieur ou gal 7 <=

Suprieur 7 >

Suprieur ou gal 7 >

AOI-4-1

ET-2

ET

IN1

IN2

OUT1

OU-2

OU

IN1

IN2

OUT1

NON

NON-1

IN1 OUT1

ET-2

ET

IN1

IN2

OUT1

A

B

C

D

F

AB

CD

O

F=A.B + C.D

AB=A.B

CD=C.D

O=AB+CD

F=O

2 possibilits :

Composant AOI-4-1 : 4 entres, 1 sortie, fonction : F=A.B + C.D

EXEMPLE : DESCRIPTION DUN COMPOSANT COMPLEXE

Objectif :

Premire Possibilit : DESCRIPTION par FLOT de DONNES

-- fichier AOI-4-1-v1.vhd

-- Librairies

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- Entit

entity AOI-4-1 is

port(A,B,C,D : in std_logic;

F : out std_logic);

end entity AOI-4-1

-- Architecture

architecture version1 of AOI-4-1 is

--pas de signaux internes

begin

F <= not( (A and B) or (C and D) );

end architecture version1;

AOI-4-1

A

B

C

D

F

F=A.B + C.D

-- fichier AOI-4-1-v1.vhd

-- Librairies

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- Entit

entity AOI-1-1 is

port(I : in std_logic_vector(3 downto 0);

F : out std_logic);

end entity AOI-1-1

-- Architecture

architecture version1 of AOI-1-1 is

--pas de signaux internes

begin

F <= not( (I(0) and I(1)) or (I(2) and I(3)) );

end architecture version1;

Avec :

A = I(0)

B=I(1)

C=I(2)

D=I(3)

AOI-1-1

F

F=A.B + C.D

I(3-0)

4

OU

1re tape : description des 3 composants de base

ET-2

ET

IN1

IN2

OUT1

-- fichier ET-2_flot.vhd

-- Librairies

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- Entit

entity ET-2 is

port(IN1 : in std_logic;

IN2 : in std_logic;

OUT1 : out std_logic);

end entity ET-2

-- Architecture

architecture flot of ET-2 is

--pas de signaux internes

begin

OUT1 <= IN1 and IN2 ;

end architecture flot;

OU-2

OU

IN1

IN2

OUT1

--- fichier OU-2_flot.vhd

-- Librairies

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- Entit

entity OU-2 is

port(IN1 : in std_logic;

IN2 : in std_logic;

OUT1 : out std_logic);

end entity OU-2

-- Architecture

architecture flot of OU-2 is

--pas de signaux internes

begin

OUT1 <= IN1 or IN2 ;

end architecture flot;

NON

NON-1

IN1 OUT1

-- fichier NON-1_flot.vhd

-- Librairies

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- Entit

entity NON-1 is

port(IN1 : in std_logic;

OUT1 : out std_logic);

end entity NON-1

-- Architecture

architecture flot of NON-1 is

--pas de signaux internes

begin

OUT1 <= not(IN1);

end architecture flot;

Deuxime Possibilit : DESCRIPTION STRUCTURELLE

AOI-4-1

OU-2

OU

IN1

IN2

OUT1

NON

NON-1

IN1

OUT1

A

B

C

D

F

AB

CD

O

ET-2

ET

IN1

IN2

OUT1

ET-2

ET

IN1

IN2

OUT1

2me tape : description du

composant final

-- Entit

entity ET-2 is

port(IN1 : in std_logic;

IN2 : in std_logic;

OUT1 : out std_logic);

end entity ET-2

ET-2

ET

IN1

IN2

OUT1

-- Entit

entity OU-2 is

port(IN1 : in std_logic;

IN2 : in std_logic;

OUT1 : out std_logic);

end entity OU-2

OU-2

OU

IN1

IN2

OUT1

NON

NON-1

IN1 OUT1

-- Entit

entity NON-1 is

port(IN1 : in std_logic;

OUT1 : out std_logic);

end entity NON-1

-- fichier AOI-4-1-v2.vhd

-- Librairies

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- Entit

entity AOI is

port(A,B,C,D : in std_logic;

F : out std_logic);

end entity AOI

-- Architecture

architecture version2 of AOI is

--signaux internes

signal AB,CD,O : std_logic;

begin

PremierET : entity work.ET-2(flot)

port map(A,B,AB);

DeuxiemeET : entity work.ET-2(flot)

port map(C,D,CD);

OU : entity work.OU-2(flot)

port map(AB,CD,O);

NON : entity work.NON-1(flot)

port map(O,F);

end architecture version2;

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire

Logique Combinatoire

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire

Transposition de lalg`ebre de Boole `a lelectronique

Rendu possible grace au composant tel que le transistor

commande en tension

Le domaine de validite de ce qui suit est lelectronique

numerique

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire

Denition :

Un circuit electronique est dit combinatoire si ses sorties sont

determinees par la combinaison de ses variables dentrees et ceci

apr`es un temps ni. Letat dun syst`eme est donc deni par la

combinaison des variables e

1

, . . . , e

i

, . . . , e

n

.

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire

Circuit

Combinatoire

e

1

e

n

s

1

s

i

s

n

e

i

t

p

Cours delectronique numerique

Logique Combinatoire

Les Aleas Temporels

a + a = 0 ?

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire - Operateurs de base

Fonctions `a une variable

Buer (identite) : s = a

1

Inverseur : s = a

1

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire - Operateurs de base

Fonctions `a deux variables

ET (AND) : s = a.b

&

NON-ET (NAND) : s = a.b

&

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire - Operateurs de base

Fonctions `a deux variables

OU (OR) : s = a + b

1

NON-OU (NOR) : s = a + b

1

Cours delectronique numerique

Logique Combinatoire

Logique Combinatoire - Operateurs de base

Fonctions `a deux variables

OU-EXCLUSIF : s = a b = ab + ab

1

NON-OU-EXCLUSIF : s = a b = ab + ab = ab + ab

1

Cours delectronique numerique

Logique Combinatoire

Plan du Cours

Introduction

Alg`ebre de Boole et Logique Combinatoire

Fonctions Combinatoires Complexes

Cours delectronique numerique

Logique Combinatoire

Fonctions Combinatoires Complexes

Fonctions Combinatoires Complexes

Cours delectronique numerique

Logique Combinatoire

introduction

Composees `a partir des operateurs de base

Conditionnement de donnees

Controle de donnees

Denies par leur table de verite

Cours delectronique numerique

Logique Combinatoire

Fonction Egalite

Egalite 2 bits

a b s

0 0 1

0 1 0

1 0 0

1 1 1

s = a b

Cours delectronique numerique

Logique Combinatoire

Egalite - VHDL

entity egalite is

port( a,b : in std_logic;

s : out std_logic);

end entity egalite;

architecture flot of egalite is

begin

s <= not(a xor b);

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

Fonction Egalite

Egalite 2 mots de 2 bits

a = a

1

, a

0

et b = b

1

, b

0

0

0

0

1

1

1

1

0

00

01

11

10

1

1

1

a1

a0

b1b0

1

s = (a

1

b

1

)(a

0

b

0

)

Egalite de 2 mots de n bits :

s = (a

n1

b

n1

)(a

n2

b

n2

)(...)(a

1

b

1

)(a

0

b

0

)

Cours delectronique numerique

Logique Combinatoire

Egalite - VHDL

entity egalite is

port( a,b : in std_logic_vector(1 downto 0);

s : out std_logic);

end entity egalite;

architecture flot of egalite is

begin

s <= not(a(1) xor b(1)) and not(a(0) xor b(0));

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

Egalite - VHDL

VHDL apres lUE LE201

Ce que peut faire VHDL

Hors du cadre du cours LE201

entity egalite is

port( a,b : in std_logic_vector(1 downto 0);

s : out std_logic);

end entity egalite;

architecture comp of egalite is

begin

process(a,b) is

begin

if a= b then

s<=1;

else

s<=0;

end if;

end process;

end architecture comp;

Cours delectronique numerique

Logique Combinatoire

Multiplexeurs

Multiplexeur = Aiguillage

Une commande choisie lentree

Entree choisie recopiee sur la sortie

Partie Commande : p bits

Partie Donnee : 2

p

= n entrees, 1 sortie

Cours delectronique numerique

Logique Combinatoire

Multiplexeurs 2 vers 1 - Table de verite

0

0

0

1

1

1

1

0

0

1

a

b

sel

1 1

1 1

s = sel .a + sel .b

Cours delectronique numerique

Logique Combinatoire

Multiplexeurs 2 vers 1

Schema

a

b

s

sel

Cours delectronique numerique

Logique Combinatoire

VHDL - mux2v1

entity m2v1 is

port(a,b,sel : in std_logic;

s: out std_logic);

end entity m2v1;

architecture flot of m2v1 is

begin

s <= (a and not(sel)) or (b and sel);

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

VHDL - mux2v1

VHDL un petit cran en plus

Ou lon utilise des constructions VHDL un peu plus expressives

entity m2v1 is

port(a,b,sel : in std_logic;

s: out std_logic);

end entity m2v1;

architecture flot of m2v1 is

begin

s <= a when sel=0 else b; -- s prend la valeur de a si

-- sinon si sel <> 0 s prend

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

Multiplexeurs 4 vers 1

4 donnees et 2 commandes

2

6

= 64 lignes dans la table de verite

Toutes les lignes ne sont pas interessantes

Une commande Une variable pertinente

Cours delectronique numerique

Logique Combinatoire

Multiplexeurs 4 vers 1

sel1 sel0 s

0 0 a

0 1 b

1 0 c

1 1 d

s = sel 1.sel 0.a + sel 1.sel 0.b + sel 1.sel 0.c + sel 1.sel 0.d

Cours delectronique numerique

Logique Combinatoire

Multiplexeurs 4 vers 1

s

sel0

sel1

a

b

c

d

Cours delectronique numerique

Logique Combinatoire

Multiplexeurs

Permet de realiser des fonctions logiques

Un Multiplexeur n vers 1 realise 2

n

fonctions

Valeurs des entrees = valeurs de la fonction

Un Multiplexeur 4 vers 1

x y s entree mux

0 0 0 a = 0

0 1 0 b = 0

1 0 0 c = 0

1 1 1 d = 1

x et y commandes du multiplexeur

Cours delectronique numerique

Logique Combinatoire

Demultiplexeurs

Inverse du Multiplexeurs

1 donnees, p commandes, 2

p

= n sorties

Demultiplexeur 1 vers 2

sel a s1 s0

0 0 0 0

0 1 0 1

1 0 0 0

1 1 1 0

Cours delectronique numerique

Logique Combinatoire

Demultiplexeurs

sel a s1 s0

0 0 0 0

0 1 0 1

1 0 0 0

1 1 1 0

s0 = sel .a et s1 = sel .a

Cours delectronique numerique

Logique Combinatoire

Demultiplexeurs

a

sel

s0

s1

Cours delectronique numerique

Logique Combinatoire

Demultiplexeurs - VHDL

entity demux is

port ( sel,a : in std_logic;

s0,s1 : out std_logic);

end entity demux;

architecture flot of demux is

begin

s0 <= a when sel = 0 else 0;

s1 <= a when sel = 1 else 0;

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

Decodeurs

Decodage Binaire Codage 1 parmi n

n entrees, 2

n

sorties

a b s3 s2 s1 s0

0 0 0 0 0 1

0 1 0 0 1 0

1 0 0 1 0 0

1 1 1 0 0 0

Autant de tableaux de Karnaugh que de sorties !

Trivial :

s0 = a.b,

s1 = a.b,

s2 = a.b,

s3 = a.b

Cours delectronique numerique

Logique Combinatoire

Decodeur

s0

s1

s2

s3

a

b

Cours delectronique numerique

Logique Combinatoire

Decodeur

Decodeur Binaire Base n

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

{

Nombre

Binaire

Dcodeur

4 vers 16

a

a0

a1

a2

a3

Cours delectronique numerique

Logique Combinatoire

Encodeurs

inverseur des decodeurs :codeurs

2

n

entrees, n sorties

s3 s2 s1 s0 a b

0 0 0 1 0 0

0 0 1 0 0 1

0 1 0 0 1 0

1 0 0 0 1 1

b = s3.s2.s1.s0 + s3.s2.s1.s0 = s2.s0(s3 s1)

a = s3.s2.s1.s0 + s3.s2.s1.s0 = s1.s0.(s3 s2)

Cours delectronique numerique

Logique Combinatoire

Encodeurs

a

b

s0

s1

s2

s3

Cours delectronique numerique

Logique Combinatoire

Fonctions Combinatoires Complexes

Fonctions Combinatoires Arithmetiques

Cours delectronique numerique

Logique Combinatoire

Nombres Signes

Comment Coder les Nombres Signes en Binaire ?

Introduire un bit de signe : bit de poids fort

Nombre sur 4 bits

b

3

b

2

b

1

b

0

signe valeur decimale

0 1 0 0 + 4

1 1 0 0 - -4

Codage Signe + Valeur Absolue

Necessite trop de logique pour realiser des operateurs

arithmetiques

Cours delectronique numerique

Logique Combinatoire

Complement `a 2

Utilisation dun codage qui permet de limiter les operateur

Complement `a 2 :

Bit de signe : bit de poids fort

Si bit de signe = 0 : Le nombre est code

Si bit de signe = 1 : Complement `a 2 pour avoir la valeur

Principe : Pour un nombre de n bits complementer le nombre

pour arriver `a 2

n

Cours delectronique numerique

Logique Combinatoire

Complement `a 2

Codage de 7 :

b

3

b

2

b

1

b

0

signe valeur decimale

0 1 1 1 + 7

Codage de -7 :

b

3

b

2

b

1

b

0

signe valeur decimale

1 0 0 1 - -7

Cours delectronique numerique

Logique Combinatoire

Complement `a 2

Etapes pour complementer `a 2

Faire le complement `a 1 du nombre : complementation bit `a

bit

Ajouter 1 au nombre

Exemple : codage de -5

b

3

b

2

b

1

b

0

Commentaires

0 1 0 1 Valeur Absolue

1 0 1 0 Complement `a 1

+ 1 Ajout de 1

1 0 1 1 Complement `a 2

Cours delectronique numerique

Logique Combinatoire

Complement `a 2

Avantage :

Unicite du 0

Utilisation du meme operateur pour laddition et la

soustraction

Modulo : 9

H

- 4

H

= (9

H

+ C

H

)modulo(10

H

) = 5

H

Exemples en binaire.

Cours delectronique numerique

Logique Combinatoire

Complement `a 2

Codage sur N bits, N ni

On veut coder un nombre negatif P sur N bits, P [0, 2

N

]

On sait que 2

N

= CP + P

On pose P = CPmod2

N

Ce qui donne P = (2

N

P)mod2

N

On sait que P [0, 2

N

] donc on a bien (2

N

P)mod2

N

= P

Cours delectronique numerique

Logique Combinatoire

Complement `a 2

Si P positif on le code

P =

P

i =N1

i =0

b

i

2

i

P = b

N1

2

N1

+

P

i =N2

i =0

b

i

2

i

avec b

N1

= 0

Si P negatif on le code

P = (2

N

P

i =N1

i =0

b

i

2

i

)

P = (2

N

b

N1

2

N1

P

i =N2

i =0

b

i

2

i

) avec b

N1

= 1

P = (2

N

2

N1

P

i =N2

i =0

b

i

2

i

)

P = (2

N1

(2 1)

P

i =N2

i =0

b

i

2

i

)

P = (2

N1

P

i =N2

i =0

b

i

2

i

)

P = b

N1

2

N1

+

P

i =N2

i =0

b

i

2

i

avec b

N1

= 1

Nombre en complement `a 2

P = b

N1

2

N1

+

P

i =N2

i =0

b

i

2

i

Cours delectronique numerique

Logique Combinatoire

Demi-Additionneur

Realisation dun demi-additionneur

a b s r

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

s = a b

r = a.b

Cours delectronique numerique

Logique Combinatoire

Demi-Additionneur

a

b

s

c

Cours delectronique numerique

Logique Combinatoire

Demi-Additionneur

entity demi-add is

port( a,b : in std_logic;

s,c : out std_logic);

end entity demi-add;

architecture flot of demi-add is

begin

s<= a xor b;

c<= a and b;

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

Additionneur 1 bit

Introduction dune retenue dentree

Trois variables dentrees, deux de sorties

a

i

,b

i

,c

i

et s

i

,c

i +1

s

i

= a

i

b

i

c

i

c

i +1

= a

i

.b

i

+ a

i

.c

i

+ b

i

.c

i

Utilisation de deux demi-additionneurs

Cours delectronique numerique

Logique Combinatoire

Additionneur 1 bit

Demi

Additionneur

ai

bi

Demi

Additionneur

si

ci+1

ci

Cours delectronique numerique

Logique Combinatoire

Additionneur 1 bit

entity add1 is

port( a,b,cin : in std_logic;

s,cout : out std_logic);

end entity add1;

architecture struct of add1 is

signal stemp,ctemp1,ctemp2 : std_logic;

begin

demi-add1 : entity work.demi-add(flot)

port map(a,b,stemp,ctemp1);

demi-add2 : entity work.demi-add(flot)

port map(stemp,cin,s,ctemp2);

cout <= ctemp1 or ctemp2

end architecture struct;

Cours delectronique numerique

Logique Combinatoire

Additionneur 1 bit

entity add1 is

port( a,b,cin : in std_logic;

s,cout : out std_logic);

end entity add1;

architecture flot of add1 is

begin

s<= a xor b xor cin;

cout<= (a and b) or (a and cin)

or (b and cin);

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

Additionneur 1 bit

VHDL apres lUE LE201

Ce que peut faire VHDL

Hors du cadre du cours LE201

entity add1 is

port( a,b : in std_logic;

s : out std_logic);

end entity add1;

architecture comport of add1 is

begin

s<= a + b;

end architecture comport;

Cours delectronique numerique

Logique Combinatoire

Additionneur 4 bits

a0

b0

c0

a1

b1

c1

a2

b2

c2

a3

b3

c3

s0 s1 s2 s3

c4

Cours delectronique numerique

Logique Combinatoire

Additionneur 4 bits : Entite

ENTITY add4 IS

port (a,b : in std_logic_vector(3 downto 0);

cin : in std_logic;

s : out std_logic_vector(3 downto 0);

cout : out std_logic);

END ENTITY add4;

Cours delectronique numerique

Logique Combinatoire

Additionneur 4 bits : Architecture Simple

ARCHITECTURE struct_simple OF add4 IS

signal c : std_logic_vector(4 downto 0);

BEGIN

c(0) <= cin;

cout <= c(4);

add1_0 : entity work.add1(flot)

port map (a(0),b(0),c(0),s(0),c(1));

add1_1 : entity work.add1(flot)

port map (a(1),b(1),c(1),s(1),c(2));

add1_2 : entity work.add1(flot)

port map (a(2),b(2),c(2),s(2),c(3));

add1_3 : entity work.add1(flot)

port map (a(3),b(3),c(3),s(3),c(4));

END ARCHITECTURE struct_simple;

Cours delectronique numerique

Logique Combinatoire

Additionneur 4 bits : Architecture avec Generation

ARCHITECTURE struct_generate OF add4 IS

signal c : std_logic_vector(4 downto 0);

BEGIN

c(0) <= cin;

cout <= c(4);

instance : for i in 0 to 3 generate

add1_i : entity work.add1(flot)

port map (a(i),b(i),c(i),s(i),c(i+1));

end generate;

END ARCHITECTURE struct_generate;

Cours delectronique numerique

Logique Combinatoire

Multiplieur

Utilisation de lalgorithme de Multiplication

n m m additions de n

ai

bi

ci

si

ci+1

ai

bi

ci

si

ci+1

ai

bi

ci

si

ci+1

ai

bi

ci

si

ci+1

ai

bi

ci

si

ci+1

ai

bi

ci

si

ci+1

b

0

b

1

b

2

a

0

a

1

a

2

0

0

0

p

0

p

1

p

2

p

3

p

4

p

5

Cours delectronique numerique

Logique Combinatoire

Complement VHDL : Modelisation du temps

library ieee;

use ieee.std_logic_1164.all;

entity mon-et is

port(a,b : in std_logic;

s : out std_logic);

end entity mon-et;

architecture flot of mon-et is

begin

s <= a and b after 25 ns;

end architecture flot;

Cours delectronique numerique

Logique Combinatoire

Complement VHDL : Decalage et mise `a lechelle

library ieee;

use ieee.std_logic_1164.all;

entity conversion is

port(a : in std_logic_vector(5 downto 0);

s,s2,s3 : out std_logic_vector(11 downto 0));

end entity conversion;

architecture flot of conversion is

begin

a <= "010101";

s <= "0000" & a & "00"; -- s = "000001010100"

s2 <= "00000" & a & 0; -- s2 = "000000101010"

s3 <= a & "000000"; -- s3 = "010101000000"

end architecture flot;

LE201 Electronique numrique

Logique squentielle

Les bascules

2 notions importantes : le rythme et la mmoire

Bascule RS asynchrone

Vers les bascules synchrones

Bascule D

Considrations temporelles

La bascule D en VHDL

Les bascules JK et T

Les registres

Les compteurs

Les convertisseurs analogique/numrique

et numrique/analogique

LE201 Electronique numrique

Logique squentielle

2 notions importantes : le rythme et la mmoire

Logique combinatoire : ralisation statique de fonctions

boolennes

laide de portes, dcodeurs, multiplexeurs.

Logique squentielle : les oprations logiques sont

effectues

au rythme dune horloge

Entre deux tops dhorloge les signaux doivent tre mis en

mmoire

LE201 Electronique numrique

Logique squentielle

LE201 Electronique numrique

Logique squentielle

Source : http://comelec.enst.fr/tpsp/eni/poly/enich6.html

Logique squentielle

LE201 Electronique numrique

Cest quoi une horloge ?

Q

0

H

Un signal priodique carr TTL de priode T

H

Un front montant est linstant du passage 01

Un front descendant est linstant du passage 10

T

H

Comment mettre en mmoire ?

Logique squentielle

Mmoire lmentaire : charge dun condensateur

LE201 Electronique numrique

R

C

entre

sortie

criture

lecture

0

1

0

1

Rsistance de fuite r

entre sortie

0

0

0

0

1

1

1

1

criture de

lentre dans C

Mise en mmoire

Lecture en sortie

du contenu de C

Non utilis

Problme : C se dcharge

dans la rsistance de fuite

C=10pF, r=100 M

t = 1 ms

LE201 Electronique numrique

Premire tape : bascule asynchrone Bascule RS

Table de vrit

Mmoire

Set

Reset

LE201 Electronique numrique

Bascule RS portes Nand

R S Q Q

0 0 interdit

1 0 1 0 Set

0 1 0 1 Reset

1 1 Q Q Mmoire

Tout est invers

LE201 Electronique numrique

Vers les bascules synchrones

Il faut viter :

Ltat interdit RS=11

Rajouter une horloge

Bascule D asynchrone

pour viter ltat 11

D

Ltat mmoire 00 a disparu!

LE201 Electronique numrique

Bascule RS synchrone

pour ajouter une horloge

R.H

S.H

H

S

R

Vers les bascules synchrones

R S H Q Q

X X 0 Q Q Mmoire

0 1 1 1 0 Set

1 0 1 0 1 Reset

0 0 1 Q Q Mmoire

1 1 1 Interdit

Ltat interdit nest pas

limin

Et la bascule est active

sur niveau (H=1) pas sur

front

LE201 Electronique numrique

Latch (verrou) en combinant les deux

R

H

S

S.H

R.H

D

H D R.H S.H Q Q

0 X 0 0 Q Q

1 0 0 1 0 1

1 1 1 0 1 0

Cest un verrou

Si H=0 Mmoire

(verrouill)

Si H=1 Q=D (verrou

transparent)

Bascule active sur

niveau (pas sur front)

LE201 Electronique numrique

Bascule active sur front : structure matre esclave

LE201 Electronique numrique

La Bascule D

LE201 Electronique numrique

Considrations temporelles

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

ENTITY basculeD IS

port (d,hor,raz,rau : in std_logic;

q,qb : out std_logic);

END ENTITY basculeD;

ARCHITECTURE comport OF basculeD IS

BEGIN

-- Bascule D avec Raz et Rau asynchrone

stockage: process(d,hor,raz,rau) is

begin

if (raz = '0') then

q <= '0';

qb <= '1';

elsif (rau = '0') then

q <= '1';

qb <= '0';

elsif (hor'event and hor = '0') then

q<=d;

qb <= not d;

end if;

end process stockage;

END ARCHITECTURE comport;

La bascule D en VHDL

LE201 Electronique numrique

{ Dans un process : les instructions sont excutes

squentiellement, les unes la suite des autres

(instructions standart de la prog. structure).

{ Execution du process : chaque changement dun

signal de la liste de sensibilit

{ Changements dtat des signaux : la fin de

lexecution du process

LE201 Electronique numrique

La bascule D en VHDL : process

Syntaxe :

[Nom_du_process] : process (liste_de_sensibilit_noms_des_signaux)

Begin

--instructions

End process [nom_du_process]

La bascule D en VHDL : instruction if

LE201 Electronique numrique

Syntaxe:

If condition then

Instruction

Elsif condition then

instructions

Else

instructions

End if;

Exemple :

If (reset=0) then

sortie<="0000

Elsif load=1 then

sortie<=entree;

Else

sortie<=D(5 downto 2);

End if;

Bascules JK et T

LE201 Electronique numrique

Entres asynchrones

LE201 Electronique numrique

Les registres : registres parallles

LE201 Electronique numrique

D Q

D Q

D Q

D Q

Clk

D

0

D

1

D

3

D

2

Q

0

Q

1

Q

2

Q

3

Bascules indpendantes,

Lentre Clk est commune toutes

les horloges

Le registre transfert les valeurs du

bus dentre sur 4 bits vers la sortie

sur 4 bits au moment du front

dhorloge.

Applications : synchronisation, tampons

LE201 Electronique numrique

Les registres dcalage srie

D Q

D Q

D Q

D Q

In

Q

0

Q

3

Clk

Q

1

Q

2

Les bascules sont relies entre elles.

Lhorloge est commune toutes les bascules.

Dcalage des sorties vers la droite chaque top dhorloge.

Applications: transformations dinformations parallle/srie,

mission sur 1 fil de 1 bit

Diffrences srie parallle

Transfert Srie

Linformation est transfre un bit

la fois

Dcale les bits du registre source vers

le registre destination

Transfert Parallle :

Tous les bits du registre sont

transfrs en mme temps

LE201 Electronique numrique

Registre universel

http://wwwdsa.uqac.ca/~rbeguena/Systemes_Digitaux/Systemes%20Digitaux6_I.pdf

LE201 Electronique numrique

Registre universel

LE201 Electronique numrique

Registre universel

LE201 Electronique numrique

LE201 Electronique numrique

Les compteurs

Un systme squentiel plus complexe

un compteur

base de bascules (souvent bascules D)

Suite simple des nombres binaires :

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Q

3

Q

2

Q

1

Q

0

Q

0

change chaque fois

( chaque top dhorloge)

Q

1

change une fois sur deux

(tous les 2 tops dhorloge)

Q

2

change une fois sur quatre (tous les 4 tops)

Q

3

change une fois sur huit (tous les 8 tops)

Un compteur est un circuit dont la valeur des sorties est

directement lie au nombre d'impulsions appliques sur son

entre d'horloge

LE201 Electronique numrique

Les compteurs

Q

0

sortie dune bascule T avec T=1 :

n 1 n

Q Q =

+

Avec une bascule D :

0 n 1 n 0

Q Q Q D = = =

+

D

Q

Q

H

1

Q

1

sortie

dune bascule T avec T=1 et

avec H1 de priode T

1

=2 T

0

:

2

0 1

Q H =

1 n 1 n 1

Q Q Q D = = =

+

Q

0

H

T

H

T

0

=2T

H

f

0

=f

H

/2

Diviseur de

frquence par 2

LE201 Electronique numrique

Les compteurs

D

0

Q

0

Q

0

H

D

1

Q

1

Q

1

Q

0

H

Q

1

1

1 1

1

1

0

1

0 0

0

1

0

1

0

0

0

Dcompteur! problme

Il faudrait que Q

1

soit modifi sur le front descendant de Q

0

Il suffit de prendre H

1

=Q

0

T

1

=4T

H

T

H

Diviseur de frquence par 4

LE201 Electronique numrique

Les compteurs

LE201 Electronique numrique

Les compteurs

D

0

Q

0

Q

0

H

D

1

Q

1

Q

1

Q

0

H

Q

1

compteur!

Pour 4 bits :

D

2

Q

2

Q

2

D

2

Q

2

Q

2

Q

2

Q

3

1

1 1

1

1

0

1

0 0

0

1

0

1

0

0

0

0 0 0 0

1

1 1 1

0 0 0 0 0 0 0

1

Avec 4 bascules : 4 bits en sortie, 2

4

valeurs possibles=16

Compteur par 16 ou modulo 16

Avec N bascules : N bits en sortie, 2

N

valeurs possibles

Compteur par 2

N

ou modulo 2

N

LE201 Electronique numrique

Les compteurs

Compteurs Q : entre Clk de la bascule suivante

Dcompteurs Q : entre Clk de la bascule suivante

Diviseurs de frquence :

la sortie de la 1

re

bascule : diviseur par 2

la sortie de la N

ime

bascule : diviseur par 2

N

LE201 Electronique numrique

Les compteurs

Compteurs par P2

N

1. Combien de bascules ?

2

N1

<P<2

N2

on prend N2 bascules

2. Comment sarrter P ?

remise zro P-1

utilisation des entres asynchrones (Reset, Set)

Exemple : compteur par 5

000

001

010

011

100

000

tats indsirables:

101

110

111

Reset=1

Reset=Q

2

.(Q

1

+Q

0

)

LE201 Electronique numrique

Les compteurs

Inconvnients de ces compteurs :

Quand on prend en compte les temps de propagation de

chaque bascule:

Des problmes dala de fonctionnement (Glitch)

indsirables peuvent apparatre

Compteurs asynchrones

Toutes les bascules nont pas la mme horloge

LE201 Electronique numrique

Les compteurs

LE201 Electronique numrique

Les compteurs

Pour viter les problmes dus aux temps de propagation

Compteurs synchrones

Toutes les bascules sont commandes par la mme horloge

=> Pas de problme de cumul des temps de propagation

=> Etats transitoires parasites limits

Une mthode unique pour raliser tous les types de

compteurs

LE201 Electronique numrique

Les compteurs

Synthse dun compteur modulo P

partir de bascule D synchrones

1 - Nombre de bascules ncessaires : n, o 2

n-1

< P 2

n

3 - Calculer l'expression des entres D des bascules

D

i

= Q

i

+

= f(Q

j

)

2 - Etablir la table de transition du compteur

tat suivant (Q

i

+) en fonction de l'tat prsent (Q

i

)

Q

n

Q

1

Q

0

Q

n

+

Q

1

+

Q

0

+

..

010

..

011

LE201 Electronique numrique

Les compteurs

Exemple : compteur modulo 8 (2

3

)

1. Combien de bascules ?

3 bascules

2. Table de vrit

Q

2

Q

1

Q

0

Q

2

+

Q

1

+

Q

0

+

LE201 Electronique numrique

Les compteurs

3. Calcul des expressions des entres D

i

= Q

i

+

= f(Q

i

)

Q

2

Q

1

Q

0

Q

2

+

Q

1

+

Q

0

+

00 01 11 10

0 1 0 0 1

1 1 0 0 1

Q

2

Q

1

Q

0

D

0

0 0

Q D =

00 01 11 10

0 0 1 0 1

1 0 1 0 1

Q

2

Q

1

Q

0

D

1

0 1 0 1 1

Q Q Q Q D + =

1 0 1

Q Q D =

00 01 11 10

0 0 0 1 0

1 1 1 0 1

Q

2

Q

1

Q

0

D

2

0 2 1 2 0 1 2 2

Q Q Q Q Q Q Q D + + =

( ) ( )

2 0 1 2 0 1 2

Q Q Q Q Q Q D + =

( )

0 1 2 2

Q Q Q D =

LE201 Electronique numrique

Les compteurs

0 0

Q D =

1 0 1

Q Q D =

( )

0 1 2 2

Q Q Q D =

0 0

Q D =

( ) 1

0 1

> =

i , Q Q Q D

i i i

Compteur modulo 2

n

Q

0

Q

1

Q

2

Q

0

Q

1

Q

2

Clk

(Q

2

Q

1

Q

0

)

Exemple : compteur modulo 6

1. Combien de bascules ?

2

2

=4 < 6 < 2

3

=8 3 bascules

2. Table de vrit

LE201 Electronique numrique

Les compteurs

Q

2

Q

1

Q

0

Q

2

+

Q

1

+

Q

0

+

LE201 Electronique numrique

Les compteurs

3. Calcul des expressions des entres D

i

= Q

i

+

= f(Q

i

)

D

0

=Q

0

D

1

=Q

2

.(Q

1

+ Q

0

)

D

2

=Q

1

.Q

0

+ Q

2

Q

0

tats indsirables ?

110?

111?

On vrifie que les tats suivants sont dans la boucle de

comptage

OU on indique ces tats dans la table de vrit en

choisissant les tats suivants ( 000 souvent) et on en

tient compte dans les quations

LE201 Electronique numrique

Les compteurs

Avec cette mthode on peut raliser:

Des compteurs dcrivant dautres cycles que

lnumration binaire

-dcompteur

-code de Gray

-cycles quelconques

Compteurs programmables :

En ajoutant des entres asynchrones, on peut crer

-chargement parallle du compteur

-commande de validation / inhibition du comptage

-programmation du sens du comptage

Compteurs synchrones par P

{ Compteur par p>16, on prend

directement un compteur par 2

n

puis on dfinit un reset actif lorsque

sortie=p

LE201 Electronique numrique

LE201 Electronique numrique

Les compteurs

Un compteur en VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

ENTITY compteur_8 IS

port(

clk, reset : std_logic;

s: out std_logic_vector(2 downto 0));

END ENTITY compteur_8;

ARCHITECTURE struct OF compteur_8 IS

signal D0, D1, D2 : std_logic;

Signal sint, nsint : std_logic_vector(2 downto 0);

BEGIN

--instanciation des 3 bascules

basc1 : entity work.basculeD(comport)

port map(D=>D0,CK=>clk,Rst=>reset,

Q=>sint(0),NQ=>nsint(0));

basc1 : entity work.basculeD(comport)

port map(D=>D1,CK=>clk,Rst=>reset,

Q=>sint(1),NQ=>nsint(1));

basc1 : entity work.basculeD(comport)

port map(D=>D2,CK=>clk,Rst=>reset,

Q=>sint(2),NQ=>nsint(2));

--quations des entres Di des bascules

D0<=nsint(0);

D1<=sint(0) xor sint(1);

D2<=sint(2) xor (sint(1) and sint(0));

--affectations des signaux internes aux sorties

s<=sint;

END ARCHITECTURE struct;

A base de

bascules D

Rst

LE201 Electronique numrique

Les compteurs

Un compteur en VHDL A base de bascules D

Sans reset

--quations des entres Di des bascules

D0<=nsint(0);

D1<=sint(0) xor sint(1);

D2<=sint(2) xor (sint(1) and sint(0));

--affectations des signaux internes aux sorties

s<=sint;

--reset synchrone actif niveau haut

Proc_reset: PROCESS (clk, reset) IS

BEGIN

If (clkevent and clk=1) then

if (reset=1) then

sint<=000;

nsint<=111;

end if;

End if;

END PROCESS;

END ARCHITECTURE struct;

ARCHITECTURE struct OF compteur_8 IS

signal D0, D1, D2 : std_logic;

Signal sint, nsint : std_logic_vector(2 downto 0);

BEGIN

--instanciation des 3 bascules

basc1 : entity work.basculeD(comport)

port map(D=>D0,CK=>clk,

Q=>sint(0),NQ=>nsint(0));

basc1 : entity work.basculeD(comport)

port map(D=>D1,CK=>clk,

Q=>sint(1),NQ=>nsint(1));

basc1 : entity work.basculeD(comport)

port map(D=>D2,CK=>clk,

Q=>sint(2),NQ=>nsint(2));

Pipeline

Additionneur 4 bits : pipelin pour acclrer la vitesse de calcul

LE201 Electronique numrique

Pipeline

Principe :

Dcouper loprateur en plusieurs tages isols les uns des autres.

Cest le signal dhorloge qui autorise les transfert des donnes dun

tage lautre. Cette technique permet dacclrer la cadence de

production des rsultats.

Latence

La latence (dure dexcution totale) de loprateur est suprieure

dau moins celle dun oprateur non pipelin.

Si la dure maximale dun tage de loprateur pipelin est de Tmax et

quil y a n tages, alors la latence de loprateur est

T = n .Tclk avec Tclk > Tmax + th + ts

avec ts et th les temps de prpositionnement

et de maintien des bascules.

LE201 Electronique numrique

Convertisseurs analogique - numrique

et numrique analogique (CAN et CNA)

Plan

{ Gnralits

{ Chane de conversion

{ Echantillonnage

{ CAN

z Caractristiques

z Convertisseur rampe

z Conv. approximations successives

z Conv. flash

{ CNA

z Poids pondrs

z Rseau R/2R

LE201 Electronique numrique

Monde analogique et continu

grandeur anal ogi que

-1,5

-1

-0,5

0

0,5

1

1,5

0 100 200 300 400 500

t

U

Le monde est analogique

La temprature, la pression, la luminosit, le son ..

varient de manire continue avec le temps.

Capteur

Signal lectrique

Support de

linformation

Signal

mcanique

Support de

linformation

Autres supports physiques :papier, lumire,

champs lectromagntiques (adapts la

transmission et au stockage de linformation :

livres, cdroms, fibre optiques, tlphone

portable ou par satellite)

Mais pas adapts pour le traitement

Traitement

LE201 Electronique numrique

Monde numrique et discret

{ Le monde numrique est discret

(pas continu)

Signal

lectrique

Signal

numrique

Traitement

lectronique

numrique

??

Il faut numriser le signal

LE201 Electronique numrique

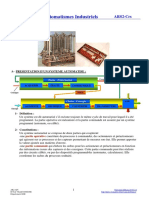

capteurs

Chane de conversion

Monde

analogique

P, T, m, I

grandeur grandeur

analogique

lectrique

CAN

Bus de n bits

grandeur

numrique

Monde

numrique

Traitement

analogique

CNA

Actionneur

Bus de

m bits

LE201 Electronique numrique

Chane de conversion

{ Plus en dtails

capteurs

grandeur grandeur

analogique

lectrique

CAN

grandeur

numrique

Bus de n bits

analogique

Ampli

Filtre

Passe-bas

Anti-

repliement

Echantillonneur

bloqueur

LE201 Electronique numrique

Echantillonnage

LE201 Electronique numrique

Echantillonnage

Echantillonnage

Echantillonnage

Echantillonnage

En amont du convertisseur, un chantillonneur-bloqueur

prlve rgulirement une valeur de la tension

continue U sortie du capteur. Il maintient ou bloque

cette valeur constante jusqu lchantillon suivant.

(mmoire analogique)

Une infinit de valeurs

Tension d'entre du CAN

le temps de conversion doit tre

infrieur Te

Commande de l'chantillonneur

Priode Te , Frquence Fe = 1/Te

double quantification : quantification temporelle ( chantillonnage ) +

quantification en amplitude ( rsolution )

http://www.ac- grenoble.fr/disciplines/spc/ file/ppt/seconde/mpi/mpigiustini/

deux/cnacan/cnacan.ppt#275,1,1/ CAN CNA Exemple d'un enregistrement sonore

Thorme de Shannon

Problmes dchantillonnage

{ Si la frquence dchantillonnage nest pas assez

leve pb de repliement du spectre

{ Pb lorsquil y a des composantes haute frquence

(craquements)

http://fr.wikipedia.org Thorme d'chantillonnage de Nyquist-Shannon

Priodisation du spectre en frquence

Filtre Passe-bas pour couper les hautes frquences

Codage

{ Quelques normes de codage audio

Dfinition

{ CAN : Dfinition

{ La conversion analogique-numrique consiste

transformer une grandeur lectrique reprsente

par un signal en une grandeur numrique

exprime sur N bits aprs chantillonnage et

quantification du signal. Cette valeur est une

valeur code reprsentant un nombre

proportionnel a la grandeur lectrique.

Caractristiques dun CAN

{ Rsolution analogique :

z r : cart minimum entre 2 valeurs de

Ve qui donne 2 sorties binaires

diffrentes

z Correspond au LSB

0 <Ue<Uref Sinon ampli permet dadapter

la gamme damplitude

Exemple CAN 3 bits

2

n

= 8 valeurs

7

0

1

2

A

Ue

Une infinit de valeurs possibles

A mot binaire

0 000

1 001

2 010

3 011

4 100

5 101

6 110

7 111

U

ref

r rsolution

analogique

U

ref

= 5 V

r=5/8=0,625 V

r= U

ref

/2

n

Rsolution numrique : n

Nombre de bits en sortie

Caractristiques des CAN : suite

Erreur de quantification e :

Temps de conversion : caractristique importante. Dpend

du systme utilis

0 e r

Convertisseur Simple rampe

+

-

Sortie sur

n bits

Ve tension convertir

Vc

Vc

t

Ue

Fin de conv

Tant que V

+

>V

-

soit Ve>Vc

Vs=1

Compteur sincrmente

C se charge, Vc augmente

Vs

Convertisseur rampe numrique

Sortie sur

n bits

Temps de conversion des conv. simple rampe :

Temps variable selon la valeur de Ve

Au maximum : si Ve=V

ref

Tconv = (2

n

-1) T

clk

Conv. approximations successives

{ Principe de la pese

Le rsultat de la

conversion est ici

11010

Temps de conversion

Tconv=n.T

clk

Convertisseur plus

rapide que ceux

rampe

Convertisseur flash ou parallle

Sortie sur

n bits

Avantage :

tous les comparateurs fonctionnent

en parallle donc conversion rapide

Tconv=2 T

clk

Inconvnient :