Académique Documents

Professionnel Documents

Culture Documents

Class 02 Transistors I

Transféré par

kumaranrajCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Class 02 Transistors I

Transféré par

kumaranrajDroits d'auteur :

Formats disponibles

Class 02: Transistors I

Topics: What is a transistor? History of transistors Views of an n-type transistor schematic and cross section channel length, channel width Where are we headed? Final cross section for CMOS CMOS vs. NMOS Layout layers for a transistor Layout and Cross section for an NMOS transistor CMOS Formation Substrate and Doping Why Isolate? Isolation, Nwell Vt Adjust Poly P+ Diffusion N+ Diffusion Final Cross Section for CMOS

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

Transistor - trans(fer) (res)istor NFET (PFET) - n-type (p-type) field effect transistor NMOS (PMOS) - n-type (p-type) metal oxide semiconductor (misnomer) MESFET - metal semiconductor FET MISFET - metal insulator FET IGFET - insulated gate FET JFET - junction FET (BJT - Bipolar Junction Transistor) History: 1875 - Selenium shown to have rectifying and optoelectronic properties 1906 - Silicon used for diode to detect radio waves 1935 - Selenium rectifiers and photodetectors commercially availabe WWII - Radar spurs growth of Silicon and Germanium research 1948 - Point contact transistor by Bardeen and Brattain (Bell Labs) 1949 - Junction diodes and junction transistors by Shockley (Bell Labs) 1949 - Single crystal (as opposed to polycrystalline) silicon developed 1952 - Grown junction germanium transistors by Shockley (Bell Labs) 1954 - Grown junction silicon transistors by Texas Instruments 1959 - Integrated circuit by Kilby (Texas Instruments) 1961 - Silicon planar transistor by Hoerni (Fairchild) (References: Runyan and Bean, Yang, Sze)

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

NMOS Cross Section (Martin p.91)

A transistor has four terminals source

gate drain

Substrate, bulk, well, or back gate

Why is this important? W, L, S, D, G are fundamental to every aspect of IC design (circuit level, gate level, layout, simulation) Each transistor is the basically the same, so know one, you know them all

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

Final Cross Section for CMOS (Martin p. 47)

Cross Section

Partial Layout

Why is this important? Design Engineers: understanding of how transistors are formed leads to better designs Process Engineers: each step in the formation is related to the next Product Engineers: debugging of product-level issues involves cross section CAD/Layout Engineers: integrating rules and determining violations to layout

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

CMOS vs. NMOS CMOS - Complementary Metal Oxide Semiconductor NMOS - N-type Metal Oxide Semiconductor Assumptions for CMOS: Substrate is p-type Gate material is made of polysilicon The process is single-well (nwell) CMOS vs. NMOS: NMOS process uses n-type transistors only CMOS (complementary MOS) uses n- and p-type NMOS process has a substrate (p-type) no wells CMOS process has a substrate (p-type) and (usually) one well (nwell)

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

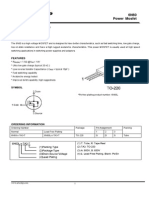

Layout Layers for Transistor

Drawn and MASK layers used to create a transistor: 1) Well (aka substrate, tub, moat) nmos are in pwell, pmos are in nwell 2) Diffusion , ACTIVE, NSELECT, PSELECT (aka diff) type of diffusion for Source/Drain set by well defines active vs. isolation (or field) regions 3) Poly (aka gate) gate material over diff defines W and L of transistor 4) Contact , CT-TO-ACTIVE, CT-TO-POLY (aka ct) defines how the source, drain, gate, and tap are contacted to higher levels 5) Tap, ACTIVE, NSELECT, PSELECT defines contact to substrate or well heavily doped, same type as sub/well (i.e., n-type in nwell, p-type in p-substrate)

1/16/01

Joseph A. Elias, PhD

Class 02: Transistors I

Layout and Cross Section - NMOS (Martin p.50)

Isolation Region

Isolation Region

Isolation Region

Isolation Region

1/16/01

Joseph A. Elias, PhD

Class 02: Transistors I

CMOS Formation - Substrate, Doping

Research Areas: II-VI III-V

Presently, most starting material (substrate) is <100> p-type silicon Silicon is a group IV element (4 outer electrons) p-type dopants are ones with less electrons, or more holes (B) n-type dopants are ones with more electrons, or less holes (P, As)

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

CMOS Formation - Why isolate? (Wolf p.18)

1/16/01

Joseph A. Elias, PhD

Class 02: Transistors I

CMOS Formation - Isolation, Nwell (Martin p.42)

nwell

Diff-tap

Deposit SiO2, Si3N4, photoresist (PR) Use DiffTap (aka moat, active) mask to define isolation regions. This is where transistors will NOT be located, which is the inverse of diffusion and tap regions Grow isolation (LOCOS), or etch silicon and deposit oxide (STI), strip Si3N4 Deposit photoresist, expose NWELL mask, develop, implant N-type well (Phos) Optional : Implant field regions for channel stop (CS), punchthrough (PT)

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

CMOS Formation - Vt Adjust (Martin p.43)

nwell

Diff-tap

Implant will show up here as well, but be counter-doped later in the process

The order of events can vary, but in general: With NWELL pattern still on silicon, implant gate threshold adjust Strip thin oxide, regrow oxide to 30-100A (depending on process node) Done since oxide has been damaged due to implant Allows for gate oxide to be as clean as possible Purpose of Vt adjust will become apparent further in the semester

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

CMOS Formation - Poly (Martin p. 44)

nwell

Diff-tap poly

Deposit polysilcon everywhere on wafer, deposit PR Use POLY mask to define regions where poly is to remain Expose, develop PR; etch polysilicon; implant poly with P or As

1/16/01

Joseph A. Elias, PhD

Class 02: Transistors I

CMOS Formation - P+ diffusion (Martin p.45)

nwell

Pdiff

Diff-tap poly

Use Diff-Tap layout to generate, or manually draw p-diff mask Size up the diff-tap region to account for misalignment Implant is self-aligned to gate, as gate acts as a mask

1/16/01

Joseph A. Elias, PhD

Class 02: Transistors I

CMOS Formation - N+ diffusion (Martin p. 45)

nwell

Pdiff

Ndiff

poly

Incorrect tap to well

Use Diff-Tap layout to generate, or manually draw n-diff mask Size up the diff-tap region to account for misalignment Implant is self-aligned to gate, as gate acts as a mask Taps should NOT cross well boundaries!

1/16/01 Joseph A. Elias, PhD

Class 02: Transistors I

Final Cross Section for CMOS (Martin p. 47)

Further processing: CT (contact) mask to open up regions in thin oxide to contact diff CT (contact) mask to open up regions over poly to contact gates Deposition of ILD (inter-level dielectric) , shown as CVD SiO2 MET1 (metal 1) mask to identify routing Deposition of ILD, VIA mask to contact MET1, MET2 mask to route Deposition of PO (protective oxide), shown as Overglass

1/16/01 Joseph A. Elias, PhD

Vous aimerez peut-être aussi

- Tcs Apti 6Document8 pagesTcs Apti 6kumaranrajPas encore d'évaluation

- Tcs Apti3Document8 pagesTcs Apti3kumaranrajPas encore d'évaluation

- Tcs Apti 7Document8 pagesTcs Apti 7kumaranrajPas encore d'évaluation

- Tcs Apti 5Document8 pagesTcs Apti 5kumaranrajPas encore d'évaluation

- Tcs Apti2Document8 pagesTcs Apti2kumaranrajPas encore d'évaluation

- Tcs Apti1Document7 pagesTcs Apti1kumaranrajPas encore d'évaluation

- Class 02 Transistors I - DetailsDocument24 pagesClass 02 Transistors I - DetailskumaranrajPas encore d'évaluation

- Class 04: Device Physics I: Joseph A. Elias, PHDDocument13 pagesClass 04: Device Physics I: Joseph A. Elias, PHDkumaranrajPas encore d'évaluation

- Aptitude PapDocument3 pagesAptitude PapkumaranrajPas encore d'évaluation

- Class 12 Multiplexors and DecodersDocument5 pagesClass 12 Multiplexors and DecoderskumaranrajPas encore d'évaluation

- PG Course IN ANNA UNIVDocument16 pagesPG Course IN ANNA UNIVkumaranrajPas encore d'évaluation

- An Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationDocument5 pagesAn Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationkumaranrajPas encore d'évaluation

- Embedded Systems Syllabus PSGDocument15 pagesEmbedded Systems Syllabus PSGkumaranrajPas encore d'évaluation

- M.E. Vlsi Design: Anna University of Technology Madurai MADURAI - 625002 Regulations 2010 Curriculam & SyllabiDocument34 pagesM.E. Vlsi Design: Anna University of Technology Madurai MADURAI - 625002 Regulations 2010 Curriculam & SyllabikumaranrajPas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- SFR/U9034: Advanced Power MOSFETDocument8 pagesSFR/U9034: Advanced Power MOSFETRobson JuniorPas encore d'évaluation

- Universidad Nacional Mayor de San Marcos: Apellidos y Nombres: CódigoDocument8 pagesUniversidad Nacional Mayor de San Marcos: Apellidos y Nombres: CódigoKarenPas encore d'évaluation

- 6N60Document6 pages6N60nishatiwari82Pas encore d'évaluation

- Fabrication of Ic'sDocument14 pagesFabrication of Ic'sBhaskar Rao OndruPas encore d'évaluation

- Lecture 20: Introduction To Semiconductor ManufacturingDocument17 pagesLecture 20: Introduction To Semiconductor ManufacturingsuganyaPas encore d'évaluation

- Photolithography LessonsDocument4 pagesPhotolithography LessonsDeep BhattacharjeePas encore d'évaluation

- VLSI Lab Journal 1Document98 pagesVLSI Lab Journal 1KUMAR HIMANSHUPas encore d'évaluation

- NPCIL ET Electronics Question Paper 2011 Model Paper With AnswersDocument7 pagesNPCIL ET Electronics Question Paper 2011 Model Paper With Answerssourav_cybermusicPas encore d'évaluation

- A Transistor Is A Semiconductor Device Used To Amplify or Switch Electronic Signals and Electrical PowerDocument2 pagesA Transistor Is A Semiconductor Device Used To Amplify or Switch Electronic Signals and Electrical PowerGeorge NeagoePas encore d'évaluation

- VLSI Important QuestionsDocument19 pagesVLSI Important Questionsratnams100% (1)

- Asic Design Flow Tutorial 3228glDocument138 pagesAsic Design Flow Tutorial 3228glMahesh Reddy MandapatiPas encore d'évaluation

- Sem V Bee 502power ElectronicsDocument111 pagesSem V Bee 502power ElectronicsnazibPas encore d'évaluation

- Literature Review of Gan, Ldmos and DC-DC Buck Converter: Author-Rishabh Soni (T19125)Document3 pagesLiterature Review of Gan, Ldmos and DC-DC Buck Converter: Author-Rishabh Soni (T19125)t19125 t19125Pas encore d'évaluation

- To Study and Plot The I-V Characteristics of A P-N JunctionDocument2 pagesTo Study and Plot The I-V Characteristics of A P-N Junctionamuhammadahsan73Pas encore d'évaluation

- BT169Document4 pagesBT169ketab_doostPas encore d'évaluation

- CD4007 - FetDocument5 pagesCD4007 - FetFrancisco LaudaresPas encore d'évaluation

- Sub: VLSI Design 4-1 ECE Descriptive Questions: Ds DsDocument3 pagesSub: VLSI Design 4-1 ECE Descriptive Questions: Ds DsMohan DasPas encore d'évaluation

- Bece201l Electronic-Materials-And-Devices TH 1.0 0 Bece201lDocument3 pagesBece201l Electronic-Materials-And-Devices TH 1.0 0 Bece201lkambojnaman2005Pas encore d'évaluation

- A CMOS-integrated Compute-In-Memory MacroDocument10 pagesA CMOS-integrated Compute-In-Memory MacroMo SongPas encore d'évaluation

- Bipolar Junction Transistor (BJT)Document36 pagesBipolar Junction Transistor (BJT)Muhammad AmeenPas encore d'évaluation

- GeSemiconductorDataHandbook1977 Text PDFDocument1 378 pagesGeSemiconductorDataHandbook1977 Text PDFAnonymous xAqiGcQdDL100% (5)

- Electronic Devices Lab MANUALDocument24 pagesElectronic Devices Lab MANUALna_hariprsadPas encore d'évaluation

- MarblesDocument4 pagesMarblesrubixkubePas encore d'évaluation

- KH Distributors - Electronic Components - PriceListJan2009Document30 pagesKH Distributors - Electronic Components - PriceListJan2009ryan780926Pas encore d'évaluation

- HCF4069UB: Hex InverterDocument8 pagesHCF4069UB: Hex InverterJoel PalzaPas encore d'évaluation

- Thyristor and Its ApplicationsDocument22 pagesThyristor and Its ApplicationsLouisPas encore d'évaluation

- Sub Threshold Region Modeling and EquationsDocument9 pagesSub Threshold Region Modeling and EquationsSatish BojjawarPas encore d'évaluation

- 2SC5343 PDFDocument5 pages2SC5343 PDFIslam RabiePas encore d'évaluation

- IndusDocument7 pagesIndusTristan Cabatac100% (1)

- IXFH20N80P IXYSCorporationDocument5 pagesIXFH20N80P IXYSCorporationMantenimiento AsistelPas encore d'évaluation