Académique Documents

Professionnel Documents

Culture Documents

Version

Transféré par

John NgCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Version

Transféré par

John NgDroits d'auteur :

Formats disponibles

This is version 1.5 of the MC8051 IP core.

September 2006: Oregano Systems - Design & Consulting GesmbH ============================================================ Changes: - When an interrupt is pending and the instruction executed is RETI or a write access to IE or IP one more instruction is executed before vectoring to the interrupt routine. - The synchronization stage of the interrupt inputs in the timer/counter unit has been hardended with additional series flip-flops due to the high operating frequencies nowadays in use. - A prescaler in the serial interface unit has been changed to 1/12 instead of 1/16 to conform to mode 0 databook descriptions. - The carry flag was incorrectly reset during a special situation. This has been corrected. - tmr/ctr1 erroneously used his run flag when tmr/ctr0 was in mode 3. This has been corrected. - In certain interrupt situations the stack pointer has been erroneously set. This has been corrected. ============================================================ Oregano Systems - Design & Consulting GesmbH Phorusgasse 8, A-1040 Vienna @: mc8051@oregano.at W: http://oregano.at/ip/8051.htm

************************************************************ This is version 1.4 of the MC8051 IP core. November 2004: Oregano Systems - Design & Consulting GesmbH ============================================================ Changes: - corrected behaviour of RETI instruction handling - added synchronization for interrupt signals - corrected timer problems

************************************************************ This is version 1.3 of the MC8051 IP core. September 2002: Oregano Systems - Design & Consulting GesmbH ============================================================ Change history: - Improved tb_mc8051_siu_sim.vhd to verify duplex operation. - Corrected problem with duplex operation in file mc8051_siu_rtl.vhd

************************************************************ This is version 1.2. of the MC8051 IP core. June 2002 - Oregano Systems - Design & Consulting GesmbH ============================================================ Change history:

- Eliminated the scr subdirectory form the distribution. - Improved documentation. - Corrected several bugs in the source code (see the website for more details). - Improved the testbench with respect to the I/O port behavior. - Enriched the msim directory with the assembler source code of an example program. - Provided the source code of a Intel hex to binary textfile converter to ease simulation of the user's assambler programs.

************************************************************ This is version 1.1. of the MC8051 IP core. Jan 31st 2002 - Oregano Systems - Design & Consulting GesmbH

Vous aimerez peut-être aussi

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- M160-6 Design Control ProcedureDocument20 pagesM160-6 Design Control ProcedureBrewer HousePas encore d'évaluation

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Big Data Management For Dummies Informatica EdDocument53 pagesBig Data Management For Dummies Informatica Edpearlramar100% (3)

- Basic PLC Program Design ExamplesDocument169 pagesBasic PLC Program Design ExamplesAlexCanenciaPas encore d'évaluation

- Ceb 72-3285Document2 pagesCeb 72-3285turboshaftPas encore d'évaluation

- AnyBody TutorialsDocument256 pagesAnyBody Tutorialsromulozg100% (1)

- Tatuil TendenangDocument466 pagesTatuil TendenangJosias D TatontosPas encore d'évaluation

- Cloud Control 13 CDocument23 pagesCloud Control 13 CMayerling Alarcon VPas encore d'évaluation

- Cisco Switching Basics.Document272 pagesCisco Switching Basics.Vipin AroraPas encore d'évaluation

- Computer Teaching Guide 8 PDFDocument108 pagesComputer Teaching Guide 8 PDFMuhammad Asif75% (4)

- Hkcee Mathematics - 4.1 Polynomials - Function and Graph - P.1Document3 pagesHkcee Mathematics - 4.1 Polynomials - Function and Graph - P.1Kathy WongPas encore d'évaluation

- HTTP en Wikipedia Org Wiki Bell Labshttp en Wikipedia Org Wiki Alexander Graham BellDocument1 pageHTTP en Wikipedia Org Wiki Bell Labshttp en Wikipedia Org Wiki Alexander Graham BellJohn NgPas encore d'évaluation

- HTTP en Wikipedia Org Wiki History of UnixDocument6 pagesHTTP en Wikipedia Org Wiki History of UnixJohn NgPas encore d'évaluation

- Arg TestDocument1 pageArg TestJohn NgPas encore d'évaluation

- HTTP en Wikipedia Org Wiki Bell LabsDocument7 pagesHTTP en Wikipedia Org Wiki Bell LabsJohn NgPas encore d'évaluation

- Q 2Document22 pagesQ 2John NgPas encore d'évaluation

- M 3Document3 pagesM 3John NgPas encore d'évaluation

- Q 4Document75 pagesQ 4John NgPas encore d'évaluation

- Q 3Document31 pagesQ 3John NgPas encore d'évaluation

- SDSWFFDocument110 pagesSDSWFFJohn NgPas encore d'évaluation

- Q 1Document10 pagesQ 1John NgPas encore d'évaluation

- M 2Document2 pagesM 2John NgPas encore d'évaluation

- M 1Document3 pagesM 1John NgPas encore d'évaluation

- SDSWFFDocument110 pagesSDSWFFJohn NgPas encore d'évaluation

- VfvfvddssaaDocument1 pageVfvfvddssaaJohn NgPas encore d'évaluation

- Tweet Topics2Document1 104 pagesTweet Topics2John NgPas encore d'évaluation

- VfvfvddssaaDocument1 pageVfvfvddssaaJohn NgPas encore d'évaluation

- DdsDocument1 pageDdsJohn NgPas encore d'évaluation

- Attemp 3Document3 pagesAttemp 3John NgPas encore d'évaluation

- QqsqsDocument1 pageQqsqsJohn NgPas encore d'évaluation

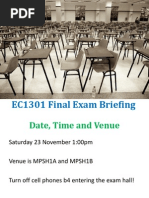

- Final Exam Briefing-1dfdsfdsDocument13 pagesFinal Exam Briefing-1dfdsfdsJohn NgPas encore d'évaluation

- VCVCDDDocument1 pageVCVCDDJohn NgPas encore d'évaluation

- VVVVDocument1 pageVVVVJohn NgPas encore d'évaluation

- HW HW HW HS HW HSDocument1 pageHW HW HW HS HW HSJohn NgPas encore d'évaluation

- QqsqsDocument1 pageQqsqsJohn NgPas encore d'évaluation

- QqsqsDocument1 pageQqsqsJohn NgPas encore d'évaluation

- QqssDocument1 pageQqssJohn NgPas encore d'évaluation

- DdsDocument1 pageDdsJohn NgPas encore d'évaluation

- Temp 1Document1 pageTemp 1John NgPas encore d'évaluation

- TempDocument1 pageTempJohn NgPas encore d'évaluation

- Applicant Response CTD Rev 1 2012 02Document7 pagesApplicant Response CTD Rev 1 2012 02silviaperPas encore d'évaluation

- PorjDocument4 pagesPorjTaimenTaiPas encore d'évaluation

- CortanaDocument5 pagesCortanaAseel JameelPas encore d'évaluation

- Experienced Golang and C++ Developer Seeking New OpportunitiesDocument2 pagesExperienced Golang and C++ Developer Seeking New OpportunitiesAmit VermaPas encore d'évaluation

- Solution Manager CEN Alerting GuideDocument5 pagesSolution Manager CEN Alerting GuidebardouniPas encore d'évaluation

- Kornak - (STM32-Discovery-F4) - 0001 Rev 1.00 Module Pinouts & FunctionsDocument29 pagesKornak - (STM32-Discovery-F4) - 0001 Rev 1.00 Module Pinouts & Functionsfred5678Pas encore d'évaluation

- Warping Constant of Open Sections With Arbitrary Profile Geometry Rev 1 2011Document24 pagesWarping Constant of Open Sections With Arbitrary Profile Geometry Rev 1 2011hoojztePas encore d'évaluation

- Monkey JamDocument7 pagesMonkey JamMahendra AdityaPas encore d'évaluation

- PrintDocument3 pagesPrintAmirul SyakirPas encore d'évaluation

- DCO Introduction - Pega PRPC v5.5Document10 pagesDCO Introduction - Pega PRPC v5.5Seheri Sowmya RajPas encore d'évaluation

- Lab 1 StudentDocument21 pagesLab 1 StudentyemivesPas encore d'évaluation

- DullGelinasWheeler9e TB Chapter 03Document18 pagesDullGelinasWheeler9e TB Chapter 03JimboWinePas encore d'évaluation

- Computer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsDocument68 pagesComputer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsNapsterPas encore d'évaluation

- D. Null OperatorDocument49 pagesD. Null OperatorPlayIt All100% (2)

- Data Structure Lab AssignmentDocument38 pagesData Structure Lab AssignmentAbhratanu PalPas encore d'évaluation

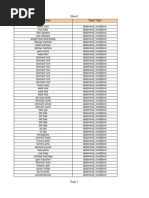

- Tabel Entrian SDM DinkesDocument71 pagesTabel Entrian SDM Dinkesfredian siskaPas encore d'évaluation

- HR Consulting Services of IbmDocument6 pagesHR Consulting Services of IbmKîshórè KümãrPas encore d'évaluation

- Windows 7 Cheat SheetDocument4 pagesWindows 7 Cheat SheetAndrey FadinPas encore d'évaluation

- Exam QuestionDocument25 pagesExam QuestiononePas encore d'évaluation

- Dse334 Data Sheet (Usa)Document2 pagesDse334 Data Sheet (Usa)naveedPas encore d'évaluation