Académique Documents

Professionnel Documents

Culture Documents

74AC02

Transféré par

Alexandre S. CorrêaDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

74AC02

Transféré par

Alexandre S. CorrêaDroits d'auteur :

Formats disponibles

74AC0274ACT02 Quad 2-Input NOR Gate

November 1988 Revised November 1999

74AC0274ACT02 Quad 2-Input NOR Gate

General Description

The AC02/ACT02 contains four, 2-input NOR gates.

Features

s ICC reduced by 50% on 74AC02 only s Outputs source/sink 24 mA s ACT02 has TTL-compatible inputs

Ordering Codes:

Order Number 74AC02SC 74AC02SJ 74AC02MTC 74AC02PC 74ACT02SC 74ACT02MTC 74ACT02PC Package Number M14A M14D MTC14 N14A M14A MTC14 N14A Package Description 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow Body 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow Body 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Device also available in Tape and Reel. Specify by appending suffix letter X to the ordering code. (PC not available in Tape and Reel.)

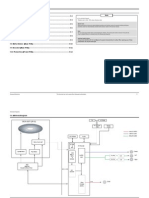

Logic Symbol

IEEE/IEC

Connection Diagram

Pin Descriptions

Pin Names An , Bn On Description Inputs Outputs

FACT is a trademark of Fairchild Semiconductor Corporation.

1999 Fairchild Semiconductor Corporation

DS009912

www.fairchildsemi.com

74AC0274ACT02

Absolute Maximum Ratings(Note 1)

Supply Voltage (VCC) DC Input Diode Current (IIK) VI = 0.5V VI = VCC + 0.5V DC Input Voltage (VI) DC Output Diode Current (IOK) VO = 0.5V VO = VCC + 0.5V DC Output Voltage (VO) DC Output Source or Sink Current (IO) DC VCC or Ground Current per Output Pin (ICC or IGND) Storage Temperature (TSTG) Junction Temperature (TJ) PDIP 140C 50 mA 65C to +150C 50 mA 20 mA +20 mA 0.5V to VCC + 0.5V 20 mA +20 mA 0.5V to VCC + 0.5V 0.5V to +7.0V

Recommended Operating Conditions

Supply Voltage (VCC) AC ACT Input Voltage (VI) Output Voltage (VO) Operating Temperature (TA) Minimum Input Edge Rate (V/t) AC Devices VIN from 30% to 70% of VCC VCC @ 3.3V, 4.5V, 5.5V Minimum Input Edge Rate (V/t) ACT Devices VIN from 0.8V to 2.0V VCC @ 4.5V, 5.5V 125 mV/ns

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT circuits outside databook specifications.

2.0V to 6.0V 4.5V to 5.5V 0V to VCC 0V to VCC 40C to +85C

125 mV/ns

DC Electrical Characteristics for AC

Symbol VIH Parameter Minimum HIGH Level Input Voltage VIL Maximum LOW Level Input Voltage VOH Minimum HIGH Level Output Voltage VCC (V) 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 3.0 4.5 5.5 VOL Maximum LOW Level Output Voltage 3.0 4.5 5.5 3.0 4.5 5.5 IIN (Note 4) Maximum Input Leakage Current IOLD IOHD ICC (Note 4) Minimum Dynamic Output Current (Note 3) Maximum Quiescent Supply Current 5.5 5.5 5.5 5.5 2.0 0.002 0.001 0.001 TA = +25C Typ 1.5 2.25 2.75 1.5 2.25 2.75 2.99 4.49 5.49 2.1 3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 2.56 3.86 4.86 0.1 0.1 0.1 0.36 0.36 0.36 0.1 TA = 40C to +85C Guaranteed Limits 2.1 3.15 3.85 0.9 1.35 1.65 2.9 4.4 5.4 VIN = VIL or VIH 2.46 3.76 4.76 0.1 0.1 0.1 VIN = VIL or VIH 0.44 0.44 0.44 1.0 75 75 20.0 A mA mA A V IOL = 12 mA IOL = 24 mA IOL = 24 mA (Note 2) VI = VCC, GND VOLD = 1.65V Max VOHD = 3.85V Min VIN = VCC or GND V IOUT = 50 A V IOH = 12 mA IOH = 24 mA IOH = 24 mA (Note 2) V IOUT = 50 A V VOUT = 0.1V or VCC 0.1V V Units Conditions VOUT = 0.1V or VCC 0.1V

Note 2: All outputs loaded; thresholds on input associated with output under test. Note 3: Maximum test duration 2.0 ms, one output loaded at a time. Note 4: IIN and ICC @ 3.0V are guaranteed to be less than or equal to the respective limit @ 5.5V VCC.

www.fairchildsemi.com

74AC0274ACT02

DC Electrical Characteristics for ACT

Symbol VIH VIL VOH Parameter Minimum HIGH Level Input Voltage Maximum LOW Level Input Voltage Minimum HIGH Level Output Voltage VCC (V) 4.5 5.5 4.5 5.5 4.5 5.5 4.5 5.5 VOL Maximum LOW Level Output Voltage 4.5 5.5 4.5 5.5 IIN ICCT IOLD IOHD ICC Maximum Input Leakage Current Maximum ICC/Input Minimum Dynamic Output Current (Note 6) Maximum Quiescent Supply Current 5.5 5.5 5.5 5.5 5.5 4.0 0.6 0.001 0.001 TA = +25C Typ 1.5 1.5 1.5 1.5 4.49 5.49 2.0 2.0 0.8 0.8 4.4 5.4 3.86 4.86 0.1 0.1 0.36 0.36 0.1 TA = 40C to +85C Guaranteed Limits 2.0 2.0 0.8 0.8 4.4 5.4 3.76 4.76 0.1 0.1 0.44 0.44 1.0 1.5 75 75 40.0 Units V V V Conditions VOUT = 0.1V or VCC 0.1V VOUT = 0.1V or VCC 0.1V IOUT = 50 A VIN = VIL or VIH V V IOH = 24 mA IOH = 24 mA (Note 5) IOUT = 50 A VIN = VIL or VIH V A mA mA mA A IOL= 24 mA IOL= 24 mA (Note 5) VI = VCC, GND VI = VCC 2.1V VOLD = 1.65V Max VOHD = 3.85V Min VIN = VCC or GND

Note 5: All outputs loaded; thresholds on input associated with output under test. Note 6: Maximum test duration 2.0 ms, one output loaded at a time.

AC Electrical Characteristics for AC

VCC Symbol tPLH tPHL Parameter Propagation Delay Propagation Delay (V) (Note 7) 3.3 5.0 3.3 5.0

Note 7: Voltage Range 3.3 is 3.3V 0.3V Voltage Range 5.0 is 5.0V 0.5V

TA = +25C CL = 50 pF Min 1.5 1.5 1.5 1.5 Typ 5.0 4.0 5.0 4.5 Max 7.5 6.0 7.5 6.5

TA = 40C to +85C CL = 50 pF Min 1.0 1.0 1.0 1.0 Max 8.0 6.5 8.0 7.0 ns ns Units

AC Electrical Characteristics for ACT

VCC Symbol tPLH tPHL Parameter Propagation Delay Propagation Delay (V) (Note 8) 5.0 5.0 Min 1.0 1.0 TA = +25C CL = 50 pF Typ 6.0 6.5 Max 8.5 9.5 TA = 40C to +85C CL = 50 pF Min 1.0 1.0 Max 9.0 10.0 ns ns Units

Note 8: Voltage Range 5.0 is 5.0V 0.5V

Capacitance

Symbol CIN CPD Parameter Input Capacitance Power Dissipation Capacitance Typ 4.5 30.0 Units pF pF VCC = OPEN VCC = 5.0V Conditions

www.fairchildsemi.com

74AC0274ACT02

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow Body Package Number M14A

www.fairchildsemi.com

74AC0274ACT02

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide Package Number M14D

www.fairchildsemi.com

74AC0274ACT02

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Thin Shrink Small Outline Package (TSSOP) JEDEC MO-153, 4.4mm Wide Package Number MTC14

www.fairchildsemi.com

74AC0274ACT02 Quad 2-Input NOR Gate

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 7 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

www.fairchildsemi.com

Vous aimerez peut-être aussi

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsD'EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Yamaha Receiver Rxv-595 SchematicDocument7 pagesYamaha Receiver Rxv-595 SchematicMauricio Bumba100% (1)

- The UltralightDocument20 pagesThe UltralightAlexandre S. Corrêa100% (2)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Build Your Own VAWT by David MussellDocument17 pagesBuild Your Own VAWT by David MussellMr Void100% (9)

- Vistabule 2014 Feb Brochure LRDocument10 pagesVistabule 2014 Feb Brochure LRAlexandre S. CorrêaPas encore d'évaluation

- Build "Wild Goose": A Sturdy Overnight TrailerDocument7 pagesBuild "Wild Goose": A Sturdy Overnight TrailerAlexandre S. CorrêaPas encore d'évaluation

- 8051 Microcontroller: An Applications Based IntroductionD'Everand8051 Microcontroller: An Applications Based IntroductionÉvaluation : 5 sur 5 étoiles5/5 (6)

- Beginning Digital Electronics through ProjectsD'EverandBeginning Digital Electronics through ProjectsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Modular CNC Router 2009v1 FREE PLANSDocument10 pagesModular CNC Router 2009v1 FREE PLANSModularCNC57% (7)

- 74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesDocument8 pages74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesAini NierisPas encore d'évaluation

- 74AC04, 74ACT04 Hex Inverter: Features General DescriptionDocument10 pages74AC04, 74ACT04 Hex Inverter: Features General Descriptionarao_filhoPas encore d'évaluation

- 74AC08, 74ACT08 Quad 2-Input AND Gate: Features General DescriptionDocument10 pages74AC08, 74ACT08 Quad 2-Input AND Gate: Features General DescriptioniknowwhatudidPas encore d'évaluation

- Datasheet 74HCT14Document7 pagesDatasheet 74HCT14Humberto AcostaPas encore d'évaluation

- 74HC04Document7 pages74HC04Brian DoylePas encore d'évaluation

- DatasheetDocument8 pagesDatasheetMaizatul Hanisah RoziPas encore d'évaluation

- 74HC14 PDFDocument8 pages74HC14 PDFNielsy R. Aparicio QuirogaPas encore d'évaluation

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocument7 pagesMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CePas encore d'évaluation

- Quad 2-Input and Gate: Order CodesDocument8 pagesQuad 2-Input and Gate: Order CodesMaizatul Hanisah RoziPas encore d'évaluation

- 74AC74Document9 pages74AC74ciernesPas encore d'évaluation

- 7Z08Document7 pages7Z08André Frota PaivaPas encore d'évaluation

- CD4023Document6 pagesCD4023Jules Le GrandPas encore d'évaluation

- 74HC08Document7 pages74HC08Brian DoylePas encore d'évaluation

- CD4011BCDocument10 pagesCD4011BCKike DavilaPas encore d'évaluation

- CD4093 PDFDocument8 pagesCD4093 PDFIván IvanovPas encore d'évaluation

- CD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesDocument8 pagesCD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesbanoluPas encore d'évaluation

- DatasheetDocument9 pagesDatasheetLuis Caba RamirezPas encore d'évaluation

- 74LVX32 Low Voltage Quad 2-Input OR Gate: General Description FeaturesDocument5 pages74LVX32 Low Voltage Quad 2-Input OR Gate: General Description FeaturesAlexandre S. CorrêaPas encore d'évaluation

- MM74HC164 8-Bit Serial-in/Parallel-out Shift Register: General DescriptionDocument7 pagesMM74HC164 8-Bit Serial-in/Parallel-out Shift Register: General Descriptionmalirezazadeh5549Pas encore d'évaluation

- MM74HC139 Dual 2-To-4 Line Decoder: General DescriptionDocument7 pagesMM74HC139 Dual 2-To-4 Line Decoder: General DescriptionnizarfebPas encore d'évaluation

- 74HC240Document8 pages74HC240rajesha_sPas encore d'évaluation

- 023M01 (Triple NAND Gate)Document7 pages023M01 (Triple NAND Gate)el_george0079491Pas encore d'évaluation

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoPas encore d'évaluation

- Compuerta and 74HC08Document9 pagesCompuerta and 74HC08Elio GranadosPas encore d'évaluation

- HCF4081Document10 pagesHCF4081satyamcafe_vidishaPas encore d'évaluation

- 4073Document7 pages4073S Eko AnangPas encore d'évaluation

- 74AHC1G86 74AHCT1G86: 1. General DescriptionDocument12 pages74AHC1G86 74AHCT1G86: 1. General DescriptionKushalSwamyPas encore d'évaluation

- Hex Buffer/Converter: Order CodesDocument8 pagesHex Buffer/Converter: Order CodespopovjimPas encore d'évaluation

- 74LS86P PDFDocument6 pages74LS86P PDFOsman KoçakPas encore d'évaluation

- 74LS393-Dual 4-Bit Binary CounterDocument6 pages74LS393-Dual 4-Bit Binary Counterkakashi116Pas encore d'évaluation

- CD54/74HC688, CD54/74HCT688: Features DescriptionDocument6 pagesCD54/74HC688, CD54/74HCT688: Features Descriptionbhavsar_vaibhavPas encore d'évaluation

- HCC4073B/81B/82B HCF4073B/81B/82B: and GatesDocument10 pagesHCC4073B/81B/82B HCF4073B/81B/82B: and GatessttepencambiandoPas encore d'évaluation

- MM74HCT540 - MM74HCT541 Inverting Octal 3-STATE Buffer - Octal 3-STATE BufferDocument7 pagesMM74HCT540 - MM74HCT541 Inverting Octal 3-STATE Buffer - Octal 3-STATE Buffermeroka2000Pas encore d'évaluation

- CD40106BE DatasheetDocument10 pagesCD40106BE DatasheetOscar GonzalesPas encore d'évaluation

- 74AC541, 74ACT541 Octal Buffer/Line Driver With 3-STATE OutputsDocument11 pages74AC541, 74ACT541 Octal Buffer/Line Driver With 3-STATE OutputsPerez JuanPas encore d'évaluation

- Hex Inverter Technical Data SheetDocument5 pagesHex Inverter Technical Data SheetIonut SimaPas encore d'évaluation

- C.I 74HC175Document7 pagesC.I 74HC175DOMINGOS ALADIRPas encore d'évaluation

- 27C512Document12 pages27C512technicalavrPas encore d'évaluation

- 74ACT244Document12 pages74ACT244nevdullPas encore d'évaluation

- CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDocument6 pagesCD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDouglas CorderoPas encore d'évaluation

- 4024Document6 pages4024Merényi OszkárPas encore d'évaluation

- CD4047Document9 pagesCD4047Haryadi VjPas encore d'évaluation

- TC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderDocument9 pagesTC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderAndrea DispoPas encore d'évaluation

- 74AC74, 74ACT74 Dual D-Type Positive Edge-Triggered Flip-FlopDocument13 pages74AC74, 74ACT74 Dual D-Type Positive Edge-Triggered Flip-FlopMudasir UmarPas encore d'évaluation

- CD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionDocument13 pagesCD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionWissam NawfalPas encore d'évaluation

- 7402Document9 pages7402eredrag07Pas encore d'évaluation

- 74VHC14 Hex Schmitt Inverter: Features General DescriptionDocument8 pages74VHC14 Hex Schmitt Inverter: Features General DescriptionAriel NavarretePas encore d'évaluation

- Quad Exclusive or Gate: PD CC oDocument7 pagesQuad Exclusive or Gate: PD CC oHungChiHoPas encore d'évaluation

- Datasheet orDocument9 pagesDatasheet orM Mustafa GözüküçükPas encore d'évaluation

- Octal 3-State Noninverting Transparent Latch: SL74HC573Document5 pagesOctal 3-State Noninverting Transparent Latch: SL74HC573Prayu GarnurmPas encore d'évaluation

- MM74HC14 Hex Inverting Schmitt Trigger: Features General DescriptionDocument10 pagesMM74HC14 Hex Inverting Schmitt Trigger: Features General Descriptiond_richard_dPas encore d'évaluation

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsD'EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsÉvaluation : 1 sur 5 étoiles1/5 (1)

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsD'EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercPas encore d'évaluation

- Manual Transistor PDFDocument4 pagesManual Transistor PDFAlexandre S. CorrêaPas encore d'évaluation

- Optical Comp Exp - Edu SilvaDocument6 pagesOptical Comp Exp - Edu SilvaAlexandre S. CorrêaPas encore d'évaluation

- F e A T U R e SDocument2 pagesF e A T U R e SAlexandre S. CorrêaPas encore d'évaluation

- Manual 2016 Nitro g5Document2 pagesManual 2016 Nitro g5Alexandre S. CorrêaPas encore d'évaluation

- Schematic Diagrams: Special NoteDocument12 pagesSchematic Diagrams: Special NoteAlexandre S. Corrêa100% (1)

- CCE TV HPS-2071B Diagrama EsquematicoDocument1 pageCCE TV HPS-2071B Diagrama EsquematicoDaniel AvecillaPas encore d'évaluation

- 4HD D0049.0611 - 06FDocument104 pages4HD D0049.0611 - 06FCarlosLimaPas encore d'évaluation

- 1947 Trailer For TwoDocument7 pages1947 Trailer For TwoAlexandre S. CorrêaPas encore d'évaluation

- Sansung CL21A551MLDocument9 pagesSansung CL21A551MLleno2Pas encore d'évaluation

- Cold Cold HOT HOT: QFP80 QFP80Document1 pageCold Cold HOT HOT: QFP80 QFP80Jone Ferreira Dos SantosPas encore d'évaluation

- XR-A550 XR-A330: Stereo CD Cassette Deck ReceiverDocument82 pagesXR-A550 XR-A330: Stereo CD Cassette Deck ReceiverAlexandre S. CorrêaPas encore d'évaluation

- Ta 8403 KDocument5 pagesTa 8403 KFlorenz RemasteredPas encore d'évaluation

- Schematic Diagram DVD-P370Document8 pagesSchematic Diagram DVD-P370Alexandre S. Corrêa0% (1)

- Datasheet 7400Document9 pagesDatasheet 7400gab50Pas encore d'évaluation

- 74574Document6 pages74574Alexandre S. CorrêaPas encore d'évaluation

- 74573Document4 pages74573jamesrychurdPas encore d'évaluation

- TDA2002 10wDocument21 pagesTDA2002 10wAlexandre S. CorrêaPas encore d'évaluation

- ICL7106 and ICL7107 VoltmeterDocument16 pagesICL7106 and ICL7107 VoltmeterAntonino ScordatoPas encore d'évaluation

- 74688Document4 pages74688Alexandre S. CorrêaPas encore d'évaluation

- Tip41-2 20wDocument3 pagesTip41-2 20wAlexandre S. CorrêaPas encore d'évaluation

- TL 074Document10 pagesTL 074Alexandre S. CorrêaPas encore d'évaluation

- DC Da90Document24 pagesDC Da90Alexandre S. CorrêaPas encore d'évaluation

- 74VHCU04Document6 pages74VHCU04Alexandre S. CorrêaPas encore d'évaluation

- 802Document4 pages802BooksPas encore d'évaluation