Académique Documents

Professionnel Documents

Culture Documents

High Power High Efficiency Power Amplifier Reference Design in IIIV Wide Bandgap GaN

Transféré par

Narasimha SunchuCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

High Power High Efficiency Power Amplifier Reference Design in IIIV Wide Bandgap GaN

Transféré par

Narasimha SunchuDroits d'auteur :

Formats disponibles

High-power, High-efficiency Power Amplifier Reference Design in IIIV Wide Bandgap Gallium Nitride Technology using Nonlinear Vector

Network Analyzer and X-parameters

Troels S. Nielsen, Ulrik R. Madsen, and Michael Dieudonn, Agilent Technologies, Measurement Research Labs, B-3110 Rotselaar, Belgium

Abstract This paper presents a complete power amplifier design using new Nonlinear Vector Network Analyzer (NVNA) and X-parameter technologies. A high-power, pulsed Continuous Wave (CW) NVNA setup is presented and harmonic tuning capabilities of the measured X-parameter model is demonstrated using the same setup. From fundamental and harmonic impedance tuning, input and output power amplifier matching networks are synthesized and first-pass design success is confirmed by measurements of the fabricated power amplifier. Index Terms Nonlinear vector network analyzer, Xparameters, behavioral modeling, power amplifier design, gallium nitride, high power, high efficiency.

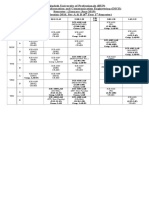

accurately [5]. In this paper, it is demonstrated how nonlinear VNA and X-parameters are used to bridge the gap currently found between GaN transistor physics and simulator models in a complete power amplifier design developed entirely inside the circuit simulator, but based on measured nonlinear data. Section II outlines the details of the hardware setup used to measure X-parameters of a commercially available GaN power transistor. Section III describes the amplifier design developed in the circuit simulator. Section IV compares results from the circuit simulator to measurement results of the fabricated PA. II. PULSED CW X-PARAMETER MEASUREMENTS USING NVNA In this work, an unmatched 10W High Electron Mobility Transistor (HEMT) is used (CGH40010F from CREE). The power transistor is biased in deep Class AB operation and the hardware setup used to characterize the transistor and extract its X-parameters is shown in Fig. 1. Essential to this setup is the N5242A 10MHz to 26.5GHz 4 port PNA-X with two phase comb generators (U9391C) for cross-frequency phase calibration and measurement. The following NVNA firmware capabilities are installed on the instrument: Option 510 (Base NVNA firmware), Option 514 (X-parameters), and Option 520 (Load-dependent X-parameter extension). The PNAX/NVNA controls all hardware in the setup as well as the complete X-parameter measurement sequence.

I. INTRODUCTION Compact transistor models currently available for wide bandgap III-V technologies such as Gallium Nitride (GaN) generally suffer from long development times and limited accuracy [1]. Inaccuracies are largely attributed to details in the device physics that may not yet be fully known or accurately implemented into the underlying model framework. Using NVNA data, however, there have been significant recent advances [2]. And, also based on NVNA, X-parameters have recently been demonstrated as a powerful behavioral level modeling approach with appealing device model properties [3, 4]. Contrary to compact models, this type of model assumes no a priori knowledge of the internal device composition. Instead, it relies exclusively on wisely selected large-signal measurements and mathematical fitting functions, which may approximate device transfer characteristics very

N6705A DC Power Analyzer

34411A 6 Digit Multimeter

AR60S1G4 W Tuner Part of U3020A

CGH40010F in ICM fixture W Tuner N2783A Current probe Part of U3020A

ZHL-16W-43+

Copyright 2011 IEEE. Reprinted from 2011 IEEE COMCAS, Tel Aviv, Israel, November 7-9. This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of Crees products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

+34dBm -19dBm -39dBm (ET) NVNA Port 1 +28dBm +8dBm (ET) Part of U3020A

+33dBm +27dBm +7dBm (ET)

A. Calibration The NVNA calibration includes three steps: Vector calibration, phase calibration, and amplitude calibration. NVNA calibration reference planes are defined at the tuner APC7 coaxial connectors. The TRL based fixture files are then used to de-embed measurements to the device gate and drain terminals. Phase calibration establishes a harmonic phase reference signal with a constant phase relationship versus frequency. Incident and reflected waves are ratioed against this signal to eliminate arbitrary phase shifts introduced when sweeping the PNA-X local oscillator. Amplitude calibration corrects the receivers using a power meter at one of the tuners. To avoid damage to the calibration standards, it may be advantageous to calibrate the system after removing preamplifiers or increasing source attenuation. Changing preamplifiers or attenuators between the RF source and reference coupler, does not affect measurement accuracy as the NVNA uses 8-term error vector correction. B. X-parameter Model Validation An essential step in the development of any simulation model is validation. The extracted load-dependent Xparameter model is validated in multiple ways. First, it is checked against DC and small-signal S-parameter measurements over the range of bias conditions. Then, it is checked against large-signal measurements both at load conditions included in the extraction data (to verify that the model plays-back large-signal measurements correctly) and at independent load conditions not used during model extraction (to validate interpolation capabilities within the measured load grid). Example validation results are presented in Fig 3-4. Although the measurement setup depicted in Fig. 1 employs fundamental tuners only, the X-parameter framework contains, in addition to the large-signal AM/AM and AM/PM transfer functions, also small-signal S and T terms providing harmonic load sensitivities of the DUT behavior at input and output ports [2]. These are derived from phase-swept active source- 50

40 30 20 Power [dBm] 10 0 -10 Fundamental -20 -30 -5 2nd harmonic 3rd harmonic 0 5 10 15 20 Available input power [dBm] 25 30 35

AR60S1G4 G = ~47dB Pmax = +48dBm F = 0.8 to 4.2GHz

CF = 20dB

CF = 20dB

+7dBm (ET)

+27dBm

Tuner

28dB

18dB

+33dBm CGH40010F Fc = 1300MHz G = 14dB (typ) Pout = +41dBm +41dBm

R1 -20dBm A -20dBm +32dBm -13dBm (ET) NVNA Port 3 +30dBm (ET) Part of U3020A +31dBm (ET) +31dBm 15dB

DUT

Tuner

10dB

+21dBm (ET)

ZHL-16W-43+ G = 45dB (typ) Pmax = +41dBm F = 1.3 to 4.0GHz

CF = 20dB

CF = 20dB

32dB

31dB

R3

-20dBm -20dBm

Fig. 2. NVNA power budget is calculated based on DUT specifications and the PNA-X receiver linearity requirements.

As the CGH40010F is packaged, a microwave transistor test fixture is used to establish measurement reference planes directly at the transistor gate and drain terminals from an infixture TRL calibration. All measurements are performed under pulsed Continuous Wave (CW) conditions using a 1.3GHz carrier frequency with 100S pulse width and 10% duty cycle. Pulse generators and pulse modulators internal to the PNA-X are used to control the RF pulse conditions [6]. Standard PNA-X input power ratings are typically +30dBm at the test ports (or +40dBm with Option H85). Thus, to accommodate DUT power levels, a high-power NVNA test set (U3020A) is employed and adequate power levels for input drive and X-parameter output measurements are provided by two linear bench amplifiers (AR60S1G4 and ZHL-16W-43+, respectively). To sustain measurement receiver linearity requirements (-20dBm at receivers at peak powers), the NVNA power budget is calculated from DUT specifications and sufficient attenuation is added at receiver inputs (Fig. 2). The measurement setup is also equipped with fundamental mechanical tuners to extend the measured X-parameter model into highly mismatched source and load conditions [7]. Tuner control software is installed directly on the PNA-X platform. Two N6705A DC power analyzer modules are used for device gate and drain DC biasing. Bias conditions are automatically embedded into the measured X-parameter model. Large Electrolytic Capacitors (ELCOs) placed at the transistor fixture combined with lead wire inductance to the fixture drain terminal prevent accurate current measurements using the N6705A DC power analyzer. Instead, an N2783A current probe placed between transistor drain terminal and the ELCOs takes several in-pulse current samples. Samples are then averaged by the NVNA to ensure very accurate Power Added Efficiency (PAE) measurements.

Fig. 3. Simulated (blue) and measured (red) fundamental and harmonic power at RL=29.5+j19.5ohm (not used in extraction data).

Drain current [A]

0.6 0.4 0.2 0 -5 2

Measured Simulated

10 15 20 Available input power [dBm]

25

30

35

Drain current [A]

1 0 -1

Measured Simulated

10

20

30 40 Drain voltage [V]

50

60

70

Fig. 4. Upper: Simulated (blue) and measured (red) device drain current at a fundamental load of 20.1+j26.5ohm. Lower: Simulated (blue) and measured (red) dynamic load lines at a fundamental load of 20.1+j26.5ohm and at +20dBm available input power.

Fig. 6. Measured loads presented to the DUT. Black: Fundamental nd rd loads. Blue: 2 harmonic loads. Red: 3 harmonic loads.

and load-pull measurements and scope out impedance regions around fundamental and harmonic terminations where models can be accurately source- and load-pulled. The effect of S and T terms is readily recognized from comparison between simulated and measured fundamental load-pull results (Fig. 5, black and red contours, respectively). In a fundamental loadpull setup with mechanical tuners like the one in Fig. 1, tuning at the harmonic frequencies is uncontrolled. The slugs used in slide-screw tuners are typically very wideband, but the reflection phase is rotated along the tuner slabline and highly offset at harmonic frequencies (Fig. 6). Due to the Xparameter S and T terms, harmonic impedances must be properly embedded in the simulator to accurately reproduce measured load-pull results (Fig. 5, blue contours). In an amplifier design, purpose of the matching network is not only to provide a certain load line at the fundamental frequency.

Higher order harmonic content, especially in the device output, plays also a major role. The harmonic tuning capabilities demonstrated in Fig. 5 are thus very essential [4]. III. POWER AMPLIFIER DESIGN USING X-PARAMETERS In a deep Class AB operation, harmonic power at the output Z0 is generally unwanted and should either be shorted or reflected back to the device with proper phase angle. Several matching topologies may fulfill such requirements. Here, we employ lowpass filter structures realized using microstrip elements on a high quality Rogers Duroid 6010 laminate. A. Output Match Design objectives are to maximize output power and efficiency while also minimizing harmonic content at the output Z0 (i.e., optimizing amplifier linearity). The chosen output match topology is depicted in Fig. 7 (upper). Albeit the filter structure should be designed in low Q circles, the impact rd on harmonics was also carefully considered. For optimum 3 harmonic suppression, the open stub (osc3) is designed with an electrical length equal to a short at 3Fc. Fig. 7 (lower) shows the idealized element transformation within a constant 0.6 Qn circle. A final transformation to the drain terminal is done using a DC feed with an 80 degrees electrical short at 2Fc. B. Input Match The purpose of the input matching network is to transform source Z0 to a proper gate impedance that yields optimum power gain and stability. At lower frequencies, the CGH40010F has higher gain and is prone to oscillate. For frequency octaves lower than Fc, a series resistor is thus added to limit the source reflection coefficient. The DC gate bias

Fig. 5. Pdel load-pull results. Red: Measured, opt. is +40.4dBm at 33+j12ohm; Black: Simulated with fundamental load tuner impedances only, opt. is +40.3dBm at 38+j9ohm; Blue: Simulated nd rd with fundamental, 2 and 3 harmonic tuner impedances, opt. is at +40.4dBm at 33+j12ohm.

50

80

40

60 Drain efficiency [%]

Pout [dBm]

30

40

20

20

10

10

15 20 25 30 Pin [dBm] & Pout [dBm]

35

40

0 45

Fig. 9. Simulated (solid) and measured (dotted) AM/AM (blue) and drain efficiency (green) power amplifier characteristics. Fig. 7. Upper: Simplified output match topology. Lower: Idealized transformation within a constant Qn circle of 0.6 (shaded area).

feed is constructed using a high impedance meander quarter wavelength transformer with degraded Q to lower the nd reflection circle at the 2 harmonic. IV. RESULTS The fabricated PA is shown in Fig. 8. Simulated and measured amplifier AM/AM and drain efficiency vs. delivered output power is shown in Fig. 9. Measured saturated output power is +41.9dBm (simulation predicts +42.1dBm) and measured max. drain efficiency is 66.6% (simulation predicts 66.7%). Overall simulation and measurement results agree very well. V. CONCLUSIONS In this paper, it has been demonstrated how an unmatched 10W GaN HEMT power transistor can be characterized and modeled using NVNA and X-parameters. From measured Xparameters, a complete high-power, high-efficiency deep class

AB power amplifier was designed in the circuit simulator. Measurements of the fabricated amplifier confirm a first-pass design success with less than 0.2dB and 0.3% overall deviation between simulated and measured amplifier AM/AM and drain efficiency characteristics, respectively. ACKNOWLEDGEMENT Authors would like to thank D. E. Root for fruitful discussions and Agilent Technologies management for supporting this work. REFERENCES

[1] O. Jardel, F. De Groote, C. Charbonniaud, T. Reveyrad, J. P. Teyssier, R. Quere, and D. Floriot, A Drain-lag Model for AlGaN/GaN Power HEMTs, Microwave Symposium, 2007, IEEE/MTT-S International, pp. 601-604, Jun. 2007. [2] J. Xu, J. Horn, M. Iwamoto, D. E. Root, Large-signal FET Model with Multiple Time Scale Dynamics from Nonlinear Vector Network Analyzer Data, IEEE MTT-S International Microwave Symposium Digest, pp. 417-420, May 2010. [3] J. Verspecht, D. E. Root, PolyHarmonic Distortion Modeling, IEEE Microwave Magazine, pp. 44-57, Jun. 2006. [4] J. Horn, G. Simpson, and D. E. Root, GaN Device Modeling with X-parameters, IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), pp. 1-4, Oct. 2010. [5] T. S. Nielsen, Behavioral Modeling of Microwave Power Amplifiers, Chapter 31 in RF and Microwave Circuits, Measurements, and Modeling, CRC Press, Taylor & Francis Group, 2008. [6] Active-Device Characterization in Pulsed Operation Using the PNA-X, Agilent Technologies, Application Note 1408-21. [7] G. Simpson, J. Horn, D. Gunyan, and D. E. Root, Load-pull + NVNA = Enhanced X-parameters for PA Designs with High Mismatch and Technology-independent Large-signal Device Models, ARFTG Microwave Measurement Symposium, 2008, nd 72 , pp. 119-127, Dec. 2009.

Fig. 8. The fabricated PA mounted on an aluminum heat sink.

Vous aimerez peut-être aussi

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- LTCC Coupler Family: Directional/Bi-DirectionalDocument1 pageLTCC Coupler Family: Directional/Bi-DirectionalNarasimha SunchuPas encore d'évaluation

- Filter Design TechniquesDocument124 pagesFilter Design TechniquesNarasimha Sunchu100% (2)

- Discrete FET - PHEMT DevicesDocument65 pagesDiscrete FET - PHEMT DevicesNarasimha SunchuPas encore d'évaluation

- Comm D Runt On Pa Symposium 11Document37 pagesComm D Runt On Pa Symposium 11Narasimha SunchuPas encore d'évaluation

- Model 1H0360-3: Hybrid CouplersDocument1 pageModel 1H0360-3: Hybrid CouplersNarasimha SunchuPas encore d'évaluation

- Model RFP-4047: Hybrid CouplersDocument2 pagesModel RFP-4047: Hybrid CouplersNarasimha SunchuPas encore d'évaluation

- CLF1G0060 10 - 1G0060S 10Document18 pagesCLF1G0060 10 - 1G0060S 10Narasimha SunchuPas encore d'évaluation

- 3 DB Hybrid Coupler, Ca-88 Series: Wireless Band Version, 7-16 or N-Connectors Broadband, 698 - 2,700 MHZ Rev. ADocument1 page3 DB Hybrid Coupler, Ca-88 Series: Wireless Band Version, 7-16 or N-Connectors Broadband, 698 - 2,700 MHZ Rev. ANarasimha SunchuPas encore d'évaluation

- CGH40025Document13 pagesCGH40025Narasimha SunchuPas encore d'évaluation

- CGH40010Document14 pagesCGH40010Narasimha SunchuPas encore d'évaluation

- BLF6G21-10G: 1. Product ProfileDocument12 pagesBLF6G21-10G: 1. Product ProfileNarasimha SunchuPas encore d'évaluation

- BLF8G20LS 200VDocument14 pagesBLF8G20LS 200VNarasimha SunchuPas encore d'évaluation

- BDCN 14 342+Document1 pageBDCN 14 342+Narasimha SunchuPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Modular Heavy Duty Truck TransmissionDocument6 pagesModular Heavy Duty Truck Transmissionphucdc095041Pas encore d'évaluation

- 1.2 The Basic Features of Employee's Welfare Measures Are As FollowsDocument51 pages1.2 The Basic Features of Employee's Welfare Measures Are As FollowsUddipta Bharali100% (1)

- Ateneo de Naga University: Professional Training For Teacher 4.0Document10 pagesAteneo de Naga University: Professional Training For Teacher 4.0Rosemarie BrionesPas encore d'évaluation

- Human Development and Performance Throughout The Lifespan 2nd Edition Cronin Mandich Test BankDocument4 pagesHuman Development and Performance Throughout The Lifespan 2nd Edition Cronin Mandich Test Bankanne100% (28)

- All Worksheets MYSQLDocument33 pagesAll Worksheets MYSQLSample1Pas encore d'évaluation

- Class Routine Final 13.12.18Document7 pagesClass Routine Final 13.12.18RakibPas encore d'évaluation

- Chapter Two: General Design ConsiderationsDocument27 pagesChapter Two: General Design ConsiderationsTeddy Ekubay GPas encore d'évaluation

- 4 PDFDocument81 pages4 PDFMohammad K. NassouraPas encore d'évaluation

- (Word 365-2019) Mos Word MocktestDocument4 pages(Word 365-2019) Mos Word MocktestQuỳnh Anh Nguyễn TháiPas encore d'évaluation

- 19 Uco 578Document20 pages19 Uco 578roshan jainPas encore d'évaluation

- Thesis - A Surlyn® Ionomer As A Self-Healing and Self-Sensing Composite - 2011 - UKDocument194 pagesThesis - A Surlyn® Ionomer As A Self-Healing and Self-Sensing Composite - 2011 - UKAhmedPas encore d'évaluation

- Lesson Exemplar Math 7Document6 pagesLesson Exemplar Math 7Pablo Jimenea100% (2)

- Flow Through A Converging-Diverging Tube and Its Implications in Occlusive Vascular Disease-IDocument9 pagesFlow Through A Converging-Diverging Tube and Its Implications in Occlusive Vascular Disease-IRukhsarAhmedPas encore d'évaluation

- Ad For Guru Ned'S Enlightenment Masterclass 1 of 33Document33 pagesAd For Guru Ned'S Enlightenment Masterclass 1 of 33ElliuggPas encore d'évaluation

- Design of Footing R1Document8 pagesDesign of Footing R1URVESHKUMAR PATELPas encore d'évaluation

- HCH - 15 04 004Document5 pagesHCH - 15 04 004NarvaxisPas encore d'évaluation

- 00.diesel Engine Power Plant Design PDFDocument4 pages00.diesel Engine Power Plant Design PDFmardirad100% (1)

- INJkon 01 4.0 ManualDocument93 pagesINJkon 01 4.0 ManualJansirani SelvamPas encore d'évaluation

- Dpb6013 HRM - Chapter 3 HRM Planning w1Document24 pagesDpb6013 HRM - Chapter 3 HRM Planning w1Renese LeePas encore d'évaluation

- Aristotle Metaphysics Lambda Accessed 201111 Classicalk LibraryDocument19 pagesAristotle Metaphysics Lambda Accessed 201111 Classicalk Librarygijsbo2000Pas encore d'évaluation

- Emerson Mentor MP ManualDocument182 pagesEmerson Mentor MP ManualiampedrooPas encore d'évaluation

- Combinational Logic-Part-2 PDFDocument25 pagesCombinational Logic-Part-2 PDFSAKSHI PALIWALPas encore d'évaluation

- 02 Lab 1.HCIDocument2 pages02 Lab 1.HCILopao SerojemPas encore d'évaluation

- (Ug, PG & PHD) Fellowship: Tih-Iot Chanakya GroupDocument3 pages(Ug, PG & PHD) Fellowship: Tih-Iot Chanakya GroupVijay M.MPas encore d'évaluation

- World Trends in Municipal Solid Waste ManagementDocument11 pagesWorld Trends in Municipal Solid Waste ManagementNeima EndrisPas encore d'évaluation

- Tecsun Pl310et PDFDocument30 pagesTecsun Pl310et PDFAxel BodemannPas encore d'évaluation

- How To Install 64 Bits IDES On 32 Bits OSDocument1 pageHow To Install 64 Bits IDES On 32 Bits OSMuhammad JaveedPas encore d'évaluation

- IES OBJ Civil Engineering 2000 Paper IDocument17 pagesIES OBJ Civil Engineering 2000 Paper Itom stuartPas encore d'évaluation

- History of Psychotherapy FinalDocument38 pagesHistory of Psychotherapy FinalMarco BonettiPas encore d'évaluation

- The Data Driven AuditDocument34 pagesThe Data Driven AuditMon compte Mon comptePas encore d'évaluation