Académique Documents

Professionnel Documents

Culture Documents

The CMOS Fabrication Process & Design Rules

Transféré par

Bhupender KumawatCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

The CMOS Fabrication Process & Design Rules

Transféré par

Bhupender KumawatDroits d'auteur :

Formats disponibles

Growing the Silicon Ingot

CSE/EE 462: VLSI Design Fall 2004 The CMOS Fabrication Process and Design Rules

Jay Brockman

[Adapted from Mary Jane Irwin and Vijay Narananan, CSE Penn State adaptation of Rabaeys Digital Integrated Circuits, 2002, J. Rabaey et al.]

From Smithsonian, 2000

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.1 Brockman, ND, 2004 CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.2 Brockman, ND, 2004

Silicon Wafer

Single die

ND Multi-Project Reticle: Rocket Chip

Wafer

From http://www.amd.com

CMOS Process

CMOS Process at a Glance

Define active areas Etch and fill trenches

Implant well regions

One full photolithography sequence per layer (mask) Built (roughly) from the bottom up

5 metal 2 4 metal 1 2 polysilicon exception! 3 source and drain diffusions 1 tubs (aka wells, active areas)

Deposit and pattern polysilicon layer

Implant source and drain regions and substrate contacts

Create contact and via windows Deposit and pattern metal layers

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.5

Brockman, ND, 2004

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.6

Brockman, ND, 2004

Photolithographic Process

optical mask

CMOS Inverter

oxidation

stepper exposure photoresist removal (ashing) photoresist coating photoresist development process step

spin, rinse, dry

acid etch

P-Type Substrate and N-Well

Active Area

deposited nitride layer N-well PMOS devices go here P-type substrate NMOS devices go here N-well mask active mask defines p-type and n-type mosfet locations (drain-gate-source)

Brockman, ND, 2004 CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.10 Brockman, ND, 2004

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.9

Field Oxide Growth

o2 o2 o2 o2 o2 o2 o2 o2 o2 o2

Polysilicon Gate

Thick field oxide electrically isolates transistors Nitride prevents field oxide growth Thin gate oxide grown after nitride removed

gate oxide field oxide

SiO2 formation consumes Si Si-SiO2 interface below original Si surface

poly mask added to layout

P-Select Mask and N-Type Source/Drain Implant

N-Select Mask and P-Type Source/Drain Implant

n-type implant

p-select covers p-type source/drain regions select mask must overlap active areas n-type ion implant creates n-type source/drain regions high temperature anneal repairs silicon lattice and causes diffusion of implanted ions

p-type implant

finished mosfets

both select masks added

Brockman, ND, 2004

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.13

Brockman, ND, 2004

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.14

Contact Cuts

Metal 1

non-planar surface

Via 1 and Metal 2

Advanced Metallization

Multilevel interconnect fabrication processes planarize between layers (expensive) MOSIS SCMOS does not allow stacked vias

Brockman, ND, 2004 CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.18 Brockman, ND, 2004

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.17

Advanced Metallization

A Modern CMOS Process

Dual-Well Trench-Isolated CMOS

gate oxide field oxide Al (Cu) SiO2 tungsten

TiSi2

p well p-epi n+ p-

n well p+

SiO2

Design Rules

Why Have Design Rules?

Interface between the circuit designer and process engineer Guidelines for constructing process masks Unit dimension: minimum line width

z z

To be able to tolerate some level of fabrication errors such as

1. Mask misalignment

scalable design rules: lambda parameter absolute dimensions: micron rules

2. Dust

Rules constructed to ensure that design works even when small fab errors (within some tolerance) occur A complete set includes

z z z

3. Process parameters (e.g., lateral diffusion)

set of layers intra-layer: relations between objects in the same layer inter-layer: relations between objects on different layers

Brockman, ND, 2004

4. Rough surfaces

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.22 Brockman, ND, 2004

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.21

Intra-Layer Design Rule Origins

Intra-Layer Design Rules

Same Potential Well 10 Active

0.3 micron

Minimum dimensions (e.g., widths) of objects on each layer to maintain that object after fab

z

minimum line width is set by the resolution of the patterning process (photolithography)

Different Potential 9 Polysilicon 2 2

Minimum spaces between objects (that are not related) on the same layer to ensure they will not short after fab

0 or 6 3

Metal1 Contact or Via Hole 2 2

Metal2 3

3 2 Select

3

4

0.15 0.15

0.3 micron

Inter-Layer Design Rule Origins

1.

Transistor Layout

Transistor rules transistor formed by overlap of active and poly layers

Transistor

Transistors

Catastrophic error

Unrelated Poly & Diffusion

Thinner diffusion, but still working

5

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.25

Brockman, ND, 2004

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.26

Brockman, ND, 2004

Select Layer

2 3 1 3 3 2 Select

Inter-Layer Design Rule Origins, Continued

2.

Contact and via rules

M1 contact to p-diffusion M1 contact to n-diffusion M1 contact to poly Mx contact to My

Contact Mask Via Masks mask misaligned

both materials

2 5

0.3

Contact: 0.44 x 0.44

0.14

Substrate

Well

Vias and Contacts

2 Via 1 1 5 Metal to 1 Active Contact Metal to Poly Contact 3 2 4

2 2

CSE/EE 462 L05 CMOS Fabrication Process and Design Rules.29

Brockman, ND, 2004

Vous aimerez peut-être aussi

- Lab Report VLSIDocument24 pagesLab Report VLSIK Eerti Vyas0% (2)

- VLSI Micro-Project Report Group A PDFDocument14 pagesVLSI Micro-Project Report Group A PDFganesh SawantPas encore d'évaluation

- Cmos Process FlowDocument29 pagesCmos Process FlowPushparaj Karu100% (1)

- Unit 2Document33 pagesUnit 2Venky VellankiPas encore d'évaluation

- Fabrication of MOSFETDocument48 pagesFabrication of MOSFETYogesh TiwariPas encore d'évaluation

- Nmos and Cmos FabricationDocument33 pagesNmos and Cmos FabricationmannslovePas encore d'évaluation

- MOS and Bi-CMOS Circuit Design ProcessesDocument54 pagesMOS and Bi-CMOS Circuit Design ProcessesVenkateswara ReddyPas encore d'évaluation

- Fabrication of Mosfet: Dr. Arti Noor, M. Tech Division, CDAC Noida. Email: Artinoor@cdacnoida - inDocument43 pagesFabrication of Mosfet: Dr. Arti Noor, M. Tech Division, CDAC Noida. Email: Artinoor@cdacnoida - inDebasis MukherjeePas encore d'évaluation

- Special Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesDocument11 pagesSpecial Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesMoaaz AhmedPas encore d'évaluation

- Vlsi 1 Chapter 111111111Document15 pagesVlsi 1 Chapter 111111111Dinesh PalavalasaPas encore d'évaluation

- FEOL Wafer Processing GuideDocument17 pagesFEOL Wafer Processing GuidekarthikPas encore d'évaluation

- MOS Fabrication ProcessDocument22 pagesMOS Fabrication ProcessRishabh RaiPas encore d'évaluation

- CMOS Fabrication and Layout RulesDocument65 pagesCMOS Fabrication and Layout Rulessasindhur r100% (2)

- CMOS Fabrication Technologies and Process Design RulesDocument14 pagesCMOS Fabrication Technologies and Process Design RulesPrashant SinghPas encore d'évaluation

- VLSI Unit 2 Technology - SDocument52 pagesVLSI Unit 2 Technology - SIndrajeet GautamPas encore d'évaluation

- CH 02 FabricationDocument55 pagesCH 02 FabricationUPADHYAY SHIVANSHPas encore d'évaluation

- Cmos Digital Integrated Circuits: Fabrication of MosfetsDocument48 pagesCmos Digital Integrated Circuits: Fabrication of Mosfetsapi-127299018Pas encore d'évaluation

- Design RulesDocument14 pagesDesign RulesmayankfirstPas encore d'évaluation

- Complementary MetalDocument5 pagesComplementary MetalesaidanPas encore d'évaluation

- Fabrication of MosfetDocument19 pagesFabrication of Mosfetnarayana89% (9)

- Nano ElectronicsDocument41 pagesNano Electronicschatterjee_somenath2204Pas encore d'évaluation

- Chapter 1: Cmos Circuits - A Brief IntroductionDocument3 pagesChapter 1: Cmos Circuits - A Brief IntroductionbhannuPas encore d'évaluation

- NMOS Fabrication: Step 1: Processing The SubstrateDocument5 pagesNMOS Fabrication: Step 1: Processing The Substratechinthala santhosh srkPas encore d'évaluation

- Fabrication, Layout, and SimulationDocument26 pagesFabrication, Layout, and Simulationshiny johnPas encore d'évaluation

- DEC50143 CHAPTER 2 - PART C - EditDocument49 pagesDEC50143 CHAPTER 2 - PART C - Edity mePas encore d'évaluation

- Chapter 3. CMOS Processing Technology - VLSI - CAD LaboratoryDocument45 pagesChapter 3. CMOS Processing Technology - VLSI - CAD LaboratoryYidnekachwe MekuriaPas encore d'évaluation

- Layout Design8Document34 pagesLayout Design8Sandeep BoyinaPas encore d'évaluation

- MODULE 2 - MOS AND BiCMOS CIRCUIT DESIGN PROCESSDocument33 pagesMODULE 2 - MOS AND BiCMOS CIRCUIT DESIGN PROCESSrahulmohan3777Pas encore d'évaluation

- Fabrication of CMOSDocument11 pagesFabrication of CMOSprasanna810243Pas encore d'évaluation

- The Introduction of The Ceramic PCB Manufacturing ProcessDocument8 pagesThe Introduction of The Ceramic PCB Manufacturing ProcessjackPas encore d'évaluation

- Design Rules: A. Gunasundari Asst - Professor Eee Dept, PSGCTDocument35 pagesDesign Rules: A. Gunasundari Asst - Professor Eee Dept, PSGCTS.DharanipathyPas encore d'évaluation

- CMOS Fabrication Process StepsDocument17 pagesCMOS Fabrication Process StepsNoman Ali35Pas encore d'évaluation

- T3 Metodologia PDFDocument60 pagesT3 Metodologia PDFMARCOS MARTÍNEZ MARTÍNEZPas encore d'évaluation

- VLSI Design Process RulesDocument29 pagesVLSI Design Process RulesSai KallemPas encore d'évaluation

- Set 3, LayoutDesignConceptsDocument46 pagesSet 3, LayoutDesignConceptsapi-3804613Pas encore d'évaluation

- VLSI DesignDocument181 pagesVLSI Designprabhug22Pas encore d'évaluation

- Design RulesDocument14 pagesDesign RulessivapothiPas encore d'évaluation

- Introduction To MOS TechnologiesDocument15 pagesIntroduction To MOS TechnologieslokeshwarrvrjcPas encore d'évaluation

- Microelectronic Engineering: Alexander Vladimirov GrigorovDocument9 pagesMicroelectronic Engineering: Alexander Vladimirov Grigorov135713571357Pas encore d'évaluation

- PolyMUMPs ProcessDocument28 pagesPolyMUMPs ProcessMajid GhaffarPas encore d'évaluation

- Micro WindDocument14 pagesMicro Windlak_prabPas encore d'évaluation

- Processing of DevicesDocument31 pagesProcessing of DevicesBituPas encore d'évaluation

- Making TransistorsDocument23 pagesMaking TransistorsRANGAM NAGARAJUPas encore d'évaluation

- A Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerDocument10 pagesA Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerRohit JangidPas encore d'évaluation

- Ic FabricationDocument7 pagesIc FabricationphooolPas encore d'évaluation

- C-1 CMOS Processing FlowDocument76 pagesC-1 CMOS Processing FlowKu Ble YanPas encore d'évaluation

- Layout Design, Fabrication and Characterization of N-Channel MOSFETDocument7 pagesLayout Design, Fabrication and Characterization of N-Channel MOSFETashiqur rahman rahulPas encore d'évaluation

- Chapter 6 Thermal Oxidation - I Bo CuiDocument23 pagesChapter 6 Thermal Oxidation - I Bo CuisbotacondPas encore d'évaluation

- Links between fabrication, circuit design and chip performanceDocument11 pagesLinks between fabrication, circuit design and chip performanceNagaPas encore d'évaluation

- A Teacher-Student Conversation On "Cmos Fabrication Process Flow"Document70 pagesA Teacher-Student Conversation On "Cmos Fabrication Process Flow"Calcutta University RPE 2020Pas encore d'évaluation

- 3.2.2 Surface Micromachining: Dry/wet Isotropic EtchingDocument7 pages3.2.2 Surface Micromachining: Dry/wet Isotropic EtchingRana Muhammad UmerPas encore d'évaluation

- Analog Digital VLSI Design TechniquesDocument78 pagesAnalog Digital VLSI Design TechniqueshkajaiPas encore d'évaluation

- Faculty of Engineering Lab Sheet Processing and Fabrication Technology EEN3106Document15 pagesFaculty of Engineering Lab Sheet Processing and Fabrication Technology EEN3106KarimovaRaikhanovnaPas encore d'évaluation

- Cmos Technology GroupDocument56 pagesCmos Technology GroupAiman NabihahPas encore d'évaluation

- 17EC63Document23 pages17EC63LittiPas encore d'évaluation

- NMOS FabricationDocument18 pagesNMOS FabricationDhaval Doshi100% (1)

- Plasma Etching Processes for CMOS Devices RealizationD'EverandPlasma Etching Processes for CMOS Devices RealizationNicolas PossemePas encore d'évaluation

- Industry Standard FDSOI Compact Model BSIM-IMG for IC DesignD'EverandIndustry Standard FDSOI Compact Model BSIM-IMG for IC DesignPas encore d'évaluation

- An Essential Guide to Electronic Material Surfaces and InterfacesD'EverandAn Essential Guide to Electronic Material Surfaces and InterfacesPas encore d'évaluation

- MOS Integrated Circuit DesignD'EverandMOS Integrated Circuit DesignE. WolfendalePas encore d'évaluation

- 1 Amdocs Seating PlanDocument23 pages1 Amdocs Seating PlanBhupender KumawatPas encore d'évaluation

- And Power in Full Subtractor Circuit: Transistor Gating: Reduction of Leakage CurrentDocument11 pagesAnd Power in Full Subtractor Circuit: Transistor Gating: Reduction of Leakage CurrentBhupender KumawatPas encore d'évaluation

- 5705 - 1 - HCL Extempore Based 2nd Session - 25th SepDocument18 pages5705 - 1 - HCL Extempore Based 2nd Session - 25th SepBhupender KumawatPas encore d'évaluation

- Low Power High Speed Multipliers: Submitted byDocument22 pagesLow Power High Speed Multipliers: Submitted byBhupender KumawatPas encore d'évaluation

- Ratan Tata Getting AwardDocument1 pageRatan Tata Getting AwardBhupender KumawatPas encore d'évaluation

- Gilbert Cell DesignDocument21 pagesGilbert Cell DesignBhupender KumawatPas encore d'évaluation

- Gate Leakage ReductionDocument5 pagesGate Leakage ReductionSandeep SriramPas encore d'évaluation

- Rtlinux: (Ece-496) Section-E2E04Document3 pagesRtlinux: (Ece-496) Section-E2E04Bhupender KumawatPas encore d'évaluation

- Beauty With BrainDocument1 pageBeauty With BrainBhupender KumawatPas encore d'évaluation

- List of Recipients Bharat RatnaDocument7 pagesList of Recipients Bharat RatnaBhupender KumawatPas encore d'évaluation

- 2G - Wikipedia, The Free EncyclopediaDocument4 pages2G - Wikipedia, The Free EncyclopediaBhupender KumawatPas encore d'évaluation

- 04 AcknowledgementsDocument2 pages04 AcknowledgementsBhupender KumawatPas encore d'évaluation

- Visitor CounterDocument2 pagesVisitor CounterBhupender KumawatPas encore d'évaluation

- 1 LandraDocument1 page1 LandraBhupender KumawatPas encore d'évaluation

- Mobile Phone Detector: Indian Institute of Technology HyderabadDocument7 pagesMobile Phone Detector: Indian Institute of Technology HyderabadBhupender KumawatPas encore d'évaluation

- QuestionsDocument2 pagesQuestionsBhupender KumawatPas encore d'évaluation

- Cadence Design Tools TutorialDocument124 pagesCadence Design Tools TutorialBhupender KumawatPas encore d'évaluation

- EnggDocument5 pagesEnggBhupender KumawatPas encore d'évaluation

- 1Document1 page1Bhupender KumawatPas encore d'évaluation

- How Can I Create A 8 - 1 Multiplexer Using 2 - 1 MultiplexerDocument1 pageHow Can I Create A 8 - 1 Multiplexer Using 2 - 1 MultiplexerBhupender KumawatPas encore d'évaluation

- EpitaxyDocument1 pageEpitaxyBhupender KumawatPas encore d'évaluation

- 1 - Detail of Centers For StudentsDocument2 pages1 - Detail of Centers For StudentsBhupender KumawatPas encore d'évaluation

- HTML TablesDocument2 pagesHTML TablesBhupender KumawatPas encore d'évaluation

- Ec 1451Document17 pagesEc 1451saravisaPas encore d'évaluation

- MultiplexersDocument16 pagesMultiplexersmiloš_lakićevićPas encore d'évaluation

- HTML LinksDocument2 pagesHTML LinksBhupender KumawatPas encore d'évaluation

- Presentation 1Document19 pagesPresentation 1Bhupender KumawatPas encore d'évaluation

- HTML Quick ListDocument2 pagesHTML Quick ListBhupender KumawatPas encore d'évaluation

- HTML Basic - : 4 ExamplesDocument2 pagesHTML Basic - : 4 ExamplesBhupender KumawatPas encore d'évaluation

- Si8751/52 Data Sheet: Isolated FET Driver With Pin Control or Diode Emulator InputsDocument27 pagesSi8751/52 Data Sheet: Isolated FET Driver With Pin Control or Diode Emulator InputsAnti-cosmoPas encore d'évaluation

- VLSI Design Lecture Notes for B.Tech IV Year ISEM StudentsDocument115 pagesVLSI Design Lecture Notes for B.Tech IV Year ISEM Studentsyuvaraaj aletiPas encore d'évaluation

- Basic Concepts of ElectricityDocument81 pagesBasic Concepts of ElectricityNasarMahmoodPas encore d'évaluation

- Código BF 256B DatasheetDocument4 pagesCódigo BF 256B DatasheetEddy SamaniegoPas encore d'évaluation

- Digital Logic Families GuideDocument82 pagesDigital Logic Families Guidemoney_kandan2004Pas encore d'évaluation

- BE (2nd) May19Document1 pageBE (2nd) May19jagdish singhPas encore d'évaluation

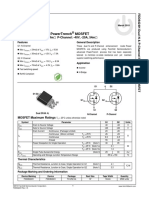

- FDD8424H-92711 - Transistor de Efeito de CampoDocument12 pagesFDD8424H-92711 - Transistor de Efeito de CampoTiago LeonhardtPas encore d'évaluation

- Electronics Mechanic (Semester Pattern) : Syllabus For The Trade ofDocument41 pagesElectronics Mechanic (Semester Pattern) : Syllabus For The Trade ofMohamed SalamPas encore d'évaluation

- SEMIKRON Application-Note An-1403 Switchinglosses enDocument15 pagesSEMIKRON Application-Note An-1403 Switchinglosses enmarcor08Pas encore d'évaluation

- STP 16 NF 06 FPDocument14 pagesSTP 16 NF 06 FPjoverjover1Pas encore d'évaluation

- Buz 80 FiDocument10 pagesBuz 80 Figabriel taberneroPas encore d'évaluation

- Boardworks Cambridge IGCSE Mapping Grid PhysDocument15 pagesBoardworks Cambridge IGCSE Mapping Grid PhysengrroyPas encore d'évaluation

- L31-Microwave TransistorsDocument14 pagesL31-Microwave TransistorsMohamed shabanaPas encore d'évaluation

- Ece532 Pres Ekv BsimDocument29 pagesEce532 Pres Ekv BsimKenneth Palma CarmonaPas encore d'évaluation

- V-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower FrequenciesDocument4 pagesV-Band GaAs Metamorphic Low-Noise Amplifier Design Technique For Sharp Gain Roll-Off at Lower Frequencieskarthik srivatsa mbPas encore d'évaluation

- BGR ProjectDocument37 pagesBGR ProjectAnonymous TPVfFif6TOPas encore d'évaluation

- 464-Fab Slides Ch09Document26 pages464-Fab Slides Ch09mnahas84Pas encore d'évaluation

- 1.5A USB-Friendly Li-Ion Battery Charger and Power-Path Management ICDocument33 pages1.5A USB-Friendly Li-Ion Battery Charger and Power-Path Management ICanarchie2008Pas encore d'évaluation

- Analogue Short Report Lab 4Document8 pagesAnalogue Short Report Lab 4Arfan AzmanPas encore d'évaluation

- BQ 24721 CDocument60 pagesBQ 24721 CdanielarteagaPas encore d'évaluation

- EI2203 - Electronic Devices and Circuits - 2 Marks With AnswersDocument16 pagesEI2203 - Electronic Devices and Circuits - 2 Marks With AnswersASPCN 2017Pas encore d'évaluation

- 3 N 187Document1 page3 N 187Axel Ricardo RojasPas encore d'évaluation

- Ebook Reparacion de Laptop Por Adie DkhazDocument175 pagesEbook Reparacion de Laptop Por Adie Dkhazjose Luis nuñez veintimilla100% (1)

- Introduction To Compact ModelingDocument66 pagesIntroduction To Compact Modelingmanurudin2Pas encore d'évaluation

- Ga As Rel HandbookDocument221 pagesGa As Rel Handbookafn07120Pas encore d'évaluation

- MTP3055VLDocument3 pagesMTP3055VLsybiantechnologies2009Pas encore d'évaluation

- FS8205 DS 19 - enDocument6 pagesFS8205 DS 19 - enJaime Andres Aranguren CardonaPas encore d'évaluation

- 1986 Siliconix FET Databook PDFDocument374 pages1986 Siliconix FET Databook PDFbayman0% (1)

- Mosfet (Iii) - I-V CharacteristicsDocument11 pagesMosfet (Iii) - I-V Characteristics許博凱Pas encore d'évaluation