Académique Documents

Professionnel Documents

Culture Documents

Control de Brushless PWM

Transféré par

Pablo NarvaezDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Control de Brushless PWM

Transféré par

Pablo NarvaezDroits d'auteur :

Formats disponibles

designfeature By Michael Copeland, Infineon

ON-CHIP TIMERS AND REGISTERS ENABLE 8-BIT CS TO GENERATE SYMMETRIC SPACE-VECTOR PWM SIGNALS FOR THREE-PHASE MOTORS.

Generate advanced PWM signals using 8-bit Cs

he use of variable-speed drives (VSDs) has increased remarkably in recent years. This trend will probably continue and even accelerate as VSDs continue to penetrate the industrial, automotive, and consumer markets. Paramount to the success of VSDs is the ability to increase system performance and decrease price. Space-vector modulation, or SVM, is one way to increase the performance of many types of VSDs. Implementing the complicated equations for SVM with a low-cost, 8bit C, instead of a DSP, also decreases the system cost. In fact, an optimized SVM algorithm can often allow a low-cost, 8-bit C to perform all of the control requirements for the system (Reference 1).

WHAT IS SVM?

SVM is one of many methods that you can use to create sinusoidal voltages from a three-phase inverter. Figure 1 THREE-PHASE INVERTER shows a typical inverterPOSITIVE RAIL F i g u r e 1 fed VSD system. The load is typically an induction, relucLOAD (MOTOR) tance, or sinusoidal brushless dc motor. The control unit in Figure A B C 1 applies the appropriate PWM RECTIFIER signal to the six transistors that NEUTRAL make up the inverter. CONTROL UNIT You can contrast the operation A B C of SVM with sinusoidally weighted PWM (SWPWM), which is a popular method for creating sinusoidal voltages. SWPWM applies sinusoidally weighted PWM signals, at a constant frequency, to NEGATIVE RAIL each transistor. The PWM signals for each high-side transistor should be 120 out of phase. Each In a typical inverter-fed variable-speed-drive (VSD) system, the load is an induction, reluctance, or sinuPWM signal for each low-side soidal brushless dc motor. The control unit applies the appropriate PWM to the six transistors that make up transistor should be the comple- the inverter.

www.ednmag.com February 3, 2000 | edn 63

ment of the signal for the corresponding high-side transistor, and these PWM signals must include some dead time to prevent shoot-through current. A C usually implements SWPWM using a sine table that you store in ROM. You can scale the values in the sine table to generate sinusoids of variable magnitude. The C controls the frequency by reading the same sine-table value more than once, which produces a low frequency, or by skipping sine-table values, which produces a high frequency. Figure 2a shows ideal maximum-magnitude output voltages, after filtering, of SWPWM. These plots show the measured phase voltage in percent with respect to the negative rail of the inverter. As the figure shows, the amplitude of the line-to-line voltages is only about 86% of the inverter rail voltage. Intuitively, you would expect the line-to-line voltage VAB

designfeature Generating advanced PWM signals

to reach both the positive and negative for easy calculations because no negative inverter switches are in a constant state. rail voltages. For example, if transistors numbers are involved. In addition to The (x, x, x) type of notation indicates A+ and B of Figure 1 are conducting, these advantages, SVM also lends itself the state of the inverter. For example, the then VAB should be equal to the inverter easily to overmodulation. Overmodula- inverter state (+, , +) indicates that rail voltage. This lower line-to-line volt- tion is a method of generating even larg- transistors A+, B, and C+ are conage is one of the major disadvantages to er voltages. However, as you can intu- ducting. SWPWM. Using the alternative SVM, itively guess, the line-to-neutral voltages One way to describe SVM is to say that however, you can apply a larger voltage produced by overmodulation are no it uses a sophisticated averaging techto the motor. longer sinusoidal. nique to smooth out the steps in sixFor motor control, the line-to-neutral step mode. For example, assume that a voltage VAN and the induced phase volt- SVM SMOOTHS OUT THE STEPS required voltage is between two steps. Asage determine the current in each phase. To describe the C algorithm for SVM sume that this required voltage is beThe phase currents determine the motor and overmodulation, first look at how tween the voltages that result from actitorque. Thus, its important that the line- SVM works by examining the popular vating the inverter state (+, , )and to-neutral voltages are sinusoidal, and as six-step method for generating sinu- (+, +, ). SVM will approximate the relong as they are, it doesnt matter what soidal line-to-neutral voltages. Figure 3 quired voltage inside of one PWM perithe phase voltages look like. With SVM, shows the voltages that the inverter gen- od (T0) by first applying the state (+,, the generated phase voltage is not sinu- erates with a resistive balanced load us- )for a time tAT0, and then the state (+, soidal, but the line-to-neutral and line- ing six-step mode. During each step, the +, )for a time tBT0. If there is any time left over in that PWM to-line voltages are sinuperiod, then SVM apsoidal (Figure 2b). FurPHASE VOLTAGE (X), LINE-TO-LINE VOLTAGE (*) plies zero voltage for the thermore, the magnitude LINE-TO-NEUTRAL VOLTAGE (+) leftover time t0 by using of the line-to-line Figure 2 the inverter state (+, +, voltage reaches +) or (, , ). This the full inverter rail volttype of SVM implemenage, which indicates that tation deals with the time SVM takes full advantage each inverter state is acof the inverters capability PERCENT OF tive. Taking advantage of to generate sinusoidal RAIL VOLTAGE the powerful PWM genvoltages. erators of a C requires To implement SVM, converting these state you can use the SWPWM times to output times algorithm and replace the or duty cycles for each ROM sine table by the output pin. Figure 4 phase-voltage waveform shows the switching sein Figure 2b. In fact, an inDEGREES (a) quence for symmetric finite number of phase PWM and how the sevoltages can produce the PHASE VOLTAGE (X), LINE-TO-LINE VOLTAGE (*) quence relates to the same line-to-neutral voltLINE-TO-NEUTRAL VOLTAGE (+) times T0, tA, tB, and t0. age as Figure 2b shows. So This type of symmetric why use SVM instead of PWM is advantageous some other homegrown because it has very few PWM method? The answitching events and swer is that SVM fits niceproduces low torque ly with vector-control PERCENT OF ripple. schemes. Another reason RAIL VOLTAGE The implementation why SVM is popular is bein Figure 4 is based on cause the derivation of the using the CAPCOM6 phase-voltage equations module in the C504, can lead to a simple imC508, and C164I Cs plementation. A good (www.infineon.com). SVM algorithm can calcu(b) The compare timer withlate the phase voltage onDEGREES in the CAPCOM6 modline and requires only a ule generates symmetric single small look-up table With sinusoidally weighted PWM (SWPWM), the line-to-line voltage reaches only PWM by toggling output that contains only 60 86% of the rail voltage (a). With SVM, however, the line-to-line voltage reaches pins when the compare worth of information. The 100% of the rail voltage (b), which means that SVM can apply a larger voltage to timer reaches a compare SVM formulas also allow the motor.

64 edn | February 3, 2000

www.ednmag.com

designfeature Generating advanced PWM signals

value. From Figure 4, you can see the following relationships between the compare values and the times tA, tB and t0: CC0(t0/2)T0 ; CC1((t0/2tA))T0; and CC2(1t0/2)T0. Calculating the values of tA and tB requires making use of a graphical representation of the six-step-mode voltages. Converting the line-to-neutral voltages of six-step mode to space vectors and plotting the vectors on the complex plane creates the vectors in Figure 5. The following equation can transform any three quantitiesin this case, the line-to-neutral voltagesthat sum to zero into space vectors: uSVAN(t)ej0VBN(t)ej2/3VCN(t)ej2/3 . As Figure 5 shows, there are six distinct space vectors, one for each inverter state, when using the six-step mode. The input to the SVM algorithm is a space-vector voltage uS that has a magnitude, U, and angle, . If you transform truly sinusoidal three-phase voltages into a space vector, the value of U remains constant for all time but increases at a constant rate. If you assume that increases slowly, the SVM algorithm can treat both U and as constants during each switching period. For any vector that does not lie exactly on one of the six base vectors that is, any voltage that is between two stepsthe algorithm must generate an approximation by applying the two adjacent base vectors for the appropriate

Figure 3

VAN 67% 33% 33% 67% VBN 67% 33% 33% 67% VCN 67% 33% 33% 67% (+, , ) (+, +, ) (, +, ) (, +, +) (, , +) (+, , +)

amount of time. The projections of uS. onto the two adjacent base vectors give the values of tA and tB. The following formulas determine tA and tB when uS is in sector 0: tB2U(31/2)sin(); tAU[cos()(31/2)sin()]; and t0T0tAtB. The equations for SVM show that when uS lies outside of the hexagon, t0 becomes negative, which is not physically possible. To generate sinusoidal voltages, the tip of uS must lie within the hexagon at all times. This means that the length U of uS must be no greater than the radius of the inner circle of Figure 5. Voltages between the inner circle and the hexagon are reachable but will not create a sinusoid because the vector will not be able to rotate 360 without crossing the hexagon boundary. The formulas for tA and tB are only valid when uS is in sector 0. If uS is outside of sector 0, then the results of the formula are still useful, but the algorithm should rotate the vector back in 60 increments until the vector is in sector 0. The C can then apply the times tA and tB to the appropriate switching states. IMPLEMENT SVM USING LOOK-UP TABLES The calculation of compare values requires the calculation of tA, tB, and t0. These variables require calculation of sine and cosine values and several multiplies, which all must be done on-line. Proper scaling of the variables so that they fit in an 8-bit C architecture can

make the task much simpler. For example, if you program the compare timer to count from 0 to 0xFF, then the C can store all of the compare values as 8-bit values. Because the CAPCOM6 module has multiple prescalers for the timer, this 8-bit value will not really limit the choices for the actual PWM frequency. If sector zero comprises 256 angles, the precision of will be approximately 0.235. This degree of precision is more than enough for nearly all VSD applications. Partitioning each sector into 256 angles means that must be 11 bits long. This length is convenient because the most significant 3 bits indicate the sector and the least significant 8 bits indicate the angle within the sector. The C can store these values in two bytes. The least significant byte will always work in the tA and tB equations because this byte will always be less than or equal to 60. A look-up table of 256 bytes can store the tB values for each , for the case when U1. The C can then scale each tB value by the real value of U, which is always less than or equal to 1 by performing just one multiply. By examining the formula for tB, you can see that the look-up table will contain sine values for angles between 0 and 60. Because these values are always greater than 0, the C doesnt need to represent any negative numbers. The C can perform this same procedure for tA. However, if you examine the table for tA, you will find that the table is exactly the same as the tB table, but in reverse. This result stems from the chosen scaling. The C can store the values for tA and tB in the same look-up table. Because the table is 256 bytes long, the same pointerthe variablecan retrieve both tA and tB. The C simply needs to complement the pointer. Thus, the C can determine tA and tB to a great degree of accuracy using only two table look-ups and two multiplies. FURTHER OPTIMIZATIONS You can make several other optimizations to the SVM algorithm. An 8051-type C can complete the entire SVM algorithm in as few as 55 instruction cycles, including

www.ednmag.com

During each step of the popular six-step method for generating sinusoidal line-to-neutral voltages, the inverter switches are in a constant state. In essence, SVM uses an averaging technique to smooth out the steps.

66 edn | February 3, 2000

designfeature Generating advanced PWM signals

Figure 4

CCO CC1 CC2

T0

COMPARE TIMER COMPARE VALUES

1 2 t0T0

tAT0 u1 (+, , )

tBT0 u2 (+, +, )

1 2 t0T0

1 2 t0T0

tBT0 u2 (+, +, )

tAT0 u1 (+, , )

1 2 t0T0

u0 (, , )

u7 (+, +, +)

u7 (+, +, +)

u0 (, , )

A A

B B

C C

To generate symmetric SVM signals, a compare timer within the CAPCOM6 module toggles output pins when the compare timer reaches a compare value, CCx (x0, 1, or 2), which is related to times tA, tB, t0, and T0.

SECTOR push and pop instructions. If the C 1 has a 300-nsec minimum inF i g u r e 5 struction cycle time, all of the (+, +, ) (, +, ) SVM calculations take just 16.5 sec. u2 u3 This short time leaves ample time, even when switching at 20 kHz, to perform open-loop or simple closed-loop conSECTOR SECTOR trol, such as slip frequency compensa2 0 tion. The cost of this type of C is easuS ily less than $5 and, in high volume, can tB be less than $2. For a high-end vector-control system, (+, , ) (, +, +) a two-chip solution is possible by using u1 u t 4 A a simple low-cost 32- or 16-bit processor, such as a C161, to perform the vector-control calculations. You can use the 8-bit C as a PWM unit, and this C can also perform all of the current and voltSECTOR SECTOR age measurements with the onboard 3 5 A/D converter. The cost of such a twochip solution can be much less than $10. You can also use a 16-bit C, the (, , +) (+, , +) C164CI, which contains the CAPCOM6 u5 u6 module. This single C can perform SECTOR 4 all of the vector-control and SVM calcuConverting the line-to-neutral voltages of six-step mode to space vectors and plotting the vectors lations. For an extra 20 instruction cycles, you on the complex plane creates six distinct space vectors, one for each inverter state.

68 edn | February 3, 2000

www.ednmag.com

designfeature Generating advanced PWM signals

Figure 6

(a)

(b)

SVM generates a sinusoidal line-to-neutral voltage and a nonsinusoidal phase voltage (a). When controlling a three-phase induction motor, SVM generates the phase currents in (b).

can add an overmodulation mode that allows the drive system to apply even higher nonsinusoidal voltages to the motor. This type of drive is often useful in automotive applications. Figure 6a shows the phase and line-toneutral voltage that SVM generates. Figure 6b shows the phase current when you

use the SVM algorithm to control a three-phase induction motor. Reference 1. A complete application note on SVM and overmodulation, including example code, is available at www. infineon.com/microcontrollers.

Authors biography Michael Copeland is senior applications specialist for Infineon Technologies Corp (San Jose, CA). He holds an MS and a BS from Michigan State University.

Circle 4 or visit www.ednmag.com/infoaccess.asp

70 edn | February 3, 2000

www.ednmag.com

Vous aimerez peut-être aussi

- Nuts&Volts 2009 02Document100 pagesNuts&Volts 2009 02Pablo NarvaezPas encore d'évaluation

- Nuts&Volts 2009 05Document100 pagesNuts&Volts 2009 05Pablo NarvaezPas encore d'évaluation

- Tda2822d 150Document7 pagesTda2822d 150Pablo NarvaezPas encore d'évaluation

- Nuts&Volts 2009 10Document84 pagesNuts&Volts 2009 10Pablo NarvaezPas encore d'évaluation

- Nuts&Volts 2009 04Document84 pagesNuts&Volts 2009 04Pablo NarvaezPas encore d'évaluation

- Nuts&Volts 2009 04Document84 pagesNuts&Volts 2009 04Pablo NarvaezPas encore d'évaluation

- Nuts&Volts 2009 11Document84 pagesNuts&Volts 2009 11Pablo NarvaezPas encore d'évaluation

- Nuts&Volts 2009 03Document100 pagesNuts&Volts 2009 03Pablo Narvaez100% (1)

- Pequenos - Transformadores - Francisco L.Singer PDFDocument127 pagesPequenos - Transformadores - Francisco L.Singer PDFPablo Narvaez83% (6)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- 20 - How To Calculate Wire & Fuse Sizes For Electric MotorsDocument2 pages20 - How To Calculate Wire & Fuse Sizes For Electric MotorsLPas encore d'évaluation

- Apxvll13n CDocument2 pagesApxvll13n CqaisersiddiPas encore d'évaluation

- Generador Electrico Aska - Apd75c-6Document4 pagesGenerador Electrico Aska - Apd75c-6Nj Nelson JavierPas encore d'évaluation

- T F /,, - The Skid-Mounted Blower AssemblyDocument2 pagesT F /,, - The Skid-Mounted Blower Assemblyprihartono_diasPas encore d'évaluation

- Altera Weave Effect An528Document20 pagesAltera Weave Effect An528Tony LuanPas encore d'évaluation

- PushbuttonDocument5 pagesPushbuttonapi-242591736Pas encore d'évaluation

- Manual Mircom FA-1000 Manual PDFDocument72 pagesManual Mircom FA-1000 Manual PDFwerusso30Pas encore d'évaluation

- Metex M3600 B Series Operating ManualDocument13 pagesMetex M3600 B Series Operating ManualBeshim RahmedowPas encore d'évaluation

- Service Manual Dr-Id-300 - 23Document1 pageService Manual Dr-Id-300 - 23bilal aloulouPas encore d'évaluation

- Single - Stage BJT Amplifier: Experiment No. 1Document12 pagesSingle - Stage BJT Amplifier: Experiment No. 1Yousef BobadillaPas encore d'évaluation

- MTDocument14 pagesMTHernanJHSPas encore d'évaluation

- Zelio Electromechanical: RelaysDocument45 pagesZelio Electromechanical: RelaysDaniel ReyPas encore d'évaluation

- 8发电机启动停机检查Document19 pages8发电机启动停机检查Ruben MaychelPas encore d'évaluation

- Bok:978 3 319 17659 8Document365 pagesBok:978 3 319 17659 8Miguel Ángel González GaliciaPas encore d'évaluation

- Photo Electric SensorDocument176 pagesPhoto Electric SensorAlfiansyah Dharma Setia Djaketra100% (1)

- EP FA EL 02 ST - Standard - For - Voltage - LevelDocument15 pagesEP FA EL 02 ST - Standard - For - Voltage - Levelmarin cristianPas encore d'évaluation

- BJT PresentationDocument128 pagesBJT PresentationMarcus FPas encore d'évaluation

- Exp 12) Prbs Generator and Shift RegisterDocument5 pagesExp 12) Prbs Generator and Shift RegisterMani BharathiPas encore d'évaluation

- Compufire20100 Hd-1m Dual FireDocument4 pagesCompufire20100 Hd-1m Dual Fire12dan11Pas encore d'évaluation

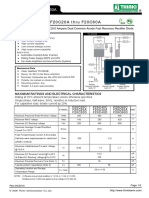

- F20C20C RectificadorDocument2 pagesF20C20C Rectificadoralexjcc10Pas encore d'évaluation

- PalaDocument822 pagesPalaemilio cortes100% (1)

- Grid Scale Battery StorageDocument8 pagesGrid Scale Battery StoragetyaskartikaPas encore d'évaluation

- Electrical Machines Lab ManualDocument41 pagesElectrical Machines Lab Manualsohaib hashmatPas encore d'évaluation

- Power System AnalysisDocument4 pagesPower System Analysisahmedfhd1Pas encore d'évaluation

- Aha Welding PDFDocument4 pagesAha Welding PDFcrnkarlos100% (1)

- Mto-12!13!8016 BMT App MaintenanceDocument2 pagesMto-12!13!8016 BMT App MaintenanceStephen BridgesPas encore d'évaluation

- TVSS Data SheetDocument8 pagesTVSS Data SheetJason MendozaPas encore d'évaluation

- Kollmorgen KBM Series 2011 CatalogDocument80 pagesKollmorgen KBM Series 2011 CatalogElectromatePas encore d'évaluation

- Sensor and TransducerDocument15 pagesSensor and Transducerrashmi patil100% (1)

- HP EQUIVWPN-wmDocument16 pagesHP EQUIVWPN-wmstruja2010Pas encore d'évaluation