Académique Documents

Professionnel Documents

Culture Documents

MM 74 HC 08

Transféré par

Iván DelgadoDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

MM 74 HC 08

Transféré par

Iván DelgadoDroits d'auteur :

Formats disponibles

MM74HC08 Quad 2-Input AND Gate

September 1983 Revised December 1999

MM74HC08 Quad 2-Input AND Gate

General Description

The MM74HC08 AND gates utilize advanced silicon-gate CMOS technology to achieve operating speeds similar to LS-TTL gates with the low power consumption of standard CMOS integrated circuits. The HC08 has buffered outputs, providing high noise immunity and the ability to drive 10 LS-TTL loads. The 74HC logic family is functionally as well as pin-out compatible with the standard 74LS logic family. All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.

Features

s Typical propagation delay: 7 ns (tPHL), 12 ns (tPLH) s Fanout of 10 LS-TTL loads s Quiescent power consumption: 2 A maximum at room temperature s Low input current: 1 A maximum

Ordering Code:

Order Number MM74HC08M MM74HC08SJ MM74HC08MTC MM74HC08N Package Number M14A M14D MTC14 N14A Package Description 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Wide 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code. (Tape and Reel not available in N14A)

Connection Diagram

Top View

1999 Fairchild Semiconductor Corporation

DS005297

www.fairchildsemi.com

MM74HC08

Absolute Maximum Ratings(Note 1)

(Note 2) Supply Voltage (VCC ) DC Input Voltage (VIN) DC Output Voltage (VOUT) Clamp Diode Current (IIK, IOK) DC Output Current, per pin (IOUT) DC VCC or GND Current, per pin (ICC) Storage Temperature Range (TSTG) Power Dissipation (PD) (Note 3) S.O. Package only Lead Temperature (TL) (Soldering 10 seconds) 260C (Note 4)

VCC

Recommended Operating Conditions

Min Supply Voltage (VCC) DC Input or Output Voltage (VIN, VOUT) Operating Temperature Range (TA) Input Rise or Fall Times (tr, tf) VCC = 2.0V VCC = 4.5V VCC = 6.0V 40 +85 1000 500 400 C ns ns ns 2 0 Max 6 VCC Units V V

0.5 to +7.0V 1.5 to VCC +1.5V 0.5 to VCC +0.5V 20 mA 25 mA 50 mA 65C to +150C 600 mW 500 mW

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur. Note 2: Unless otherwise specified all voltages are referenced to ground. Note 3: Power Dissipation temperature derating plastic N package: 12 mW/C from 65C to 85C.

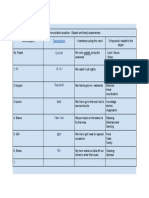

DC Electrical Characteristics

Symbol VIH Parameter Minimum HIGH Level Input Voltage VIL Maximum LOW Level Input Voltage VOH Minimum HIGH Level Output Voltage VIN = VIH

Conditions

TA = 25C Typ 1.5 3.15 4.2 0.5 1.35 1.8 2.0 4.5 6.0 4.2 5.7 0 0 0 0.2 0.2 1.9 4.4 5.9 3.98 5.48 0.1 0.1 0.1 0.26 0.26 0.1 2.0

TA = 40 to 85C TA = 40 to 125C Guaranteed Limits 1.5 3.15 4.2 0.5 1.35 1.8 1.9 4.4 5.9 3.84 5.34 0.1 0.1 0.1 0.33 0.33 1.0 20 1.5 3.15 4.2 0.5 1.35 1.8 1.9 4.4 5.9 3.7 5.2 0.1 0.1 0.1 0.4 0.4 1.0 40

Units V V V V V V V V V V V V V V V V A A

2.0V 4.5V 6.0V 2.0V 4.5V 6.0V |IOUT| 20 A 2.0V 4.5V 6.0V VIN = VIH |IOUT| 4.0 mA |IOUT| 5.2 mA 4.5V 6.0V 2.0V 4.5V 6.0V VIN = VIH or VIL |IOUT| 4.0 mA |IOUT| 5.2 mA 4.5V 6.0V 6.0V 6.0V

VOL

Maximum LOW Level Output Voltage

VIN = VIH or VIL |IOUT| 20 A

IIN ICC

Maximum Input Current

VIN = VCC or GND IOUT = 0 A

Maximum Quiescent Supply Current VIN = VCC or GND

Note 4: For a power supply of 5V 10% the worst case output voltages (VOH, and VOL) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case VIH and VIL occur at VCC = 5.5V and 4.5V respectively. (The VIH value at 5.5V is 3.85V.) The worst case leakage current (IIN, ICC, and IOZ) occur for CMOS at the higher voltage and so the 6.0V values should be used.

www.fairchildsemi.com

MM74HC08

AC Electrical Characteristics

VCC = 5V, TA = 25C, CL = 15 pF, tr = tf = 6 ns Symbol tPHL tPLH Parameter Maximum Propagation Delay, Output HIGH-to-LOW Maximum Propagation Delay, Output LOW-to-HIGH 7 15 ns Conditions Typ 12 Guaranteed Limit 20 Units ns

AC Electrical Characteristics

VCC = 2.0V to 6.0V, CL = 50 pF, tr = tf = 6 ns (unless otherwise specified) Symbol tPHL Parameter Maximum Propagation Delay, Output HIGH-to-LOW tPLH Maximum Propagation Delay, Output LOW-to-HIGH tTLH, tTHL Maximum Output Rise and Fall Time CPD CIN Power Dissipation Capacitance (Note 5) Maximum Input Capacitance (per gate) Conditions VCC 2.0V 4.5V 6.0V 2.0V 4.5V 6.0V 2.0V 4.5V 6.0V TA = 25C Typ 77 15 13 30 10 8 30 8 7 38 4 10 10 121 24 20 90 18 15 75 15 13 TA = 40 to 125C Guaranteed Limits 175 35 30 134 27 23 110 22 19 ns ns ns ns ns ns ns ns ns pF pF Units

Note 5: CPD determines the no load dynamic power consumption, PD = CPD VCC2 f + ICC VCC, and the no load dynamic current consumption, IS = CPD VCC f + ICC.

www.fairchildsemi.com

MM74HC08

Physical Dimensions inches (millimeters) unless otherwise noted

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow Body Package Number M14A

www.fairchildsemi.com

MM74HC08

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide Package Number M14D

www.fairchildsemi.com

MM74HC08

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide Package Number MTC14

www.fairchildsemi.com

MM74HC08 Quad 2-Input AND Gate

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 7 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

www.fairchildsemi.com

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Grammar PDFDocument27 pagesGrammar PDFIván DelgadoPas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Transcription: We Solve Puzzles During The Weekends - Loisir / Leisure. - Stress. - DecorationDocument2 pagesTranscription: We Solve Puzzles During The Weekends - Loisir / Leisure. - Stress. - DecorationIván DelgadoPas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Transcription: We Solve Puzzles During The Weekends - Loisir / Leisure. - Stress. - DecorationDocument1 pageTranscription: We Solve Puzzles During The Weekends - Loisir / Leisure. - Stress. - DecorationIván DelgadoPas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Readme - Guide To Files PDFDocument2 pagesReadme - Guide To Files PDFIván DelgadoPas encore d'évaluation

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Story MappingDocument2 pagesStory MappingghoyarbidePas encore d'évaluation

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Mabaqueroc@Document1 pageMabaqueroc@Iván DelgadoPas encore d'évaluation

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Reading QuizDocument1 pageReading QuizIván DelgadoPas encore d'évaluation

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Read The Following Questions and THEN Read The Text Can Reading Make You Smarter?' To Answer ThemDocument1 pageRead The Following Questions and THEN Read The Text Can Reading Make You Smarter?' To Answer ThemIván DelgadoPas encore d'évaluation

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- MM 74 HC 08Document7 pagesMM 74 HC 08Iván DelgadoPas encore d'évaluation

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- 1999, 2003 - Purple Triangles - BrochureDocument32 pages1999, 2003 - Purple Triangles - BrochureMaria Patinha100% (2)

- Drug Distribution MethodsDocument40 pagesDrug Distribution MethodsMuhammad Masoom Akhtar100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Mathematicaleconomics PDFDocument84 pagesMathematicaleconomics PDFSayyid JifriPas encore d'évaluation

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Storey Publishing Fall 2017 CatalogDocument108 pagesStorey Publishing Fall 2017 CatalogStorey PublishingPas encore d'évaluation

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Midterm Decision Analysis ExercisesDocument5 pagesMidterm Decision Analysis ExercisesAYLEN INJAYAPas encore d'évaluation

- Analysing Worship in The Pentateuch and Its ApplicationDocument12 pagesAnalysing Worship in The Pentateuch and Its ApplicationDaniel Solomon100% (1)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- ACT December 2018 Form B05 PDFDocument54 pagesACT December 2018 Form B05 PDFPranav ChatiPas encore d'évaluation

- Creating Literacy Instruction For All Students ResourceDocument25 pagesCreating Literacy Instruction For All Students ResourceNicole RickettsPas encore d'évaluation

- Carbon Facial Copies of SlidesDocument33 pagesCarbon Facial Copies of Slides77yr72cdh6Pas encore d'évaluation

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- RFP On Internal AuditDocument33 pagesRFP On Internal AuditCan dien tu Thai Binh DuongPas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Ministry of Truth Big Brother Watch 290123Document106 pagesMinistry of Truth Big Brother Watch 290123Valentin ChirilaPas encore d'évaluation

- Filipino HousesDocument4 pagesFilipino HousesjackPas encore d'évaluation

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Introduction To The Field of Organizational BehaviorDocument22 pagesIntroduction To The Field of Organizational BehaviorSayyid Al AriziePas encore d'évaluation

- Sample Internship PPTDocument19 pagesSample Internship PPTSangeeta JamadarPas encore d'évaluation

- Stroke Practice GuidelineDocument274 pagesStroke Practice GuidelineCamila HernandezPas encore d'évaluation

- NorthStar 5th Edition Reading-Writing SKILLS 3-4Document265 pagesNorthStar 5th Edition Reading-Writing SKILLS 3-4Hassan JENZYPas encore d'évaluation

- Vrushalirhatwal (14 0)Document5 pagesVrushalirhatwal (14 0)GuruRakshithPas encore d'évaluation

- Air Augmented Rocket (285pages) Propulsion ConceptsDocument285 pagesAir Augmented Rocket (285pages) Propulsion ConceptsAlexandre PereiraPas encore d'évaluation

- TLS FinalDocument69 pagesTLS FinalGrace Arthur100% (1)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- CV AmosDocument4 pagesCV Amoscharity busoloPas encore d'évaluation

- Public Administration 2000 - CSS ForumsDocument3 pagesPublic Administration 2000 - CSS ForumsMansoor Ali KhanPas encore d'évaluation

- Nurse-Patient Trust RelationshipDocument12 pagesNurse-Patient Trust RelationshipMarina Costa100% (1)

- Behaviour of Investors in Indian Equity Markets: Submitted byDocument26 pagesBehaviour of Investors in Indian Equity Markets: Submitted byDibyanshu AmanPas encore d'évaluation

- Argumentative Essay Project DescriptionDocument5 pagesArgumentative Essay Project DescriptionKaren Jh MoncayoPas encore d'évaluation

- New Document (116) New Document (115) New Document (1Document9 pagesNew Document (116) New Document (115) New Document (1Manav PARMARPas encore d'évaluation

- 38 Page 2046 2159 PDFDocument114 pages38 Page 2046 2159 PDFAkansha SharmaPas encore d'évaluation

- Effects of Alcohol, Tobacco, and Marijuana - PR 1Document11 pagesEffects of Alcohol, Tobacco, and Marijuana - PR 1Mark Andris GempisawPas encore d'évaluation

- Full Download Social Animal 14th Edition Aronson Test BankDocument35 pagesFull Download Social Animal 14th Edition Aronson Test Banknaeensiyev100% (32)

- Oration For Jon Kyle ValdehuezaDocument2 pagesOration For Jon Kyle ValdehuezaJakes ValPas encore d'évaluation

- LakmeDocument34 pagesLakmeSuraj Pratap Sawhney79% (14)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)