Académique Documents

Professionnel Documents

Culture Documents

Unit4 VTU Format PDF

Transféré par

ammayi9845_930467904Description originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Unit4 VTU Format PDF

Transféré par

ammayi9845_930467904Droits d'auteur :

Formats disponibles

UNIT#4 Instruction and programming

4.1Assembly language instructions can be classified as: Arithmetic operations. Load and store instructions. Logical operations. Program-control operations

Operators Used in Instruction Set:

Table 4.1. Operator used in instruction set

4.1.1 Arithmetic operations:

Add Instructions: Syntax ADD Smem, src ADD Smem, TS, src ADD Smem, 16, src [ , dst ] ADD Smem [, SHIFT ], src [ , dst ] ADD Xmem, SHFT, src ADD Xmem, Ymem, dst ADD #lk [, SHFT ], src [ , dst ] ADD #lk, 16, src [ , dst ] ADD src [ , SHIFT ] [ , dst ] ADD src, ASM [ , dst ] ADDC Smem, src ADDM #lk, Smem Expression src src = src + Smem src = src + Smem << TS dst = src + Smem << 16 dst = src + Smem << SHIFT src = src + Xmem << SHFT dst = Xmem << 16 + Ymem << 16 dst = src + #lk << SHFT dst = src + #lk << 16 dst = dst + src << SHIFT dst = dst + src << ASM src = src + Smem + C Smem = Smem + #lk

ADD: Add to Accumulator Syntax : 1: ADD Smem, src 2: ADD Smem, TS, src 3: ADD Smem, 16, src [, dst ] 4: ADD Smem [, SHIFT], src [, dst ] 5: ADD Xmem, SHFT, src 6: ADD Xmem, Ymem, dst 7: ADD #lk [, SHFT], src [, dst ] 8: ADD #lk, 16, src [, dst ] 9: ADD src [, SHIFT], [, dst ] 10: ADD src, ASM [, dst ] Operands : Smem: Xmem, Ymem: src, dst: Single data-memory operand Dual data-memory operands A (accumulator A) B (accumulator B)

32 768 lk 32 767 16 SHIFT 15 0 SHFT 15 Execution : 1: (Smem) + (src) src 2: (Smem) << (TS) + (src) src 3: (Smem) << 16 + (src) dst 4: (Smem) [<< SHIFT] + (src) dst 5: (Xmem) << SHFT + (src) src 6: ((Xmem) + (Ymem)) << 16 dst 7: lk << SHFT + (src ) dst 8: lk << 16 + (src) dst 9: (src or [dst]) + (src) << SHIFT dst 10: (src or [dst]) + (src) << ASM dst Status Bits: Affected by SXM and OVM Affects C and OVdst (or OVsrc, if dst = src)

Example 1 ADD *AR3+, 14, A Before Instruction After Instruction

Example 2. ADD A, 8, B Before Instruction After Instruction

ADDC : Add to Accumulator With Carry Syntax: Syntax: ADDC Smem, src Operands: Smem: Single data-memory operand Src: A (accumulator A) B (accumulator B) (Smem) + (src) + (C) src Affected by OVM, C Affects C and OVsrc

Execution: Status Bits

Example: ADDC *+AR2(5), A ADDM: Add Long-Immediate Value to Memory Syntax: ADDM #lk, Smem Operands: Smem: Single data-memory operand 32 768 lk 32 767 Execution: Status Bits: #lk + (Smem) Smem Affected by OVM and SXM Affects C and OVA

Example 1: ADDM 0123Bh, *AR4+ Example 2: ADDM 0FFF8h, *AR4+

ADDS: Add to Accumulator with Sign-Extension Suppressed

Example:

SUB: Subtract From Accumulator

Example:

SUBB: Subtract From Accumulator with Borrow

SUBC: Subtract Conditionally

SUBS: Subtract with accumulator with sign extension suppressed

MPY: Multiply With/Without Rounding

MPYA: Multiply by Accumulator A

MPYU:Multiply Unsigned

SQUR: Square

SQURA: Square and Accumulate

SQURS: Square and Subtract

MAC[R]: Multiply Accumulate With/Without Rounding

MACA[R]: Multiply by Accumulator A and Accumulate With/Without Rounding

MACD: Multiply by Program Memory and Accumulate With Delay

MACP: Multiply by Program Memory and Accumulate

MACSU: Multiply Signed by Unsigned and Accumulate

MACSU: Multiply Signed by Unsigned and Accumulate

MAS[R] :Multiply and Subtract With/Without Rounding

MASA[R] :Multiply by Accumulator A and Subtract With/Without Rounding

MAX :Accumulator Maximum

MIN : Accumulator Minimum

ABDST: Absolute Distance

ABS: Absolute Value of Accumulator

CMPL :Complement Accumulator

CMPM :Compare Memory With Long Immediate

CMPS :Compare, Select and Store Maximum

EXP: Accumulator Exponent

SAT :Saturate Accumulator

NORM: Normalization

4.1.2 Logical Operations: AND: AND With Accumulator

ANDM:AND Memory With Long Immediate

OR: OR with Accumulator

ORM: OR Memory With Constant

XOR: Exclusive OR With Accumulator

XORM: Exclusive OR Memory with Constant

ROL: Rotate Accumulator Left

ROLTC: Rotate Accumulator Left Using TC

ROR: Rotate Accumulator Right

SFTA: Shift Accumulator Arithmetically

SFTC: Shift Accumulator Conditionally

SFTL: Shift Accumulator Logically

BIT :Test Bit

BITF: Test Bit Field Specified by Immediate Value

BITT :Test Bit Specified by T

4.1.3.Load and Store operations: LD: Load Accumulator with Shift

LD :Load T/DP/ASM/ARP

LDM: Load Memory-Mapped Register

LD||MAC[R] :Load Accumulator With Parallel Multiply Accumulate With/Without Rounding

LD||MAS[R]: Load Accumulator With Parallel Multiply Subtract With/Without Rounding

LDR: Load Memory Value in Accumulator High With Rounding

LDU :Load Unsigned Memory Value

LMS: Least Mean Square

LTD :Load T and Insert Delay

ST : Store T, TRN, or Immediate Value Into Memory

STH : Store Accumulator High Into Memory

STL: Store Accumulator Low Into Memory

ST||ADD : Store Accumulator With Parallel Add

ST||LD: Store Accumulator with Parallel Load

ST||MAC[R]: Store Accumulator With Parallel Multiply Accumulate With/Without Rounding

ST||MAS[R]: Store Accumulator With Parallel Multiply Subtract With/Without Rounding

ST||MPY: Store Accumulator With Parallel Multiply

ST||SUB: Store Accumulator With Parallel Subtract

STRCD: Store T Conditionally

4.1.4. Miscellaneous Load-Type and Store-Type Instructions MVDD: Move Data From Data Memory to Data Memory With X, Y addressing

MVDK: Move Data From Data Memory to Data Memory With Destination Addressing

MVDM: Move Data From Data Memory to Memory-Mapped Register

MVDP: Move Data from Data Memory to Program Memory

MVKD: Move Data From Data Memory to Data Memory With Source Addressing

MVMD: Move Data From Memory-Mapped Register to Data Memory

MVMM: Move Data From Memory-Mapped Register to Memory-Mapped Register

MVPD: Move Data From Program Memory to Data Memory

PORTR: Read Data from Port

PORTW: Write Data to Port

READA: Read Program Memory addressed by Accumulator A and Store in Data Memory

WRITA: Write Data to Program Memory Addressed by Accumulator A

Branch Instructions B[D]: Branch Unconditionally

BACC[D]: Branch to Location Specified by Accumulator

BANZ[D]: Branch on Auxiliary Register Not Zero

BC[D]: Branch Conditionally

FB[D]: Far Branch Unconditionally

FBACC[D]: Far Branch to Location Specified by Accumulator

CALA[D]: Call Subroutine at Location Specified by Accumulator

CALL[D]: Call Unconditionally

CC[D]: Call Conditionally

FCALA[D]: Far Call Subroutine at Location Specified by Accumulator

FCALL[D]: Far Call Unconditionally

4.1.5.Interrupt Instructions:

INTR: Software Interrupt

TRAP: Software Interrupt

4.1.6. Return Instructions FRET[D]: Far Return

FRETE[D]: Enable Interrupts and Far Return From Interrupt

RC[D]: Return Conditionally

RET[D]: Return

RETE[D]: Enable Interrupts and Return From Interrupt.

RETF[D]: Enable Interrupts and Fast Return From Interrupt

4.1.7. Repeat Instructions

RPT: Repeat Next Instruction

RPTB[D]: Block Repeat

RPTZ: Repeat Next Instruction and Clear Accumulator

4.1.8.Stack-Manipulating Instructions FRAME: Stack Pointer Immediate Offset

POPD: Pop Top of Stack to Data Memory

POPM: Pop Top of Stack to Memory-Mapped Register

PSHD: Push Data-Memory Value onto Stack

PSHM: Push Memory-Mapped Register onto Stack

4.1.9. Miscellaneous Program-Control Instructions

SSBX: Set Status Register Bit

RSBX: Reset Status Register Bit

NOP: No Operation

RESET: Software Reset

4.2. Programming Examples Assembly Files Describe steps to create executable output files Create an assembly file containing: Code Constants (initialized data) Variables Create a linker command file which:

Identifies input and output files Describes a systems available memory Indicates where code and data shall be located Develop multi-file systems

Figure 4.1. Assembly conventions diagram. Any ASCII text is O.K Use .asm extension Instructions & directives cannot be in first column Comments O.K any column after semicolon Mnemonics Lines of 320 code Generally written in upper case Become components of program memory Directives Begin with a period (.) and are lower case Can create constants and variables

May occupy no memory space when used to control ASM and LNK process

Table 4.2.Different COFF data types

The .bss Directive: Only directive with assembly label defined in the operand field Use separate .bss statements for each named variable

Remember .bss by thinking:: Block - reserves a block of memory Symbol - beginning at address symbol Size - of the specified size Example: Create a 5-word array x

Table 4.3.Different Assembler Directives

Table 4.4.Different Named section

Table 4.5. Summary of COFF Directive

Example: 1.write a program to find the sum of a series of signed numbers stored at successive locations in the data memory and places the result in the accumulator. Solution: AR1as pointer to the numbers. AR2 as counter for the numbers. Accumulator value set to zero. Sign extension mode is selected. Add each number into accumulator. Increment the pointer & decrement the counter. Repeat until count in AR2 reaches zero.

Accumulator contains the sum of number. This program computes the signed sum of data memory locations from address 410h to 41fh.The result is placed in A. A=dmad(410h)+dmad(411h)+..+ dmad(41fh)

.mmregs .global _c_int000 .text ._c_int00: STM #10h, AR2 STM #410h, AR2 LD #0h, A SSBX SXM START: ADD *AR1+, A BANZ START, *AR2NOP .end

:initialize counter AR2=10h :Initialize Pointer AR2=410h :Initialize sum A=0 :Select sign extension mode :Add the next data value :Repeat if not done :No operation

Eaxmple2: Program to computes multiply and accumulate using direct addressing mode: Y (n) =h0x(n)+h1x(n-1)+h2x(n-2) Solution: data memory

h0x(n),h1x(n-1)&h2x(n-2)are :(T)*(dmad)Acc A or B

computed

using

MPY

instruction

Accumulator contain output value Acc (15-0) dmad

Acc (31-16) dmad+1

.global _c_int00 X Y h .usect Input Samples, 3 .usect outout, 2 .usect coefficient, 3 .text

_c_int00: SSBX LD LD LD MPY LD LD LD MPY ADD LD LD LD MPY ADD SXM #h, DP @h, T #x, DP @x, A #h, DP @h+1, T #x, DP @x+1, B A, B #h, DP @h+2, T #x, DP @x+2, B A, B ;Select sign extension mode ;Select the data page for coefficients ;get the coefficient h(0) ;select the data page for input samples ; A = x(n) * h(0) ; select the data page for coefficients ; get the coefficient h(1) ;select the data page for input singals ; B = x(n-1) * h(1) ; B = x(n)*h(0) + x(n-1)*h(1) ; select the data page for coefficients ; get the coefficient h(2) ;select the data page for input samples ; B = x(n-2) * h(1) ; B = x(n)*h(0)+ x(n-1)*h(1) + x(n-2) * h(2)

LD #y, DP STL B, @y STH B, @y+1 NOP .end

; select the data page for outputs ; save low part of output ; save high part of output ; No operation

Example3: Program computes multiply and accumulate using indirect addressing mode

.global _c_int00 h .int 10, 20, 30 .text

_c_int00: SSBX STM 310H STM MPY MPY ADD

SXM ; Select sign extension mode #310H, AR2 ; Initialize pointer AR2 for x(n) stored at @h, AR3 *AR2+,*AR3+, A *AR2+,*AR3+, B A, B ; Initialize pointer AR3 for coefficients ; A = x(n) * h(0) ; A = x(n-1) * h(1) ; B = x(n) * h(0) + x(n-1) * h(1)

MPY *AR2+,*AR3+, A ADD A, B STL B, *AR2+ STH B, * AR2+ NOP .end

; A = x(n-2) * h(2) ; B = x(n) * h(0) + x(n-1) * h(1) + x(n-2) * h(2) ; Save low part of result ; Save high part of result ; No operation

Example4: Program computes multiply and accumulate using MAC instruction :

.global _c_int00 .data .bss x, 3 .bss y, 2 h .int 10, 20, 30 .text _c_int00: SSBX SXM STM #x, AR2

; Select sign extension mode ; Initialize AR2 to point to x(n)

STM #h, AR3 LD #0H, A RPT #2 MAC *AR2+,*AR3+,A STM #y, AR2 STL A, *AR2+ STL A, *AR2+ NOP .end

; Initialize AR3 to point to h(0) ; Initialize result in A = 0 ; Repeat the next operation 3 times ; y(n) computed ; Select the page for y(n) ; Save the low part of y(n) ; Save the high part of y(n) ; No operation

4.3. On chip peripherals: It facilitates interfacing with external devices. The peripherals are: General purpose I/O pins A software programmable wait state Hardware timer Host port interface (HPI) Clock generator Serial port 4.3.1 It has two general purpose I/O pins: BIOinput pin used to monitor the status of external devices. XF output pin, software controlled used to signal external devices 4.3.2. Software programmable wait state generator: Extends external bus cycles up to seven machine cycles. generator.

4.3.3. Hardware Timer An on chip down counter Used to generate signal to initiate any interrupt or any other process Consists of 3 memory mapped registers: The timer register (TIM) Timer period register (PRD) Timer controls register (TCR) Pre scaler block (PSC). TDDR (Time Divide Down ratio) TIN &TOUT

The timer register (TIM) is a 16-bit memory-mapped register that decrements at every pulse from the prescaler block (PSC). The timer period register (PRD) is a 16-bit memory-mapped register whose contents are loaded onto the TIM whenever the TIM decrements to zero or the device is reset (SRESET). The timer can also be independently reset using the TRB signal. The timer control register (TCR) is a 16-bit memory-mapped register that contains status and control bits. Table shows the functions of the various bits in the TCR. The prescaler block is also an on-chip counter. Whenever the prescaler bits count down to 0, a clock pulse is given to the TIM register that decrements the TIM register by 1. The TDDR bits contain the divide-down ratio, which is loaded onto the prescaler block after each time the prescaler bits count down to 0. That is to say that the 4-bit value of TDDR determines the divide-by ratio of the timer clock with respect to the system clock. In other words, the TIM decrements either at the rate of the system clock or at a rate slower than that as decided by the value of the TDDR bits. TOUT and TINT are the output signal generated as the TIM register decrements to 0. TOUT can trigger the start of the conversion signal in an ADC interfaced to the DSP. The sampling frequency of the ADC determines how frequently it receives the TOUT signal. TINT is used to generate interrupts, which are required to service a peripheral such as a DRAM controller periodically. The timer can also be stopped, restarted, reset, or disabled by specific status bits.

Bit 15-12 11

Name Reserved Soft

Function Reserved; always read as 0. Used in conjunction with the free bit to determine the state of the timer Soft=0,the timer stops immediately. Soft=1,the timer stops when the counter decrements to 0.

10

Free

Use in conjunction with the soft bit Free=0,the soft bit selects the timer mode free=1,the timer runs free

Bit 9-6

Name PSC

Function Timer prescaler counter, specifies the count for the on-chip timer

TRB

Timer reload. Reset the on-chip timer.

TSS

Timer stop status, stop or starts the on-chip timer.

3-0

TDDR

Timer divide-down ration

Table 4.6. Pin details of software wait state generator

Figure 4.2.Logical block diagram of timer circuit. 4.3.4. Host port interface (HPI): Allows to interface to an 8bit or 16bit host devices or a host processor Signals in HPI are: Host interrupt (HINT) HRDY HCNTL0 &HCNTL1 HBIL HR/

4.3. A generic diagram of the host port interface (HPI) Important signals in the HPI are as follows: The 16-bit data bus and the 18-bit address bus. The host interrupt, Hint, for the DSP to signal the host when it attention is required. HRDY, a DSP output indicating that the DSP is ready for transfer. HCNTL0 and HCNTL1, control signal that indicate the type of transfer to carry out. The transfer types are data, address, etc. HBIL. If this is low it indicates that the current byte is the first byte; if it is high, it indicates that it is second byte. HR/W indicates if the host is carrying out a read operation or a write operation

4.3.5. Clock Generator: The clock generator on TMS320C54xx devices has two options-an external clock and the internal clock. In the case of the external clock option, a clock source is directly connected to the device. The internal clock source option, on the other hand, uses an internal clock generator and a phase locked loop (PLL) circuit. The PLL, in turn, can be hardware configured or software programmed. Not all

devices of the TMS320C54xx family have all these clock options; they vary from device to device. 4.3.6. Serial I/O Ports: Three types of serial ports are available: Synchronous ports. Buffered ports. Time-division multiplexed ports. The synchronous serial ports are high-speed, full-duplex ports and that provide direct communications with serial devices, such as codec, and analog-to-digital (A/D) converters. A buffered serial port (BSP) is synchronous serial port that is provided with an auto buffering unit and is clocked at the full clock rate. The head of servicing interrupts. A time-division multiplexed (TDM) serial port is a synchronous serial port that is provided to allow time-division multiplexing of the data. The functioning of each of these on-chip peripherals is controlled by memory-mapped registers assigned to the respective peripheral.

4.4. Interrupts of TMS320C54xx Processors: Many times, when CPU is in the midst of executing a program, a peripheral device may require a service from the CPU. In such a situation, the main program may be interrupted by a signal generated by the peripheral devices. This results in the processor suspending the main program in order to execute another program, called interrupt service routine, to service the peripheral device. On completion of the interrupt service routine, the processor returns to the main program to continue from where it left. Interrupt may be generated either by an internal or an external device. It may also be generated by software. Not all interrupts are serviced when they occur. Only those interrupts that are called nonmaskable are serviced when ever they occur. Other interrupts, which are called maskable interrupts, are serviced only if they are enabled. There is also a priority to determine which interrupt gets serviced first if more than one interrupts occur simultaneously. Almost all the devices of TMS320C54xx family have 32 interrupts. However, the types and the number under each type vary from device to device. Some of these interrupts are reserved for use by the CPU. 4.5. Pipeline operation of TMS320C54xx Processors: The CPU of 54xx devices have a six-level-deep instruction pipeline. The six stages of the pipeline are independent of each other. This allows overlapping execution of

instructions. During any given cycle, up to six different instructions can be active, each at a different stage of processing. The six levels of the pipeline structure are program prefetch, program fetch, decode, access, read and execute. 1 2 During program prefetch, the program address bus, PAB, is loaded with the address of the next instruction to be fetched. In the fetch phase, an instruction word is fetched from the program bus, PB, and loaded into the instruction register, IR. These two phases from the instruction fetch sequence. During the decode stage, the contents of the instruction register, IR are decoded to determine the type of memory access operation and the control signals required for the data-address generation unit and the CPU. The access phase outputs the read operands on the data address bus, DAB. If a second operand is required, the other data address bus, CAB, also loaded with an appropriate address. Auxiliary registers in indirect addressing mode and the stack pointer (SP) are also updated. In the read phase the data operand(s), if any, are read from the data buses, DB and CB. This phase completes the two-phase read process and starts the twophase write processes. The data address of the write operand, if any, is loaded into the data write address bus, EAB. The execute phase writes the data using the data write bus, EB, and completes the operand write sequence. The instruction is executed in this phase.

Figure 4.4. Pipeline operation of TMS320C54xx Processors

Figure 4.5.Pipe flow diagram

Eaxmple1: Show the pipeline operation of the following sequence of instructions if the initial value of AR3 is 80 & the values stored in memory location 80, 81, 82 are 1, 2 & 3. LD *AR3+, A ADD #1000h, A STL A, *AR3+

Figure 4.6. Pipeline operation for above example1

Show the pipeline operation of the following sequence of instructions if the initial value of AR1,AR3,A are 84,81,1 & the values stored in memory location 81,82,83,84 are 2,3,4,6.Also provide the values of registers AR3,AR1,T & accumulator A ,after completion of each cycle. ADD LD MPY ADD . . . *AR3+,A *AR1+, T *AR3+, B B, A,

Figure 4.7. Pipeline operation for above example2

Vous aimerez peut-être aussi

- Instructions and Instruction SequencingDocument25 pagesInstructions and Instruction Sequencingsamueljamespeter100% (4)

- Microprocessor Short Questions (Part-2)Document11 pagesMicroprocessor Short Questions (Part-2)Ln Amitav BiswasPas encore d'évaluation

- Unit 3 - Computer Architecture - WWW - Rgpvnotes.inDocument14 pagesUnit 3 - Computer Architecture - WWW - Rgpvnotes.inNathuram GodsePas encore d'évaluation

- MP Lab ObservationDocument115 pagesMP Lab ObservationBhargav Mushini100% (1)

- Instruction Set of c54xDocument1 pageInstruction Set of c54xshajehanPas encore d'évaluation

- CSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsDocument8 pagesCSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsSandipChowdhuryPas encore d'évaluation

- Lab Manual - ProcessorDocument47 pagesLab Manual - ProcessorSurendran DevarajanPas encore d'évaluation

- Asm AsmblerDocument93 pagesAsm AsmblerstormviruxPas encore d'évaluation

- The 8085 Instruction SetDocument30 pagesThe 8085 Instruction SetSindu RangaswamyPas encore d'évaluation

- COA Unit 3Document52 pagesCOA Unit 3guptakrishns23Pas encore d'évaluation

- Lab Workbook of Microprocessor For StudentsDocument43 pagesLab Workbook of Microprocessor For StudentsHarris Baig100% (1)

- CPUDocument50 pagesCPUabhishek sPas encore d'évaluation

- COE301 Lab 12 Single Cycle CPU DesignDocument10 pagesCOE301 Lab 12 Single Cycle CPU DesignItz Sami UddinPas encore d'évaluation

- Microsoft Word - Unit4 VTU FormatDocument100 pagesMicrosoft Word - Unit4 VTU FormatKrishPas encore d'évaluation

- Chapter 5Document86 pagesChapter 5Muhammad OmerPas encore d'évaluation

- ARM Instruction SetDocument29 pagesARM Instruction SetNeeshank MahajanPas encore d'évaluation

- 6 RISCvsCISCDocument28 pages6 RISCvsCISCAnushiMaheshwariPas encore d'évaluation

- 05 Instruction SetDocument36 pages05 Instruction SetFurkan TopaloğluPas encore d'évaluation

- Design Contest 2010 MentorDocument27 pagesDesign Contest 2010 MentorUjjwal KantPas encore d'évaluation

- SRC SRC SRC SRC SRC DST DST DST DSTDocument3 pagesSRC SRC SRC SRC SRC DST DST DST DSTnorbihaverPas encore d'évaluation

- Question No. 1 16 Bit Processor Opcode General Purpose Register ALU R1 R2 R3 R4 R5 R6 R7 R8Document11 pagesQuestion No. 1 16 Bit Processor Opcode General Purpose Register ALU R1 R2 R3 R4 R5 R6 R7 R8mihafeezPas encore d'évaluation

- Cha 1Document31 pagesCha 1Asha NaveenPas encore d'évaluation

- Computer Organization Chapter 8 Short NoteDocument31 pagesComputer Organization Chapter 8 Short NoteMeskatul Islam2100% (1)

- Chapter 02Document4 pagesChapter 02John doePas encore d'évaluation

- Bascom CodingDocument9 pagesBascom CodingJoel MendozaPas encore d'évaluation

- Chapter-5: Assembly Language Programming Using 8086 (16 Marks)Document55 pagesChapter-5: Assembly Language Programming Using 8086 (16 Marks)PRABHAKAR MOREPas encore d'évaluation

- Chapter 02Document58 pagesChapter 02vvnhjhjPas encore d'évaluation

- 2 MarksDocument17 pages2 MarksGeetha ParthibanPas encore d'évaluation

- System Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversityDocument31 pagesSystem Software and Machine Architecture: Department of Computer Science National Tsing Hua UniversitymonajosephjustinPas encore d'évaluation

- MPMC Manual - Ar17Document87 pagesMPMC Manual - Ar17Sowmya ChowdaryPas encore d'évaluation

- FALLSEM2021-22 CSE2006 ETH VL2021220103995 Reference Material I 17-Aug-2021 ALP INTRODocument13 pagesFALLSEM2021-22 CSE2006 ETH VL2021220103995 Reference Material I 17-Aug-2021 ALP INTROvivek kilaparthiPas encore d'évaluation

- By: Dr. Anil Swarnkar Assistant Professor Department of Electrical Engineering, MNIT, JaipurDocument115 pagesBy: Dr. Anil Swarnkar Assistant Professor Department of Electrical Engineering, MNIT, Jaipurpankajkthr100% (2)

- 11 Instruction Set of 8086Document61 pages11 Instruction Set of 8086kingmeno0% (1)

- Opcode AsmDocument72 pagesOpcode AsmbingbanglaPas encore d'évaluation

- 8085 Instruction SetDocument43 pages8085 Instruction SetprajwaleliyaPas encore d'évaluation

- Instruction Formats & Addressing Modes Prof. M P Patel: Topic: Guided byDocument21 pagesInstruction Formats & Addressing Modes Prof. M P Patel: Topic: Guided byHarshit BhayaniPas encore d'évaluation

- PDF of Instruction FormatDocument18 pagesPDF of Instruction FormatSaGar MallaPas encore d'évaluation

- Addressing Modes & Instruction SetDocument39 pagesAddressing Modes & Instruction SetlekaPas encore d'évaluation

- Chapter04 ProcessorDesign PDFDocument39 pagesChapter04 ProcessorDesign PDFTrần Thảo NguyênPas encore d'évaluation

- Project Description:: Comm14 Version (I) MicroprocessorDocument7 pagesProject Description:: Comm14 Version (I) MicroprocessorMarwan AhmedPas encore d'évaluation

- Processor: Aim: To Find Volume of Cone by The Value of Radius and Height Using 8087 Tool UsedDocument3 pagesProcessor: Aim: To Find Volume of Cone by The Value of Radius and Height Using 8087 Tool UsedHARIKET SUKESH KUMAR SHETHPas encore d'évaluation

- ARM Instruction SetDocument75 pagesARM Instruction SetEragon ShadeSlayerPas encore d'évaluation

- Motorola68k 2Document114 pagesMotorola68k 2SoumyabrataPatraPas encore d'évaluation

- Central Processing UnitDocument43 pagesCentral Processing Unitmanishbhardwaj8131Pas encore d'évaluation

- Microprocessor (MP) - : Lab Manual:-: Saraswati College of Engineering, KhargharDocument23 pagesMicroprocessor (MP) - : Lab Manual:-: Saraswati College of Engineering, KhargharnikitaPas encore d'évaluation

- Ics 232 Lab 1Document9 pagesIcs 232 Lab 1psl36533Pas encore d'évaluation

- System Software 2 Marks and 16 Marks With AnswerDocument23 pagesSystem Software 2 Marks and 16 Marks With AnswerpriyaaramPas encore d'évaluation

- Central Processing Unit: Cpe 252: Computer Organization 1Document30 pagesCentral Processing Unit: Cpe 252: Computer Organization 1sulekhaisaacPas encore d'évaluation

- Instruction Set ArchitectureDocument27 pagesInstruction Set Architecturejeroro6730Pas encore d'évaluation

- Week 2Document22 pagesWeek 2Shubhadeep GhatakPas encore d'évaluation

- MP Lab ManualDocument54 pagesMP Lab Manualsateesh180siri0% (2)

- CPU Organization Bindu AgarwallaDocument22 pagesCPU Organization Bindu AgarwallaNobodyPas encore d'évaluation

- Unit 2Document166 pagesUnit 2rohanrec92Pas encore d'évaluation

- Introducition To Masm/Tasm: Assembly Language Programming Using Masm SoftwareDocument159 pagesIntroducition To Masm/Tasm: Assembly Language Programming Using Masm SoftwareShah JahanPas encore d'évaluation

- MicroDocument20 pagesMicro142 Bhumika LachakePas encore d'évaluation

- Unit - 2 Central Processing Unit TOPIC 1: General Register OrganizationDocument13 pagesUnit - 2 Central Processing Unit TOPIC 1: General Register OrganizationRam Prasad GudiwadaPas encore d'évaluation

- ARM Assembly Language ExamplesDocument12 pagesARM Assembly Language Examplesabhi198808Pas encore d'évaluation

- Chapter 2Document14 pagesChapter 2Mauricio Alejandro Pozo UribePas encore d'évaluation

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationD'EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationPas encore d'évaluation

- Simcom 900 GSM Module: GSM/GPRS Modem FeturesDocument3 pagesSimcom 900 GSM Module: GSM/GPRS Modem Feturesammayi9845_930467904Pas encore d'évaluation

- Continued: Detection of A/D ConvertionDocument2 pagesContinued: Detection of A/D Convertionammayi9845_930467904Pas encore d'évaluation

- Data Acquisition - Why 3G?Document3 pagesData Acquisition - Why 3G?ammayi9845_930467904Pas encore d'évaluation

- Superscripts: 2 2x 2x 2x Subscripts: X X X XDocument1 pageSuperscripts: 2 2x 2x 2x Subscripts: X X X Xammayi9845_930467904Pas encore d'évaluation

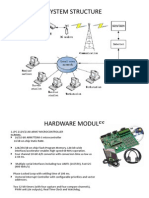

- System StructureDocument3 pagesSystem Structureammayi9845_930467904Pas encore d'évaluation

- Agenda: Phytomonitoring System Recommended Setup Block Diagram Work Done Future Work Plan ReferenceDocument3 pagesAgenda: Phytomonitoring System Recommended Setup Block Diagram Work Done Future Work Plan Referenceammayi9845_930467904Pas encore d'évaluation

- Future Work Plan: Month TasksDocument2 pagesFuture Work Plan: Month Tasksammayi9845_930467904Pas encore d'évaluation

- Work Done Till First ReviewDocument3 pagesWork Done Till First Reviewammayi9845_930467904Pas encore d'évaluation

- LCD Interfacing With lpc2148: Header File and Variable Declaration Initialization FunctionDocument3 pagesLCD Interfacing With lpc2148: Header File and Variable Declaration Initialization Functionammayi9845_930467904Pas encore d'évaluation

- February: Interfacing Multiple Sensors Using Wireless Network and Using Visual Software Display On MonitorDocument3 pagesFebruary: Interfacing Multiple Sensors Using Wireless Network and Using Visual Software Display On Monitorammayi9845_930467904Pas encore d'évaluation

- Adaptive Noise Cancellation - NewDocument21 pagesAdaptive Noise Cancellation - Newammayi9845_930467904Pas encore d'évaluation

- Work Plan: Month PlansDocument3 pagesWork Plan: Month Plansammayi9845_930467904Pas encore d'évaluation

- Phytomonitoring System: Data Colection Software SensorsDocument3 pagesPhytomonitoring System: Data Colection Software Sensorsammayi9845_930467904Pas encore d'évaluation

- Design RequirementsDocument5 pagesDesign Requirementsammayi9845_930467904Pas encore d'évaluation

- Design RequirementsDocument2 pagesDesign Requirementsammayi9845_930467904Pas encore d'évaluation

- Figure 1: A Block Diagram of A Basic FilterDocument10 pagesFigure 1: A Block Diagram of A Basic Filterammayi9845_930467904Pas encore d'évaluation

- New Proj - SynopsisDocument2 pagesNew Proj - Synopsisammayi9845_930467904Pas encore d'évaluation

- Work Flow ChartDocument3 pagesWork Flow Chartammayi9845_930467904Pas encore d'évaluation

- Swami Proj. ProposalDocument1 pageSwami Proj. Proposalammayi9845_930467904Pas encore d'évaluation

- List of Figures Fig. No. Title of The Figure Page NoDocument2 pagesList of Figures Fig. No. Title of The Figure Page Noammayi9845_930467904Pas encore d'évaluation

- List of Tables: Table No. Name of Table Page NoDocument1 pageList of Tables: Table No. Name of Table Page Noammayi9845_930467904Pas encore d'évaluation

- Declaration Certificate Acknowledgement List of Figures List of Tables AcronymsDocument2 pagesDeclaration Certificate Acknowledgement List of Figures List of Tables Acronymsammayi9845_930467904Pas encore d'évaluation

- Improving The Effectiveness of The Median Filter: Kwame Osei Boateng, Benjamin Weyori Asubam and David Sanka LaarDocument13 pagesImproving The Effectiveness of The Median Filter: Kwame Osei Boateng, Benjamin Weyori Asubam and David Sanka Laarammayi9845_930467904Pas encore d'évaluation

- Data SheetDocument56 pagesData SheetfaycelPas encore d'évaluation

- Unit-4.ppt MicrocontrollerDocument74 pagesUnit-4.ppt MicrocontrollerVigneshwaran KandaswamyPas encore d'évaluation

- Chapt Er EL EVEN: 8 2 5 5 I/O ProgrammingDocument22 pagesChapt Er EL EVEN: 8 2 5 5 I/O ProgrammingHackathon PDA CEKPas encore d'évaluation

- MPMC 2 MarksDocument13 pagesMPMC 2 Markssetup.143Pas encore d'évaluation

- Input-Output OrganizationDocument39 pagesInput-Output OrganizationTamanna SharmaPas encore d'évaluation

- Axisware PCIM Manual: FactoryLink Driver For GE Fanuc PCIM Genius BusDocument67 pagesAxisware PCIM Manual: FactoryLink Driver For GE Fanuc PCIM Genius BusAxisware LLCPas encore d'évaluation

- 8051 TutorialDocument88 pages8051 Tutorialanon-596672100% (1)

- Memory Mapped IDocument20 pagesMemory Mapped IKanika SharmaPas encore d'évaluation

- UG - EC303 DSP Part-3 Fixed Point DSP Addressing Modes - PrintDocument25 pagesUG - EC303 DSP Part-3 Fixed Point DSP Addressing Modes - PrintShreyas TaterPas encore d'évaluation

- A429 Users ManualDocument244 pagesA429 Users ManualbaburaokodavatiPas encore d'évaluation

- Unit - IiiDocument41 pagesUnit - IiiJit Agg0% (1)

- Simatic s7-1200 CatalogDocument122 pagesSimatic s7-1200 CatalogAto AnsoriPas encore d'évaluation

- Etherlink Ii Adapter Technical Reference Manual: A Member of The Etherlink Product FamilyDocument56 pagesEtherlink Ii Adapter Technical Reference Manual: A Member of The Etherlink Product Familyantonius0990Pas encore d'évaluation

- Datasheet - HK st52t400g3 202820Document94 pagesDatasheet - HK st52t400g3 202820Ian22Pas encore d'évaluation

- UNIT II - Embedded NetworkingDocument24 pagesUNIT II - Embedded NetworkingKALAIVANIPas encore d'évaluation

- Atmel SAM D21 - Datasheet PDFDocument977 pagesAtmel SAM D21 - Datasheet PDFsigiloPas encore d'évaluation

- DMA Controller (DMAC) : - Data transfer between the μP's main memory & an externalDocument6 pagesDMA Controller (DMAC) : - Data transfer between the μP's main memory & an externalharinik7100% (1)

- 8051 Atmel DatasheetDocument12 pages8051 Atmel Datasheetpranav_c22100% (3)

- Tms 320 C 10Document149 pagesTms 320 C 10saurom lamderthPas encore d'évaluation

- Lecture 3 Introduction To Peripheral DevicesDocument27 pagesLecture 3 Introduction To Peripheral DevicesRabindra DhitalPas encore d'évaluation

- Architecture, Register Organization and Flag Register of 8086 MicroprocessorDocument28 pagesArchitecture, Register Organization and Flag Register of 8086 Microprocessormkrishnad100% (1)

- The 8086 Input / Output Interface: Yamama A. Shafeek & Noor A. Yousif University of Technology Iraq, BaghdadDocument17 pagesThe 8086 Input / Output Interface: Yamama A. Shafeek & Noor A. Yousif University of Technology Iraq, BaghdadMohammed MohsinPas encore d'évaluation

- 8051 PresentationDocument40 pages8051 PresentationnavimolPas encore d'évaluation

- Computer Peripherals & InterfacingDocument128 pagesComputer Peripherals & InterfacingMd MianPas encore d'évaluation

- Microprocessor ComponentsDocument2 pagesMicroprocessor ComponentsBryan YaranonPas encore d'évaluation

- 16F54Document90 pages16F54SHAHID_71Pas encore d'évaluation

- FST ReferenceDocument146 pagesFST Referencecetec1234100% (1)

- Manual Postcard LCD 60Document32 pagesManual Postcard LCD 60TiagoKstilhosPas encore d'évaluation

- MPMC Model Exam Answer KeyDocument21 pagesMPMC Model Exam Answer KeyVenkatesan SundaramPas encore d'évaluation