Académique Documents

Professionnel Documents

Culture Documents

Practica 9 (Cronometro 0-99)

Transféré par

Leonardo MoraCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Practica 9 (Cronometro 0-99)

Transféré par

Leonardo MoraDroits d'auteur :

Formats disponibles

SEP INSTITUTO

DGEST TECNOLGICO DE

SNEST MATAMOROS

DEPARTAMENTO DE INGENIERA ELCTRICA Y ELECTRNICA

DISEO DIGITAL CON VHDL

8:00 a 9:00pm, Lunes, Mircoles, Viernes 7:00 a 9:00 pm, Martes

Prctica 9.- Cronometro en VHDL

Alumnos: Leonardo Adn Mora Vzquez Jos Fortino Rico San Martn Luis Eduardo Guzmn Puga Julin Vera vila Nm. de control: 11260099 11260110 11260085 11260125

Profesor: Ing. Arturo Rodrguez Casas

H. MATAMOROS, TAM.

05 DE NOVIEMBRE DE 2013

OBJETIVO

Implementar un cronometro del 0 al 99 con opcin de pausa y reseteo usando el Aldec HDL y el kit de desarrollo Basys 2.

MARCO TERICO

Los dispositivos digitales medidores de tiempo son una aplicacin de lgica secuencial en la solucin de una situacin de nuestra vida diaria. Un ejemplo de estos dispositivos digitales son los cronmetros.

El cronmetro es un reloj cuya precisin ha sido comprobada y certificada por algn instituto o centro de control de precisin. La palabra cronmetro es un neologismo de etimologa griega: Cronoses el dios del tiempo, metron es hoy un sufijo que significa aparato para medir.

CDIGOS VHDL

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity relojanodos is port( resetanodo,clkan:in std_logic; clkanout: out std_logic ); end relojanodos; architecture func_relojanodos of relojanodos is signal counter:std_logic_vector(19 downto 0); signal clkoutsignal: std_logic; begin process(resetanodo, clkan) begin if (resetanodo='1')then clkoutsignal<='0'; counter<=(others=>'0'); elsif(clkan'event and clkan='1')then if(counter=x"186a0")then counter<=(others=>'0'); clkoutsignal<=not clkoutsignal; else counter<=counter+1; end if; end if; end process; clkanout<=clkoutsignal; end func_relojanodos; Relojanodos

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity relojcontador is port ( rst2,clkin2 : in std_logic; clkout2 : out std_logic ); end relojcontador; architecture behavioral of relojcontador is signal counter : std_logic_Vector (27 downto 0); signal clkout2Signal : std_logic; begin process (clkin2, rst2) begin if (rst2 = '1') then clkout2Signal <= '0'; counter <= (others => '0'); elsif (clkin2'event and clkin2 = '1') then if (counter = "1011111010111100001000000")then counter <= (others => '0'); clkout2Signal <= not clkout2Signal; else counter <= counter + 1; end if; end if; end process; -- output assignments clkout2 <= clkout2Signal; end behavioral; relojcontador

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity contador7seg is port ( clkincontador,rst,start,pause,continue : in std_logic; digitOne,digitTen : out std_logic_vector (3 downto 0) ); end contador7seg; architecture func_contador7seg of contador7seg is signal digitOneSignal : std_logic_vector (3 downto 0); signal digitTenSignal : std_logic_vector (3 downto 0); type states is (resetState, countState, pauseState); signal state : states; begin process (clkincontador, rst) begin if (rst = '1') then state <= resetState; elsif (clkincontador'event and clkincontador = '1') then case state is when resetState => digitOneSignal <= (others => '0'); digitTenSignal <= (others => '0'); if (start = '1') then state <= countState; end if; when countState => if (pause = '1') then state <= pauseState; end if; if (digitOneSignal = "1001") then digitOneSignal <= (others => '0'); digitTenSignal <= digitTenSignal + '1'; if (digitTenSignal = "1001") then digitTenSignal <= (others => '0'); end if; else digitOneSignal <= digitOneSignal + '1'; end if; when pauseState => if (continue = '1') then state <= countState; end if; end case; end if; end process; digitOne <= digitOneSignal; digitTen <= digitTenSignal; end func_contador7seg;

contador7s eg

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity controldeanodos is port (clkinanodo : in std_logic; san0,san1,san2,san3 : out std_logic ); end controldeanodos; architecture func_controldeanodos of controldeanodos is signal an0Signal,an1Signal,an2Signal,an3Signal : std_logic; begin process (clkinanodo) begin if (clkinanodo = '0') then an2Signal <= '1'; an3Signal <= '0'; else an2Signal <= '0'; an3Signal <= '1'; end if; end process; -- an0 & an1 are always '1' an0Signal <= '1'; an1Signal <= '1'; -- output assignments san0 <= an0Signal; san1 <= an1Signal; san2 <= an2Signal; san3 <= an3Signal; end func_controldeanodos; controldeanodos

library IEEE; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity bcd7seg is port( binaryin: in std_logic_vector(3 downto 0); seg7out: out std_logic_vector(0 to 6) ); end bcd7seg; architecture func_bcd7seg of bcd7seg is signal seg7signal: std_logic_vector(0 to 6); begin process(binaryin) begin case binaryin is --abcdefg se encienden en 0 when "0000" =>seg7signal <= "0000001"; --0 when "0001" =>seg7signal <= "1001111"; --1 when "0010" =>seg7signal <= "0010010"; --2 when "0011" =>seg7signal <= "0000110"; --3 when "0100" =>seg7signal <= "1001100"; --4 when "0101" =>seg7signal <= "0100100"; --5 when "0110" =>seg7signal <= "0100000"; --6 when "0111" =>seg7signal <= "0001111"; --7 when "1000" =>seg7signal <= "0000000"; --8 when others =>seg7signal <= "0001100"; --9 end case; end process; --dp is always zero --seg7signal(7)<='1'; seg7out<=seg7signal; end func_bcd7seg; bcd7seg

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity mux7seg is port (an2in,an3in: in std_logic; sevenOne : in std_logic_vector (0 to 6); sevenTen : in std_logic_vector (0 to 6); sevenOut : out std_logic_vector (0 to 6) ); end mux7seg; architecture behavioral of mux7seg is signal sevenOutSignal : std_logic_vector (0 to 6); begin process (an2in, an3in, sevenOne, sevenTen) begin if (an2in = '1' and an3in = '0') then sevenOutSignal <= sevenTen; else sevenOutSignal <= sevenOne; end if; end process; sevenOut <= sevenOutSignal; end behavioral; mux7seg

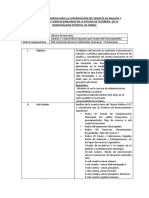

Interconexin de los componentes

U1 Reset CLK50M

re s etano d o c lk an c lk ano ut

U4

c lk inano d o s an0 s an1 s an2 s an3

relojanodos U2

rs t2 c lk in2 c lk out2

an0 an1 an2 an3 U7

an2 in s e v enO ut(0:6 )

controldeanodos

U5

b inary in(3 :0 ) s e g 7o ut(0 :6 )

Display(0:6)

an3 in s e v enO ne (0:6 ) s e v e nT e n(0 :6 )

relojcontador U3

c lk inc ontad o r rs t d ig itO ne (3:0 ) d ig itT e n(3 :0 )

bcd7seg U6

b inary in(3 :0 ) s e g 7o ut(0 :6 )

mux7seg

Iniciar Pausar Continuar

s tart p aus e c o ntinue

bcd7seg

contador7seg

Cableado.bde

CONCLUSIN

Durante la realizacin de la prctica no se presentaron inconvenientes, fue finalizada correctamente a la primera, algo que pudimos notar es como se pueden usar condiciones de estado para elaborar sistemas ms complejos, y como se pueden facilitar la electrnica digital con la ayuda de la programacin en VHDL.

Vous aimerez peut-être aussi

- Jhon Roger Relaciones Amor Matrimonio y EspirituDocument238 pagesJhon Roger Relaciones Amor Matrimonio y Espirituleat2199Pas encore d'évaluation

- Recetas Flipantes Ebook4Document36 pagesRecetas Flipantes Ebook4Mario GlezPPas encore d'évaluation

- Pequenosheroes Joseymaria Copyright v52017Document11 pagesPequenosheroes Joseymaria Copyright v52017Grecia Jeronimo100% (2)

- Contador DijitalDocument10 pagesContador Dijitaltomkito100% (1)

- Informe 3Document23 pagesInforme 3Cristobal SolisPas encore d'évaluation

- Teoria Vincular Tesis Sonia Kleiman PDFDocument16 pagesTeoria Vincular Tesis Sonia Kleiman PDFMaria TricaricoPas encore d'évaluation

- Formato Caracterizacion para El EstudianteDocument4 pagesFormato Caracterizacion para El EstudianteYUDY VIVIANA OSPIANPas encore d'évaluation

- Inplementacion de MRPDocument56 pagesInplementacion de MRPCesar RamirezPas encore d'évaluation

- Modulación Banda Lateral Única (SSB)Document12 pagesModulación Banda Lateral Única (SSB)oscarlopezPas encore d'évaluation

- Lab4 G7Document19 pagesLab4 G7Jhojan Mamani100% (1)

- Simulaciones de Amplitud Modulada en Matlab y SimulinkDocument5 pagesSimulaciones de Amplitud Modulada en Matlab y SimulinkCheylibeth OchoaPas encore d'évaluation

- Sistemas Digitales SecuencialesDocument15 pagesSistemas Digitales SecuencialesOvanio MolinaPas encore d'évaluation

- Display's BCD 7 y 16 SegmentosDocument5 pagesDisplay's BCD 7 y 16 SegmentosLuis Alberto SDPas encore d'évaluation

- Buena Idea para El ReporteDocument4 pagesBuena Idea para El ReporteAngel Montes de OcaPas encore d'évaluation

- Marquesina Con GalDocument2 pagesMarquesina Con GalJesus GarridoPas encore d'évaluation

- Diseño de Circuitos Combinacionales en VHDLDocument6 pagesDiseño de Circuitos Combinacionales en VHDLPablo PulachePas encore d'évaluation

- Codificadores y DecodificadoresDocument38 pagesCodificadores y Decodificadoreszoru_hatakePas encore d'évaluation

- Ejercicios Modulacion DigitalDocument2 pagesEjercicios Modulacion DigitalAndres Rich ValenzuelaPas encore d'évaluation

- Actividades de CircuitosDocument1 pageActividades de CircuitosAndrea GarciaPas encore d'évaluation

- Cronómetro DigitalDocument7 pagesCronómetro DigitalJhoselyn Pamela GuachaminPas encore d'évaluation

- Clase 6. ADC y MemoriaDocument13 pagesClase 6. ADC y MemoriaSergio GuerreroPas encore d'évaluation

- Tutorial Básico de Uso de VivadoDocument12 pagesTutorial Básico de Uso de VivadoAngel YaaelPas encore d'évaluation

- Practica6 Organización y Arquitectura de ComputadorasDocument17 pagesPractica6 Organización y Arquitectura de ComputadorasEduardo RojasPas encore d'évaluation

- Taller Gnuradio-FskDocument8 pagesTaller Gnuradio-FskAdriana Marcela Quintero VasquezPas encore d'évaluation

- 2 - Ucpic18f2550 2017Document37 pages2 - Ucpic18f2550 2017hipolitoPas encore d'évaluation

- Divisor de Frecuencia y Contador de RizoDocument2 pagesDivisor de Frecuencia y Contador de RizoEddy Fernando Queca CadizPas encore d'évaluation

- Display de 7 Segmentos y Contador Del 0 Al 9Document5 pagesDisplay de 7 Segmentos y Contador Del 0 Al 9Hévy PsicodeliaPas encore d'évaluation

- Circuitos Digitales SecuencialesDocument7 pagesCircuitos Digitales SecuencialesJose Martinez EstradaPas encore d'évaluation

- LABORATORIO 05 - 2 Contadores AsincronosDocument5 pagesLABORATORIO 05 - 2 Contadores AsincronosDarwin YoverdPas encore d'évaluation

- Balotario Capitulo 7Document2 pagesBalotario Capitulo 7Rosmery MilagrosPas encore d'évaluation

- Manipulacion de Puertos en Lenguaje CDocument12 pagesManipulacion de Puertos en Lenguaje CSalvador Soria SalgadoPas encore d'évaluation

- 8255 PDFDocument17 pages8255 PDFAliangie Valeria ZambranoPas encore d'évaluation

- Lab1 IEEEDocument6 pagesLab1 IEEEJhulian VillafuertePas encore d'évaluation

- Informe 1 PotenciaDocument3 pagesInforme 1 PotenciaDanny MantillaPas encore d'évaluation

- Equipo Gris - Proyecto Final (Cronómetro)Document13 pagesEquipo Gris - Proyecto Final (Cronómetro)Mario DxPas encore d'évaluation

- Ensamblador Basico 2Document31 pagesEnsamblador Basico 2david morales rodriguezPas encore d'évaluation

- LAB. 07 - Arreglos - VenturaDocument6 pagesLAB. 07 - Arreglos - VenturaJoaquin OtreraPas encore d'évaluation

- Sistema Sumador y Comparador de 4 BitsDocument10 pagesSistema Sumador y Comparador de 4 BitsOscar Ortiz PérezPas encore d'évaluation

- Practica#1 Com2 Codificacion de Señales DigitalesDocument13 pagesPractica#1 Com2 Codificacion de Señales DigitalesFerdyc1991Pas encore d'évaluation

- Practica 5. Codificador de BCD A Codigo GrayDocument8 pagesPractica 5. Codificador de BCD A Codigo GrayJorge VargasPas encore d'évaluation

- 4.5.1 Observación de TCP y UDP Utilizando NetstatDocument9 pages4.5.1 Observación de TCP y UDP Utilizando NetstatalejoneyPas encore d'évaluation

- Contador 7490 y Decodificador 7447 PracticaDocument3 pagesContador 7490 y Decodificador 7447 Practicavictormorales21Pas encore d'évaluation

- Ejercicio de Sistemas Digitales IIDocument29 pagesEjercicio de Sistemas Digitales IIJose Cueva TumbacoPas encore d'évaluation

- Comunicacion Serial SincronaDocument24 pagesComunicacion Serial Sincronaandres8179Pas encore d'évaluation

- Codigos de ArduinoDocument8 pagesCodigos de ArduinoruthPas encore d'évaluation

- Practica 5 Diseño Digital ModernoDocument8 pagesPractica 5 Diseño Digital ModernoSuárez Hernández Sara AmalinaliPas encore d'évaluation

- Pre Informe Lab 1teleDocument9 pagesPre Informe Lab 1teleAngela María Cordero CondePas encore d'évaluation

- Circuito de Luces DireccionalesDocument3 pagesCircuito de Luces DireccionalesAdelaagaPas encore d'évaluation

- Proyecto c1 181Document3 pagesProyecto c1 181Emily LopezPas encore d'évaluation

- Registros - Previo 3Document22 pagesRegistros - Previo 3César Guerrero CornePas encore d'évaluation

- La Transformada Z FormulasDocument4 pagesLa Transformada Z FormulasEdgar MojicaPas encore d'évaluation

- Ejercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialDocument7 pagesEjercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialWilmer Villegas CodenaPas encore d'évaluation

- Primer Examen Parcial de Microprocesadores IDocument3 pagesPrimer Examen Parcial de Microprocesadores IGustavoPaolo MaldonadoCallisaya100% (1)

- Labo3 Tele2Document8 pagesLabo3 Tele2Cesar Terrazas VillarroelPas encore d'évaluation

- Reloj DigitalDocument18 pagesReloj DigitalRuben PadillaPas encore d'évaluation

- Problema 1Document2 pagesProblema 1Saucito Teocaltiche MXPas encore d'évaluation

- MODULO Uc 1Document43 pagesMODULO Uc 1piero100% (1)

- Clase Practica - Unidad IiDocument3 pagesClase Practica - Unidad IiAder Hariel Treminio MontoyaPas encore d'évaluation

- Cerradura ElectronicaDocument12 pagesCerradura ElectronicaPablo CaquiPas encore d'évaluation

- PRACTICA 1 LaboratorioDigitalDocument23 pagesPRACTICA 1 LaboratorioDigitalRonald Molina FariasPas encore d'évaluation

- Redes de ComputadorasDocument28 pagesRedes de ComputadorasMV OrchestratorPas encore d'évaluation

- Circuitos Digitales 01.07Document7 pagesCircuitos Digitales 01.07Geraldine GutierrezPas encore d'évaluation

- Manejo de Temporizadores AVRDocument17 pagesManejo de Temporizadores AVRrickypina0% (1)

- Generador de Ondas Cuadradas para ArduinoDocument2 pagesGenerador de Ondas Cuadradas para ArduinoPierDonneePas encore d'évaluation

- Practica 7 (Maquina de Estado Finito) PDFDocument7 pagesPractica 7 (Maquina de Estado Finito) PDFLeonardo Mora100% (1)

- Prob DiversosDocument14 pagesProb DiversosLeslie_g_mPas encore d'évaluation

- Actividad 1 U-III. Introducción A Los Convertidores CD-CDDocument1 pageActividad 1 U-III. Introducción A Los Convertidores CD-CDLeonardo MoraPas encore d'évaluation

- Practica 1 Solo CurvasDocument4 pagesPractica 1 Solo CurvasLeonardo MoraPas encore d'évaluation

- Actividad 1 U-III. Introducción A Los Convertidores CD-CDDocument1 pageActividad 1 U-III. Introducción A Los Convertidores CD-CDLeonardo MoraPas encore d'évaluation

- Servicio Editable TerminadoDocument14 pagesServicio Editable TerminadoLeonardo MoraPas encore d'évaluation

- U3, Act. 1 Introducción A Circuitos Trocedores PDFDocument10 pagesU3, Act. 1 Introducción A Circuitos Trocedores PDFLeonardo MoraPas encore d'évaluation

- U4, Actividad 1. Introducción A Los Circuitos Inversores (CD-CA)Document5 pagesU4, Actividad 1. Introducción A Los Circuitos Inversores (CD-CA)Leonardo MoraPas encore d'évaluation

- Guia LecturaDocument78 pagesGuia Lecturavany_062310Pas encore d'évaluation

- DEFINICIONESDocument9 pagesDEFINICIONESLeonardo MoraPas encore d'évaluation

- Instrumentacion ImprimirDocument18 pagesInstrumentacion ImprimirLucia Morales MoncadaPas encore d'évaluation

- Mapa PotenciaDocument3 pagesMapa PotenciaLeonardo MoraPas encore d'évaluation

- Practica 1 (El Analizador de Espectros)Document8 pagesPractica 1 (El Analizador de Espectros)Leonardo MoraPas encore d'évaluation

- 3.-Procesador RISC ExpoDocument10 pages3.-Procesador RISC ExpoLeonardo MoraPas encore d'évaluation

- Portada IndividualDocument2 pagesPortada IndividualLeonardo MoraPas encore d'évaluation

- Practica 8 (Distorsion Armonica)Document3 pagesPractica 8 (Distorsion Armonica)Leonardo MoraPas encore d'évaluation

- Sumador Multiplexor Paralelo SerieDocument7 pagesSumador Multiplexor Paralelo SerieLeonardo MoraPas encore d'évaluation

- Practica 11 (Return Loss)Document3 pagesPractica 11 (Return Loss)Leonardo MoraPas encore d'évaluation

- Reticula Ingenieria Electronica IELC-2010-211Document1 pageReticula Ingenieria Electronica IELC-2010-211Ludovico HernandezPas encore d'évaluation

- Problemas U2Document2 pagesProblemas U2Leonardo MoraPas encore d'évaluation

- Practica 1 (El Analizador de Espectros)Document8 pagesPractica 1 (El Analizador de Espectros)Leonardo MoraPas encore d'évaluation

- 1.-Exposicion Arquitectura HarvardDocument8 pages1.-Exposicion Arquitectura HarvardLeonardo MoraPas encore d'évaluation

- Arquitectura Von NewmannDocument14 pagesArquitectura Von NewmannLeonardo MoraPas encore d'évaluation

- Herramientas de DesarolloDocument9 pagesHerramientas de DesarolloLeonardo MoraPas encore d'évaluation

- Registro UniversalDocument10 pagesRegistro UniversalNathy NiamaPas encore d'évaluation

- Estructura Interna de Una AluDocument12 pagesEstructura Interna de Una AluLeonardo MoraPas encore d'évaluation

- Ejercicio 1 Anexo SemaforoDocument5 pagesEjercicio 1 Anexo SemaforoLeonardo MoraPas encore d'évaluation

- Como Personalizar Un Control (LabVIEW)Document4 pagesComo Personalizar Un Control (LabVIEW)Jaime Fuentes100% (2)

- Maquinas Electricas Cuestionario UNIDAD 1Document3 pagesMaquinas Electricas Cuestionario UNIDAD 1Leonardo Mora100% (1)

- Practica 10 (Reloj) (Leonardo MoraDocument9 pagesPractica 10 (Reloj) (Leonardo MoraLeonardo MoraPas encore d'évaluation

- Practica 10 (Reloj) (Leonardo MoraDocument9 pagesPractica 10 (Reloj) (Leonardo MoraLeonardo MoraPas encore d'évaluation

- Practica 10 (Reloj) (Leonardo MoraDocument9 pagesPractica 10 (Reloj) (Leonardo MoraLeonardo MoraPas encore d'évaluation

- Artrópodos Del SueloDocument4 pagesArtrópodos Del SueloElioGustavoCordobaPas encore d'évaluation

- Akron Gear Oil-1Document1 pageAkron Gear Oil-1Mario GonzalesPas encore d'évaluation

- Common RailDocument20 pagesCommon RailEnrique RodriguezPas encore d'évaluation

- Adolescentes RebeldesDocument2 pagesAdolescentes RebeldesAndres BurneoPas encore d'évaluation

- TERMINADO Antecedentes de La Globalización y Los Negocios InternacionalesDocument7 pagesTERMINADO Antecedentes de La Globalización y Los Negocios InternacionalesVale PortoPas encore d'évaluation

- Trabajo Tac. Gral.Document4 pagesTrabajo Tac. Gral.Aracely SandalioPas encore d'évaluation

- Informe Del Laboratorio de HidráulicaDocument5 pagesInforme Del Laboratorio de HidráulicaBernys AlvarezPas encore d'évaluation

- ALBAHACADocument8 pagesALBAHACAsocoPas encore d'évaluation

- Examen Final MTDDocument10 pagesExamen Final MTDAngelPas encore d'évaluation

- SHIPBROKERDocument7 pagesSHIPBROKERLilibeth MartínezPas encore d'évaluation

- Acabados ProyectoDocument18 pagesAcabados ProyectoEvaa C GuzmánPas encore d'évaluation

- Procesoso Tendencias de La EvolucionDocument3 pagesProcesoso Tendencias de La EvolucionSoco FloresPas encore d'évaluation

- Arduino DUE Enero2016 PDFDocument73 pagesArduino DUE Enero2016 PDFEdgarMartinezPas encore d'évaluation

- Instrucciones Tarea 3Document3 pagesInstrucciones Tarea 3profesorbenitorevecoPas encore d'évaluation

- Localizacio y PorcentajesDocument15 pagesLocalizacio y PorcentajesClaudia FranciscaPas encore d'évaluation

- Etapa Ejecución y Seguimiento de ProyectosDocument38 pagesEtapa Ejecución y Seguimiento de ProyectosAntonellaPas encore d'évaluation

- Análisis de La Novela Pedro Páramo de Juan RulfoDocument8 pagesAnálisis de La Novela Pedro Páramo de Juan RulfoAnaPas encore d'évaluation

- Terminos de Referencia Conciliaciones Bancarias.Document2 pagesTerminos de Referencia Conciliaciones Bancarias.jose angel castillo riosPas encore d'évaluation

- Semana 31 Cuento La Hormiga Desobediente - Inicial 3 - 4 - 5 AñosDocument5 pagesSemana 31 Cuento La Hormiga Desobediente - Inicial 3 - 4 - 5 AñosJoel Medina100% (1)

- El Problema Alimentario en Colombia: Absalón MachadoDocument142 pagesEl Problema Alimentario en Colombia: Absalón Machadodavi coloradoPas encore d'évaluation

- Valoración de Dos Sistemas Acuapónicos para El Cultivo de FresaDocument78 pagesValoración de Dos Sistemas Acuapónicos para El Cultivo de FresaBramyer Rafael Arias PortilloPas encore d'évaluation

- Ejercicios Reales BT3 2018Document7 pagesEjercicios Reales BT3 2018Vsm Hns GlsPas encore d'évaluation

- UCAL DERE - Iluminación Residencial - Trabajo Práctico - Avance 1 - 2023-10Document7 pagesUCAL DERE - Iluminación Residencial - Trabajo Práctico - Avance 1 - 2023-10Daniela Alejandra Eslava UrbinaPas encore d'évaluation