Académique Documents

Professionnel Documents

Culture Documents

Lab1 - Diana C. Meneses M. Cod - 2100756

Transféré par

D Carolina MenesesTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Lab1 - Diana C. Meneses M. Cod - 2100756

Transféré par

D Carolina MenesesDroits d'auteur :

Formats disponibles

CURSO DE ELECTRONICA DIGITAL GRUPO 51 OPERADORES LGICOS CON TECNOLOGAS TTL Y CMOS. Diana Carolina Meneses Muoz (krolinaek@gmail.

com) DEPARTAMENTO DE AUTOMATICA Y ELECTRONICA UNIVERSIDAD AUTNOMA DE OCCIDENTE 1. INTRODUCCION. El objetivo de este laboratorio es conocer e identificar las caractersticas de las familias lgicas usadas en el desarrollo de circuitos electrnicos digitales. 2. CONCEPTOS PREVIOS. - Qu es una Familia Lgica? Una familia lgica es un conjunto de circuitos integrados que implementan distintas operaciones lgicas, se comparte la tecnologa de fabricacin y presentan caractersticas similares en las entradas, salidas y circuitos internos. Tomando en cuenta el tipo de transistores utilizados en conmutacin las familias lgicas se dividen en dos grandes grupos: las que utilizan transistores bipolares y las que emplean transistores MOS. - Operadores Lgicos. Muy utilizados en Informtica, Lgica proposicional y lgebra booleana, entre otras disciplinas. Los operadores lgicos son lo que proporcionan un resultado a partir de que se cumpla o no una cierta condicin. Esto genera una serie de valores que, en los casos ms sencillos, pueden ser representados con los valores numricos 0 y 1. La combinacin de dos o ms operadores lgicos conforma una funcin lgica. - Margen de ruido Noise Margin. El margen de ruido en un circuito digital es definido como cualquier alteracin no deseada de las magnitudes elctricas (tensin o intensidad) en una seal digital. - Qu es fan-out? Es el denominado mximo nmero de entradas (denominadas cargas) que se pueden conectar a una lnea de salida. 3. DESCRIPCION DE LOS ELEMENTOS ELECTRICOS. SN7409: Cudruple de 2 entradas de puerta positiva, AND, con salida de colector abierto. Este dispositivo contiene cuatro de 2 entradas independientes como puertas And. El colector abierto de la salida requiere una resistencia de Pull-up para operar de forma correcta. Pueden estar conectados a otro colector abierto e implementar una funcin de actividad baja en OR o una actividad alta en AND. El dispositivo de colector abierto es usado a menudo para generar altos niveles de VOH. El SN7409, se caracteriza por operar dentro de un rango de temperatura militar de: 0C a 70 C. CD4011B: Esta compuerta es una monoltica complementaria de la familia MOS con circuitos integrados (CMOS), construido con transistores de canal tipo N y tipo P mejorados. Tiene capacidad de igualdad en las fuentes de voltaje y corriente conforme a la salida B en serie Los dispositivos tambin tienen buffers de salida el cual mejora la caracterstica de transferencia y provee una alta ganancia. Todas las entradas estn protegidas contra las descargas estticas con diodos a VDD y VSS. Esta compuerta tiene baja compatibilidad con la familia TTL. Los rangos de voltaje paramtricos son 5 V10V-15V. Caracterstica de salida simtrica. Mxima entrada de fuga 1A a 15V en un rango de temperatura mxima. 4. RESULTADOS DIAGRAMAS ELECTRICOS Y SIMULACIONES. a. A qu familia lgica pertenece? SN7409 Pertenece a la familia TTL (Transistor Transistor Logic) CD4011B Tecnologa CMOS: Lgica MOS

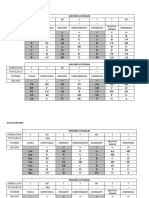

b. Qu operacin lgica se ha implementado? Compruebe. La operacin lgica que se ha implementado para el Sn7409 es la And y para comprobar que es una And se realiz la siguiente operacin y para la CD 4011B es una Nand:

c. Verifique cual es el rango para los niveles lgicos de entrada. Los trminos utilizados para designar el rango de niveles lgicos son los siguientes: SN7409 VIH(min) 1 lgico: 2 v. VIL(max) 0 lgico: 0,8 v. CD4011B VIH(min) 1 lgico: 3,5 v. VIL(max) 0 lgico: 1,5 v.

SN7409 LSNM = 0,4 V

CD4011B LSNM = 1,45 V

g. Que Fan-out puede manejar? (Explique). Para calcular el fan-out, debe ser el cociente entre las corrientes de salida y entrada para cada nivel lgico.

|| | | | | | | |

d. Verifique cual es el rango para los niveles lgicos de salida. El rango de los niveles lgicos para la salida es: SN7409 VoH(min): 5,5 V. VoL(max):0,4 v. CD4011B VoH(min): 4,95 V. VoL(max):0,05 v.

SN7409 Corrientes de IIH= 40A ; IIL= salida y 1,6 mA IOH = entrada para 0,25 mA ; IOL = los niveles 16 mA lgicos NH 6,25 NL 10 Fan out 6,25

CD4011B IIH= -0,10 A ; IIL= 0,25 A IOH = -0,88 mA ; IOL = 0,88 mA 8,80E+03 3520 3520

e. Explique y calcule el margen de ruido en estado alto. Si la amplitud del ruido est por encima de unos lmites definidos, denominados mrgenes de ruido, puede provocar que la seal este fuera de los niveles de tensin permitidos, por lo que se podra interpretar un nivel alto cuando debera ser un nivel bajo. La formula para definir este margen de ruido es la siguiente:

SN7409 HSNM = 3,5 V

CD4011B HSNM = 1,45 V

h. Qu tipo de compuertas lgicas son sensibles a la electricidad esttica y Por qu? Las familias lgicas MOS son especialmente susceptibles a daos por carga electrosttica. Esto es consecuencia directa de la alta impedancia de entrada de estos CI. Una pequea carga electrosttica que circule por estas altas impedancias puede dar origen a voltajes peligrosos. Los CMOS estn protegidos contra dao por carga esttica mediante la inclusin en sus entradas de diodos zner de proteccin. Diseados para conducir y limitar la magnitud del voltaje de entrada a niveles muy inferiores a los necesarios para provocar dao. Si bien los zner por lo general cumplen con su finalidad, algunas veces no comienzan a conducir con la rapidez necesaria para evitar que el CI sufra daos. i. Para qu se utilizan las resistencias PullUp y Pulldown en las entradas de las compuertas CMOS? Las resistencias de pull-up se conectan de una entrada o salida digital a Vcc, las de pull-down de una entrada o salida digital a masa (referencia). Esto se hace con el objetivo de evitar niveles de voltajes que caen en el rango indefinido, o respuestas no deseadas. Por tanto, las de pull-up fijan un 1 lgico y las de pulldown un cero lgico.

f. Explique y calcule el margen de ruido en estado bajo. Si la amplitud del ruido est por debajo de unos lmites definidos, puede provocar que la seal este fuera de los niveles de tensin permitidos, por lo que se pudiera interpretar un nivel bajo cuando debera ser un nivel alto.

j. En cul tipo de las familias lgicas citadas, las compuertas disipan menos potencia y por qu? Las familias que disipan menos potencia son las CMOS porque: Cuando la tensin entre drenador y fuente supera cierto lmite, el canal de conduccin bajo la puerta(Gate) sufre un estrangulamiento en las cercanas del drenador(Drain) y desaparece. La corriente entre fuente y drenador no se interrumpe, ya que es debido al campo elctrico entre ambos, pero se hace independiente de la diferencia de potencial entre ambos terminales.

operacin va desde: en Alta velocidad de operacin, pueden trabajar con un rango de 18 a 20 MHz y en algunas veces hasta 80 MHz y 250MHZ. Y en los CMOS es un rango de operacin solamente hasta los 50Mhz. Es mayor en los TTL porque La disipacin de potencia de un CI CMOS ser muy baja mientras est en una condicin dc. Desafortunadamente, PD siempre crecer en proporcin a la frecuencia en la cual los circuitos cambian de estado.

Mientras que en un transistor BJT cuando se utiliza como interruptor o switch, la corriente de base debe tener un valor para lograr que el transistor entre en corte y otro para que entre en saturacin.

Esto quiere decir que cuando la frecuencia es alta, el CMOS comienza a perder algunas de sus ventajas sobre otras familias lgicas. Como regla general, una compuerta CMOS tendr el mismo PD en promedio que una compuerta 74LS en frecuencias alrededor de cerca dc 2 a 3 MHz. n. Deduzca, calcule o mida la impedancia de entrada. Para calcular la impedancia de entrada en un circuito se realiza un thevenin en la entrada del circuito y se mide la corriente de entrada del circuito, as teniendo la corriente de entrada, una fuente virtual y una carga podemos usar ley de ohm para medir la impedancia. o. Deduzca, calcule o mida la impedancia de salida. Para el clculo de la impedancia de salida colocamos una carga variable en el final nuestro circuito y hacemos caer el voltaje de salida a la mitad y medimos el valor de resistencia el cual nos dar el valor de la impedancia de salida. Diagramas Elctricos: Para la interpretacin de los diagramas se debe de tener en cuenta que 5V es un 1 lgico y que valores con y por debajo de los mA sern tomados como un 0 lgico. La siguiente tabla de verdad muestra el comportamiento de una compuerta AND, de acuerdo a esta tabla realizo las simulaciones de la compuerta Sn7409: A B S 0 0 0 0 1 0 1 0 0 1 1 1

Tabla No.1. Tabla de verdad compuerta AND.

k. En cul tipo de familias lgicas, las compuertas drenan menos corriente en la entrada y por qu? En las CMOS se drena menos corriente porque su entrada base (Gate) es de alta impedancia permitiendo que esta se pierda de las corrientes de Drain y source para entrar en Switch mientras que en un TTL la corriente de base debe tener un valor significativo para poder que el transistor entre colector emisor sea polarizado y pueda entrar en switch. l. En cul tipo de familias lgicas, es ms amplio el rango de voltaje de Alimentacin? El tipo de familia en el que es ms alto el rango de voltaje es el de los: CMOS. Los rangos de voltaje manejados por la familia TTL son: 4,75V - 5,25V. Y para la familia de los CMOS son: 3 a 15V. m. En cul tipo de familias lgicas, es ms amplio el rango de frecuencia de operacin y porque? El rango de frecuencias de operacin es ms amplio en las TTL su rango de frecuencias de

Cuando la entrada A=0 y B= 0, la salida debe ser igual a 0:

Cuando la entrada A= 1 y B= 1, la salida debe ser igual a 1:

Fig.1. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 0 y B= 0.

Fig.4. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 1 y B= 1.

Cuando la entrada A= 0 y B= 1, la salida debe ser igual a 0:

La siguiente tabla de verdad muestra el comportamiento de una compuerta NAND, de acuerdo a esta tabla realizo las simulaciones de la compuerta CD4011B: A 0 0 1 1 B 0 1 0 1 S 1 1 1 0

Tabla No.2. Tabla de verdad compuerta NAND.

Cuando la entrada A=0 y B= 0, la salida debe ser igual a 1:

Fig.2. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 0 y B= 1.

Cuando la entrada A= 1 y B= 0, la salida debe ser igual a 0:

Fig.5. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 0 y B=0.

Fig.3. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 1 y B= 0.

5. Cuando la entrada A=0 y B= 1, la salida debe ser igual a 1:

Conclusiones

Se reconoci la principal aplicacin de las configuraciones en triestado que es la construccin de buses de comunicacin en los que cada puerta deposita la informacin de manera aleatoria y nunca se deben habilitar dos puertas al mismo tiempo ya que ello provocara un problema o error. Se logr identificar a las diferentes familias lgicas que existen para la construccin de circuitos digitales con sus principales caractersticas. Se recordaron conceptos vistos en semestres anteriores y se reconoci la importancia de tener un buen concepto en el funcionamiento de impedancias y caractersticas de dispositivos anlogos. 6. Referencia bibliogrfica.

Fig.6. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 0 y B=1.

Cuando la entrada A=1 y B= 0, la salida debe ser igual a 1:

http://www.uhu.es/raul.jimenez/DIGIT

AL_I/dig1_vii.pdf

http://www.fceia.unr.edu.ar/eca1/files/

teorias/Familias_logicas-2009.pdf

http://pdf1.alldatasheet.com/datasheet

-pdf/view/27354/TI/SN7409.html

http://pdf1.alldatasheet.com/datasheet

-pdf/view/26843/TI/CD4011B.html

http://www.uned.es/ca-

bergara/ppropias/Morillo/web_et_dig/03_ fam_log_ttl/transp_fam_logi_ttl.pdf

Fig.7. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 1 y B=0.

Cuando la entrada A=1 y B= 1, la salida debe ser igual a 0:

Fig.8. Diagrama elctrico y simulacin compuerta Sn7409 con entradas A= 1 y B=1.

Vous aimerez peut-être aussi

- Maquinaria PlantaDocument2 pagesMaquinaria PlantaD Carolina MenesesPas encore d'évaluation

- MM TONOSDocument5 pagesMM TONOSD Carolina MenesesPas encore d'évaluation

- Inventario Archivo Mtto 2020Document6 pagesInventario Archivo Mtto 2020D Carolina Meneses0% (1)

- ARCHIVODocument22 pagesARCHIVOD Carolina MenesesPas encore d'évaluation

- 10 - Arquitectura de ProductosDocument52 pages10 - Arquitectura de ProductosD Carolina MenesesPas encore d'évaluation

- Rotativa 4Document6 pagesRotativa 4D Carolina MenesesPas encore d'évaluation

- PlanosDocument25 pagesPlanosD Carolina MenesesPas encore d'évaluation

- Acker PlaceDocument1 pageAcker PlaceD Carolina MenesesPas encore d'évaluation

- ControlableDocument2 pagesControlableD Carolina MenesesPas encore d'évaluation

- Controlador Neuro Fuzzy para El Sistema de Bola y BarraDocument6 pagesControlador Neuro Fuzzy para El Sistema de Bola y BarraD Carolina MenesesPas encore d'évaluation

- Ejercicios DedosDocument2 pagesEjercicios DedosD Carolina MenesesPas encore d'évaluation

- Te NecesitoDocument1 pageTe NecesitoD Carolina Meneses50% (2)

- Sin Ti La LeyDocument1 pageSin Ti La LeyD Carolina MenesesPas encore d'évaluation

- Ensayo de PolimerosDocument4 pagesEnsayo de PolimerosD Carolina MenesesPas encore d'évaluation

- Lab 1 MaterialesDocument8 pagesLab 1 MaterialesD Carolina MenesesPas encore d'évaluation

- Quan CerDocument2 pagesQuan CerD Carolina MenesesPas encore d'évaluation

- Punto 2 en Command Window de MatlabDocument7 pagesPunto 2 en Command Window de MatlabD Carolina MenesesPas encore d'évaluation

- Tabla de Sobreimpluso Contra Factor de AmortiguamientoDocument1 pageTabla de Sobreimpluso Contra Factor de AmortiguamientoD Carolina MenesesPas encore d'évaluation

- Procesos CementoDocument5 pagesProcesos CementoD Carolina MenesesPas encore d'évaluation

- Propiedades Opticas de Los MaterialesDocument23 pagesPropiedades Opticas de Los MaterialesD Carolina MenesesPas encore d'évaluation

- Propiedades Opticas de Los MaterialesDocument23 pagesPropiedades Opticas de Los MaterialesD Carolina MenesesPas encore d'évaluation

- Presentaciones Efectivas EducacionDocument24 pagesPresentaciones Efectivas EducacionD Carolina MenesesPas encore d'évaluation

- Lab1 CompletoDocument5 pagesLab1 CompletoD Carolina MenesesPas encore d'évaluation

- Campo MagneticoDocument8 pagesCampo MagneticoAndres MeraPas encore d'évaluation

- Taller 1 2015 IIDocument2 pagesTaller 1 2015 IID Carolina MenesesPas encore d'évaluation

- CulombDocument9 pagesCulombD Carolina MenesesPas encore d'évaluation

- Fa-124 SDocument0 pageFa-124 SEnrique NavaPas encore d'évaluation

- Alternativa para La Demanda Hidrica de La Ciudad de Cali Valle Del CaucaDocument9 pagesAlternativa para La Demanda Hidrica de La Ciudad de Cali Valle Del CaucaD Carolina MenesesPas encore d'évaluation

- Act I Vida Des Complement Aria Su 3Document15 pagesAct I Vida Des Complement Aria Su 3D Carolina MenesesPas encore d'évaluation

- Joe Dominguez Vicki Robin La Bolsa O La Vida PDFDocument137 pagesJoe Dominguez Vicki Robin La Bolsa O La Vida PDFseodavisPas encore d'évaluation

- Informe de Laboratorio 4Document10 pagesInforme de Laboratorio 4Andrey LopezPas encore d'évaluation

- Modasa Grupos ElectrogenosDocument2 pagesModasa Grupos Electrogenosasc99Pas encore d'évaluation

- Capacidad EléctricaDocument15 pagesCapacidad Eléctricachichis1Pas encore d'évaluation

- PT Hamilton 2Document4 pagesPT Hamilton 2Nerida Cecilia Rocha CorreaPas encore d'évaluation

- Hidroelectricidad 1Document26 pagesHidroelectricidad 1Ingenieria TotalPas encore d'évaluation

- Problemas de Intensidad de Campo Eléctrico (Practicas)Document3 pagesProblemas de Intensidad de Campo Eléctrico (Practicas)esteban40% (5)

- Guia 3 Amplificadores OperacionalesDocument5 pagesGuia 3 Amplificadores OperacionalesAlex GonzálezPas encore d'évaluation

- AAGL - Practica #3 - LabME (1985208)Document13 pagesAAGL - Practica #3 - LabME (1985208)Aaron Alejandro Garcia LopezPas encore d'évaluation

- Manta TermicaDocument2 pagesManta TermicaDANIEL IGNACIOPas encore d'évaluation

- Proforma PR00017-2020 - Levantamiento Obs Taller - Rev.01Document4 pagesProforma PR00017-2020 - Levantamiento Obs Taller - Rev.01Rodolfo Elias Castillo Vigo100% (1)

- Circuitos RLC PDFDocument9 pagesCircuitos RLC PDFMaxidvpPas encore d'évaluation

- Practica 6 EB Grupo 4 PDFDocument5 pagesPractica 6 EB Grupo 4 PDFAlexis CastroPas encore d'évaluation

- UNIDAD III Elementos de Las Instalaciones EléctricasDocument25 pagesUNIDAD III Elementos de Las Instalaciones EléctricasJosue ValenciaPas encore d'évaluation

- Práctica 2 Redes Inalambricas - Romero Zavala EdwardDocument7 pagesPráctica 2 Redes Inalambricas - Romero Zavala EdwardEDWARD AARON ROMERO ZAVALAPas encore d'évaluation

- 2.ejercicios Evaluacion 2Document2 pages2.ejercicios Evaluacion 2CJ JchuraPas encore d'évaluation

- Informe Final 1Document8 pagesInforme Final 1Javier Aldo Yataco CéspedesPas encore d'évaluation

- Examen FinalDocument19 pagesExamen FinalMiguel RomeroPas encore d'évaluation

- Arteche CT CX EsDocument4 pagesArteche CT CX EsFernandoPas encore d'évaluation

- Electricidad y Electronica BasicaDocument4 pagesElectricidad y Electronica BasicaWilber Aldair AlegríaPas encore d'évaluation

- 4.formato RCM-AMEF-Sistema de Generacion-AerogeneradorDocument22 pages4.formato RCM-AMEF-Sistema de Generacion-AerogeneradorElvis Diaz100% (1)

- Triptico Bcos de Capacitores en BT Single Oct 2011Document6 pagesTriptico Bcos de Capacitores en BT Single Oct 2011Jose ManuelPas encore d'évaluation

- 8198 - Práctica 3° Parcial Grupo 8Document17 pages8198 - Práctica 3° Parcial Grupo 8ALEXANDER FABIAN GUAMAN QUINATOAPas encore d'évaluation

- Capitulo 7 - JfetDocument21 pagesCapitulo 7 - JfetCertus PC FloridaPas encore d'évaluation

- 5.1 Registro de PresionesDocument17 pages5.1 Registro de PresionesEverardoRamirezPas encore d'évaluation

- Hoja de Vida de Termometro - GMDDocument1 pageHoja de Vida de Termometro - GMDrenePas encore d'évaluation

- L1CC2EVAVDCDocument47 pagesL1CC2EVAVDCChristian ChalcoPas encore d'évaluation

- E5csv PDFDocument4 pagesE5csv PDFRick AvilPas encore d'évaluation

- Compensación Fija de Energía Reactiva en TransformadoresDocument4 pagesCompensación Fija de Energía Reactiva en TransformadoresRuben Guagnini100% (1)

- Corte, Protección y LEGRANDDocument54 pagesCorte, Protección y LEGRANDDavid Aquiles Oyarzún BahamondePas encore d'évaluation