Académique Documents

Professionnel Documents

Culture Documents

MP3389 r1.04

Transféré par

Andres AlegriaDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

MP3389 r1.04

Transféré par

Andres AlegriaDroits d'auteur :

Formats disponibles

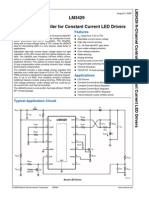

MP3389

12String, Step-up White LED Driver

The Future of Analog IC Technology

DESCRIPTION

The MP3389 is a step-up controller with 12channel current sources designed for driving the WLED arrays for large size LCD panel backlighting applications. The MP3389 uses current mode, fixed frequency architecture. The switching frequency is programmable by an external frequency setting resistor. It drives an external MOSFET to boost up the output voltage from a 5V to 28V input supply. The MP3389 regulates the current in each LED string to the programmed value set by an external current setting resistor. The MP3389 applies 12 internal current sources for current balance. And the current matching can achieve 2.5% regulation accuracy between strings. Its low 550mV regulation voltage on LED current sources reduces power loss and improves efficiency. PWM dimming is implemented with external PWM input signal or DC input signal. The dimming PWM signal can be generated internally, and the dimming frequency is programmed by an external setting capacitor.

FEATURES

High Efficiency and Small Size 5V to 28V Input Voltage Range Balanced Driver for 12 Strings of WLEDs Maximum 60mA for Each String 2.5% Current Matching Accuracy Between Strings Programmable Switching Frequency PWM or DC Input Burst PWM Dimming Open and Short LED protection Programmable Over-voltage Protection Under Voltage Lockout Thermal Shutdown 28-pin TSSOP and 28-pin SOIC Package Desktop LCD Flat Panel Displays Flat Panel Video Displays LCD TVs and Monitors

APPLICATIONS

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. MPS and The Future of Analog IC Technology are Registered Trademarks of Monolithic Power Systems, Inc.

TYPICAL APPLICATION

M1 L1 D1 COUT

VIN 5V~28V

CIN

R1

2 VIN VFAULT 27

CVCC C COMP RCOMP

R2

3 VCC GATE 26

M2

COMP

ISENSE

24

Enable

R OSC

VCC

EN

NC

28

RSENSE

OSC

PGND

25

NC

OVP

23

10

BOSC

RBOSC

C BOSC

7 GND

MP3389

LED1

22

LED2

21

DIMMING

RSET

DBRT

LED3

20

ISET

LED4

19

11

LED12

LED5

18

12

LED11

LED6

17

13

LED10

LED7

16

14

LED9

LED8

15

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

ORDERING INFORMATION

Part Number* MP3389EF MP3389EY Package TSSOP28 SOIC28 Top Marking 3389EF 3389EY

*For Tape & Reel, add suffix Z (eg. MP3389EFZ). For RoHS compliant packaging, add suffix LF (eg. MP3389EFLFZ) **For Tape & Reel, add suffix Z (eg. MP3389EYZ). For RoHS compliant packaging, add suffix LF (eg. MP3389EYLFZ)

PACKAGE REFERENCE

TOP VIEW

NC VIN VCC COMP EN DBRT GND OSC ISET BOSC LED12 LED11 LED10 LED9 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 NC VFAULT GATE PGND ISENSE OVP LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8

TSSOP28

SOIC28

ABSOLUTE MAXIMUM RATINGS (1)

VIN .................................................-0.3V to +30V VVFAULT ........................................... VIN - 6V to VIN VGATE ..............................................-0.5V to 6.3V VLED1 to VLED12 ..................................-1V to +50V All Other Pins ...............................-0.3V to +6.3V (2) Continuous Power Dissipation (TA = +25C) TSSOP28 ...3.9W SOIC28 ...2.1W Junction Temperature ...............................150C Lead Temperature ....................................260C Storage Temperature............... -65C to +150C

Thermal Resistance

(4)

JA

JC

TSSOP28 ................................32 ....... 6 .... C/W SOIC28 ..................................60 ...... 30 ... C/W

Notes: 1) Exceeding these ratings may damage the device. 2) The maximum allowable power dissipation is a function of the maximum junction temperature TJ (MAX), the junction-toambient thermal resistance JA, and the ambient temperature TA. The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) = (TJ (MAX)-TA)/JA. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage. 3) The device is not guaranteed to function outside of its operation conditions. 4) Measured on JESD51-7, 4-layer PCB.

Recommended Operating Conditions

(3)

Supply Voltage VIN ..............................5V to 28V LED Current (Backlight) .............10mA to 60mA Operating Junction Temp. (TJ). -40C to +125C

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

ELECTRICAL CHARACTERISTICS

VIN =12V, VEN = 5V, TA = +25C, unless otherwise noted.

Parameters Operating Input Voltage Supply Current (Quiescent) Supply Current (Shutdown) LDO Output Voltage Input UVLO Threshold Input UVLO Hysteresis EN High Voltage EN Low Voltage STEP-UP CONVERTER Gate Driver (Sourcing) Gate Driver (Sinking) Impedance Impedance fSW VOSC TON_MIN DMAX Max Duty Cycle

(6)

Symbol VIN IQ IST VCC VIN_UVLO VEN_HIGH VEN_LOW

Condition VIN=12V, VEN=5V, no load with switching VEN=0V, VIN=12V VEN=5V, 0<IVCC<10mA Rising Edge VEN Rising VEN Falling 6V<VIN<28V,

Min 4.5

Typ

Max 28

Units V mA

4 2 4.5 3.4 1.6 0.6 5 3.9 200 5.5 4.3

A V V mV V V

VCC=5V,VGATE=5V VCC=5V,IGATE=10mA ROSC= 115k ROSC= 374k PWM Mode, when no pulse skipping happens 90 175 530 160 1.18

4 2 590 180 1.23 100 650 200 1.28

kHz kHz V ns %

Switching Frequency OSC Voltage Minimum On Time Maximum Duty Cycle ISENSE Limit Leading Edge Blanking Time PWM DIMMING DBRT Leakage Current BOSC Frequency BOSC Output Current LED CURRENT REGULATION ISET Voltage LEDX Average Current Current Matching PROTECTION OVP Over Voltage Threshold

(5)

220 250

265

mV ns

TLEB

IDBRT_LK FBOSC IBOSC VISET ILED VLEDX VOVP_OV RISET=40k ILED=30.5mA ILED=30.5mA Rising Edge CBOSC=2.2nF

-5 1.2 6.37 1.20 29.6 410 1.20 1.6 7.5 1.22 30.5 550 1.23

+5 2 8.63 1.245 31.4 2.5 690 1.26

A kHz A V mA % mV V

LEDX Regulation Voltage

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

ELECTRICAL CHARACTERISTICS (continued)

VIN =12V, VEN = 5V, TA = +25C, unless otherwise noted.

Parameters OVP UVLO threshold LEDX Over Voltage Threshold LEDX UVLO Threshold Thermal Shutdown Threshold VFAULT Pull Down Current VFAULT Blocking-Off Voltage (with Respect to VIN) Symbol VOVP_UV VLEDX_OV VLEDX_UV TST IFAULT VFAULT VIN =12V, VIN-VFAULT 40 5.3 Condition Step-up Converter Fails VIN>5.5V Min 50 5.1 140 Typ 70 5.5 180 130 55 5.8 70 6.3 Max 90 5.9 220 Units mV V mV A V

Notes: 5) Matching is defined as the difference of the maximum to minimum current divided by 2 times average currents. 6) Guarantee by design.

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

PIN FUNCTIONS

Pin # 1 2 Name Description NC VIN No Connect. Supply Input. VIN supplies the power to the chip, as well as the step-up converter switch. Drive VIN with a 5V to 28V power source. Must be locally bypassed. The Internal 5V Linear Regulator Output. VCC provides power supply for the internal MOSFET switch gate driver and the internal control circuitry. Bypass VCC to GND with a ceramic capacitor. Step-up Converter Compensation Pin. This pin is used to compensate the regulation control loop. Connect a capacitor or a series RC network from COMP to GND. Enable Control Input. Do not let this pin floating.

VCC

4 5

COMP EN

Brightness Control Input. To use external PWM dimming mode, apply a PWM signal on this pin for brightness control. To use DC input PWM dimming mode, apply a DC voltage range from DBRT 0.2V to 1.2V on this pin linearly to set the internal dimming duty cycle from 0% to 100%. The MP3389 has positive dimming polarity on DBRT. GND OSC Analog Ground. Switching Frequency Set. Connect a resistor between OSC and GND to set the step-up converter switching frequency. The voltage at this pin is regulated to 1.23V. The clock frequency is proportional to the current sourced from this pin. LED Current Set. Tie a current setting resistor from this pin to ground to program the current in each LED string. The MP3389 regulates the voltage across the current setting resistor. The regulation voltage is 1.22V. The proportion of the current through the ISET resistor and the LED current is 1:1000.

7 8

ISET

10

Dimming Repetition Set. This is the timing pin for the oscillator to set the dimming frequency. To use DC input PWM dimming mode, connect a capacitor from this pin to GND to set the internal BOSC dimming frequency. A saw-tooth waveform is generated on this pin. To use external PWM dimming mode, connect a 100k resistor from this pin to GND, and apply the PWM signal on DBRT pin. LED String 12 Current Input. This pin is the open-drain output of an internal dimming control LED12 switch. Connect the LED String 12 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 11 Current Input. This pin is the open-drain output of an internal dimming control LED11 switch. Connect the LED String 11 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 10 Current Input. This pin is the open-drain output of an internal dimming control LED10 switch. Connect the LED String 10 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 9 Current Input. This pin is the open-drain output of an internal dimming control LED9 switch. Connect the LED String 9 cathode to this pin. If this string is not used, connect Vin to this pin.

11

12

13

14

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

PIN FUNCTIONS (continued)

Pin # 15 16 17 18 19 20 Name LED8 LED7 LED6 LED5 LED4 LED3 Description LED String 8 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 8 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 7 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 7 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 6 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 6 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 5 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 5 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 4 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 4 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 3 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 3 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 2 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 2 cathode to this pin. If this string is not used, connect Vin to this pin. LED String 1 Current Input. This pin is the open-drain output of an internal dimming control switch. Connect the LED String 1 cathode to this pin. If this string is not used, connect Vin to this pin. Over-voltage Protection Input. Connect a resistor divider from output to this pin to program the OVP threshold. When this pin voltage reaches 1.23V, the MP3389 triggers OV Protection mode. Current Sense Input. During normal operation, this pin senses the voltage across the external inductor current sensing resistor for peak current mode control and also to limit the inductor current during every switching cycle. Step-up Converter Power Ground. Step-up Converter Power Switch Gate Output. This pin drives the external power N-MOS device. Fault Disconnection Switch Gate Output. When the system starts up normally, this pin smoothly turns on the external PMOS. When the MP3389 is disabled, the external PMOS is turned off to disconnect the input and output. No Connect.

21

LED2

22

LED1

23

OVP

24 25 26 27 28

ISENSE PGND GATE VFAULT NC

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

TYPICAL PERFORMANCE CHARACTERISTICS

VIN =12V, 14 LEDs in series, 12 strings parallel, 20mA/string, unless otherwise noted.

Efficiency vs. Input Voltage

0.95 0.9

VSW 20V/div. VOUT (AC) 1V/div. VLED1 1V/div. ILED1 20mA/div. VOUT 20V/div. VIN 5V/div. ILED 200mA/div. VSW 20V/div.

Steady State

Vin Startup

EFFICIENCY

0.85 0.8 0.75 0.7

12 18 24 INPUT VOLTAGE (V)

30

Ven Startup

VSW 20V/div.

VSW 20V/div.

VSW 20V/div. VOUT 20V/div. VPWM1 5V/div. ILED 200mA/div.

VOUT 20V/div. VEN 5V/div. ILED 200mA/div.

VOUT 20V/div. VBOSC 500mV/div. ILED 200mA/div.

Open LED Protection

open all LED strings at working

Short LED Protection

short VOUT to LEDx at working

Short LED Protection

short VOUT to GND at working

VSW 20V/div.

VSW 20V/div.

VSW 20V/div. VOUT 50V/div.

VOUT 20V/div. VFAULT 5V/div. ILED 200mA/div.

VOUT 20V/div. VLED1 20V/div. ILED 100mA/div.

VFAULT 5V/div. ILED 200mA/div.

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

FUNCTION DIAGRAM

VCC VIN GND

Regulator

VFAULT

Control Logic

GATE

PWM Comparator

Current Sense Amplifier

+ -

ISENSE PGND

OV Comparator

OSC

Oscillator LED OV Comparator Short String Protection

+

+ -

OVP

1.23V

5.5V Max Feedback Control

COMP

Enable Control

EA

Min

600 mV

EN

LED1

+

1.22V

ISET

Current Control

BOSC

DPWM Oscillator DPWM Comparator

-

DBRT

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

LED12

Figure 1MP3389 Function Block Diagram

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

OPERATION

The MP3389 employs a programmable constant frequency, peak current mode step-up converter and 12-channels regulated current sources to regulate the array of 12 strings white LEDs. The operation of the MP3389 can be understood by referring to the block diagram of Figure 1. Internal 5V Regulator The MP3389 includes an internal linear regulator (VCC). When VIN is greater than 5.5V, this regulator offers a 5V power supply for the internal MOSFET switch gate driver and the internal control circuitry. The VCC voltage drops to 0V when the chip shuts down. In the application of VIN smaller than 5.5V, tie VCC and VIN together. The MP3389 features Under Voltage Lockout. The chip is disabled until VCC exceeds the UVLO threshold. And the hysteresis of UVLO is approximately 200mV. System Startup When the MP3389 is enabled, the chip checks the topology connection first. The VFAULT pin drives the external Fault Disconnection PMOS to turn on slowly. Then the chip monitors the OVP pin to see if the Schottky diode is not connected or the boost output is short to GND. If the OVP voltage is lower than 70mV, the chip will be disabled and the external PMOS is turned off together. The MP3389 will also check other safety limits, including UVLO and OTP after the OVP test is passed. If they are all in function, it then starts boosting the step-up converter with an internal soft-start. It is recommended on the start up sequence that the enable signal comes after input voltage and PWM dimming signal established. Step-up Converter The converter operation frequency is programmable (from 100kHz to 500kHz) with a external set resistor on OSC pin, which is helpful for optimizing the external components sizes and improving the efficiency. At the beginning of each cycle, the external MOSFET is turned with the internal clock. To prevent sub-harmonic oscillations at duty cycles greater than 50 percent, a stabilizing ramp is

added to the output of the current sense amplifier and the result is fed into the PWM comparator. When this result voltage reaches the output voltage of the error amplifier (VCOMP) the external MOSFET is turned off. The voltage at the output of the internal error amplifier is an amplified signal of the difference between the 550mV reference voltage and the feedback voltage. The converter automatically chooses the lowest active LEDX pin voltage for providing enough bus voltage to power all the LED arrays. If the feedback voltage drops below the 550mV reference, the output of the error amplifier increases. It results in more current flowing through the power FET, thus increasing the power delivered to the output. In this way it forms a close loop to make the output voltage in regulation. At light-load or Vout near to Vin operation, the converter runs into the pulse-skipping mode, the FET is turned on for a minimum on-time of approximately 100ns, and then the converter discharges the power to the output in the remain period. The external MOSFET will keep off until the output voltage needs to be boosted again. Dimming Control The MP3389 provides two PWM dimming methods: external PWM signal or DC input PWM Dimming mode (see Figure 2). Both methods results in PWM chopping of the current in the LEDs for all 12 channels to provide LED control.

Ex-PWM Input

DPWM Comparator

-

DPWM Output

DBRT

DPWM Oscillator C BOSC BOSC

Figure 2PWM Dimming Method When bias the BOSC pin to a DC level, applying a PWM signal to the DBRT pin to achieve the PWM dimming. A DC analog signal can be

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

directly applied to the DBRT pin to modulate the LED current. And the DC signal is then converted to a DPWM dimming signal at the setting oscillation frequency. The brightness of the LED array is proportional to the duty cycle of the DPWM signal. The DPWM signal frequency is set by the cap at the BOSC pin. Open String Protection The open string protection is achieved through the over voltage protection. If one or more strings are open, the respective LEDX pins are pulled to ground and the IC keeps charging the output voltage until it reach OVP threshold. Then the part will mark off the open strings whose LEDX pin voltage is less than 180mV. Once the markoff operation completes, the remaining LED strings will force the output voltage back into tight regulation. The string with the highest voltage drop is the ruling string during output regulation. The MP3389 always tries to light at least one string and if all strings in use are open, the MP3389 shuts down the step-up converter. The part will maintain mark-off information until the part shuts down. Short String Protection The MP3389 monitors the LEDX pin voltage to judge if the short string occurs. If one or more strings are short, the respective LEDX pins will be pulled up to the boost output and tolerate high voltage stress. If the LEDX pin voltage is higher than 5.5V, the short string condition is detected on the respective string. When the short string fault (LEDX over-voltage fault) continues for greater than 512 switching clocks, the string is marked off and disabled. Once a string is marked off, its current regulation is forced to disconnect from the output voltage loop regulation. The marked-off LED strings will be shut off totally until the part restarts. If all strings in use are short, the MP3389 will shut down the step-up converter.

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

10

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

APPLICATION INFORMATION

Selecting the Switching Frequency The switching frequency of the step-up converter is programmable from 100kHz to 500kHz. A oscillator resistor on OSC pin sets the internal oscillator frequency for the step-up converter according to the equation: fSW = 67850 / ROSCk For ROSC=191k, the switching frequency is set to 355 kHz. Setting the LED Current The LED string currents are identical and set through the current setting resistor on the ISET pin. ILED = 1000 x 1.22V / RSET For RSET=60.4k, the LED current is set to 20mA. The ISET pin can not be open. Selecting the Input Capacitor The input capacitor reduces the surge current drawn from the input supply and the switching noise from the device. The input capacitor impedance at the switching frequency should be less than the input source impedance to prevent high frequency switching current from passing through the input. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a 4.7F ceramic capacitor paralleled a 220uF electrolytic capacitor is sufficient. Selecting the Inductor and Current Sensing Resistor The inductor is required to force the higher output voltage while being driven by the input voltage. A larger value inductor results in less ripple current, resulting in lower peak inductor current and reducing stress on the internal N-Channel MOSFET. However, the larger value inductor has a larger physical size, higher series resistance, and lower saturation current. Choose an inductor that does not saturate under the worst-case load conditions. A good rule for determining the inductance is to allow the peakto-peak ripple current to be approximately 30% to 40% of the maximum input current. Calculate the required inductance value by the equation:

L= VIN (VOUT VIN ) VOUT fSW I

IIN(MAX) =

VOUT ILOAD(MAX) VIN

I = (30%~40%) IIN(MAX)

Where VIN is the minimum input voltage, fSW is the switching frequency, ILOAD(MAX) is the maximum load current, I is the peak-to-peak inductor ripple current and is the efficiency. The switch current is usually used for the peak current mode control. In order to avoid hitting the current limit, the voltage across the sensing resistor RSENSE should be less than 80% of the worst case current limit voltage, VSENSE.

RSENSE =

0.8 VSENSE IL(PEAK )

Where IL(PEAK) is the peak value of the inductor current. VSENSE is shown in Figure 3.

VSENSE vs. Duty Cycle

700 600 500 400 300 200 100 0 0 10 20 30 40 50 60 70 80 90 100 DUTY CYCLE (%)

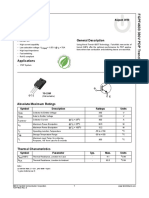

Figure 3VSENSE vs Duty Cycle Selecting the Power MOSFET The MP3389 is capable of driving a wide variety of N-Channel power MOSFETS. The critical parameters of selection of a MOSFET are: 1. Maximum drain to source voltage, VDS(MAX) 2. Maximum current, ID(MAX) 3. On-resistance, RDS(ON) 4. Gate source charge QGS and gate drain charge QGD

5.

Total gate charge, QG

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

11

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

Ideally, the off-state voltage across the MOSFET is equal to the output voltage. Considering the voltage spike when it turns off, VDS(MAX) should be greater than 1.5 times of the output voltage. The maximum current through the power MOSFET happens when the input voltage is minimum and the output power is maximum. The maximum RMS current through the MOSFET is given by

IRMS(MAX) = IIN(MAX) D MAX

For extended knowledge of the power loss estimation, readers should refer to the book Power MOSFET Theory and Applications written by Duncan A. Grant and John Gowar. The total gate charge, QG, is used to calculate the gate drive loss. The expression is

PDR = Q G VDR f SW

Where VDR is the drive voltage. Selecting the Output Capacitor The output capacitor keeps the output voltage ripple small and ensures feedback loop stability. The output capacitor impedance should be low at the switching frequency. Ceramic capacitors with X7R dielectrics are recommended for their low ESR characteristics. For most applications, a 4.7F ceramic capacitor paralleled 10uF electrolytic capacitor will be sufficient. Setting the Over Voltage Protection The open string protection is achieved through the over voltage protection (OVP). In some cases, an LED string failure results in the feedback voltage always zero. The part then keeps boosting the output voltage higher and higher. If the output voltage reaches the programmed OVP threshold, the protection will be triggered. To make sure the chip functions properly, the OVP setting resistor divider must be set with a proper value. The recommended OVP point is about 1.2 times higher than the output voltage for normal operation. VOVP=1.23V*(R1+R2)/R2 Selecting Dimming Control Mode The MP3389 provides 2 different dimming methods 1. Direct PWM Dimming An external PWM dimming signal is employed to achieve PWM dimming control. Connect a 100k resistor from BOSC pin to GND and apply the 100Hz to 2kHz PWM dimming signal to DBRT pin. The minimum recommended amplitude of the PWM signal is 1.2V. The low level should less than 0.4V. (See Figure 4).

Where:

D MAX VOUT VIN(MIN) VOUT

The current rating of the MOSFET should be greater than 1.5 times IRMS, The on resistance of the MOSFET determines the conduction loss, which is given by:

Pcond = IRMS

2

R DS (on) k

Where k is the temperature coefficient of the MOSFET. The switching loss is related to QGD and QGS1 which determine the commutation time. QGS1 is the charge between the threshold voltage and the plateau voltage when a driver charges the gate, which can be read in the chart of VGS vs. QG of the MOSFET datasheet. QGD is the charge during the plateau voltage. These two parameters are needed to estimate the turn on and turn off loss.

PSW Q RG = GS1 VDS IIN f SW + VDR VTH Q GD R G VDS IIN f SW VDR VPLT

Where VTH is the threshold voltage, VPLT is the plateau voltage, RG is the gate resistance, VDS is the drain-source voltage. Please note that the switching loss is the most difficult part in the loss estimation. The formula above provides a simple physical expression. If more accurate estimation is required, the expressions will be much more complex.

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

12

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

Layout Considerations Careful attention must be paid to the PCB board layout and components placement. Proper layout of the high frequency switching path is critical to prevent noise and electromagnetic interference problems. The loop of external MOSFET (M2), output diode (D1), and output capacitor (C5) is flowing with high frequency pulse current. it must be as short as possible (See Figure 6).

BOSC R1 100 k

MP3389

DBRT

PWM Dimming 100Hz~2kHz

Figure 4Direct PWM Dimming Table 1 shows the PWM dimming duty Range with different PWM dimming frequency. Tab 1 The Range of PWM Dimming Duty

fpwm(Hz) Dmin Dmax

100<f200 200<f500 500<f1k 1k<f2k 2k<f5k 5k<f10k 10k<f20k

0.30% 0.75% 1.50% 3.00% 7.50% 15.00% 30.00%

100% 100% 100% 100% 100% 100% 100%

2. DC Input PWM Dimming To apply DC input PWM dimming, apply an analog signal (range from 0.2 V to 1.2V) to the DBRT pin to modulate the LED current directly. If the PWM is applied with a zero DC voltage, the PWM duty cycle will be 0%. If the DBRT pin is applied with a DC voltage>1.2V, the output will be 100% (See Figure 5). The capacitor on BOSC pin set the frequency of internal triangle waveform according to the equation: FUNITE = 3.5F / CUNITE

BOSC C1

Figure 6Layout Consideration The IC exposed pad is internally connected to GND pin, and all logic signals are refer to the GND. The PGND should be externally connected to GND and is recommended to keep away from the logic signals. External MOSFET for Short Protection When output voltage is higher than rating of LED1-12 pins, external MOSFET is needed for each LED channel to avoid destroying LED1 -12 pins. (See Figure 8 for 4 channels application) The rating of MOSFET must be higher than 1.2* VOUT t and more than 1.2* ILED.

MP3389

DC Signal DBRT

Figure 5DC input PWM Dimming

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

13

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

TYPICAL APPLICATION CIRCUIT

8V-28V VIN

F1 C1 C2

NC

C3

M1

AM4499P

L1

D1

B180

C13

C16

14S 12P 20mA

LED+

C10 C17

5.6nF NC

R26

NC

LED1

R51

432k

GND

GND GND

R11

GND

R20

10

GND

C12

NC M2 AM4490N

GND

C15

GND

LED2 LED3 LED4 LED5 LED6 LED7 LED8

U1 R54

10k

3 VCC GATE 26 2 VIN VFAULT 27

R22

0

R53

10k

C14

100pF

LED9 LED10 LED11 LED12

C9

4

R1

COMP

ISENSE

24 GND

EN

2k

GND

100nF

C4

R15

0

5 EN NC 28

R24

0.05

R25

NC

R4

20k

C18 R13

191k

GND GND

OSC

PGND

25

GND 1 NC OVP 23

R27 0

10 BOSC LED1 22

R8

100k

C6

NC

GND 7 GND

MP3389

LED2

R28 0

21

R2

DIMMING

2k

NET00016

R29 0

6 DBRT LED3 20

R5

20k

GND

R16

60.4k

R30 0

9 ISET LED4 19

R31 0

11 LED12 LED5 18

GND 12 LED11 LED6 17

R32 0 R33 0

13 LED10 LED7 16

R34 0

14 LED9 LED8 15

R35 0 R36 0 R37 0 R38 0

Figure 7Drive 14 LEDs in Series, 12 Strings 20mA/string for Monitor Backlighting

8V-28V VIN

F1 C1 C2

NC

C3

M1

AM4499P

L1

D1

B180

C13

C16

18S 4P 60mA

LED+

C10 C17

5.6nF NC

R26

NC

R51

432k

GND

GND GND

R11

GND

R20

10

GND

C12

NC M2 AM4490N

GND

C15

GND

U1 R54

10k

3 VCC GATE 26 2 VIN VFAULT 27

R22

0

R53

10k

C14

100pF

C9

4

R1

COMP

ISENSE

24 GND

EN

2k

GND

100nF

C4

R15

0

5 EN NC 28

R24

0.05

R25

NC

R4

20k

C18 R13

191k

GND GND

OSC

PGND

25

LED1

GND

LED2 LED3 LED4

1,2,5,6 1,2,5,6

NC

OVP

23

R27 0

10 BOSC LED1 22

R8

100k

C6

NC

GND 7 GND

MP3389

LED2

21

R2

DIMMING

2k

NET00016

DBRT

LED3

20

R5

20k

GND

R16

60.4k

R30 0

9 ISET LED4 19

11

LED12

LED5

18

GND 12 LED11 LED6 17

R33 0

13 LED10 LED7 16

M3-M6: AM3490N

1,2,5,6

R32 0

R31 0

M4

R29 0

R28 0

M3

100V/1A

TSOP6

14

LED9

LED8

15

R36 0 R37 0 R38 0 M6

4

1,2,5,6

VIN

R39

0

R40

NC

GND

Figure 8 Drive 18LEDs in Series, 4 strings 60mA/string

Note: For Vin>15V application, use R139 and R40(10k) divider to make a 15V bias voltage for M3-M6.

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

R35 0

R34 0

M5

14

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

PACKAGE INFORMATION

TSSOP28

5.90 TYP 9.60 9.80 28 15 0.40 TYP 1.60 TYP 0.65 BSC

PIN 1 ID

4.30 4.50

6.20 6.60

3.20 TYP

5.80 TYP

14

TOP VIEW

RECOMMENDED LAND PATTERN

0.80 1.05 0.19 0.30 0.65 BSC 0.00 0.15

1.20 MAX SEATING PLANE SEE DETAIL "A"

0.09 0.20

FRONT VIEW

SIDE VIEW

GAUGE PLANE 0.25 BSC 5.70 6.10 0 -8

o o

0.45 0.75

DETAIL

2.60 3.10

NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS . 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH , PROTRUSION OR GATE BURR . 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING ) SHALL BE 0.10 MILLIMETERS MAX . 5) DRAWING CONFORMS TO JEDEC MO -153, VARIATION AET. 6) DRAWING IS NOT TO SCALE .

BOTTOM VIEW

MP3389 Rev. 1.04 3/27/2013

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

15

MP338912-STRING WHITE LED DRIVER WITH STEP-UP CONTROLLER

PACKAGE INFORMATION

SOIC28

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

MP3389 Rev. 1.04 3/27/2013 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. 2013 MPS. All Rights Reserved.

16

Vous aimerez peut-être aussi

- LM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible InterfaceDocument45 pagesLM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible Interfacethoth2487Pas encore d'évaluation

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânPas encore d'évaluation

- SM72441 Programmable Maximum Power Point Tracking Controller For Photovoltaic Solar PanelsDocument10 pagesSM72441 Programmable Maximum Power Point Tracking Controller For Photovoltaic Solar PanelsShahid SiddiquePas encore d'évaluation

- Datasheet PDFDocument32 pagesDatasheet PDFMochamad AlbiPas encore d'évaluation

- Fan 7314Document14 pagesFan 7314Kamal NonekPas encore d'évaluation

- MP3394 r1.07Document17 pagesMP3394 r1.07ansonjonelPas encore d'évaluation

- EN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated InductorDocument16 pagesEN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated Inductorcatsoithahuong84Pas encore d'évaluation

- Fan 6961Document13 pagesFan 6961Ariel NavarretePas encore d'évaluation

- MAQ3203YM Evaluation Board User GuideDocument23 pagesMAQ3203YM Evaluation Board User GuideJohnPas encore d'évaluation

- DM0265Document19 pagesDM0265liberthPas encore d'évaluation

- DatasheetDocument13 pagesDatasheetkishore kumarPas encore d'évaluation

- Highly Efficient Integrated Synchronous Buck Regulator for DDR ApplicationsDocument31 pagesHighly Efficient Integrated Synchronous Buck Regulator for DDR ApplicationsFauzan Akbar SahriPas encore d'évaluation

- Description: Green-Power PWM Controller With Freq. JigglingDocument8 pagesDescription: Green-Power PWM Controller With Freq. JigglingLuis GuevaraPas encore d'évaluation

- Bp3102 - Ds - Rev 1.0 en Led DriverDocument10 pagesBp3102 - Ds - Rev 1.0 en Led DriverTheodoradrianPas encore d'évaluation

- MAX77680 Datasheet and Technical InfoDocument9 pagesMAX77680 Datasheet and Technical InfojackPas encore d'évaluation

- Fan7340 Slc1012c PWM Backlight Samsung 32Document16 pagesFan7340 Slc1012c PWM Backlight Samsung 32Andres Alegria50% (4)

- OB2269Document12 pagesOB2269Juan Ballon100% (1)

- ZXSC410 420Document12 pagesZXSC410 420Catalin TirtanPas encore d'évaluation

- LM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BDocument24 pagesLM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BPravin MevadaPas encore d'évaluation

- LD7552 DS 00Document10 pagesLD7552 DS 00BRIGHT_SPARKPas encore d'évaluation

- Oz9938 PDFDocument12 pagesOz9938 PDFCarlosPas encore d'évaluation

- Datasheet LM3429Document34 pagesDatasheet LM3429Bagus KrisviandikPas encore d'évaluation

- Max 2981Document13 pagesMax 2981Jamila RobinsonPas encore d'évaluation

- lx1692 PDFDocument15 pageslx1692 PDFvideosonPas encore d'évaluation

- Max 8729Document26 pagesMax 8729lagreta55Pas encore d'évaluation

- Aerosemi: Features ApplicationsDocument9 pagesAerosemi: Features Applicationsttnaing100% (1)

- Injector and Ignition Driver For Automotive ApplicationsDocument25 pagesInjector and Ignition Driver For Automotive ApplicationsAnonymous 4IEjoc100% (1)

- Accurate, Fast Settling Analog Voltages From Digital PWM SignalsDocument2 pagesAccurate, Fast Settling Analog Voltages From Digital PWM SignalsAdhi Ne CutcakrowoPas encore d'évaluation

- Features General Description: HT7L4813 Non-Isolation Buck LED Lighting Driver With Active PFCDocument10 pagesFeatures General Description: HT7L4813 Non-Isolation Buck LED Lighting Driver With Active PFCEnéas BaronePas encore d'évaluation

- Fan 7316Document21 pagesFan 7316sontuyet82Pas encore d'évaluation

- Green-Mode PWM Controller: General Description FeaturesDocument10 pagesGreen-Mode PWM Controller: General Description FeaturesLuis Luis GarciaPas encore d'évaluation

- FAN7930BDocument22 pagesFAN7930Bpagy snv100% (1)

- 700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolDocument6 pages700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolNathan WilliamsPas encore d'évaluation

- Supermodified - Miniature Controller For DC MotorsDocument38 pagesSupermodified - Miniature Controller For DC MotorsGiovanni GambaPas encore d'évaluation

- 10884Document13 pages10884karthikeidPas encore d'évaluation

- Feature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerDocument11 pagesFeature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerEnéas BaronePas encore d'évaluation

- SG 6841 TDocument14 pagesSG 6841 TBayron Salazar SaborioPas encore d'évaluation

- PT4115EDocument18 pagesPT4115Edragom2Pas encore d'évaluation

- LM3414/LM3414HV 1A 60W Common Anode Capable Constant Current Buck LED Driver Requires No External Current Sensing ResistorDocument20 pagesLM3414/LM3414HV 1A 60W Common Anode Capable Constant Current Buck LED Driver Requires No External Current Sensing ResistorAyala KarlPas encore d'évaluation

- 10.709 Gbps Laser Diode Driver Chipset: A To 1200 ADocument12 pages10.709 Gbps Laser Diode Driver Chipset: A To 1200 ABanyugeaPas encore d'évaluation

- DRV 8811Document22 pagesDRV 8811nelson_loboPas encore d'évaluation

- A4989 DatasheetDocument17 pagesA4989 DatasheetGopalkrishnan Nadar100% (1)

- LD7750 High-Voltage PWM ControllerDocument20 pagesLD7750 High-Voltage PWM ControllerAndres Alegria100% (1)

- IC-ON-LINE - CN dm0365r 44840Document20 pagesIC-ON-LINE - CN dm0365r 44840MoscandoPas encore d'évaluation

- HT7 L4815 V 100Document9 pagesHT7 L4815 V 100Enéas BaronePas encore d'évaluation

- Features General Description: Advanced Dual PWM and Dual Linear Power ControllerDocument13 pagesFeatures General Description: Advanced Dual PWM and Dual Linear Power ControllerbehzadPas encore d'évaluation

- Single Synchronous Buck PWM DC-DC ControllerDocument16 pagesSingle Synchronous Buck PWM DC-DC Controllerbachet56Pas encore d'évaluation

- CCFL Inverter IC OZ960Document12 pagesCCFL Inverter IC OZ960davesworkshopPas encore d'évaluation

- MC 33186Document21 pagesMC 33186Olga PlohotnichenkoPas encore d'évaluation

- Construccion y Diseño de InverterDocument15 pagesConstruccion y Diseño de InverterestmejiasPas encore d'évaluation

- FSDM07652R DatasheetDocument16 pagesFSDM07652R Datasheetmarianos67Pas encore d'évaluation

- Richtek RT7247ADocument15 pagesRichtek RT7247Ajhg-crackmePas encore d'évaluation

- L6565Document18 pagesL6565Sergio Daniel BarretoPas encore d'évaluation

- LCD221SD Service ManualDocument41 pagesLCD221SD Service Manual1cvbnmPas encore d'évaluation

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsD'EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Analog Circuit Design Volume Three: Design Note CollectionD'EverandAnalog Circuit Design Volume Three: Design Note CollectionÉvaluation : 3 sur 5 étoiles3/5 (2)

- 48DR3505ADocument50 pages48DR3505ALuis TorresPas encore d'évaluation

- FGPF 4633Document9 pagesFGPF 4633Andres AlegriaPas encore d'évaluation

- FAN73711 High-Current, High-Side Gate Drive IC: Features DescriptionDocument12 pagesFAN73711 High-Current, High-Side Gate Drive IC: Features DescriptionAndres AlegriaPas encore d'évaluation

- MosfetsDocument13 pagesMosfetsAndres AlegriaPas encore d'évaluation

- 2A20112 PFC Fuentes LG Audio PFC CRITICALDocument9 pages2A20112 PFC Fuentes LG Audio PFC CRITICALAndres AlegriaPas encore d'évaluation

- LG Led 32ln5400sa - 32ln540b CH - lj36bDocument77 pagesLG Led 32ln5400sa - 32ln540b CH - lj36bRobertoJavierAPas encore d'évaluation

- Medidor de Potencia AC-DC PDFDocument7 pagesMedidor de Potencia AC-DC PDFAndres AlegriaPas encore d'évaluation

- Telefunken+TF LED50S10T2+K PL L01 PDFDocument1 pageTelefunken+TF LED50S10T2+K PL L01 PDFAndres AlegriaPas encore d'évaluation

- Radio FM Con RDS Un Proyecto HAT Superior para Raspberry Pi PDFDocument8 pagesRadio FM Con RDS Un Proyecto HAT Superior para Raspberry Pi PDFAndres AlegriaPas encore d'évaluation

- Haier: Service ManualDocument52 pagesHaier: Service ManualAndres AlegriaPas encore d'évaluation

- Telefunken+TF LED50S10T2+K PL L01Document4 pagesTelefunken+TF LED50S10T2+K PL L01Andres AlegriaPas encore d'évaluation

- AOD446Document6 pagesAOD446sahabatemanPas encore d'évaluation

- TCL 32M61 - MS19 Service Manual PDFDocument72 pagesTCL 32M61 - MS19 Service Manual PDFlujorebPas encore d'évaluation

- EGS002 Manual en PDFDocument6 pagesEGS002 Manual en PDFValerică Hizanu67% (6)

- 12.09.27 Selectionguide AC-DCandPFCDocument47 pages12.09.27 Selectionguide AC-DCandPFCGabriel TorresPas encore d'évaluation

- AP3041 Ic Driver Placa Simply Syled37i Que Se QuemaDocument14 pagesAP3041 Ic Driver Placa Simply Syled37i Que Se QuemaAndres Alegria0% (1)

- Panasonic Tc-32 26lx70l, Service Manual, Manual de ServicioDocument55 pagesPanasonic Tc-32 26lx70l, Service Manual, Manual de ServicioGlennPas encore d'évaluation

- EGS002 Manual en PDFDocument6 pagesEGS002 Manual en PDFValerică Hizanu67% (6)

- (LJ46B) 32LB580B-SBDocument79 pages(LJ46B) 32LB580B-SBMárcio FerreiraPas encore d'évaluation

- 27F520T M134C PDFDocument97 pages27F520T M134C PDFAndres AlegriaPas encore d'évaluation

- LGP32-14PL1 Rev3.1 PCB Eax65391401 Eax65693102Document29 pagesLGP32-14PL1 Rev3.1 PCB Eax65391401 Eax65693102Andres AlegriaPas encore d'évaluation

- Aoc Le39a0321 OvidioDocument68 pagesAoc Le39a0321 OvidioAndres AlegriaPas encore d'évaluation

- An4087 Maxim SmpsDocument6 pagesAn4087 Maxim Smpsgpalencia_1Pas encore d'évaluation

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- MFL68606401 32LF550D-DD Da NewDocument74 pagesMFL68606401 32LF550D-DD Da NewAndres Alegria100% (2)

- Green-Mode PWM Controller With Frequency Trembling and Integrated ProtectionsDocument18 pagesGreen-Mode PWM Controller With Frequency Trembling and Integrated ProtectionsAndres AlegriaPas encore d'évaluation

- SANKEN ELECTRIC SELECTION GUIDE FOR POWER MANAGEMENT ICSDocument64 pagesSANKEN ELECTRIC SELECTION GUIDE FOR POWER MANAGEMENT ICSAndres AlegriaPas encore d'évaluation

- HAIER 48dr3505Document50 pagesHAIER 48dr3505Andres AlegriaPas encore d'évaluation

- 2A20112 PFC Fuentes LG Audio PFC CRITICALDocument9 pages2A20112 PFC Fuentes LG Audio PFC CRITICALAndres AlegriaPas encore d'évaluation

- MHDV2262-04 Fuente Ob2273Document64 pagesMHDV2262-04 Fuente Ob2273Andres AlegriaPas encore d'évaluation

- GPS-Based Transmission Line Fault Location Using Traveling Wave TechnologyDocument11 pagesGPS-Based Transmission Line Fault Location Using Traveling Wave TechnologyRohit GandhiPas encore d'évaluation

- Microwave Engineering: Matching Load ImpedancesDocument7 pagesMicrowave Engineering: Matching Load ImpedancesAzmat GuldastaPas encore d'évaluation

- Full Thesis ZBP-New 663157Document145 pagesFull Thesis ZBP-New 663157KaustubhDabeerPas encore d'évaluation

- 21.1: On-Board Bus Device Driver Pseudocode ExamplesDocument7 pages21.1: On-Board Bus Device Driver Pseudocode ExamplesSoundarya SvsPas encore d'évaluation

- Reed's Basic Electrotechnology For Engineers PDFDocument311 pagesReed's Basic Electrotechnology For Engineers PDFraovisam100% (2)

- Lecture12 BJT Transistor CircuitsDocument14 pagesLecture12 BJT Transistor CircuitsKartika MunirPas encore d'évaluation

- Lse9901b1260-Lishin Elec SpecDocument9 pagesLse9901b1260-Lishin Elec SpecRobertContrerasPas encore d'évaluation

- Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper StabilizationDocument31 pagesOp-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper StabilizationAndres MauricioPas encore d'évaluation

- Load Cell Testing Report ResultsDocument2 pagesLoad Cell Testing Report ResultsAnonymous yCpjZF1rFPas encore d'évaluation

- Class 12 FCT 4 CBSE FinalDocument6 pagesClass 12 FCT 4 CBSE FinalDerekPas encore d'évaluation

- Induction Motor Speed ControlDocument46 pagesInduction Motor Speed Controlsolo400060% (10)

- EEE363 (Exp 5) Study of The Different Loading Conditions of AlternatorDocument5 pagesEEE363 (Exp 5) Study of The Different Loading Conditions of Alternatorsalad.ass420420Pas encore d'évaluation

- DSEG8600 Installation InstructionsDocument6 pagesDSEG8600 Installation Instructionsvuvantieu802Pas encore d'évaluation

- Sharp Lc32bd6x LCD TV SMDocument212 pagesSharp Lc32bd6x LCD TV SMkothuraPas encore d'évaluation

- Afc 1563Document10 pagesAfc 1563Eugene FlexPas encore d'évaluation

- Intelligent BEAM ManualDocument14 pagesIntelligent BEAM ManualmthuyaPas encore d'évaluation

- Excite1 5TDocument43 pagesExcite1 5TTihomir DrenovskiPas encore d'évaluation

- HPB PDL450 ManualDocument232 pagesHPB PDL450 ManualReinaldo Andres Castillo Jopia50% (2)

- FestoDocument239 pagesFestoRuben VelezPas encore d'évaluation

- Feed 304 M12 - M13, Feed 484 M12 - M13 R 0459 161 990 PDFDocument22 pagesFeed 304 M12 - M13, Feed 484 M12 - M13 R 0459 161 990 PDFMadalina LazarPas encore d'évaluation

- Mallory Installation InstructionsDocument4 pagesMallory Installation Instructionssantacruz08aPas encore d'évaluation

- Philips Chassis L03.1U AA 312278513933Document56 pagesPhilips Chassis L03.1U AA 312278513933Mendez FreddyPas encore d'évaluation

- KK2.1 & KK2.1.5 Instruction Manual V1.16S1 Pro Issue 1 Settings GuideDocument28 pagesKK2.1 & KK2.1.5 Instruction Manual V1.16S1 Pro Issue 1 Settings GuidePercy Pinto CornejoPas encore d'évaluation

- Chapter 17 ElectricityDocument37 pagesChapter 17 ElectricityFozia MahboobPas encore d'évaluation

- IBS For EngineerDocument185 pagesIBS For EngineerQuyết Lê ĐứcPas encore d'évaluation

- Adv Control & Robotic Lec 5Document31 pagesAdv Control & Robotic Lec 5key3hsePas encore d'évaluation

- ELK-3 550 1HC0000742AFEnDocument20 pagesELK-3 550 1HC0000742AFEnOnur FişekPas encore d'évaluation

- Triband Eight-Port Antenna: Opa65R-Ke4D Data SheetDocument13 pagesTriband Eight-Port Antenna: Opa65R-Ke4D Data SheetGuillermoPas encore d'évaluation

- Electric Power Generation TransmissionDocument14 pagesElectric Power Generation Transmissionsilambuonnet100% (1)

- Littelfuse Thyristor MAC228A D Datasheet PDFDocument5 pagesLittelfuse Thyristor MAC228A D Datasheet PDFHamid AbdPas encore d'évaluation