Académique Documents

Professionnel Documents

Culture Documents

2-Tap Polyphase Filterxy2 - Scaler

Transféré par

djdwlsTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

2-Tap Polyphase Filterxy2 - Scaler

Transféré par

djdwlsDroits d'auteur :

Formats disponibles

XY2_SCALER Bilinear Video Scaling Engine

Rev. 2.0

Key Design Features

Synthesizable, technology independent VHDL ! "ore Versatile 2#$bit R%B&'"b"r video scaler capable o( scaling )p or do*n by any (actor. Di((erent pi+el (or,ats s)pported on re-)est 2#$bit acc),)lator *ith 2#$bit scale$pitch in .2# /20 (or,at S)pports all video resol)tions bet*een /1+/1 and #021+#021 pi+els. Higher resol)tions ,ay be s)pported on re-)est 3)lly pipelined architect)re *ith si,ple (lo* control 3eat)res a 2+2 polyphase (ilter in the + and y di,ensions. Each (ilter has /1 )ni-)e phases or interpolation points 3)lly progra,,able (ilter coe((icients to s)it the desired application E+a,ple bilinear coe((icients shipped *ith the design 4)tp)t rate is / + 2#$bit pi+el per cloc5 (or scaling (actors 6 / %enerates one scaled o)tp)t (ra,e (or every inp)t (ra,e 7o (ra,e b)((er re-)ired S)pports 2809Hz: operation on basic 3!%; devices/

Block Diagram

Figure 1: Video scaler architecture

Pin-out Description Applications

Pin name I/O in in in Description Synchrono)s cloc5 ;synchrono)s reset / & ?+ scale (actor@ Speci(ied as an )nsigned n),ber in .2# /20 (or,at scaleApitchAy .2DE00 in / & ?y scale (actor@ Speci(ied as an )nsigned n),ber in .2# /20 (or,at inp)tAppl .//E00 in 7),ber o( pi+els per line in data the so)rce inp)t (ra,e ?Speci(ied as an )nsigned /2$bit n),ber@ 7),ber o( lines per (ra,e in the so)rce inp)t (ra,e ?Speci(ied as an )nsigned /2$bit n),ber@ data data Acti e state rising edge lo* data

High -)ality 2#$bit R%B&'"b"r video scaling "onversion o( pop)lar video (or,ats to any other resol)tion s)ch as V%; to <%;, SV%; to HD/0=0 etc. Digital >V set$top bo+es and ho,e ,edia sol)tions "onversion to non$standard video resol)tions $ e.g. (or )se in portable devices and (lat$panel displays Dyna,ic scaling o( video in a *indo* on a (ra,e$by$(ra,e basis !ict)re in !ict)re ?!i!@ applications

cl5 reset scaleApitchA+ .2DE00

Generic Parameters

Generic name lineA*idth log2AlineA*idth Description Bidth o( linestores in pi+els Type integer Valid range 2# C pi+els C 2/2 log2?lineA*idth@

inp)tAlp( .//E00

in

o)tp)tAppl .//E00

in

Log2 o( linestore *idth integer

7),ber o( pi+els per line in data the scaled o)tp)t (ra,e ?Speci(ied as an )nsigned /2$bit n),ber@ 7),ber o( lines per (ra,e in the scaled o)tp)t (ra,e ?Speci(ied as an )nsigned /2$bit n),ber@ data

o)tp)tAlp( .//E00

in

<ilin+ Virte+1 )sed as a bench,ar5 Do*nload this VHDL "ore !age / o( 8

"opyright F 20/D ***.zipcores.co,

XY2_SCALER Bilinear Video Scaling Engine

Rev. 2.0

Pin-out Description cont !!!

Pin name pi+in .2DE00 pi+inAvsync I/O in in Description 2#$bit pi+el in Vertical sync in ?"oincident *ith (irst pi+el o( inp)t (ra,e@ Horizontal sync in ?"oincident *ith (irst pi+el o( inp)t line@ np)t pi+el valid Acti e state data high

;s an e+a,ple, consider the scaling o( V%; (or,at video ?1#0+#=0@ to <%; (or,at video ?/02#+G1=@. n this case the scale pitch in the + and y di,ensions *o)ld be 0.128. ;s the val)e ,)st be speci(ied as a /2./2$ bit n),ber the act)al scale pitch ,)st be ,)ltiplied by 2 /2 giving the generic val)e H2810H. n addition the )ser ,)st also speci(y the e+act resol)tion o( the so)rce inp)t (ra,e and the scaled o)tp)t (ra,e )sing the para,etersE input_ppl, input_lpf, output_ppl and output_lpf. >he (ollo*ing tables give a list o( generic para,eters re-)ired (or the conversion o( so,e e+a,ple video (or,ats. SCAL !" Video I' V%; 1#0+#=0 SV%; =00+100 <%; /02#+G1= S<%; /2=0+/02#

pi+inAhsync

in

high

pi+inAval pi+inArdy pi+o)t .2DE00 pi+o)tAvsync

in

high

o)t Ready to accept inp)t pi+el high ?Handsha5e signal@ o)t 2#$bit pi+el o)t o)t Vertical sync o)t ?"oincident *ith (irst pi+el o( o)tp)t (ra,e@ o)t Horizontal sync o)t ?"oincident *ith (irst pi+el o( o)tp)t line@ o)t 4)tp)t pi+el valid in Ready to accept o)tp)t pi+el ?Handsha5e signal@ data high

Video O(T SV%; =00+100 <%; /02#+G1= HD/0=0 /220+/0=0 2I 20#=+/0=0

Pitc# Pitc# I/P ) * PP+ D2GG D200 2/=# 2810 D2GG D200 22/D D==# 1#0 =00 /02# /2=0

I/P +PF #=0 100 G1= /02#

O/P PP+ =00

O/P +PF 100

/02# G1= /220 /0=0 20#= /0=0

pi+o)tAhsync

high

pi+o)tAval pi+o)tArdy

high high SCAL #$%& Video Video I' O(T SV%; =00+100 <%; /02#+G1= HD/0=0 /220+/0=0 2I 20#=+/0=0 V%; 1#0+#=0 SV%; =00+100 <%; /02#+G1= S<%; /2=0+/02#

Pitc# Pitc# I/P ) * PP+ 8/20 82#D G1=0 188# 8/20 82#D 8G10 #D20 =00 /02# /220 20#=

I/P +PF 100 G1= /0=0 /0=0

O/P PP+ 1#0 =00

O/P +PF #=0 100

General Description

<'2AS";LER is a very high -)ality video scaler capable o( generating interpolated o)tp)t i,ages (ro, /1+/1 )p to #021+#021 pi+els in resol)tion. >he architect)re per,its sea,less scaling ?either )p or do*n@ depending on the chosen scale (actor. nternally, the scaler )ses a 2#$bit acc),)lator and a ban5 o( polyphase 3 R (ilters *ith /1 phases or interpolation points. ;ll (ilter coe((icients are progra,,able, allo*ing the )ser to de(ine a *ide range o( (ilter characteristics. !i+els (lo* in and o)t o( the scaling engine in accordance *ith the valid$ ready pipeline protocol. !i+els are trans(erred into the scaler on a rising cloc5$edge *hen pixin_val is high and pixin_rdy is high. Li5e*ise, pi+els are trans(erred o)t o( the scaler on a rising cloc5$edge *hen pixout_val is high and pixout_rdy is high. ;s s)ch, the pipeline protocol allo*s both inp)t and o)tp)t inter(aces to be stalled independently. >he scaler is partitioned into a horizontal scaling section in series *ith a vertical scaling section as sho*n by 3ig)re /. "cale pitc#$ pi%els per line and lines per &rame >he o)tp)t resol)tion o( the scaled o)tp)t i,age is controlled by the generic para,eters scale_pitch_x, scale_pitch_y, input_ppl, input_lpf, output_ppl and output_lpf. >he scale pitch ,ay be calc)lated )sing the (ollo*ing (or,)laE

/02# G1= /2=0 /02#

Flo, control !i+els (lo* in and o)t o( the scaling engine in accordance *ith the valid$ ready pipeline protocol2. >he scaling operation occ)rs on a line$by$line basis *ith the signal pixin_hsync speci(ying the start o( a ne* line and pixin_vsync speci(ying the start o( a ne* (ra,e. ;ll pi+els into the scaler ?incl)ding pixin_vsync and pixin_hsync@ ,)st be -)ali(ied by the pixin_val signal asserted high, other*ise changes to the inp)t signals *ill be ignored. 7ote that the (irst pi+el o( a ne* (ra,e is acco,panied by a valid vsync and hsync. >he (irst pi+el in a ne* line is acco,panied by hsync only. 4n receipt o( the (irst vsync, the scaling operation begins and o)tp)t pi+els are generated in accordance *ith the chosen scale para,eters. %enerally, (or scale$do*n ?deci,ation@ operations, the inp)t inter(ace *ill not stall. "onversely, (or scale$)p ?interpolation@ the n),ber o( o)tp)t pi+els *ill be greater than the n),ber o( inp)t pi+els. >his *ill res)lt in the occasional stalling o( the inp)t d)e to the change in ratio.

pitch = (

Input resolution ) 2 12 Output resolution

2 See Jipcores application noteE appAnoteAzc00/.pd( (or ,ore e+a,ples o( ho* to )se the valid$ready pipeline protocol !age 2 o( 8

"opyright F 20/D ***.zipcores.co,

Do*nload this VHDL "ore

XY2_SCALER Bilinear Video Scaling Engine

Rev. 2.0

+oading o& scale parameters >he scale para,eters are ()lly progra,,able and allo* the inp)t video to be scaled di((erently on a (ra,e$by$(ra,e basis. Bith care()l design, the architect)re also per,its di((erent video so)rces to be ,)ltiple+ed into the sa,e scaler *ith di((erent scaling para,eters. !ara,eters are )pdated contin)o)sly on every rising cloc5 edge and ,)st re,ain stable d)ring the scaling operation. Bhen progra,,ing ne* scale para,eters ?e.g. d)e to a change o( video ,ode@ it is necessary to assert the syste, reset signal (or at least one cloc5 cycle to avoid any possible corr)ption in the o)tp)t video. >his is o(ten convenient to do d)ring the vertical blan5ing period o( an inp)t video (ra,e *hen there are no active pi+els. ;(ter reset the scaler *ill loc5 to the ne+t clean inp)t (ra,e be(ore the scaling operation contin)es. "caling algorit#m >he scaler )ses a 2$tap polyphase (ilter in the +$di,ension and a 2$tap polyphase (ilter in the y$di,ension. By de(a)lt, the + and y (ilters )se bilinear interpolation ?3ig)re 2@. n addition, the )ser ,ay also )se a di((erent ()nction to derive the (ilter coe((icients depending on the applicationD.

Functional Timing

3ig)re D sho*s the signalling at the inp)t to the scaler at the start o( a ne* (ra,e. >he (irst line o( a ne* (ra,e begins *ith pixin_vsync and pixin_hsync asserted high together *ith the (irst pi+el. 7ote that the signals pixin, pixin_vsync and pixin_hsync are only valid i( pixin_val is also asserted high. n addition, the diagra, sho*s *hat happens *hen pixin_rdy is de$asserted. n this case, the pipeline is stalled and the )pstrea, inter(ace ,)st hold$o(( be(ore ()rther pi+els are processed.

Figure *: First line of a ne+ fra,e 3ig)re # sho*s the signalling at the o)tp)t o( the scaler. >he o)tp)t )ses e+actly the sa,e protocol as the inp)t. Each ne* o)tp)t line begins *ith pixout_hsync and pixout_val asserted high. n this partic)lar e+a,ple, it sho*s pixout_val de$asserted (or / cloc5$cycle, in *hich case, the o)tp)t pi+el sho)ld be ignored. Re,e,ber that trans(ers at a valid$ready inter(ace are only per,itted *hen valid and ready are both si,)ltaneo)sly high.

Figure ': (ilinear function ) x and y filter tap positioning

Figure -: Scaler output sho+ing invalid pixel

See Jipcores application noteE appAnoteAzc00D.pd( (or e+a,ples o( ho* to generate coe((icient sets Do*nload this VHDL "ore !age D o( 8

"opyright F 20/D ***.zipcores.co,

XY2_SCALER Bilinear Video Scaling Engine

Rev. 2.0

"ource File Description

;ll so)rce (iles are provided as te+t (iles coded in VHDL. >he (ollo*ing table gives a brie( description o( each (ile.

>he (ile video_in.txt (ollo*s a si,ple (or,at *hich de(ines the state o( signalsE pixin_val , pixin_vsync, pixin_hsync and pixin on a cloc5$by$cloc5 basis. ;n e+a,ple (ile ,ight be the (ollo*ingE / / 0 / . . / / 0 0 0 / 0 0 0 00 // 22 DD ## 88 00 00 00 11 GG == K pi+el 0 line 0 ?start o( (ra,e@ K pi+el / K donHt careL K pi+el 2

"ource &ile videoAin.t+t videoA(ileAreader.vhd pipelineAreg.vhd pipelineAshovel.vhd ra,AdpA*Ar.vhd (i(oAsync.vhd +2Ab)((er.vhd +2A(ilterApac5.vhd +2A(ilterApolyphase.vhd +2Ascaler.vhd y2Ab)((er.vhd y2A(ilterApac5.vhd y2A(ilterApolyphase.vhd y2Ascaler.vhd +y2Areg.vhd +y2Ascaler.vhd +y2AscalerAbench.vhd

Description >e+t$based so)rce video (ile Reads te+t$based so)rce video (ile !ipelined register ele,ent !ipelined HshovelH register D)al port R;9 co,ponent Synchrono)s 3 34 !i+el inp)t b)((er&shi(t register !ac5age containing +$(ilter coe((icients Horizontal scaler o)tp)t pi+el (ilter Horizontal scaler co,ponent Line b)((er !ac5age containing y$(ilter coe((icients Vertical scaler o)tp)t pi+el (ilter Vertical scaler co,ponent Video scaler inp)t registers Video scaler top$level co,ponent >op$level test bench

0 / 00 // 22 K pi+el 0 line / etc..

n this e+a,ple, the (irst line o( o( the video_in.txt (ile asserts the inp)t signals pi+inAval M /, pi+inAvsync M /, pi+inAhsync M / and pi+in M 0+00//22. >he si,)lation ,)st be r)n (or at least /0 ,s d)ring *hich ti,e an o)tp)t te+t (ile called video_out.txt *ill be generated. >his (ile contains a se-)ential list o( 2#$bit o)tp)t pi+els in the sa,e (or,at as video_in.txt. >he e+a,ple provided scales a G1=+8G1 so)rce test pattern by a (actor o( 0.=DD in the + and y di,ensions to give a V%; o)tp)t i,age o( 1#0+#=0 pi+els. 3ig)re 8 sho*s the res)lting i,age (ro, the test.

Functional Testing

;n e+a,ple VHDL testbench is provided (or )se in a s)itable VHDL si,)lator. >he co,pilation order o( the so)rce code is as (ollo*sE /. 2. D. #. 8. 1. G. =. 2. /0. //. /2. /D. /#. /8. /1. videoA(ileAreader.vhd pipelineAreg.vhd pipelineAshovel.vhd ra,AdpA*Ar.vhd (i(oAsync.vhd +2Ab)((er.vhd +2A(ilterApac5.vhd +2A(ilterApolyphase.vhd +2Ascaler.vhd y2Ab)((er.vhd y2A(ilterApac5.vhd y2A(ilterApolyphase.vhd y2Ascaler.vhd +y2Areg.vhd +y2Ascaler.vhd +y2AscalerAbench.vhd

Figure .: $utput fra,e fro, the hard+are si,ulation exa,ple /Scale0do+n of 123x.12 to 2-4x-345

Per&ormance

>he Bilinear Video Scaling Engine *as tested *ith a large n),ber o( scale (actors to veri(y correct operation and to observe the -)ality o( the o)tp)t video. >he tr)e de(inition and -)ality is di((ic)lt to sho* *ithin the li,itations o( this doc),ent, ho*ever, e+a,ple i,ages can be provided on re-)est. >he video scaler *as also veri(ied )sing a <ilin+N Spartan1 S!108 develop,ent board as a plat(or,. >he photo in 3ig)re 1 de,onstrates the scale do*n o( a !;L so)rce i,age to a s,all c)sto, video *indo* o( 800+#00 pi+els on an S<%; ?/2=0+/02#@ bac5gro)nd.

>he VHDL testbench instantiates the <'2AS";LER co,ponent and the )ser ,ay ,odi(y the generic para,eters in order to generate the desired scaled o)tp)t i,age. >he so)rce video (or the si,)lation is generated by the video (ile$reader co,ponent. >his co,ponent reads a te+t$based (ile *hich contains the R%B pi+el data. >he te+t (ile is called video_in.txt and sho)ld be placed in the top$level si,)lation directory.

"opyright F 20/D ***.zipcores.co,

Do*nload this VHDL "ore

!age # o( 8

XY2_SCALER Bilinear Video Scaling Engine

Rev. 2.0

V678 9 2 -esource type Slice register Slice LO> Bloc5 R;9 DS!#= 4cc)pied Slices "loc5 (re-)ency ?appro+@

.uantity used 1/# 118 D /2 2=0 9Hz

S"A78A& 2 -esource type Slice register Slice LO> Bloc5 R;9 DS!#= Figure 2: Scaler de,o la: setup /;eneration of a s,all .44x-44 video +indo+ on S9;A :ac<ground5 4cc)pied Slices "loc5 (re-)ency ?appro+@

.uantity used 1/# G=D 1 /2 D// /G0 9Hz

"ynt#esis

>he (iles re-)ired (or synthesis and the design hierarchy is sho*n belo*E

-e ision /istory

-e ision /.0 0#ange description nitial revision Date 08&02&2002

+y2Ascaler.vhd +y2Areg.vhd pipelineAreg.vhd +2Ascaler.vhd pipelineAshovel.vhd +2Ab)((er.vhd +2A(ilterApolyphase.vhd pipelineAreg.vhd y2Ascaler.vhd pipelineAshovel.vhd y2Ab)((er.vhd ra,AdpA*Ar.vhd (i(oAsync.vhd pipelineAreg.vhd y2A(ilterApolyphase.vhd pipelineAreg.vhd

/./

;dded e+tra ite,s to 5ey (eat)res

/2&01&2002

/.2

Opdated synthesis res)lts

/8&/2&2002

/.#

;dded scaling (or,)la. Opdated so)rce (ile descriptions to incl)de shovels Opdated synthesis res)lts in line *ith ,inor so)rce code changes

/=&02&20/0

/.8

2G&0/&20/2

2.0

9aPor revision. Si,pli(ied loading o( scale /0&08&20/D para,eters. 9odi(ied architect)re to s)pport one (ra,e o)t (or one (ra,e in

>he VHDL core is designed to be technology independent. Ho*ever, as a bench,ar5, synthesis res)lts have been provided (or the <ilin+N Virte+1 and Spartan1 3!%; devices. Synthesis res)lts (or other 3!%;s and technologies can be provided on re-)est. 3i+ing the scale para,eters at the scaler inp)t *ill res)lt in the ,ost opti,), scaler design. n addition, the speed o( the design ,ay be i,proved by tying the signal pixout_rdy lo*. >his ,ay be possible i( the designer 5no*s that the pipeline do*nstrea, o( the scaler *ill al*ays be able to accept o)tp)t pi+els. "are()l attention ,)st be ,ade to the *idth o( the line stores as this *ill e((ect the a,o)nt o( R;9 reso)rce )sed in the design. >rial synthesis res)lts are sho*n *ith the generic para,eters set toE line_+idth M /02# and log'_line_+idth M /0. Reso)rce )sage is speci(ied a(ter !lace and Ro)te.

"opyright F 20/D ***.zipcores.co,

Do*nload this VHDL "ore

!age 8 o( 8

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- How To Perform iSTEP UPDATES On NBTEVO PDFDocument22 pagesHow To Perform iSTEP UPDATES On NBTEVO PDFkenjyaitc100% (1)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- SH69P26K PDFDocument43 pagesSH69P26K PDFMarcos Gomes Missel83% (12)

- RSK200083 MusicProduction 2016 G3 Coursework-05Oct2018Document70 pagesRSK200083 MusicProduction 2016 G3 Coursework-05Oct2018Ashish S Maan100% (5)

- TDR Kotelnikov - Manual - Tokyo Dawn Knowledge BaseDocument31 pagesTDR Kotelnikov - Manual - Tokyo Dawn Knowledge BaseHernâni Rodrigues SilvaPas encore d'évaluation

- Btech 1 Sem Basic Electrical Engineering Ree 101 2018 19Document2 pagesBtech 1 Sem Basic Electrical Engineering Ree 101 2018 19Shrey SharmaPas encore d'évaluation

- Steval-Isa137V1: Demonstration Board Based On Viper06 From The Fixed-Frequency Viper™ Plus FamilyDocument4 pagesSteval-Isa137V1: Demonstration Board Based On Viper06 From The Fixed-Frequency Viper™ Plus FamilyalperusluPas encore d'évaluation

- KPI ExportDocument153 pagesKPI ExportnandijPas encore d'évaluation

- Lorain BD 2000 DatasheetDocument2 pagesLorain BD 2000 DatasheetalfredoculajayPas encore d'évaluation

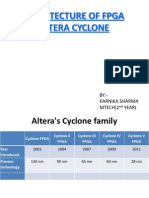

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Document29 pagesArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- ASUS ExpertCenter PN53 - Datasheet - CompressedDocument3 pagesASUS ExpertCenter PN53 - Datasheet - CompressedMaruthiPas encore d'évaluation

- Datasheet xc866Document108 pagesDatasheet xc866SartoPas encore d'évaluation

- PHÂN TÍCH 30 NGÀNH HÀNG - Trang Tính1Document12 pagesPHÂN TÍCH 30 NGÀNH HÀNG - Trang Tính1K60 Nguyễn Hữu Yên HàPas encore d'évaluation

- Project 13 - Impedance Matching Design Using Lumped and Distributed Implementations in ADS (October 2013)Document12 pagesProject 13 - Impedance Matching Design Using Lumped and Distributed Implementations in ADS (October 2013)Stephen J. WattPas encore d'évaluation

- Next Generation ExchangeDocument15 pagesNext Generation ExchangeVinay TannaPas encore d'évaluation

- Linkwitz Riley Crossovers Primer PDFDocument14 pagesLinkwitz Riley Crossovers Primer PDFloach71Pas encore d'évaluation

- Optimum Frame SynchronizationDocument5 pagesOptimum Frame SynchronizationDawit SeleshPas encore d'évaluation

- WIBO-THINK Wi-Fi Robot Controller Module: 2-1: Pin DescriptionDocument13 pagesWIBO-THINK Wi-Fi Robot Controller Module: 2-1: Pin DescriptionAbolfazl HabibiPas encore d'évaluation

- Walker Ultrasonic Wind Sensor2080Document2 pagesWalker Ultrasonic Wind Sensor2080bobPas encore d'évaluation

- Alcatel-Lucent GPON Brochure PDFDocument8 pagesAlcatel-Lucent GPON Brochure PDFSteven HungPas encore d'évaluation

- s48 2000e3 Solar Converter Datasheet - 0Document2 pagess48 2000e3 Solar Converter Datasheet - 0Charmer JiaPas encore d'évaluation

- Beamforming (TDD) Feature Parameter DescriptionDocument56 pagesBeamforming (TDD) Feature Parameter DescriptionMohammed ShakilPas encore d'évaluation

- Aeng 514 FinalDocument722 pagesAeng 514 FinalPaul GernahPas encore d'évaluation

- T Rec G.9959 201501 I!!pdf eDocument128 pagesT Rec G.9959 201501 I!!pdf eJason LaCockPas encore d'évaluation

- Tae Motoko YoDocument82 pagesTae Motoko Yoraveniro2013Pas encore d'évaluation

- ZKAccess Price List - DL With Kits - Feb 2015Document13 pagesZKAccess Price List - DL With Kits - Feb 2015Security Lock DistributorsPas encore d'évaluation

- THC1604009 - Informasi Harga CR Vita & DV5700 CR Classic & DV5950 President University Medical Center 12 April 2016Document9 pagesTHC1604009 - Informasi Harga CR Vita & DV5700 CR Classic & DV5950 President University Medical Center 12 April 2016ResaPas encore d'évaluation

- Steca Solsum Productdatasheet EN PDFDocument1 pageSteca Solsum Productdatasheet EN PDFCalin SilviuPas encore d'évaluation

- Milesight AI Vandal Proof Mini Bullet Network Camera NDAA Datasheet enDocument4 pagesMilesight AI Vandal Proof Mini Bullet Network Camera NDAA Datasheet enPhirate DorindPas encore d'évaluation

- CPU and Its Working PrincipleDocument11 pagesCPU and Its Working Principlekeshavpoudel83% (6)