Académique Documents

Professionnel Documents

Culture Documents

Capitulo 03 Interfaz Paralela

Transféré par

Fernando Felipe Tapia OrdenesTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Capitulo 03 Interfaz Paralela

Transféré par

Fernando Felipe Tapia OrdenesDroits d'auteur :

Formats disponibles

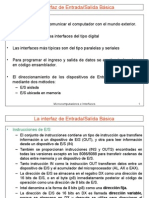

La interfaz de Entrada/Salida Bsica

Tiene por finalidad comunicar el computador con el mundo exterior. Generalmente emplea interfaces del tipo digital Las interfaces ms tpicas son del tipo paralelas y seriales Para programar el ingreso y salida de datos se emplea instrucciones en cdigo ensamblador. El direccionamiento de los dispositivos de Entrada/Salida se hace mediante dos mtodos:

E/S aislada E/S ubicada en memoria

Microcomputadores e Interfaces 1

La interfaz de Entrada/Salida Bsica

Instrucciones de E/S

El conjunto de instrucciones contiene un tipo de instruccin que transfiere informacin a un dispositivo de E/S (OUT), y otra para leer informacin desde un dispositivo de E/S (IN) Tambin se proporcionan instrucciones (INS y OUTS) encontradas en todas las versiones excepto en los 8086/8088 para transferir cadenas de datos entre memoria y un dispositivo de E/S. Tanto instruccin IN como la instruccin OUT transfieren datos entre un dispositivo de E/S y el acumulador del microprocesador (AL, AX o EAX). La direccin de E/S se almacena en el regsitro DX como una direccin de 16 bits de E/S, o en el byte (p8) inmediatamente posterior al cdigo de operacin como una direccin de 8 bits de E/S. Intel denomina a la forma de 8 bits (p8) como una direccin fija. La direccin de E/S de 16 bits en DX es llamada direccin variable, porque se almacena en DX y despus se utiliza para direccionar el dispositivo de E/S.

Microcomputadores e Interfaces

La interfaz de Entrada/Salida Bsica

Al transferir datos con la instruccin IN o OUT, la direccin de E/S tambin conocida como nmero de puerto ( o simplemente puerto), aparece en el bus de direcciones. La interfaz externa de E/S decodifica el nmero de puerto de la misma manera en que codifica un adireccin de memoria. El nmero de puerto fijo de 8 bits (p8) aparece en las conexiones A/ - A0 del bus de direcciones, con los bits A15 A8 igual a 000000002. Las direcciones por arriba de A15 no estn definidas para una instruccin de E/S. Esto significa que a las primeras 256 direcciones de puerto de E/S (00h a FFh) se accede por las instrucciones de E/S de direccin fija, como variable, pero a cualquier direccin de E/S desde 0100h a la FFFFh se accede solamente por la direccin de E/S variable.

Microcomputadores e Interfaces 3

La interfaz de Entrada/Salida Bsica

Instrucciones de E/S del 8086/8088

Instruccin

IN AL,p8 IN AX,p8 IN AL,DX IN AX,DX OUT p8,AL OUT p8,AX OUT DX,AL OUT DX,AX

Ancho datos

8 16 8 16 8 16 8 16

Funcin

Transfiere un byte del puerto p8 a AL Transfiere una palabra del puerto p8 a AX Transfiere un byte del puerto direccionado por DX a AL Transfiere una palabra del puerto direccionado por DX a AX Transfiere un byte de AL al puerto p8 Transfiere una palabra de AX al puerto p8 Transfiere un byte de AL al puerto direccionado por DX Transfiere una palabra de AX al puerto direccionado por DX

Microcomputadores e Interfaces

La interfaz de Entrada/Salida Bsica E/S aislada y ubicada en memoria (memory-mapped)

E/S Aislada.

La tcnica de transferencia ms comn de E/S empleada en los sistemas basados en los microprocesadores Intel. El trmino aislada describe cmo las localidades de E/S estn aisladas del sistema de memoria en un espacio de direccin de E/S separado.

E/S ubicada en memoria.

la E/S ubicada en memoria no utiliza las instrucciones de IN y OUT. En su lugar, usa cualquier instruccin que transfiera datos entre el microprocesador y la memoria. Un dispositivo de E/S ubicado en memora es manejado como una localidad de memoria y por consiguiente admite las instrucciones de transferencia de datos entre la memoria y el procesador.

Microcomputadores e Interfaces

La interfaz de Entrada/Salida Bsica

FFFFF

FFFFF

E/S

1M x 8

FFFF

64K x 8

00000 0000 00000

E/S aislada

Espacio de E/S

Microcomputadores e Interfaces

E/S ubicada en memoria

6

La interfaz de Entrada/Salida Bsica

Interfaces bsicas de entrada y de salida El dispositivo bsico de entrada es un conjunto de buffers de tres estados. El dispositivo bsico de salida es un conjunto de registros transparentes de datos. El trmino IN se refiere al movimiento de datos desde un dispositivo (puerta) de E/S al microprocesador (Acumulador) El trmino OUT se refiere al movimiento de datos desde el microprocesador (Acumulador) al dispositivo (puerta) de E/S

Microcomputadores e Interfaces

La interfaz de Entrada/Salida Bsica

La interfaz bsica de entrada

Los buffers de tres estados son utilizados para construir el puerto de entrada de 8 bits. Los datos TTL externos estn conectados a las entradas de los buffers Las salidas de los buffers estn conectadas al bus de datos Las conexiones del bus dependen del microprocesador ( 8, 16, 32 o 64 bits) En la siguiente figura se aprecia un circuito que ingresa datos (8 bits) que provienen de interruptores al acumulador del microprocesador, cuando la seal de seleccin SEL toma el valor lgico de 0. De esta forma, al ejecutar la instruccin IN, el contenido de los interruptores se copia al registro AL. Cuando el microprocesador ejecuta una instruccin IN, la direccin del puerto de E/S se decodifica para generar un 0 lgico en SEL. La presencia de un 0 en las entradas de control de salida (1G y 2G) del buffer 74ALS244 ocasiona que las conexiones de entrada de datos (A) sean conectadas a la conexin de salida de datos (Y). Un 1 lgico lleva al dispositivo al modo de tercer estado que desconecta los interruptores del bus de datos.

Microcomputadores e Interfaces 8

La interfaz de Entrada/Salida Bsica Caractersticas del Buffer 3-State 74LS244

Microcomputadores e Interfaces

La interfaz de Entrada/Salida Bsica

Vcc= 5.0 volts

10 K

BUS de Datos

1Y1 1Y2 1Y3 1Y4 2Y1 2Y2 2Y3 2Y4

1A 1 1A 2 1A 3 1A 4 2A 1 2A 2 2A 3 2A 4 1G 2G

74ALS244

Microcomputadores e Interfaces

10

La interfaz de Entrada/Salida Bsica

La interfaz bsica de salida

Acepta datos desde el microprocesador y por lo general, debe mantenerlos para algn dispositivo externo Sus registros o biestables, al igual que los buffers del dispositivo de entrada, frecuentemente estn integrados en el dispositivo de E/S En la figura siguiente se aprecia una conexin de 8 LEDs conectados al microcomputador a travs de la interfaz 74ALS374. El biestable almacena el nmero al que da salida el microprocesador por el bus de datos, de manera que los LEDs puedan encenderse con cualquier nmero binario de 8 bits. Los biestables son requeridos para mantener los datos, porque cuando el microprocesador ejecuta una instruccin OUT, los datos estn presentes en el bus de datos nicamente por menos de 1.0 useg. Sin un biestable, el observador nunca vera la iluminacin de los LEDs Al ejecutar la instruccin OUT, los datos de AL o AX se transfieren al registro por medio del bus de datos Cada vez que se ejecuta la instruccin OUT, se activa la seal SEL al registro

Microcomputadores e Interfaces 11

La interfaz de Entrada/Salida Bsica Caractersticas del Latch tipo D 3-State 74LS374

Microcomputadores e Interfaces

12

La interfaz de Entrada/Salida Bsica

Vcc= 5.0 volts

330

U D0 D1 D2 D3 D4 D5 D6 D7 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

Bus de Datos

>CLK

OC

74ALS374

SEL

Microcomputadores e Interfaces

13

La interfaz de Entrada/Salida Bsica

Protocolo con respuesta

Muchos dispositivos de E/S admiten o liberan informacin a una velocidad mucho menor que el microprocesador Otro mtodo para el control de E/S, es llamado protocolo de respuesta (handshaking) o encuesta (polling), sincroniza al dispositivo de E/S con el microprocesador Un caso caracterstico es la conexin entre un microcomputador y una impresora. Aqu los datos son transferidos por medio de las conexiones de datos (D7-D0), BUSY indica que la impresora est ocupada y STB(strobe) es un pulso de reloj empleado para enviar los datos que imprima la impresora. Tan pronto la impresora recibe un pulso STB genera un 1 lgico en la terminal BUSY, lo que indica que la impresora est ocupada imprimiendo un dato El software de la impresora hace una encuesta tratando de verificar en que instante la terminal BUSY cambia al estado 0 lgico.

Microcomputadores e Interfaces

14

La interfaz de Entrada/Salida Bsica

Protocolo con respuesta

El siguiente es un programa bsico de encuesta para determinar si BUSY esta ocupado o no. 0000 0002 0004 0006 0008 000A IN AL,BUSY TEST AL,BUSY_BIT JNE 0000 MOV AL,BL OUT PRINTER,AL END

Microcomputadores e Interfaces

15

La interfaz de Entrada/Salida Bsica

El conector DB25 encontrado en las computadoras y el conector Centronics de 36 terminales encontrado en impresoras para el establecimiento de la interfaz Centronics para impresoras paraleas se muestra en la sgte. figura:

DB25

CENT36

Microcomputadores e Interfaces

16

La interfaz de Entrada/Salida Bsica

Decodificacin de direccin de un puerto de E/S

La decodificacin de un puerto de E/S es muy parecida a la decodificacin de direccin de un banco de memoria La nica diferencia est en que para una memoria de usan las lneas de direccin A19-A0, mientras que en E/S aislada se usa slo A15-A0 Generalmente se emplea un Decodificador para habilitar a los distintos puertos mediante la accin de las seales provenientes de las lneas de direcciones El decodificador acta de preferencia sobre los terminales de activacin (G1, G2 , SEL, SEL1, etc) del circuito que controla el puerto de E/S. Las caractersticas de los decodificadores varan de acuerdo a la forma en que se desee controlar el puerto.

Microcomputadores e Interfaces 17

La interfaz de Entrada/Salida Bsica

El siguiente es el dibujo de un circuito decodificador 74LS138, que permite decodificar puertos de 8 bits desde F0h hasta F7h. Sus terminales de entrada son A, B y C y los de salida en complemento Y0 a Y7 Posee tres terminales de habilitacin, G1, G2A y G2B

U A B C Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

G1 G 2A G 2B

74ALS138

Microcomputadores e Interfaces

18

La interfaz de Entrada/Salida Bsica

Caractersticas del decodificador Binario 74LS138 de 3 a 8 lneas

Microcomputadores e Interfaces

19

La interfaz de Entrada/Salida Bsica

Decodificador de 8 bits F0h a F7h

A7 1 1 1 1 1 1 1 1 A6 1 1 1 1 1 1 1 1 A5 1 1 1 1 1 1 1 1 A4 1 1 1 1 1 1 1 1 A3 0 0 0 0 0 0 0 0 A2 0 0 0 0 1 1 1 1 A1 0 0 1 1 0 0 1 1 A0 0 1 0 1 0 1 0 1 Y7 1 1 1 1 1 1 1 0 Y6 1 1 1 1 1 1 0 1 Y5 1 1 1 1 1 0 1 1 Y4 1 1 1 1 0 1 1 1

U A0 A1 A2 A B C Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 F0' F1' F2' F3' F4' F5' F6' F7'

Y3 1 1 1 0 1 1 1 1

Y2 1 1 0 1 1 1 1 1

Y1 1 0 1 1 1 1 1 1

Y0 0 1 1 1 1 1 1 1

DIRECCION F0 F1 F2 F3 F4 F5 F6 F7

A4 A3

G1 G2A G2B

74ALS138

A5 A6 A7

Microcomputadores e Interfaces

20

La interfaz de Perifrica Programable (PPI)

La PPI (interfaz perifrica programable) tipo 82C55, es un componente popular y de bajo costo, que puede ser utilizado como interfaz del microprocesador con cualquier dispositivo de E/S compatible a TTL. Se emplea como interfaz de teclado y puertas de impresora paralela en computadoras (frecuentemente integradas en un chipset). Requiere la insercion de estados de espera cuando se usa con microprocesadores que usan frecuencias de reloj mayores de 8 MHz. PPI tiene 24 pines para E/S que son programables en grupos de 12 pines y tiene 3 distintos modos de operacin ( 0, 1 y 2). En la PC, un 82C55 o su equivalente es decodificado en la direccin de puertas de E/S 60H-63H. Posee tres puertos de salida, el puerto A, el B y el C. Cada puerto consta de 8 lneas de E/S (byte) Polarizacin Vcc= + 5.0 volts C.C.

Microcomputadores e Interfaces 21

La interfaz de Perifrica Programable (PPI)

Caractersticas de la PPI 82C55

Microcomputadores e Interfaces

22

La interfaz de Perifrica Programable (PPI)

GRUPO A

BUS DE DATOS

D0 D1 D2 D3 D4 D5 D6 D7 RD WR A0 A1 CS RESET PA 0 PA 1 PA 2 PA 3 PA 4 PA 5 PA 6 PA 7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

PUERTA A (PA7 PA0)

PUERTA - A

Mitad Superior PUERTA C (PC7 PC4)

CONTROL

PUERTA -B

GRUPO B PUERTA B (PB7 PB0) Mitad Inferior PUERTA C (PC3 PC0) A1 0 0 1 1 A0 0 1 0 1 Funcin Puerto A Puerto B Puerto C

Registro de Comando 23

82C55

GND

VCC

PUERTA -C

Microcomputadores e Interfaces

La interfaz de Perifrica Programable (PPI)

Descripcin de los pines del 82C55 Vcc � Terminal de polarizacin positivo de + 5 volts C.C. GND � Terminal de tierra del circuito integrado. D7 D0 � Bus de datos de lneas bidireccionales con lgica de tres estados RESET � Un 1 lgico en esta terminal borra el contenido del registro de control y todas las puertas son puestas a modo 0 y en configuracin de entrada.

Microcomputadores e Interfaces

24

La interfaz de Perifrica Programable (PPI)

Descripcin de los pines del 82C55 CS � Chip Select. Un 0 lgico puesto en este terminal habilita la comunicacin entre el 82C55 y el Bus de Datos. RD � Terminal de control de Lectura. Una seal de nivel 0 lgico puesto en este terminal permite leer el estado de la PPI o los datos enviados va el Bus de Datos al acumulador del microprocesador. WR � Terminal de control de Escritura. Una seal de nivel 0 lgico puesto en este terminal permite cargar la programacin y enviar datos va el Bus de Datos a la PPI desde el acumulador del microprocesador.

Microcomputadores e Interfaces 25

La interfaz de Perifrica Programable (PPI)

Descripcin de los pines del 82C55 A1 - A0 � Terminales de direccin. Estas seales de entrada, en conjunto con las seales de control RD y WR, controlan la seleccin de una de las tres puertas o del registro de control de la PPI. A1 y A0, son a menudo conectados a los bits menos significativos del Bus de Direcciones del Microprocesador. PA7 PA0 � Puerta A. Posee 8 lneas que se configuran como entradas o salidas. PB7 PB0 � Puerta B. Posee 8 lneas que se configuran como entradas o salidas. PC7 PC0 � Puerta C. Posee 8 lneas que se configuran como entradas o salidas.

Microcomputadores e Interfaces 26

La interfaz de Perifrica Programable (PPI)

Operacin Bsica de Control de la 82C55

A1 0 0 1 0 0 1 1 X 1 X A0 0 1 0 0 1 0 1 X 1 X RD 0 0 0 1 1 1 1 X 0 1 WR 1 1 1 0 0 0 0 X 1 1 CS 0 0 0 0 0 0 0 1 0 0 OPERACION PUERTA A -> DATA BUS PUERTA B -> DATA BUS PUERTA C -> DATA BUS DATA BUS -> PORT A DATA BUS -> PORT B DATA BUS -> PORT C DATA BUS -> CONTROL DATA BUS -> 3 STATE ERROR DATA BUS -> 3 STATE

Microcomputadores e Interfaces

27

La interfaz de Perifrica Programable (PPI)

Byte de Comando A

7 1 6 X 5 X 4 X 3 X 2 X 1 X 0 X

GRUPO B

Puerto C (PC3 PC0) 1 = entrada 1 = entrada 00 = Modo 0 0 = salida 0 = salida 01 = Modo 1 Puerto B

Activa la opcin de Bit Set/Reset 1 = inactivo 0 = activo

MODO

GRUPO A

Puerto C (PC7 PC4) 1 = entrada 1 = entrada 00 = Modo 0 Microcomputadores e Interfaces 0 = salida 0 = salida 01 = Modo 1 28 Puerto A MODO 1X = Modo 2

La interfaz de Perifrica Programable (PPI)

Byte de Comando B (Bit Set/Reset)

7 0 6 X 5 X 4 X 3 2 1 0 Establecimiento/restauracin de bit 1 = establece 0 = restaura

0 0 0 0 1 1 1 1

Microcomputadores e Interfaces

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

29

La interfaz de Perifrica Programable (PPI)

Programacin de la PPI De acuerdo al Byte de Comando, se programan los Modos y la Configuracin de las Puertas Ejemplo 01:

7 1 6 0 5 0 4 0 3 0 2 0 1 0 0 0

Bit 7 : habilita byte de comando Bites 6 y 5 : sealan Modo 0 al grupo A Bit 4 : puerta A en configuracin de salida Bit 3 : mitad superior de puerta C en configuracin de salida Bit 2 : seala Modo 0 al grupo B Bit 1 : puerta B en configuracin de salida Bit 0 : mitad inferior de puerta C en configuracin de salida

Microcomputadores e Interfaces 30

La interfaz de Perifrica Programable (PPI)

Programacin de la PPI De acuerdo al Byte de Comando, se programan los Modos y la Configuracin de las Puertas Ejemplo 02:

7 1 6 0 5 0 4 1 3 0 2 0 1 0 0 1

Bit 7 : habilita byte de comando Bites 6 y 5 : sealan Modo 0 al grupo A Bit 4 : puerta A en configuracin de entrada Bit 3 : mitad superior de puerta C en configuracin de salida Bit 2 : seala Modo 0 al grupo B Bit 1 : puerta B en configuracin de salida Bit 0 : mitad inferior de puerta C en configuracin de entrada

Microcomputadores e Interfaces 31

La interfaz de Perifrica Programable (PPI)

Programacin de la PPI De acuerdo al Byte de Comando, se programan los Modos y la Configuracin de las Puertas Ejemplo 03:

7 1 6 0 5 1 4 0 3 X 2 0 1 0 0 X

Bit 7 : habilita byte de comando Bites 6 y 5 : sealan Modo 1 al grupo A Bit 4 : puerta A en configuracin de salida Bit 3 : mitad superior de puerta C dont care Bit 2 : seala Modo 0 al grupo B Bit 1 : puerta B en configuracin de salida Bit 0 : mitad inferior de puerta C dont care

Microcomputadores e Interfaces 32

La interfaz de Perifrica Programable (PPI)

Programacin de la PPI De acuerdo al Byte de Comando, se programan los Modos y la Configuracin de las Puertas Ejemplo 04:

7 1 6 0 5 1 4 1 3 X 2 1 1 0 0 X

Bit 7 : habilita byte de comando Bites 6 y 5 : sealan Modo 1 al grupo A Bit 4 : puerta A en configuracin de entrada Bit 3 : mitad superior de puerta C dont care Bit 2 : seala Modo 1 al grupo B Bit 1 : puerta B en configuracin de salida Bit 0 : mitad inferior de puerta C dont care

Microcomputadores e Interfaces 33

La interfaz de Perifrica Programable (PPI)

Programacin de la PPI De acuerdo al Byte de Comando, se programan los Modos y la Configuracin de las Puertas Ejemplo 05:

7 1 6 1 5 X 4 X 3 X 2 1 1 0 0 X

Bit 7 : habilita byte de comando Bites 6 y 5 : sealan Modo 2 al grupo A Bit 4 : puerta A en configuracin de entrada y salida Bit 3 : mitad superior de puerta C dont care Bit 2 : seala Modo 1 al grupo B Bit 1 : puerta B en configuracin de salida Bit 0 : mitad inferior de puerta C dont care

Microcomputadores e Interfaces 34

La interfaz de Perifrica Programable (PPI)

Programacin de la PPI De acuerdo al Byte de Comando, se programan los Modos y la Configuracin de las Puertas Ejemplo 06:

7 1 6 1 5 X 4 X 3 X 2 1 1 0 0 X

Bit 7 : habilita byte de comando Bites 6 y 5 : sealan Modo 2 al grupo A Bit 4 : puerta A en configuracin de entrada y salida Bit 3 : mitad superior de puerta C dont care Bit 2 : seala Modo 1 al grupo B Bit 1 : puerta B en configuracin de salida Bit 0 : mitad inferior de puerta C dont care

Microcomputadores e Interfaces 35

La interfaz de Perifrica Programable (PPI)

82C55 : Modo de Operacin 0

Obliga al 82C55 a funcionar como un dispositivo de entrada buffer o como un dispositivo de salida latch (biestables). Todas las puertas pueden ser configuradas en forma independiente, esto significa que cualquiera de ellas puede ser de entrada o salida. Es el mtodo ms tpico en la programacin.

Microcomputadores e Interfaces

36

La interfaz de Perifrica Programable (PPI)

LABORATORIO : MICROCOMPUTADORES E INTERFACES EXPERIENCIA : Transmisin y recepcin de datos. OBJETIVOS : Entender la manera como la CPU enva y recibe datos desde otros dispositivos Aprender a programar una Interfaz Programable Perifrica PPI. Detectar un nmero de pulsos y desplegarlos por visores numricos

Microcomputadores e Interfaces

37

La interfaz de Perifrica Programable (PPI)

Las direcciones empleadas para la PPI del Entrenador MTS-88C son las siguientes:

A1 1 1 1 1

A0 0 1 2 3

Funcin Puerto A Puerto B Puerto C

Registro de Comando

Microcomputadores e Interfaces

38

La interfaz de Perifrica Programable (PPI)

Caractersticas del transceptor 74LS245

Microcomputadores e Interfaces

39

La interfaz de Perifrica Programable (PPI)

Transmisin de datos desde acumulador a puerta B

+ 5 v C.C

DISPLAY DE LEDS DEL DIGILAB

40 39 38 37 36 35 34 33

IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0 INTERF AZ DEL MICROP .

32 31 30 29 28 27 26 1

CK1 OUT 1 OUT 2 GAT 2 GAT 1 PCLK VCC GND

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

1 2 3 4 5 6 7 8 9 19

DIR

VCC

20 18 17 16 15

LS245

14 13 12 11

GND

10

Microcomputadores e Interfaces

40

La interfaz de Perifrica Programable (PPI)

Diagrama de Flujo Inicio

Programar 82C55 Modo 0 Puerta B de salida

Mueve dato a AL

Escribe AL a puerta B

Fin

Microcomputadores e Interfaces 41

La interfaz de Perifrica Programable (PPI)

Programa 0000:0400 MOV AL,80 0000:0402 OUT 13,AL 0000:0404 MOV AL,FF 0000:0406 OUT 11,AL 0000:0408 HLT ; carga AL con byte de control ; se selecciona Modo 0 y configura puerta B como salida ; carga AL con FFh ; escribe a la puerta B ; detenga programa

Microcomputadores e Interfaces

42

La interfaz de Perifrica Programable (PPI)

Recepcin de datos en el acumulador desde puerta B

INTERRUPTORES DEL DIGILAB

+ 5 v C.C

0 1

0 1

0 1

0 1

0 1

0 1

0 1

0 1

40 39 38 37 36 35 34 33

IR7 IR6 IR5 IR4 IR3 IR2 IR1 IR0 INTERFA Z DEL MICROP.

32 31 30 29 28 27 26 1

CK1 OUT 1 OUT 2 GAT 2 GAT 1 PCLK VCC GND

PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

1 2 3 4 5 6 7 8 9 19

DIR

VCC

20 18 17 16 15

LS245

14 13 12 11

GND

10

Microcomputadores e Interfaces

43

La interfaz de Perifrica Programable (PPI)

Diagrama de Flujo Inicio

Programar 82C55 Modo 0 Puerta B de entrada

Lee dato desde puerta B

Fin

Microcomputadores e Interfaces 44

La interfaz de Perifrica Programable (PPI)

Programa 0000:0400 MOV AL,90 0000:0402 OUT 13,AL 0000:0404 IN al,11 0000:0406 HLT ; carga AL con byte de control ; se selecciona Modo 0 y configura puerta B como entrada ; lee puerta B ; detiene programa

Microcomputadores e Interfaces

45

La interfaz de Perifrica Programable (PPI)

Deteccin por pulsos

+5V 4.7K 40 IR7 39 IR6 38 IR5 37 IR4 36 IR3 35 IR2 34 IR1 33 IR0 PA0 2 PA1 3 PA2 4 PA3 5 PA4 6 PA5 7 PA6 8 PA7 9 PB0 10 PB1 11 PB2 12 PB3 13 PB4 14 PB5 15 PB6 16 PB7 17

MAN74A Gnd

MAN74A Gnd

DECODER 7448 1 DIR VCC 20 2 A1 B1 18 3 A2 B2 17 4 A3 B3 16 5 A4 245 B4 15 6 A5 B5 14 7 A6 B6 13 8 A7 B7 12 9 A8 B8 11 19 EN GND 10 1B VCC 16 2C f 15 3 LT g 14 4 RGO a 13 5 RGI b 12 6D c 11 7A d 10 8 NC e9 DECODER 7448 1B VCC 16 2C f 15 3 LT g 14 4 RGO a 13 5 RGI b 12 6D c 11 7A d 10 8 NC e9

abcdefg.

abcdefg.

32 CK1 31 OUT2 30 OUT1 PC0 18 29 GAT2 PC1 19 28 GAT1 PC2 20 27 PCLK PC3 21 26 VCC PC4 22 1 GND PC5 23 PC6 24 PC7 25

Microcomputadores e Interfaces

46

La interfaz de Perifrica Programable (PPI)

Diagrama de Flujo

Inicio Borre AX Programar 82C55 Modo 0 Puerta A de entrada Puerta B de salida

Lee puerta A

PA0 = 1

Escribe AL a puerta B Retardo de tiempo Microcomputadores e Interfaces 47

La interfaz de Perifrica Programable (PPI)

Programa

0000:0400 0000:0402 0000:0404 0000:0406 0000:0408 0000:040B 0000:040D 0000:040F 0000:0411 0000:0413 0000:0416 0000:0419 0000:041A 0000:041C 0000:041E 0000:0421 XOR AX,AX MOV AL,90 OUT 13,AL IN AL,10 TEST AL,01 JNE 0406 INC AH MOV AL,AH OUT 11,AL MOV CX,0010 MOV BX,0500 DEC BX JNE 0419 LOOP 0416 JMP 0406 HLT ; borra AX ; carga AL con byte de control ; saca byte de control a puerta Control ; lee puerta A ; chequea estado del switch ; si switch est abierto rechequea ; AH=AH+1 ; escribe a puerta B ; pone retardo de tiempo ; BX=BX-1 ; salta a direccin 0419 si BX0 ; ejecuta ciclo si CX0 ; salta a direccin 0406 ; detiene programa

Microcomputadores e Interfaces 48

La interfaz de Perifrica Programable (PPI)

82C55 : Modo de Operacin 1 entrada controlada por pulso

Obliga a que los puertos A y/o B del 82C55 funcionen como dispositivos de entrada con registro. Esto permite almacenamiento de datos externos en el puerto hasta que el microprocesador est listo para recuperarlos. El puerto C tambin es empleado en el modo de operacin 1, no para datos, sino para seales de control o de respuesta que ayudan en la operacin de los puertos ya sea A o B, o ambos como puertos de entrada controlados por pulsos. El puerto de entrada controlado por pulsos captura datos de las terminales del puerto cuando se activa la seal de reloj STB. El puerto captura los datos durante la transicin de 0 a 1 del pulso STB La seal STB, activa las seales de buffer de entrada lleno IBF y de solicitud de interrupcin INTR Una vez que el microprocesador reconoce, por medio de software (IBF) o de hardware (INTR) que un dato est almacenado en el puerto, ejecuta una instruccin IN para leer el puerto (RD) Al leer el puerto, se restituyen a sus estados inactivos tanto IBF e INTR.

Microcomputadores e Interfaces 49

La interfaz de Perifrica Programable (PPI)

Definiciones de seal para entrada controlada por pulsos en modo 1

STB La entrada pulso (strobe) carga datos al regsitro del puerto, el cual mantiene la informacin hasta que es transferida al microprocesador por medio de la instruccin IN. IBF Buffer de entrada lleno es una salida que indica que el registro de entrada contiene informacin. INTR Solicitud de interrupcin es una salida que solicita una interrupcin de hardware al microprocesador. La terminal INTR asume un estado de 1 lgico cuando la entrada STB regresa al valor de 1 lgico, y es restituida cuando el dato es transferido desde el puerto al microprocesador. INTE La seal de habilitacin de interrupcin no es una entrada ni salida; es un bit interno programado por medio de la posicin PC4 (puerto A) o PC2 (puerto B)

PC7, PC6

Terminales 7 y 6 de E/S, son de propsitos generales y disponibles.

Microcomputadores e Interfaces 50

La interfaz de Perifrica Programable (PPI)

Puertos A y B (entrada) en Modo 1

Puerto A INTE A PC4 PC5 STBA IBFA INTE B PC2 PC1

Puerto B STBB IBFB

RD

PC3 PC6+7

INTRA RD E/S

PC0

INTRB

Byte de Control D7 D6 D5 D4 D3 D2 D1 D0 1 0 1 1 X X X X D7 1 X

Byte de Control D6 D5 D4 D3 D2 D1 D0 X X X 1 1 X

51

Microcomputadores e Interfaces

Operacin de entrada controlada por pulsos (Modo 1)

STB

IBF INTR RD

Buffer lleno Interrupcin solicitada

PUERTO

Dato de entrada escrito al puerto

Dato ledo por microprocesador

52

Microcomputadores e Interfaces

La interfaz de Perifrica Programable (PPI)

Ejemplo de un procedimiento donde el microprocesador lee un carcter ASCII que ingresa por la puerta A MOV MOV OUT READ_C MOV IN TEST JZ MOV IN MOV HLT AL,0BC DX,13 DX,AL DX,12 AL,DX AL,00100000 READ_C DX,10 AL,DX [0200],AL ; pone byte de control ; pone direccin de Control ; ; obtiene direccin de puerta C ; obtiene estado de puerta C ; chequea si IBF = 1 (PC5) ; si IBF = 0 vuelve a chequear ; obtiene direccin de puerta A ; ingresa ASCII de puerta A a AL ; salva dato en direccin de memoria

Microcomputadores e Interfaces

53

La interfaz de Perifrica Programable (PPI)

82C55 : Modo de Operacin 1 salida controlada por pulso Su operacin es parecida a la de entrada controlada por pulsos en modo 0, excepto que se incluyen seales de control para proporcionar respuesta. Siempre que se escriben datos a un puerto programado como puerto de salida controlado por pulsos, la seal buffer de salida lleno, OBF, asume el estado de 0 lgico para indicar la existencia de datos en el registro del puerto. Esta seal indica a un dispositivo externo de E/S que hay datos disponibles. El dispositivo externo responde al puerto que ha ledo los datos del registro del puerto, activando la entrada de reconocimiento, ACK, del puerto. La seal ACK restituye la seal OBF a 1 lgico, indicando que el buffer est desocupado.

Microcomputadores e Interfaces 54

La interfaz de Perifrica Programable (PPI)

Definiciones de seal para salida controlada por pulsos en modo 1 OBF Es una salida que asume el estado bajo siempre que los datos sean escritos (OUT) al registro de los puertos A o B. Esta seal es restituda a 1 lgico siempre que el pulso ACK es retornado desde un dispositivo externo. ACK La seal de reconocimiento ocasiona que la terminal OBF regrese al nivel lgico de 1. La seal ACK indica que el dispositivo externo recibio el dato. INTR La solicitud de interrupcin es una seal que freceuntemente interrumpe al microprocesador cuando el dispositivo externo recibe el dato por medio de la seal ACK. Esta terminal es calificada por el bit interno de habilitacin de interrupcin (INTE).

Microcomputadores e Interfaces 55

La interfaz de Perifrica Programable (PPI)

Definiciones de seal para salida controlada por pulsos en modo 1 INTE La seal de habilitacin de interrupcin no es una entrada ni salida; es un bit interno programado para habilitar o deshabilitar la terminal INTR. El bit INTE A es programado como PC6 e INTE B es programado como PC2. Las terminales 4 y 5 del puerto C son terminales de E/S de propsito general. El comando de establecimiento y restauracin puede ser usado para controlar estas terminales.

PC5 PC4

Microcomputadores e Interfaces

56

La interfaz de Perifrica Programable (PPI)

Puertos A y B (salida) en Modo 1

Puerto A INTE A PC7 PC6 OBFA ACKA INTE B PC1 PC2

Puerto B OBFB ACKB

RD

PC3 PC4+5

INTRA RD E/S

PC0

INTRB

Byte de Control D7 D6 D5 D4 D3 D2 D1 D0 1 0 1 0 X X X X D7 1 X

Byte de Control D6 D5 D4 D3 D2 D1 D0 X X X 1 0 X

57

Microcomputadores e Interfaces

Operacin de salida controlada por pulsos (Modo 1)

WR OBF Buffer lleno INTR

Interrupcin solicitada

ACK

PUERTO

Dato enviado al puerto

Dato extrado del puerto

58

Microcomputadores e Interfaces

Operacin de salida controlada por pulsos (Modo 1)

Ejemplo de un procedimiento donde el microprocesador saca un carcter ASCII que ingresa por la puerta B MOV MOV OUT DEC READ_C IN TEST JZ MOV MOV OUT HLT AL,0BC DX,13 DX,AL DX AL,DX AL,00000010 READ_C DX,11 AL,[0200] DX, AL ; pone byte de control ; pone direccin de Control ; ; DX = DX-1 ; obtiene estado de puerta C ; chequea si OBF = 1 (PC2) ; si OBF = 0 vuelve a chequear ; obtiene direccin de puerta B ; carga ASCII de memoria a AL ; ingresa dato acumulador a puerta B

Microcomputadores e Interfaces

59

La interfaz de Perifrica Programable (PPI)

Combinaciones de Modo 1 PUERTA C PC0 PC1 PC2 PC3 PC4 PC5 PC6 PC7 ENTRADA INTRB IBFB STBB INTRA STBA IBFA I/O I/O SALIDA INTRB OBFB ACKB INTRA I/O I/O ACKA OBFA

Microcomputadores e Interfaces

60

La interfaz de Perifrica Programable (PPI)

Combinaciones de Modo 1

PA7 PA0 PC4 PC5 PC3 PC6 PC7 PB7 PB0 PC1 PC2 PC0 OBFB ACKB INTRB STBA IBFA INTRA I/O PA7 PA0 PC7 PC6 PC3 PC4 PC5 PB7 PB0 PC2 PC1 PC0 STBB IBFB INTRB OBFA ACKA INTRA I/O

Microcomputadores e Interfaces

61

La interfaz de Perifrica Programable (PPI)

82C55 : Operacin bidireccional en modo 2 En el modo 2, permitido solamente con el grupo A, el puerto A se convierte en bidireccional, permitiendo la transmisin y recepcin de datos a travs de los mismos ocho conductores. Los buses bidireccionales de datos son tiles para interconectar a dos computadoras

Microcomputadores e Interfaces

62

La interfaz de Perifrica Programable (PPI)

Definiciones de seal para el modo 2 bidireccional INTR

Solicitud de interrupcin es una salida utilizada para interrumpir al microprocesador para ambas condiciones de entrada y de salida. Buffer de salida lleno es una salida que indica que el buffer de salida contiene un dato para el bus bidireccional. Reconocimiento es una entrada que habilita los buffers de 3 estados de forma que pueda aparecer un dato en el puerto A. Si ACK es un 1 lgico, los buffers de salida del puerto A estn en su estado de alta impedancia. La entrada pulso de datos carga el registro de entrada del puerto A con dato externo desde el bus bidireccional del puerto A.

Microcomputadores e Interfaces 63

OBF

ACK

STB

La interfaz de Perifrica Programable (PPI)

Definiciones de seal para el modo 2 bidireccional IBF Buffer de entrada lleno es una salida utilizada para indicar que el buffer de entrada contiene un dato para el bus bidireccional externo. INTE Habilitacin de interrupcin son bist internos (INTE1 e INTE2) que habilitan la terminal INTR. El estado de la terminal INTR es controlado por medio de los bits PC6 (INTE1) y PC4 (INTE2) del puerto C. PC2, PC1 Y PC0

Estas son terminales de E/S de propsito general en el modo 2 controlados por los comandos de establecimiento y restauracin de bits.

Microcomputadores e Interfaces

64

La interfaz de Perifrica Programable (PPI)

PC3

INTR PUERTO A

PC7

INTE 1

OBF ACK

PC6

INTE 2

PC4 PC5

STB IBF E/S

PC2 - PC0

Microcomputadores e Interfaces

65

La interfaz de Perifrica Programable (PPI)

Diagrama de tiempos en modo 2

WR OBF INTR ACK STB

IBF PORT A RD Dato almacenado en el puerto A Dato de salida (OUT) al puerto A Dato ledo del puerto A Dato de entrada (IN) desde el puerto A

Microcomputadores e Interfaces

66

La interfaz de Perifrica Programable (PPI)

Definiciones de seal de entrada

Microcomputadores e Interfaces

67

Vous aimerez peut-être aussi

- Mantenimiento de Máquinas Eléctricas - Juan Jimenez PDFDocument233 pagesMantenimiento de Máquinas Eléctricas - Juan Jimenez PDFcarg29100% (1)

- Meg Oh MetroDocument18 pagesMeg Oh MetroMaguiña Polanco EricPas encore d'évaluation

- Mantenimiento de Máquinas Eléctricas - Juan Jimenez PDFDocument233 pagesMantenimiento de Máquinas Eléctricas - Juan Jimenez PDFcarg29100% (1)

- Ley 19.712 y Politica NacionalDocument15 pagesLey 19.712 y Politica NacionalFernando Felipe Tapia OrdenesPas encore d'évaluation

- Problemas MotoresDocument2 pagesProblemas MotoresJonathan TejadaPas encore d'évaluation

- Guà A SMA Termoelectricas VFDocument25 pagesGuà A SMA Termoelectricas VFElizabeth Cares LiraPas encore d'évaluation

- Balanza y TacometroDocument4 pagesBalanza y TacometroFernando Felipe Tapia OrdenesPas encore d'évaluation

- Electronic A Teoria de Circuitos 6 Ed BoylestadDocument655 pagesElectronic A Teoria de Circuitos 6 Ed BoylestadFrancisco Diaz75% (4)

- Conceptos Generales Energía FotovoltaicaDocument20 pagesConceptos Generales Energía FotovoltaicaFernando Felipe Tapia OrdenesPas encore d'évaluation

- Capitulo IV Interfaz SerieDocument26 pagesCapitulo IV Interfaz SerieFernando Felipe Tapia OrdenesPas encore d'évaluation

- Pert-CpmDocument53 pagesPert-CpmFrancisco Aracena VidelaPas encore d'évaluation

- Pert-CpmDocument53 pagesPert-CpmFrancisco Aracena VidelaPas encore d'évaluation

- Sistema de Control Por ComputadorDocument7 pagesSistema de Control Por ComputadorFernando Felipe Tapia OrdenesPas encore d'évaluation

- Listado 1Document3 pagesListado 1Fernando Felipe Tapia OrdenesPas encore d'évaluation

- Tarea 1 Diplomado UCDocument3 pagesTarea 1 Diplomado UCFernando Felipe Tapia OrdenesPas encore d'évaluation

- SilicosisDocument20 pagesSilicosisFernando Felipe Tapia OrdenesPas encore d'évaluation

- Ejercicio Prueba DACDocument2 pagesEjercicio Prueba DACFernando Felipe Tapia OrdenesPas encore d'évaluation

- Electrónica de Comunicaciones (1994) - Manuel Sierra PerezDocument170 pagesElectrónica de Comunicaciones (1994) - Manuel Sierra Perezmao20008Pas encore d'évaluation

- TME Construccion ACHS WebDocument23 pagesTME Construccion ACHS Webtomachoc1978100% (1)

- Lenguaje Ensamblador y Programacion para IBM PC y Compatibles Capitulo 1 Al 15Document283 pagesLenguaje Ensamblador y Programacion para IBM PC y Compatibles Capitulo 1 Al 15Jean Carlo CanevelloPas encore d'évaluation

- Arquitectura de La CpuDocument54 pagesArquitectura de La CpuFernando Felipe Tapia OrdenesPas encore d'évaluation

- Unidad1 Panorama Del Hardware de La IBM PCDocument31 pagesUnidad1 Panorama Del Hardware de La IBM PCtcondesPas encore d'évaluation

- Registro de BanderasDocument9 pagesRegistro de BanderasRubí Cruz HernandezPas encore d'évaluation

- Capitulo III - Interfaz ParalelaDocument72 pagesCapitulo III - Interfaz ParalelaJorge Gianotti HidalgoPas encore d'évaluation

- Capítulo 3: Familias TMS320 de Texas InstrumentsDocument12 pagesCapítulo 3: Familias TMS320 de Texas Instrumentsivan aguilaPas encore d'évaluation

- Ensamblador UVM PDFDocument59 pagesEnsamblador UVM PDFAbel Diaz Olivares100% (1)

- SIMULADORDocument14 pagesSIMULADORCristian Flores MartínezPas encore d'évaluation

- Manual RockwellDocument36 pagesManual RockwellJesus SallasPas encore d'évaluation

- Arquitectura Computadores PDFDocument23 pagesArquitectura Computadores PDFJulio BarreraPas encore d'évaluation

- Arquitectura Basica Microprocesador IntelDocument56 pagesArquitectura Basica Microprocesador IntelEdgar OrdoñezPas encore d'évaluation

- Nocionnes Del EnsamblerDocument6 pagesNocionnes Del EnsamblerJepsi AvilaPas encore d'évaluation

- Temadeestudio PDFDocument123 pagesTemadeestudio PDFjuan alarconPas encore d'évaluation

- Guia de Taller Microprocesadores 2Document11 pagesGuia de Taller Microprocesadores 2Jed SigPas encore d'évaluation

- Tema 03 - Diseño y Arquitectura de Los Microprocesadores 8086 y 8088Document18 pagesTema 03 - Diseño y Arquitectura de Los Microprocesadores 8086 y 8088Carlos E HernandezPas encore d'évaluation

- Arquitectura Del Microprocesador z80Document9 pagesArquitectura Del Microprocesador z80Nilyan BertiPas encore d'évaluation

- Modelo 16 BitsDocument5 pagesModelo 16 BitsSebastián GiroPas encore d'évaluation

- Microprocesadores - Clase 02 - Arquitectura Del 8086Document46 pagesMicroprocesadores - Clase 02 - Arquitectura Del 8086Bruss Deyre Tasayco VigoPas encore d'évaluation

- Repertorio de Instrucciones Del 8086 PDFDocument16 pagesRepertorio de Instrucciones Del 8086 PDFjosedavid0115Pas encore d'évaluation

- Microprocesador 1 - 2 PDFDocument72 pagesMicroprocesador 1 - 2 PDFMar YfhPas encore d'évaluation

- Taller N 1 Arquitectura ComputadoresDocument11 pagesTaller N 1 Arquitectura ComputadoresSKAYLERPas encore d'évaluation

- UTP Capitulo 8 Organizacion de RegistrosDocument32 pagesUTP Capitulo 8 Organizacion de RegistrosHelen Gem Ma GarciaPas encore d'évaluation

- Z267-Practica de Laboratorio Calificado 1 40482Document9 pagesZ267-Practica de Laboratorio Calificado 1 40482Kevin Avilés TorresPas encore d'évaluation

- Imprimir SistDocument17 pagesImprimir SistAlex Jr SullnPas encore d'évaluation

- Guia 3 PDFDocument8 pagesGuia 3 PDFFabian FlorezPas encore d'évaluation

- ATmega164p GuideDocument378 pagesATmega164p GuideGeorge Yánez CajasPas encore d'évaluation

- Virus Hack - Desde Que Pulsamos El Botón de Nuestra PC HastaDocument127 pagesVirus Hack - Desde Que Pulsamos El Botón de Nuestra PC HastaCarlos C. AlvarezPas encore d'évaluation

- Examen Final II Arquitectura ComputadorasDocument11 pagesExamen Final II Arquitectura ComputadorasHector ChecasovichPas encore d'évaluation

- Ensamblador Direccionamiento en Modo Real y ProtegidoDocument3 pagesEnsamblador Direccionamiento en Modo Real y ProtegidoMiguel Angel Ordoñez GayonPas encore d'évaluation

- Microcontroladores Freescale MLCDocument7 pagesMicrocontroladores Freescale MLCMarthaPas encore d'évaluation

- Arquitectura Del Procesador X86Document9 pagesArquitectura Del Procesador X86Jean Paul PereaPas encore d'évaluation

- Finales Resueltos de Sistemas OperativosDocument288 pagesFinales Resueltos de Sistemas OperativosgerPas encore d'évaluation