Académique Documents

Professionnel Documents

Culture Documents

ECEM323 Laboratory Manual (Dante)

Transféré par

Danilyn Padillo LucioCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

ECEM323 Laboratory Manual (Dante)

Transféré par

Danilyn Padillo LucioDroits d'auteur :

Formats disponibles

Ateneo de Naga University

College of Engineering ECE /CpE Department

Logic Circuits and Switching Theory

ECEM323

LABORATORY MANUAL

Engr. Gilbert D. Detera

TOC

TABLE OF CONTENTS

Activity 1

7-SEGMENT LED DISPLAY DECODER

Activity 2 SEVEN SEGMENT DRIVER/DECODER and ENCODER

Activity 3

MULTIPLEXER AND MAGNITUDE COMPARATOR

Activity 4

BCD ADDER

Activity 5

LATCH AS A MEMORY DEVICE

Activity 6

COUNTERS USING FLIP-FLOPS

Activity 7

SHIFT REGISTERS

Activity

1 7-SEGMENT LED DISPLAY DECODER

INFORMATION Boolean Algebra is a mathematical expression that solve logical operation to its equivalent algebraic equation. The binary operations (+) stands for logical OR and ()stands for logical AND. This is some basic laws of Boolean algebra:

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

x + (x y) = x x (x + y) = x x + x = 1 x x = 0 Multisim Logic Converter is a tool that assists users to convert the truth table to its corresponding logic expression including: conversion of truth table to its boolean expression, conversion of boolean expression to its truth table, simplified boolean expression, conversion of a boolean expression to its equivalent circuit, and conversion of a boolean expression to its circuit using only NAND gates. A seven segment display, as its name indicates, is composed of seven elements. Individually on or off, they can be combined to produce simplified representations of numerals.

The seven segments are arranged as a rectangle of two vertical segments on each side with one horizontal segment on the top, middle, and bottom. Additionally, the seventh segment bisects the rectangle horizontally. There are also fourteen-segment displays and sixteen-segment displays (for full alphanumerics); however, these have mostly been replaced by dot-matrix displays. 7-segment Light Emitting Diode decoder provides way of displaying information or digital data in the form of numbers, letters or even alpha-numerical characters. Some applications of it are digital clocks, electronic meters, and other electronic devices for displaying numerical information. There are two important types of 7-segment LED digital display:

The Common Cathode Display (CCD) - In the common cathode display, all the cathode connections of the LED's are joined together to logic "0" and the individual segments are illuminated by application of a "HIGH", logic "1" signal to the individual Anode terminals.

Page 1

Laboratory Exercise No. 1

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

The Common Anode Display (CAD) - In the common anode display, all the anode connections of the LED's are joined together to logic "1" and the individual segments are illuminated by connecting the individual Cathode terminals to a "LOW", logic "0" signal.

OBJECTIVES

To design the truth table of common cathode seven-segment LED display decoder using logic zero as an output for unused states. To apply Boolean Algebra in generating the seven-segment LED display decoder equations and simplifying the logic expressions from the given truth table. To get acquainted with the Logic Converter feature of Multisim 11 as an alternative tool in generating and simplification of Boolean equation from the given truth table. To construct a common cathode seven-segment LED display decoder diagram through Multisim 11, indicating the numbers 0-9.

MATERIALS/EQUIPMENT

PC/laptop with pre-installed Multisim 11

PROCEDURE Prelab 1. Construct a truth table having 4 inputs and 7 outputs indicating every segment of the common cathode LED display. Table 1 serves as an example.

2. In the truth table for FIGURE ZERO, segments a, b, c, d, e and f

should all be ON while segment g is OFF. For FIGURE ONE, b and g should be ON while the rest are OFF.

Laboratory Exercise No. 1

Page 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

3. Complete the table for numbers 3 up to 9. 4. Using Boolean Algebra, generate the equations for segments a, b, c,

d, e, f and g. Write the simplified equations in Table 2.

Note: Be reminded that for the common cathode configuration, 0 means OFF and 1 means ON.

Lab Proper 1. Using Logic converter on the Multisim 11,

place 4 inputs (A, B, C, D) and plug-in the binary codes of every output from a-g. In this activity, use 0 instead of x in output 10-15.

Laboratory Exercise No. 1

Page 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

2. Using the truth table to simplified equation button of Logic Converter, generate the equations for segments a, b, c, d, e, f and g. Write the simplified equations in Table 3. 3. For every output (a-g) accomplished, generate the corresponding logic circuits and connect every output to its LED terminal. 4. For the input side of the logic circuits, connect pins A, B, C, and D respectively and assign an SPDT switch for each. After which, connect a 5V VCC. 5. Test the circuit by turning on/off the different switch combinations.

FOLLOW UP ACTIVITY Following the same concept and procedure in this activity, do the sevensegment common anode configuration.

Note: LED terminal assignments of the common anode configuration are just the opposite of the common cathode arrangement.

TABLES A B C D 0 1 2 3 4 5 6 0 0 0 0 0 0 0 0 0 0 0 1 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 a b c d e f g

1 1 1 1 1 1 0 0 1 1 0 0 0 0 1 1 0 1 1 0 1

Laboratory Exercise No. 1

Page 4

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

7 8 9 Segment a b c d e f g

0 1 1

1 0 0

1 0 0

1 0 1

Table 1

Boolean Equation (Boolean Algebra)

Table 2

Segment a b c d e f g

Boolean Equation (Logic Converter)

Table 3

Laboratory Exercise No. 1

Page 5

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

SCHEMATIC DIAGRAM Draw the complete schematic diagram here: -4 SPDT connected either to supply voltage Vcc (as logic 1 input) or ground (as logic 0 input) -Decoder circuit: segment a, b, c, d, e, f and g diagram -Output display: 7-segment display or 7-LEDs or 7-logic probes

ANALYSIS / OBSERVATION:

Laboratory Exercise No. 1

Page 6

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

CONCLUSION:

Laboratory Exercise No. 1

Page 7

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Activity

2

SEVEN SEGMENT DRIVER/DECODER and ENCODER

INFORMATION The 7-segment display which includes the encoder and the decoder is being used in many different ways. Because it has many uses and resources are limited, we must be aware that in constructing it, there are ways on how to simplify the equations, reduce the number of gates and ICs (Integrated Circuits) to be used. A decoder as observed on the previous laboratory activity is composed of the gate combinations that each corresponds to a particular output connected to the LED display and inputs connected to the switches. As to the encoder, it is a device designed to make a more efficient way to give commands as to what the 7-segment display must show, for example if the user press 4 on the keyboard the number 4 will also be displayed. The introduction of the method DONT CARE X had made it much simpler to do the decoder. Through this everything was reduced to its simplest form and interconnection of circuits having the same or repeated equation part was made possible. OBJECTIVES To design the truth table of common cathode seven-segment LED display decoder using dont care (x) as an output for unused states. To apply Boolean Algebra in generating the seven-segment LED display decoder equations and simplifying the logic expressions from the given truth table. To learn more about reducing the number of gates in a circuit for the 7 segment decoder.

Page 1

Laboratory Exercise No. 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Derive the simplified Boolean expressions for the encoder circuit. Construct logic circuits manually given only the Boolean expressions. Combining the encoder and the same concept of decoder on the previous activity, light up the seven segment display by encoding, this time, the number 0-9. To learn more about reducing the number of gates in a circuit for the 7 segment decoder.

MATERIALS/EQUIPMENT PC/laptop with pre-installed Multisim 11

PROCEDURE Prelab 1. Construct a truth table for 7-segment common cathode display decoder similar to that of the previous activity, observing that the output 10-15 now bears the value of dont care (x). Table 1 serves as an example. Complete the table for numbers 3 up to 9. 2. Using Boolean Algebra, generate the equations for segments a, b, c, d, e, f and g. Write the simplified equations in Table 2.

3. Research the truth table of 10-line to 4-line priority encoder. Write the corresponding output equations in Table 3.

Lab Proper 1. Using the Logic Converter of Multisim 11, generate the output equations of decoder (a, b, c, d, e, f and g) from the values of Table 1. Write the simplified equations in Table 4. 2. Construct the decoder diagram using Multisim 11 to create the 7 combinations of logical gates, each corresponding to the output equations in Table 4. Dont use the logic converter to generate the equivalent diagram. 3. With the 7 set of logical gates construct, simplify the diagram by combining those having the same part of equation. Replace it with a sub circuit and connect the pins into their respective inputs and outputs. Label it as decoder. 4. Based from the simplified equations in Table 3, do the same procedure to construct the diagram of priority encoder. Label it as encoder.

Laboratory Exercise No. 2 Page 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

5. Connect the output of the encoder to the input of decoder, and the output of decoder to the input of the indicator. Note: Observe proper component labeling. Avoid name repetitions. 6. Connect each input of the encoder with SPDT switch and connect it all to a 5v VCC. 7. Test the circuit by switching on each switch to get the desired numerical output. FOLLOW UP ACTIVITY Following the same concept and procedure in this activity, do the sevensegment common anode configuration. Note: LED terminal assignments of the common anode configuration are just the

opposite of the common cathode arrangement.

RESULTS TABLES: A B C D 0 1 2 3 4 5 6 7 8 9 10

Laboratory Exercise No. 2

a b c

d e f

0 0 0 0 0 0 0 0 1 1 1

0 0 0 0 1 1 1 1 0 0 0

0 0 1 1 0 0 1 1 0 0 1

0 1 0 1 0 1 0 1 0 1 0

1 1 1 1 1 1 0 0 1 1 0 0 0 0 1 1 0 1 1 0 1

x x x x x x x

Page 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

11 12 13 14 15

1 1 1 1 1

0 1 1 1 1

1 0 0 1 1

1 0 1 0 1

x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x

Table 1

Segment a b c d e f g

Boolean Equation (Boolean Algebra)

Table 2 Decoder

Output A B C D

Boolean Equation

Table 3 Encoder

Segment a b c

Laboratory Exercise No. 2

Boolean Equation (Logic Converter)

Page 4

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

d e f g

Table 4 Decoder

SCHEMATIC DIAGRAM Draw the complete schematic diagram here: -10 SPDT connected either to supply voltage Vcc (as logic 1 input) or ground (as logic 0 input) -Encoder circuit: Output A, B, C and D -Decoder circuit: segment a, b, c, d, e, f and g diagram -Output display: 7-segment display or 7-LEDs or 7-logic probes

ANALYSIS / OBSERVATION:

Laboratory Exercise No. 2

Page 5

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

CONCLUSION:

Laboratory Exercise No. 2

Page 6

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Activity

3

MULTIPLEXER AND MAGNITUDE COMPARATOR

INFORMATION In this experiment new devices such as Multiplexer and Magnitude Comparator are introduced. A multiplexer or mux is a device that performs multiplexing, it selects one of many analog or digital input signals and forwards the selected input into a single line. A multiplexer of 2n inputs has n select lines, which are used to select which input line to send to the output. An electronic multiplexer makes it possible for several signals to share one device or resource, for example one A/D converter or one communication line, instead of having one device per input signal. A magnitude comparator is a hardware electronic device that takes two numbers as input in binary form and determines whether one number is greater than, less than or equal to the other number. Comparators are used in a central processing units (CPU) and microcontrollers. Examples of digital comparator include the CMOS 4063 and 4585 and the TTL 7485 and 74682-'89. OBJECTIVES To learn about the use of a Multiplexer and a Magnitude Comparator in a circuit. To compare different inputs using the magnitude comparator together with LEDs as indicators. To display numbers from 0-9 with the common cathode seven segment display and switch whichever number is desired to be displayed by altering the switch that represents to Encoder A and encoder B.

Page 1

Laboratory Exercise No. 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

MATERIALS/EQUIPMENT PC/laptop with pre-installed Multisim 11

PROCEDURE Prelab 1. Find models of the following components: Encoder Decoder Multiplexer Magnitude Comparator Seven segment display (Common Cathode) 2. Browse the internet for more information about each component and for the datasheets of specific models whose product design suits the virtual components of Multisim 11. 3. Study the datasheets to know more about the components and the factors that shall affect the circuit as a whole. Lab Proper Part 1: Multiplexer 1. Setup the two different encoders according to how it works properly during pre lab activity. There should be nine switches in the input of encoder A and nine switches in encoder B. 2. The outputs of the encoder A will be connected in the inputs A of the multiplexer. Connect according to which are the MSB and LSB. Also, the outputs of the encoder B will be connected in the inputs B of multiplexer. 3. Setup the decoder as planned in the pre lab activity. Now, connect the for output pins of the multiplexer to the input pins of the decoder. Also, connect according to MSB and LSB. 4. Use a SPDT switch in the selector pins. If the selector has two pins for selector, connect the two pins in the two throws of the switch. Connect a Vcc in the other end of the switch. The selection of the pin will be based on the pin that is supplied by the voltage.

Laboratory Exercise No. 3 Page 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

5. Turn on the Vccs and select the inputs according to Table 1. Record the corresponding output display.

Part 2: Magnitude Comparator 1. The setup used in the part 1 of the activity will be used for this part of the activity. 2. Connect the A>B and A<B pin in the ground while the A=B pin will be connected to a Vcc. This may be connected before testing of results. 3. Connect the outputs of encoder A in the inputs A of the comparator and same thing with the outputs of encoder B in the inputs B of the same comparator. Connection should follow the MSB and LSB. 4. Connect the output of A>B in series with the 470 resistor and a red LED. The output of A=B is connected with 470 and green LED. And lastly, the output of A<B is connected in series with 470 and a yellow LED. 5. Turn on the Vccs and select the inputs written in Table 2. Record the corresponding LED display.

Laboratory Exercise No. 3

Page 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

FOLLOW UP ACTIVITY Using the same concept, make a circuit that shall display 2 separate digits using 2 seven-segment display but this time the common anode seven-segment display must be used. On the circuit itself, there will be lots of changes on the way it was interconnected because different pins would now be used. Redesigning the circuit is now a must and the components will then be changed. Again, research for the datasheet of the new components and be familiar with its pins. Construct the circuit on the Multisim 11 and make some test to confirm its validity. Some of the inverters which were used in the previous circuit may no longer be of any use now while some would be just transferred at the different parts of the circuit. RESULTS TABLES:

ENCODERS (input) Encode A 0 1 2 3 4 5 6 Encoder B 9 8 7 6 5 4 3 SELECTORS (display output) If selector A If selector B

Laboratory Exercise No. 3

Page 4

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University 7 8 9 0 2 2 1 0 0 2

Table 1

ENCODERS (input) Encode A Encoder B

Output (Color of LED that is ON)

0 1 2 3 4 5 6 7 8 9 0

9 8 7 6 5 4 3 2 1 0 0

Laboratory Exercise No. 3

Page 5

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

2

Table 2

SCHEMATIC DIAGRAM Draw the complete schematic diagram here:

ANALYSIS / OBSERVATION:

CONCLUSION:

Laboratory Exercise No. 3

Page 6

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Activity

4 BCD ADDER

INFORMATION The binary coded decimal (BCD) adder circuit adds two BCD encoded operands and produces a BCD encoded sum and a carry out bit. It includes a bank of parallel full adder circuits as a first stage which generates an intermediate sum vector and an intermediate carry vector from the sum of the operands and a pre-correction factor. A second stage of the BCD adder circuit includes carry look-ahead adder circuitry receiving as inputs the intermediate sum vector and the intermediate carry vector and producing a propagate vector and a final carry vector. The third stage of the BCD adder circuit conditionally modifies the propagate vector to form the BCD encoded sum according to bits of the intermediate carry vector and the final carry vector as inputs. Binary coded decimal numbers are used to represent decimal numbers in a form readily understood by both man (decimal) and computer (binary). There are sixteen possible bit combinations using four binary bits, but only ten are valid BCD digits. Therefore, when two BCD digits are added and the sum digit exceeds nine, that sum digit must be adjusted to a valid BCD digit. This is generally done by adding the constant 0110 2 (6 10) to the sum. Traditionally, BCD adder circuits have used logic to detect whether a BCD sum should be adjusted after the addition has been completed. For example, whenever the unadjusted sum of two BCD digits produced a carryout (i.e., when the sum exceeds fifteen), the sum was corrected by adding 0110 2. Also, an adjustment was needed whenever bit positions 8 and

Laboratory Exercise No. 3 Page 1

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

4 of the BCD sum were both one's (values 12 10 -15 and 2 were both one's (values 10 10 and 11 10).

10)

or when bit positions 8

OBJECTIVES To add/subtract BCD numbers using the 4 bit FULL-ADDER and displaying the digits on Seven-Segment Two-Digit Display and the corresponding operations on Alpha-Numeric Display. To apply the functions of logical gates in obtaining correct results in performing addition or subtraction. In the process of addition, the sum should be corrected by a correction factor. Also, it is required that the same circuit can be switched and can process subtraction. To understand how the 4-bit full adder function and know how each pins are connected to other circuit parts in order to come up with the desired output.

MATERIALS/EQUIPMENT PC/laptop with pre-installed Multisim 11

PROCEDURE Prelab 1. Configure a common-cathode Alpha-Numeric Display such that the plus and minus signs shall be displayed one at a time. This later on will be used at the actual lab activity wherein the plus or minus sign should be displayed accordingly to what operation is desired to be perform by the circuit. This can be done through knowing what the functions are for each pins of the Alpha-Numeric

Laboratory Exercise No. 3 Page 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Display. 2. Using a Seven-Segment One-Digit Display at common cathode configuration, display the equal sign. This will be used to specify the result of the 2 digits to be added or subtracted on the circuit. This display shall be placed before the answer when addition or subtraction was implemented. 3. Study the datasheet of the 4-bit adder that will be used. Lab Proper 1. Construct a circuit that shall have 2 encoders and 2 decoders connected to separate common cathode Seven-Segment Displays. This shall serve as the way in which the numbers to be added or subtracted can be selected. 2. In making the diagram, choose suited Integrated Circuits that can accommodate the total number of inputs and outputs for each Encoder and Decoder. Look for the pin configuration of your chosen IC and connects pins in their proper places. 3. Test the diagram by switching on 1 switch from each of the two 8 item switch pack. The number chosen must be displayed on the Seven-Segment Display.

Laboratory Exercise No. 3

Page 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

4. Search for a 2 identical 4 bit full adders. Connect this with one another and use some gates and switch that shall serve as the ON and OFF of addition and subtraction to facilitate the operation and conversions together with the correcting factors.

5. Combine the completed 4 bit full adder/subtractor with the encoders and decoders. 6. Insert the plus/minus/equal signs and arranged it in such a way that the displays shall resemble an equation for better appearance.

Laboratory Exercise No. 3

Page 4

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

7. Test the circuit by selecting numbers to be added/subtracted then switch operations to addition/subtraction. Record the results in Table 1.

FOLLOW UP ACTIVITY In the Actual Lab part, the 4 bit adder used was in the form of Integrated Circuit. With this practice, it is easy to identify connections and how to place the IC properly in the circuit by just looking at its pin configuration. To further understand the concept of a 4 bit adder, it is suggested that the components inside the IC must be studied and how it works in the circuit in order to perform desired operations. In this part of the activity, construct a circuit consisted by logic gates to form a 4 bit adder. Look for a schematic diagram of a 4 bit adder then simplify the figure with the use of Boolean Algebra to lessen the number of gates. The same output as to what was done in the Actual Lab is expected.

RESULTS

TABLE 1:

First Number 5 7 8 8 Laboratory Exercise No. 3 Operation + + + + Second Number 4 6 7 8 Page 5 Result

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

9 9 8 7 6 5

+ -

9 0 1 2 3 4

SCHEMATIC DIAGRAM Draw the complete schematic diagram here:

ANALYSIS / OBSERVATION:

Laboratory Exercise No. 3

Page 6

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

CONCLUSION:

Laboratory Exercise No. 3

Page 7

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Activity

5 LATCH AS A MEMORY DEVICE

INFORMATION Latches are circuits used to store information. They may be in the form of Integrated Circuits containing several combinations of logical gates whose inputs/outputs are corresponded by the pins on the external part of the IC. SR latch is a sequential circuit with two inputs called SET and RESET, which make the SR latch store a logic 0 (reset) or 1 (set) until actively change. The enable input on a gated SR latch provides a way to latch the Q and not-Q outputs without regard to the status of S or R.

The D-latch is rarely related to gated-SR latch. Another character of Dlatch is that it can be constructed similarly to SR latch. The inverter added to R input prevents the Restricted Combination (RC) State. The D-latch is also known as transparent latch, data latch, or simply gated latch. It has a data input and an enable signal. It had been called transparent due to the fact that, when the enable input is on (1), the signal would propagate directly through the circuit, from the input D to the output Q. Whatever you had input will be automatically your output.

Laboratory Exercise No. 5

Page 1

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

OBJECTIVES To construct a circuit using SR or D Latches which can store encoded inputs and decoded outputs. To make use of the different logical gates in order to obtain desired result. To apply encoder, decoder, multiplexers, and BCD adder/subtractor.

MATERIALS/EQUIPMENT PC/laptop with pre-installed Multisim 11

PROCEDURE Prelab 1. Look for latch models (SR or D Latch) to be use in the simulation and study each of their datasheets. 2. Study the BCD Adder/Subtractor circuit done on Laboratory Activity 4. 3. Review the function of the multiplexer used on Laboratory Activity 3. Lab Proper 1. Using the searched properties of the latch, connect the necessary voltages like ground and Vcc. 2. Connect a Vcc and resistor in the ten push buttons representing numbers 0 9. Connect the encoder. 3. Connect the first four latches to the output of the encoder and connect it to a decoder and hex display, this is just the first digit. Add another four

Laboratory Exercise No. 5 Page 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

latches to store the first digit and reset the first set of latches, so that the second digit can be stored in it. Thus, the tens digit is stored in the second set of latches and the ones digit is stored in the first set of latches. 4. Try simulating it to assure correct junctions, components, sources, etc. If the circuit is not working, check the connections or any possible errors. 5. If working, connect another four latches to both ones and tens digit to store the first number encoded. And store the second number to be added or subtracted to the first two sets of latches. 6. Repeat step 4, but if working connect four-bit adder and multiplexer to generate the desired operation. Multiplexer is used so that there will only be three hex displays which will show the input numbers and the sum or difference. Four-bit adder is used to perform addition and subtraction, correcting factor is necessary. 7. To check, switch the push button representing a number. Input a twodigit number, choose whether to add or subtract then input the next number. The result should output the right sum or difference of the inputted numbers. Record the results in Table 1. FOLLOW UP ACTIVITY In this activity, 2-digit numbers were stored, added and subtracted with a maximum digit combination of 99+99=198 as the result. As a follow-up activity, reconfigure the circuit in such a way that same operations done in the previous circuit can be performed with the addition/subtraction of another digit. This time 3-digit numbers must be stored, added and subtracted. The maximum result should be 999 + 999 = 1998 for addition.

Laboratory Exercise No. 5

Page 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

RESULTS TABLE 1:

First Number 64 75 35 9 5 91 86 57 18 5 Operation + + + + + Second Number 28 39 7 8 4 42 28 9 3 4 Result

Laboratory Exercise No. 5

Page 4

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

SCHEMATIC DIAGRAM Draw the complete schematic diagram here:

ANALYSIS / OBSERVATION:

CONCLUSION:

Laboratory Exercise No. 5

Page 5

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Activity

6 COUNTERS USING FLIP-FLOPS

INFORMATION Flip flops are commonly associated with clocks. Flip flops are being triggered by the edge of the clock. Since there are only two edges in a digital/square waveform, flip flops can either be triggered when there is a rising edge or falling edge.

Flip-flop is a circuit that has two stable states and can be used to store state information. A flip-flop circuit can be constructed from two NAND gates or two NOR gates. It has three types, namely, D Flip-Flop (DFF), T-Flip Flop (TFF), and the JK-Flip Flop (JKFF). The D-Flip Flop (DFF) is the most common flip-flop. It is better known as data or delay flip-flop as its output Q looks like a delay of input D. The Q output takes on the state of the D input at the moment of a positive edge at the clock pin or negative edge if the clock input is active low.

For the T-Flip Flop (TFF), if the T input is high, the T flip-flop changes state or toggles whenever the clock input is strobe. If the T input is low, the flip-flop holds the previous value. A JK Flip-Flop (JKFF) is a refinement of the SR flip-flop in that the indeterminate state of the SR type is defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flip-flop. Counters are the main application of these latches. These counters can either be up counting or down counting. Because of the clock (timed by the user), the circuit can be designed in anyway depending on the desired counting of the user. In digital logic and computing, a counter is a device which stores (and sometimes displays) the number of times a particular event or process has occurred, often in relationship to a clock signal. In electronics, counters can be implemented quite easily using registertype circuits such as the flip-flop, and a wide variety of classifications exist:

Laboratory Exercise No. 6 Page 1

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Asynchronous (ripple) counter changing state bits are used as clocks to subsequent state flip-flops Synchronous counter all state bits change under control of a single clock Decade counter counts through ten states per stage Up/down counter counts both up and down, under command of a control input Ring counter formed by a shift register with feedback connection in a ring Johnson counter a twisted ring counter

Cascaded counter Usually, counter circuits are digital in nature, and count in natural binary. Many types of counter circuits are available as digital building blocks, for example a number of chips in the 4000 series implement different counters. Occasionally there are advantages to using a counting sequence other than the natural binary sequence, such as the binary coded decimal counter, a linear feedback shift register counter, or a Gray-code counter. Counters are useful for digital clocks and timers, and in oven timers, VCR clocks, etc.

OBJECTIVES To know the concepts and operations of flip flops. To know the effect of clock in the flip flops. To use flip flops as counter. To design a different types of counters: Down Counter (DFF, TFF, JKFF); Up Counter (DFF, TFF, JKFF); Up Down Counter (DFF, TFF, JKFF); Bidirectional Counter with parallel loading (DFF, TFF, JKFF).

MATERIALS/EQUIPMENT PC/laptop with pre-installed Multisim 11

Laboratory Exercise No. 6

Page 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

PROCEDURE Prelab 1. Study the characteristics of each of the following Flip-Flops: a. D-Flip Flop b. T-Flip Flop c. JK-Flip Flop 2. Construct an excitation table for an Up-Counter that can display numbers 0 to 9. Complete the excitation table for each of the 3 Flip Flops. Record the results in Table 1, 2 and 3. Make also an excitation table for DFF down counter (Table 4), and DFF bidirectional counter (Table 5). 3. From the excitation table, use Karnaugh Mapping to obtain the equations in their simplest forms for each respective set of inputs. Use dont care (x) for unused states. Lab Proper 1. Using the obtained equations from the Pre-lab activity, construct individual circuits for each of the Up-Counters (DFF, TFF, and JKFF), DFF down counter, and DFF bidirectional counter. FOLLOW UP ACTIVITY Construct a two-digit down counter using the D-Flip Flops, T-Flip-Flops, and JK-Flip-Flops. With these two-digit down counters, the minimum requirement is that the maximum number to be displayed on each must be the number 15 and minimum must be 00.

Laboratory Exercise No. 6

Page 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

RESULTS TABLE:

Present state

Q3 Q2 Q1 Q0

D3

D2

D1

D0

Next state

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 D3 = D2 = D1 =

0 0 0

0 0 0

0 1 1

1 0 1

0001 0010 0011 0100 0101 0110 0111 1000 1001 0000

Laboratory Exercise No. 6

Page 4

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

D0 =

Table 1 Up-Counter (0-9) DFF

Laboratory Exercise No. 6

Page 5

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

TABLE:

Present state

Q3 Q2 Q1 Q0

T3

T2

T1

T0

Next state

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 T3 = T2 = T1 = T1 =

0 0 0

0 0 0

0 1 0

1 1 1

0001 0010 0011 0100 0101 0110 0111 1000 1001 0000

Table 2 Up-Counter (0-9) TFF

Laboratory Exercise No. 6

Page 6

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

TABLE:

Present state

Q3 Q2 Q1 Q0

J3

K3

J2

K2

J1

K1

J0

K0

Next state

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 J3 = K3 = J2 = K2 = J1 = K1 =

0 0 0

X X X

0 0 0

X X X

0 1 X

X X 0

1 X 1

X 1 X

0001 0010 0011 0100 0101 0110 0111 1000 1001 0000

Laboratory Exercise No. 6

Page 7

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

TABLE:

J0 = K0 =

Table 3 Up-Counter (0-9) JKFF

Present state

Q3 Q2 Q1 Q0

D3

D2

D1

D0

Next state

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 D3 = D2 = D1 = D0 =

Table 4 Down-Counter (9-0) DFF

1001 0000 0001 0010 0011 0100 0101 0110 0111 1000

Laboratory Exercise No. 6

Page 8

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

TABLE:

S Q3 Q2 Q1 Q0 10000 10001 10010 10011 10100 10101 10110 10111 11000 11001 00000 00001 00010 00011 00100 00101 00110 00111

D3

D2

D1

D0

NEXT STATE 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000 1001 0000 0001 0010 0011 0100 0101 0110

Laboratory Exercise No. 6

Page 9

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

TABLE:

01000 01001 (S = 0 Down Counter; S = 1 Up Counter) 0111 1000

Table 5 Bidirectional-Counter (0-9) DFF

Laboratory Exercise No. 6

Page 10

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

SCHEMATIC DIAGRAM Draw the complete schematic diagram here: DFF Up-Counter TFF Up-Counter JKFF Up-Counter DFF down counter DFF bidirectional counter.

ANALYSIS / OBSERVATION:

Page

CONCLUSION:

Laboratory Exercise No. 6

Page 11

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Page

Laboratory Exercise No. 6

12

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Activity

7

SHIFT REGISTERS

INFORMATION Shift registers are kind of sequential logic circuits that were mainly used to store digital data. The main components of a shift register were flip flops. These were used to store a bit in a flip flop. The circuit was configured in such a way that the flip flops are like in series connection. The concept of connecting the flip flops in series was to transfer the data from the flip flop to the other flip flop. These shift registers were applied to store data and move data. The movement of data was dependent to the common clock connected to the flip flops. OBJECTIVES To understand the function of register. To construct a Shift Right Register (SHR) and a Shift Left Register (SHL) using D Flip-Flop. To construct a Universal Shift Register using the following Flip-Flops: a. D Flip-Flop b. T Flip-Flop c. JK Flip-Flop To construct a Johnson Counter with Decoded 8-LEDs Running Display using D Flip-Flop.

MATERIALS/EQUIPMENT

Laboratory Exercise No. 7

Page 1

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

PC/laptop with pre-installed Multisim 11

PROCEDURE Prelab 1. Study the behavior of the Shift Right Register and Shift Left Register and how it can be implemented using the D Flip-Flop. 2. Research on how the Universal Shift Register works. 3. Look for some schematic diagrams that shall present how the different types of Flip-Flops are used together with gates and other components to construct a Universal Shift Register, specifically, how it is being implemented using the DFF, TFF and the JKFF.

A 0 0 1 1 B 0 1 0 1 Function No change/ stop SHR SHL Parallel Load

4. Find some resources about the Johnson Counter. 5. Examine how to make a Johnson Counter that shall have with it Decoded 8-LEDs Running Display. 6. Considering the properties of the D Flip-Flop, make a diagram of the Johnson Counter with the Decoded 8-LEDs Running Display.

Laboratory Exercise No. 7

Page 2

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

Lab Proper 1. Construct a Shift Right Register using the D Flip Flop. Interconnect gates and some components to implement the Shift Right Register. 2. Use different colored probes as indicators. 3. Make a Shift Left Register using the same Flip-Flop as was used in the Shift Right Register and different colored probes as indicators. 4. Use the square waveform as the clock voltage. 5. Create a Universal Shift Register, first using the D Flip-Flop. 6. As what was studied on the Pre Lab Activity, carefully connect the pins, gates, switches, and other components as required. 7. With the same procedure as the Universal Shift Register using the DFF, implement the Universal Shift Register first using the TFF then the JKFF with the additional considerations on each characteristic. 8. Based on what was researched on the Pre Lab activity about the Johnson Counter with Decoded 8-LEDs Running Display, make a simulation that shall implement it and use different colored LEDs as indicators.

FOLLOW UP ACTIVITY 1. Design a Shift Right Register and a Shift Left Register using the T FlipFlop and the JK Flip-Flop. 2. Formulate equations that can satisfy the requirements of the Toggle FlipFlop and the JK Flip-Flop separately. 3. With these equations, simulate the diagram and see if the results appear to be true with what the Shift Right Register and Shift Left Register were supposed to operate. 4. Simulate a Johnson Counter with 8-LEDs Running Display using the T Flip-Flop and the JK Flip-Flop.

Laboratory Exercise No. 7 Page 3

Logic Circuits and Switching Theory College of Engineering ECE / CpE Department Ateneo de Naga University

5. Use different colored indicators for the running display for more distinguishable result. 6. Also, perform the Ring-Counter using the D Flip-Flop, T Flip-Flop and the JK Flip-Flop. Use probes as indicators.

RESULTS SCHEMATIC DIAGRAM Draw the complete schematic diagram here: - DFF SHR - DFF SHL - DFF Universal Shift Register - TFF Universal Shift Register - JKFF Universal Shift Register - Johnson Counter with 8-LEDs Running Display ANALYSIS / OBSERVATION:

CONCLUSION:

Laboratory Exercise No. 7

Page 4

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Transmission Media 2Document5 pagesTransmission Media 2Danilyn Padillo LucioPas encore d'évaluation

- TransformerDocument9 pagesTransformerDanilyn Padillo LucioPas encore d'évaluation

- Assignment 1 (ILS Vs GNSS)Document8 pagesAssignment 1 (ILS Vs GNSS)Danilyn Padillo LucioPas encore d'évaluation

- Concet Paper SLPDocument8 pagesConcet Paper SLPDanilyn Padillo LucioPas encore d'évaluation

- LogicsDocument3 pagesLogicsDanilyn Padillo LucioPas encore d'évaluation

- Activity 1 Phase Shifter: Belza, Robeto R. Engr. Eugene Dy Lucio, Danilyn P. Organis, Zenaida DDocument2 pagesActivity 1 Phase Shifter: Belza, Robeto R. Engr. Eugene Dy Lucio, Danilyn P. Organis, Zenaida DDanilyn Padillo LucioPas encore d'évaluation

- Hyperspectral Remote Sensing of Agriculture.Document13 pagesHyperspectral Remote Sensing of Agriculture.Danilyn Padillo LucioPas encore d'évaluation

- TransformerDocument9 pagesTransformerDanilyn Padillo LucioPas encore d'évaluation

- History and Working of Fiber Optic Communication SystemsDocument7 pagesHistory and Working of Fiber Optic Communication SystemsDanilyn Padillo LucioPas encore d'évaluation

- GSM ReportDocument10 pagesGSM ReportDanilyn Padillo LucioPas encore d'évaluation

- 4GDocument103 pages4GDanilyn Padillo LucioPas encore d'évaluation

- Acknowledgement ReceptDocument1 pageAcknowledgement ReceptDanilyn Padillo LucioPas encore d'évaluation

- Ra 5734Document7 pagesRa 5734deathfistPas encore d'évaluation

- Enercoon Motors LabDocument6 pagesEnercoon Motors LabDanilyn Padillo LucioPas encore d'évaluation

- Twisted LogicDocument3 pagesTwisted LogicDanilyn Padillo LucioPas encore d'évaluation

- ECEM312 Electronics 1 Lab Diode and LED CharacterizationDocument46 pagesECEM312 Electronics 1 Lab Diode and LED CharacterizationDanilyn Padillo LucioPas encore d'évaluation

- L-20 (SSG) (Pe) ( (Ee) Nptel)Document12 pagesL-20 (SSG) (Pe) ( (Ee) Nptel)Venkatesh KarriPas encore d'évaluation

- Activity 7 Bipolar Junction Transistor FundamentalsDocument4 pagesActivity 7 Bipolar Junction Transistor FundamentalsDanilyn Padillo LucioPas encore d'évaluation

- TechnologyDocument4 pagesTechnologyDanilyn Padillo LucioPas encore d'évaluation

- Maria Clara 3Document5 pagesMaria Clara 3Danilyn Padillo LucioPas encore d'évaluation

- Chapter 7 ElectromagneticsDocument39 pagesChapter 7 ElectromagneticsDanilyn Padillo LucioPas encore d'évaluation

- CCD LetterDocument2 pagesCCD LetterDanilyn Padillo LucioPas encore d'évaluation

- Led Cube 8x8x8Document70 pagesLed Cube 8x8x8Chris MuncyPas encore d'évaluation

- Lab ResultDocument1 pageLab ResultDanilyn Padillo LucioPas encore d'évaluation

- E-Cosplay: General GuidelinesDocument3 pagesE-Cosplay: General GuidelinesDanilyn Padillo LucioPas encore d'évaluation

- AB2 - 5 Surfaces and Surface IntegralsDocument17 pagesAB2 - 5 Surfaces and Surface IntegralsnooktabletPas encore d'évaluation

- Experiment 8.1: LabDocument8 pagesExperiment 8.1: LabDanilyn Padillo LucioPas encore d'évaluation

- 15 Things A Nagueñan YouthDocument1 page15 Things A Nagueñan YouthDanilyn Padillo LucioPas encore d'évaluation

- V 10Document5 pagesV 10Danilyn Padillo LucioPas encore d'évaluation

- Viva Questions Defferentiator and IntegratorDocument2 pagesViva Questions Defferentiator and IntegratorMalik Hammad100% (1)

- Logic Selection Guide 2015: Standard Logic & Picogate Logic in Leaded and Leadless PackagesDocument70 pagesLogic Selection Guide 2015: Standard Logic & Picogate Logic in Leaded and Leadless PackagessuriantoPas encore d'évaluation

- Top 30+ Most Asked VLSI Interview Questions (2021) : 1) What Do You Understand by Boolean Logic?Document11 pagesTop 30+ Most Asked VLSI Interview Questions (2021) : 1) What Do You Understand by Boolean Logic?Nic JonesPas encore d'évaluation

- Application Examples: Vishay SemiconductorsDocument6 pagesApplication Examples: Vishay SemiconductorsdraPas encore d'évaluation

- Using The Analog-To-Digital ConverterDocument21 pagesUsing The Analog-To-Digital ConvertergpersijnPas encore d'évaluation

- Ic Op-Amp Ha 17741Document19 pagesIc Op-Amp Ha 17741evhyajahPas encore d'évaluation

- PowerPoint Translinear CircuitsDocument15 pagesPowerPoint Translinear CircuitsroohiPas encore d'évaluation

- Digital Logic MinutesDocument36 pagesDigital Logic MinutesshyamalaperiPas encore d'évaluation

- Chapter 5 - AM ReceptionDocument44 pagesChapter 5 - AM ReceptionJ A P SPas encore d'évaluation

- Lab 3Document4 pagesLab 3J SarduaPas encore d'évaluation

- C-Mos 8-Channel 8-Bit Serial A/D Converter: 9 7 6 5 4 3 2 1 A A A A A A A A 15 DODocument1 pageC-Mos 8-Channel 8-Bit Serial A/D Converter: 9 7 6 5 4 3 2 1 A A A A A A A A 15 DOAsep TatangPas encore d'évaluation

- Webster Chapter 03Document35 pagesWebster Chapter 03'Wsseim AlPas encore d'évaluation

- EEE FinalDocument14 pagesEEE FinalRishabh SharmaPas encore d'évaluation

- BJT Lab ReportDocument3 pagesBJT Lab ReportAkib Hasan NiloyPas encore d'évaluation

- Parker Smith's Series Resonance Problem No.85Document1 pageParker Smith's Series Resonance Problem No.85mu_altafPas encore d'évaluation

- Chapter 1 Combinational CMOS Logic Circuits Lecture # 4 Pass Transistors andDocument34 pagesChapter 1 Combinational CMOS Logic Circuits Lecture # 4 Pass Transistors andJacques HaPas encore d'évaluation

- Power Supply Supervisor With PWM Controller: Description Pin Configuration (Top View)Document6 pagesPower Supply Supervisor With PWM Controller: Description Pin Configuration (Top View)GigaflopsTechnology2019Pas encore d'évaluation

- Rizzoni 5e SM ch03 SolutionDocument59 pagesRizzoni 5e SM ch03 SolutionrhdquddjqPas encore d'évaluation

- MC14043B, MC14044B Cmos Msi: Quad R-S LatchesDocument8 pagesMC14043B, MC14044B Cmos Msi: Quad R-S LatchesGaspar GarciaPas encore d'évaluation

- EEE241L - Lab 4 - Parallel RLC CircuitsDocument4 pagesEEE241L - Lab 4 - Parallel RLC CircuitsMd. Imdadul Haque Nayan 2222846643Pas encore d'évaluation

- Design Word by Kezia Helena PatriciaDocument2 pagesDesign Word by Kezia Helena PatriciaKezia HelenaPas encore d'évaluation

- Vgs (TH) Is The Voltage at Which The Mosfet Channel Begins To Conduct. at This Voltage, A PositiveDocument2 pagesVgs (TH) Is The Voltage at Which The Mosfet Channel Begins To Conduct. at This Voltage, A PositiveNOOR UR AIN ZAFARPas encore d'évaluation

- BJT Construction and Configurations BJT Applications: - Common Emitter - Common BaseDocument23 pagesBJT Construction and Configurations BJT Applications: - Common Emitter - Common BaseirishPas encore d'évaluation

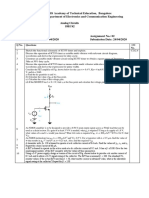

- JSS Academy of Technical Education, Bangalore Department of Electronics and Communication Engineering Analog Circuits AssignmentDocument2 pagesJSS Academy of Technical Education, Bangalore Department of Electronics and Communication Engineering Analog Circuits AssignmentSamarth SamaPas encore d'évaluation

- Z80 computer circuit diagram with component list and notesDocument1 pageZ80 computer circuit diagram with component list and notesmjs6029100% (1)

- 02 - Modulo-5 CounterDocument4 pages02 - Modulo-5 CounterUsman QadeerPas encore d'évaluation

- Silicon NPN Power Transistors: Inchange Semiconductor Product SpecificationDocument4 pagesSilicon NPN Power Transistors: Inchange Semiconductor Product SpecificationDjalma MotaPas encore d'évaluation

- YtrfgDocument1 pageYtrfgZuhaili ZawawiPas encore d'évaluation

- CNCPROM - MESA 7I33TA motion controller interfaceDocument15 pagesCNCPROM - MESA 7I33TA motion controller interfaceAlex VorobeyPas encore d'évaluation

- Elektronik Soalan 5 Dan 8 2009Document6 pagesElektronik Soalan 5 Dan 8 2009wanawokPas encore d'évaluation