Académique Documents

Professionnel Documents

Culture Documents

Fly Back

Transféré par

Đặng Văn TàiDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Fly Back

Transféré par

Đặng Văn TàiDroits d'auteur :

Formats disponibles

www.fairchildsemi.

com

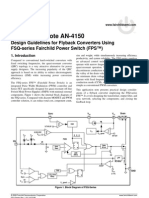

Application Note AN4137

Design Guidelines for Off-line Flyback Converters Using Fairchild Power Switch (FPS)

Abstract

This paper presents practical design guidelines for off-line flyback converters employing FPS (Fairchild Power Switch). Switched mode power supply (SMPS) design is inherently a time consuming job requiring many trade-offs and iterations with a large number of design variables. The step-by-step design procedure described in this paper helps engineers to design SMPS easily. In order to make the design process more efficient, a software design tool, FPS design assistant that contains all the equations described in this paper is also provided. The design procedure is verified through experimental prototype converter.

Bridge rectifier diode

CDC

D R(n)

L P(n)

V DC + FPS

R sn

C sn

Vsn +

Np

N S(n) CO(n)

CP(n)

VO(n)

Dsn D R1

Drain 1

L P1

N S1

AC line

FB

4

GND 2 Vcc 3

H11A817A

CO1

CP1

V O1

Ra

Da

Rd H11A817A

Rbias R1

CB

Ca

Na

RF KA431

CF

R2

Figure 1. Basic Off-line Flyback Converter Using FPS

1. Introduction

Figure 1 shows the schematic of the basic off-line flyback converter using FPS, which also serves as the reference circuit for the design process described in this paper. Because the MOSFET and PWM controller together with various additional circuits are integrated into a single package, the design of SMPS is much easier than the discrete MOSFET and PWM controller solution. This paper provides a step-by-step design procedure for a FPS based off-line flyback converter, which includes designing the transformer

and output filter, selecting the components and closing the feedback loop. The design procedure described herein is general enough to be applied to various applications. The design procedure presented in this paper is also implemented in a software design tool (FPS design assistant) to enable the engineer finish their SMPS design in a short time. In the appendix, a step-by-step design example using the software tool is provided. An experimental flyback converter from the design example has been built and tested to show the validity of the design procedure. Rev. 1.2.0

2003 Fairchild Semiconductor Corporation

AN4137

APPLICATION NOTE

2. Step-by-step Design Procedure

1. Determine the system specifications (Vlinemin, Vlinemax, fL, Po, Eff)

In this section, a design procedure is presented using the schematic of figure 1 as a reference. In general, most FPS devices have the same pin configuration from pin 1 to pin 4, as shown in figure 1. Figure 2 illustrates the design flow chart. The detailed design procedures are as follows:

(1) STEP-1 : Define the system specifications

2. Determine DC link capacitor (CDC) and DC link voltage range 3. Determine the maximum duty ratio (Dmax) 4. Determine the transformer primary side inductance (Lm) 5. Choose proper FPS considering input power and Idspeak 6. Determine the proper core and the minimum primary turns (Npmin) 7. Determine the number of turns for each output 8. Determine the wire diameter for each winding

- Line voltage range (Vlinemin and Vlinemax). - Line frequency (fL). - Maximum output power (Po). - Estimated efficiency (Eff) : It is required to estimate the power conversion efficiency to calculate the maximum input power. If no reference data is available, set Eff = 0.7~0.75 for low voltage output applications and Eff = 0.8~0.85 for high voltage output applications. With the estimated efficiency, the maximum input power is given by

Po Pin = -----E ff (1)

For multiple output SMPS, the load occupying factor for each output is defined as

Po (n ) KL ( n ) = -----------Po

Y

(2)

Is the winding window area (Aw) enough ? N Y Is it possible to change the core ?

where Po(n) is the maximum output power for the n-th output. For single output SMPS, KL(1)=1.

(2) STEP-2 : Determine DC link capacitor (CDC) and the DC link voltage range.

It is typical to select the DC link capacitor as 2-3uF per watt of input power for universal input range (85-265Vrms) and 1uF per watt of input power for European input range (195V265Vrms). With the DC link capacitor chosen, the minimum link voltage is obtained as

9. Choose the proper rectifier diode for each output

V DC

10. Determine the output capacitor

min

2 ( V line

min 2

P in ( 1 D ch ) ) -----------------------------------C DC f L

(3)

11. Design the RCD snubber

where Dch is the DC link capacitor charging duty ratio defined as shown in figure 3, which is typically about 0.2 and Pin, Vlinemin and fL are specified in step-1. The maximum DC link voltage is given as

V DC

max

12. Feedback loop design

2V line

max

(4)

Design finished

where Vlinemax is specified in step-1.

Figure 2. Flow chart of design procedure

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4137

DC link voltage

Minimum DC link voltage

T1 Dch = T1 / T2 = 0.2 T2

Figure 3. DC Link Voltage Waveform

In the case of a CCM flyback converter, the design process is straight forward since the input-to-output voltage gain depends only on the duty cycle. Meanwhile, the input-to-output voltage gain of a DCM flyback converter depends not only on the duty cycle but also on the load condition, which causes the circuit design to be somewhat complicated. However, it is generally accepted that a DCM flyback converter is designed to operate at the boundary of DCM and CCM with minimum input voltage and maximum load as shown in Fig. 4. This minimizes MOSFET conduction losses. Therefore, under these circumstances, we can use the same voltage gain equation as the CCM flyback converter with maximum load and minimum input voltage.

(3) STEP-3 : Determine the maximum duty ratio (Dmax).

A Flyback converter has two kinds of operation modes ; continuous conduction mode (CCM) and discontinuous conduction mode (DCM). CCM and DCM have their own advantages and disadvantages, respectively. In general, DCM provides better switching conditions for the rectifier diodes, since the diodes are operating at zero current just before becoming reverse biased. The transformer size can be reduced using DCM because the average energy storage is low compared to CCM. However, DCM inherently causes high RMS current, which increases the conduction loss of the MOSFET and the current stress on the output capacitors. Therefore DCM is usually recommended for high voltage and low current output applications. Meanwhile, CCM is preferred for low voltage and high current output applications.

V RO

VDC + F PS

VRO +

D rain

+ V ds -

GND

Minimum input voltage and full load condition

MOSFET Drain Current Rectifier Diode Current

0V

V DC

Figure 5. The output voltage reflected to the primary

As input voltage increases or load current decreases

MOSFET Drain Current Rectifier Diode Current

When the MOSFET in the FPS is turned off, the input voltage (VDC) together with the output voltage reflected to the primary (VRO) are imposed on the MOSFET as shown in figure 5. After determining Dmax, VRO and the maximum nominal MOSFET voltage (Vdsnom) are obtained as

D max min -V V RO = ---------------------1 D max DC V ds

nom

(5) (6)

= V DC

max

+ VRO

Figure 4. Current waveforms of DCM flyback converter

where VDCmin and VDCmax are specified in equations (3) and (4) respectively. As can be seen in equation (5) and (6), the voltage stress on MOSFET can be reduced, by decreasing Dmax. However, this increases the voltage stresses on the rectifier diodes in the secondary side. Therefore, it is desirable to set Dmax as large as possible if there is enough margin in the MOSFET voltage rating. The maximum duty ratio 3

2002 Fairchild Semiconductor Corporation

AN4137

APPLICATION NOTE

(Dmax) should be determined so that Vdsnom would be 65~70% of the MOSFET voltage rating considering the voltage spike caused by the leakage inductance. In the case of 650V rated MOSFET, it is typical to set Dmax to be 0.45~0.5 for an universal input range application. Because the current mode controlled flyback converter operating in CCM causes sub-harmonic oscillation with duty ratio larger than 0.5, set Dmax to be smaller than 0.5 for CCM.

(4) STEP-4 : Determine the transformer primary side inductance (Lm).

V DC

CCM

1 # 1 1 -$ = % --------------------------- ---------& ! 2L m f s P in VRO"

(12)

where Pin, VRO and Lm are specified in equations (1), (5) and (7), respectively, and fs is the FPS switching frequency. If the result of equation (12) has a negative value, the converter is always in CCM under the full load condition regardless of the input voltage variation.

The operation changes between CCM and DCM as the load condition and input voltage vary. For both operation modes, the worst case in designing the inductance of the transformer primary side (Lm) is full load and minimum input voltage condition. Therefore, Lm is obtained in this condition as

( VDC D max ) L m = --------------------------------------------2Pin f s KRF

min 2

I EDC

K RF = I 2I EDC

I ds peak

CCM operation : KRF < 1

(7)

I ds peak

I

I EDC

K RF = I 2I EDC

where VDCmin is specified in equation (3), Dmax is specified in step-3, Pin is specified in step-1, fs is the switching frequency of the FPS device and KRF is the ripple factor in full load and minimum input voltage condition, defined as shown in figure 6. For DCM operation, KRF = 1 and for CCM operation KRF < 1. The ripple factor is closely related with the transformer size and the RMS value of the MOSFET current. Even though the conduction loss in the MOSFET can be reduced through reducing the ripple factor, too small a ripple factor forces an increase in transformer size. When designing the flyback converter to operate in CCM, it is reasonable to set KRF = 0.25-0.5 for the universal input range and KRF = 0.4-0.8 for the European input range. Once Lm is determined, the maximum peak current and RMS current of the MOSFET in normal operation are obtained as

I ds I ds

rms peak

DCM operation : KRF =1

Figure 6. MOSFET Drain Current and Ripple Factor (KRF)

(5) STEP-5 : Choose the proper FPS considering input power and peak drain current.

I = I EDC + ---2

2 I 2 D max ----$ 3 ( IEDC ) + # ! 2 " ------------3

(8) (9)

With the resulting maximum peak drain current of the MOSFET (Idspeak) from equation (8), choose the proper FPS of which the pulse-by-pulse current limit level (Iover) is higher than Idspeak. Since FPS has 12% tolerance of Iover, there should be some margin in choosing the proper FPS device.The FPS lineup with proper power rating is also included in the software design tool.

where

P in I EDC = ------------------------------------min V DC D max

DC max I = -----------------------------------

(10)

and

min

(6) STEP-6 : Determine the proper core and the minimum primary turns.

Lm fs

(11)

where Pin, VDCmin and Lm are specified in equations (1), (3), and (7) respectively, Dmax is specified in step-3 and fs is the FPS switching frequency. The flyback converter designed for CCM at the minimum input voltage and full load condition may enter into DCM as the input voltage increases. The maximum input voltage guaranteeing CCM in the full load condition is obtained as

Actually, the initial selection of the core is bound to be crude since there are too many variables. One way to select the proper core is to refer to the manufacture's core selection guide. If there is no proper reference, use the table 1 as a starting point. The core recommended in table 1 is typical for the universal input range, 67kHz switching frequency and single output application. When the input voltage range is 195-265 Vac or the switching frequency is higher than 67kHz, a smaller core can be used. For an application with multiple outputs, usually a larger core should be used than recommended in the table.

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4137

With the chosen core, the minimum number of turns for the transformer primary side to avoid the core saturation is given by

NP

min

Output Power 0-10W

EI core EI12.5 EI16 EI19 EI22 EI25

EE core EE8 EE10 EE13 EE16 EE19 EE22

EPC core EPC10 EPC13 EPC17 EPC19 EPC25 EPC30

EER core

L m Iover 6 = ------------------- 10 B sat A e

(turns)

(13)

where Lm is specified in equation (7), Iover is the FPS pulseby-pulse current limit level, Ae is the cross-sectional area of the core as shown in figure 7 and Bsat is the saturation flux density in tesla. Figure 8 shows the typical characteristics of ferrite core from TDK (PC40). Since the saturation flux density (Bsat) decreases as the temperature goes high, the high temperature characteristics should be considered. If there is no reference data, use Bsat =0.3~0.35 T. Since the MOSFET drain current exceeds Idspeak and reaches Iover in a transition or fault condition, Iover is used in equation (13) instead of Idspeak to prevent core saturation during transition.

10-20W 20-30W 30-50W 50-70W 70-100W

EER25.5 EER28 EER28L EER35 EER40 EER42 EER49

EI28 EI30 EI35 EI40

EE25 EE30 EE35 EE40 EE50 EE60

100-150W EI50 150-200W EI60

Table 1. Core quick selection table (For universal input range, fs=67kHz and single output)

Aw

(7) STEP-7 : Determine the number of turns for each output

Figure 9 shows the simplified diagram of the transformer. First, determine the turns ratio (n) between the primary side and the feedback controlled secondary side as a reference.

NP V R0 = ------------------------n = --------Ns1 V o1 + V F1

Ae

Figure 7. Window Area and Cross Sectional Area

(14)

where Np and Ns1 are the number of turns for primary side and reference output, respectively, Vo1 is the output voltage and VF1 is the diode (DR1) forward voltage drop of the reference output. Then, determine the proper integer for Ns1 so that the resulting Np is larger than Npmin obtained from equation (13). The number of turns for the other output (n-th output) is determined as

Vo (n ) + VF ( n) Ns1 N s ( n ) = --------------------------------V o1 + V F1 ( turns ) ( 15 )

M agnetization Curves (typical) M aterial :PC40

25 !

500

60 ! 100 ! 120 !

400 Flux density B (mT)

300

The number of turns for Vcc winding is determined as

200

100

V cc * + V Fa - N s1 N a = --------------------------V o1 + VF1

( turns )

( 16 )

0 0 800 M agnetic field H (A/m ) 1600

Figure 8. Typical B-H characteristics of ferrite core (TDK/PC40)

where Vcc* is the nominal value of the supply voltage of the FPS device, and VFa is the forward voltage drop of Da as defined in figure 9. Since Vcc increases as the output load increases, it is proper to set Vcc* as Vcc start voltage (refer to the data sheet) to avoid the over voltage protection condition during normal operation.

2002 Fairchild Semiconductor Corporation

AN4137

APPLICATION NOTE

+ V F(n) V RO + Np D R(n) N S(n) + V O(n) -

severe eddy current losses as well as to make winding easier. For high current output, it is better to use parallel windings with multiple strands of thinner wire to minimize skin effect. Check if the winding window area of the core, Aw (refer to figure 7) is enough to accommodate the wires. The required winding window area (Awr) is given by

A w r = Ac K F (19)

- V Fa + + V cc * Da Na

+ V F1 D R1 N S1 + V O1 -

Figure 9. Simplified diagram of the transformer

where Ac is the actual conductor area and KF is the fill factor. Typically the fill factor is 0.2~0.25 for single output application and 0.15~0.2 for multiple outputs application. If the required window (Awr) is larger than the actual window area (Aw), go back to the step-6 and change the core to a bigger one. Sometimes it is impossible to change the core due to cost or size constraints. If the converter is designed for CCM and the winding window (Aw) is slightly insufficient, go back to step-4 and reduce Lm by increasing the ripple factor (KRF). Then, the minimum number of turns for the primary (Npmin) of the equation (13) will decrease, which results in the reduced required winding window area (Awr).

With the determined turns of the primary side, the gap length of the core is obtained as

# NP 1$ G = 40 A e % -------------------- ------& 1000L A ! m L"

2

(9) STEP-9 : Choose the rectifier diode in the secondary side based on the voltage and current ratings.

The maximum reverse voltage and the rms current of the rectifier diode (DR(n)) of the n-th output are obtained as

V DC ( Vo ( n) + VF ( n ) ) V D ( n ) = Vo ( n ) + --------------------------------------------------------------V RO ID ( n)

rms max

( mm )

( 17 )

( 20 ) ( 21 )

where AL is the AL-value with no gap in nH/turns2, Ae is the cross sectional area of the core as shown in figure 7, Lm is specified in equation (7) and Np is the number of turns for the primary side of the transformer

= I ds

rms

V RO K L ( n ) 1 Dmax ---------------------- ------------------------------------( Vo( n) + VF ( n) ) D max

(8) STEP-8 : Determine the wire diameter for each winding based on the rms current of each output.

where KL(n), VDCmax, VRO, Idsrms are specified in equations (2), (4), (5) and (9) respectively, Dmax is specified in step-3, Vo(n) is the output voltage of the n-th output and VF(n) is the diode (DR(n)) forward voltage. The typical voltage and current margins for the rectifier diode are as follows

V RRM > 1.3 V D ( n ) IF > 1.5 I D ( n )

rms

The rms current of the n-th secondary winding is obtained as

rms rms

(22) (23)

I sec ( n )

= I ds

V RO K L ( n ) 1 D max ---------------------- ------------------------------------( Vo (n ) + VF ( n) ) D max

( 18 )

are specified in equations (5) and (9), where VRO and Ids Vo(n) is the output voltage of the n-th output, VF(n) is the diode (DR(n)) forward voltage drop, Dmax is specified in step3 and KL(n) is the load occupying factor for n-th output defined in equation (2). The current density is typically 5A/mm2 when the wire is long (>1m). When the wire is short with a small number of turns, a current density of 6-10 A/mm2 is also acceptable. Avoid using wire with a diameter larger than 1 mm to avoid 6

rms

where VRRM is the maximum reverse voltage and IF is the average forward current of the diode. A quick selection guide for Fairchild Semiconductor rectifier diodes is given in table 2. In this table trr is the maximum reverse recovery time.

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4137

Schottky Barrier Diode Products SB330 SB530 MBR1035 MBR1635 SB340 SB540 SB350 SB550 SB360 SB560 MBR1060 MBR1660 Products EGP10B UF4002 EGP20B EGP30B FES16BT EGP10C EGP20C EGP30C FES16CT EGP10D UF4003 EGP20D EGP30D FES16DT EGP10F EGP20F EGP30F EGP10G UF4004 EGP20G EGP30G UF4005 EGP10J EGP20J EGP30J UF4006 UF4007 VRRM 30 V 30 V 35 V 35 V 40 V 40 V 50 V 50 V 60 V 60 V 60 V 60 V VRRM 100 V 100 V 100 V 100 V 100 V 150 V 150 V 150 V 150 V 200 V 200 V 200 V 200 V 200 V 300 V 300 V 300 V 400 V 400 V 400 V 400 V 600 V 600 V 600 V 600 V 800 V 1000 V IF 3A 5A 10 A 16 A 3A 5A 3A 5A 3A 5A 10 A 16 A IF 1A 1A 2A 3A 16 A 1A 2A 3A 16 A 1A 1A 2A 3A 16 A 1A 2A 3A 1A 1A 2A 3A 1A 1A 2A 3A 1A 1A trr trr 50 ns 50 ns 50 ns 50 ns 35 ns 50 ns 50 ns 50 ns 35 ns 50 ns 50 ns 50 ns 50 ns 35 ns 50 ns 50 ns 50 ns 50 ns 50 ns 50 ns 50 ns 75 ns 50 ns 50 ns 50 ns 75 ns 75 ns Package TO-210AD TO-210AD TO-220AC TO-220AC TO-210AD TO-210AD TO-210AD TO-210AD TO-210AD TO-210AD TO-220AC TO-220AC Package DO-41 DO-41 DO-15 DO-210AD TO-220AC DO-41 DO-15 DO-210AD TO-220AC DO-41 DO-41 DO-15 DO-210AD TO-220AC DO-41 DO-15 DO-210AD DO-41 DO-41 DO-15 DO-210AD DO-41 DO-41 DO-15 DO-210AD TO-41 TO-41

(10) STEP-10 : Determine the output capacitor considering the voltage and current ripple.

The ripple current of the n-th output capacitor (Co(n)) is obtained as

rms

I cap ( n )

( ID ( n )

rms 2

) Io ( n)

(24)

where Io(n) is the load current of the n-th output and ID(n)rms is specified in equation (21). The ripple current should be smaller than the ripple current specification of the capacitor. The voltage ripple on the n-th output is given by

I D I

peak

o ( n ) max ds RO C ( n ) L ( n ) V o ( n ) = ------------------------ + ---------------------------------------------------------- (25)

C o ( n ) fs

V R K ( V o ( n ) + VF ( n ) )

Ultra Fast Recovery diode

where Co(n) is the capacitance, Rc(n) is the effective series resistance (ESR) of the n-th output capacitor, KL(n), VRO and Idspeak are specified in equations (2), (5) and (8) respectively, Dmax is specified in step-3, Io(n) and Vo(n) are the load current and output voltage of the n-th output, respectively and VF(n) is the diode (DR(n)) forward voltage. Sometimes it is impossible to meet the ripple specification with a single output capacitor due to the high ESR of the electrolytic capacitor. Then, additional LC filter stages (post filter) can be used. When using the post filters, be careful not to place the corner frequency too low. Too low a corner frequency may make the system unstable or limit the control bandwidth. It is typical to set the corner frequency of the post filter at around 1/10~1/5 of the switching frequency.

(11) STEP-11 : Design the RCD snubber.

When the power MOSFET is turned off, there is a high voltage spike on the drain due to the transformer leakage inductance. This excessive voltage on the MOSFET may lead to an avalanche breakdown and eventually failure of FPS. Therefore, it is necessary to use an additional network to clamp the voltage. The RCD snubber circuit and MOSFET drain voltage waveform are shown in figure 10 and 11, respectively. The RCD snubber network absorbs the current in the leakage inductance by turning on the snubber diode (Dsn) once the MOSFET drain voltage exceeds the voltage of node X as depicted in figure 10. In the analysis of snubber network, it is assumed that the snubber capacitor is large enough that its voltage does not change significantly during one switching cycle. The first step in designing the snubber circuit is to determine the snubber capacitor voltage at the minimum input voltage and full load condition (Vsn). Once Vsn is determined, the power dissipated in the snubber network at the minimum input voltage and full load condition is obtained as

Table 2. Fairchild Diode quick selection table

2002 Fairchild Semiconductor Corporation

AN4137

APPLICATION NOTE

V ( V sn ) peak 2 sn 1 - = -- fs L lK ( I ds ) -------------------------P sn = ---------------2 R sn Vsn V RO

From equation (28), the maximum voltage stress on the internal MOSFET is given by

(26) V ds

max

where Ids is specified in equation (8), fs is the FPS switching frequency, Llk is the leakage inductance, Vsn is the snubber capacitor voltage at the minimum input voltage and full load condition, VRO is the reflected output voltage and Rsn is the snubber resistor. Vsn should be larger than VRO and it is typical to set Vsn to be 2~2.5 times of VRO. Too small a Vsn results in a severe loss in the snubber network as shown in equation (26). The leakage inductance is measured at the switching frequency on the primary winding with all other windings shorted. Then, the snubber resistor with proper rated wattage should be chosen based on the power loss. The maximum ripple of the snubber capacitor voltage is obtained as

peak

= V DC

max

+ V sn2

(31)

where VDCmax is specified in equation (4). Check if Vdsmax is below 90% of the rated voltage of the MOSFET (BVdss) as shown in figure 11. The voltage rating of the snubber diode should be higher than BVdss. Usually, an ultra fast diode with 1A current rating is used for the snubber network. In the snubber design in this section, neither the lossy discharge of the inductor nor stray capacitance is considered. In the actual converter, the loss in the snubber network is less than the designed value due to this effects.

V sn

V sn1 = ----------------------C sn R sn f s

(27)

VDC + CDC FPS

Rsn X VX

Csn

Vsn +

Np VRO +

where fs is the FPS switching frequency. In general, 5~10% ripple is reasonable. The snubber capacitor voltage (Vsn) of equation (26) is for the minimum input voltage and full load condition. When the converter is designed to operate in CCM, the peak drain current together with the snubber capacitor voltage decrease as the input voltage increases. The snubber capacitor voltage under maximum input voltage and full load condition is obtained as

V RO + ( VRO ) + 2R sn L lk fs ( I ds2 ) V sn2 = ------------------------------------------------------------------------------------------2

2 2

Dsn Llk

Drain

+ Vds -

GND

(28) Figure 10. Circuit diagram of the snubber network

where fs is the FPS switching frequency, Llk is the primary side leakage inductance, VRO is the reflected output voltage, Rsn is the snubber resistor and Ids2 is the peak drain current at the maximum input voltage and full load condition. When the converter operates in CCM at the maximum input voltage and full load condition (refer to equation (12)), the Ids2 of equation (28) is obtained as

max max P in # + V RO$ V DC VRO ! V DC " I ds2 = ----------------------------------------------------------------- + ----------------------------------------------------------------------------max max V VRO + V RO$ 2 Lm f s # DC ! V DC "

Voltage Margin > 10% of BVdss

(29)

BVdss

Effect of stray inductance (5-10V)

Vsn2

When the converter operates in DCM at the maximum input voltage and full load condition (refer to equation (12)), the Ids2 of equation (28) is obtained as

2 P in --------------fs Lm (30)

VRO

I ds2 =

VDC max

0V

Figure 11. MOSFET drain voltage and snubber capacitor voltage

2003 Fairchild Semiconductor Corporation

where Pin, VDCmax, VRO and Lm are specified in equations (1), (4), (5) and (7), respectively, and fs is the FPS switching frequency.

APPLICATION NOTE

AN4137

(12) STEP-12 : Design the feed back loop.

Since most FPS devices employ current mode control as shown in figure 12, the feedback loop can be simply implemented with a one-pole and one-zero compensation circuit. In the feedback circuit analysis, it is assumed that the current transfer ratio (CTR) of the opto coupler is 100%. The current control factor of FPS, K is defined as

I pk Iover K = --------- = ----------------V FB VFBsat (32)

RL ( 1 D ) 1 (1 + D) - , w = ---------------------------------------- and w p = -----------------w z = ------------------R c1 C o1 rz DL ( N N )2 R L C o1 m s1 p

where Lm is specified in equation (7), D is the duty cycle of the FPS, Co1 is the reference output capacitor and RC1 is the ESR of Co1. When the converter has more than one output, the low frequency control-to-output transfer function is proportional to the parallel combination of all load resistance, adjusted by the square of the turns ratio. Therefore, the effective load resistance is used in equation (33) instead of the actual load resistance of Vo1. Notice that there is a right half plane (RHP) zero (wrz) in the control-to-output transfer function of equation (33). Because the RHP zero reduces the phase by 90 degrees, the crossover frequency should be placed below the RHP zero. Figure 13 shows the variation of a CCM flyback converter control-to-output transfer function for different input voltages. This figure shows the system poles and zeros together with the DC gain change for different input voltages. The gain is highest at the high input voltage condition and the RHP zero is lowest at the low input voltage condition. Figure 14 shows the variation of a CCM flyback converter control-to-output transfer function for different loads. This figure shows that the low frequency gain does not change for different loads and the RHP zero is lowest at the full load condition. For DCM operation, the control-to-output transfer function of the flyback converter using current mode control is given by

Vo1 ( 1 + s w z ) v o1 - ---------------------------G vc = -------- = -------- V v FB ( 1 + s w p ) FB where 1 - , w p = 2 R L C o1 wz = ------------------R c1 C o1 (34)

where Ipk is the peak drain current and VFB is the feedback voltage, respectively for a given operating condition, Iover is the current limit of the FPS and VFBsat is the feedback saturation voltage, which is typically 2.5V.

In order to express the small signal AC transfer functions, the small signal variations of feedback voltage (vFB) and FB and v o1. controlled output voltage (vo1) are introduced as v

FPS vFB iD 1:1

vo1'

RD ibias Rbias

vo1

RB

CB

CF

RF

R1

KA431 R2 Ipk

MOSFET current

Figure 12. Control Block Diagram

For CCM operation, the control-to-output transfer function of the flyback converter using current mode control is given by

G vc v o1 = ------- v

FB

Vo1 is the reference output voltage, VFB is the feedback voltage for a given condition, RL is the effective total resistance of the controlled output, Co1 is the controlled output capacitance and Rc1 is the ESR of Co1. Figure 15 shows the variation of the control-to-output transfer function of a flyback converter in DCM for different loads. Contrary to the flyback converter in CCM, there is no RHP zero and the DC gain does not change as the input voltage varies. As can be seen, the overall gain except for the DC gain is highest at the full load condition. The feedback compensation network transfer function of figure 12 is obtained as

K R L V DC ( N p N s1 ) ( 1 + s w z ) ( 1 s w rz ) - ---------------------------------------------------------= ---------------------------------------------------1 + s wp 2V RO + v DC

( 33 )

where VDC is the DC input voltage, RL is the effective total load resistance of the controlled output, defined as Vo12/Po, Np and Ns1 are specified in step-7, VRO is specified in equation (5), Vo1 is the reference output voltage, Po is specified in step-1 and K is specified in equation (32). The pole and zeros of equation (33) are defined as

2003 Fairchild Semiconductor Corporation

AN4137

APPLICATION NOTE

w i 1 + s w zc v FB - --------------------------------- = - --- s 1 + 1 w pc v o1

(35)

RB 1 1 - , w zc = -------------------------------- , w pc = -------------where w i = ---------------------R1 RD CF ( RF + R1 ) CF RB CB

and RB is the internal feedback bias resistor of FPS, which is typically 2.8k and R1, RD, RF, CF and CB are shown in figure 12.

40 dB

fp

20 dB

fp

0 dB

High input voltage fz frz fz frz

Low input voltage

-20 dB

When the input voltage and the load current vary over a wide range, it is not easy to determine the worst case for the feedback loop design. The gain together with zeros and poles vary according to the operating condition. Moreover, even though the converter is designed to operate in CCM or at the boundary of DCM and CCM in the minimum input voltage and full load condition, the converter enters into DCM changing the system transfer functions as the load current decreases and/or input voltage increases. One simple and practical way to this problem is designing the feedback loop for low input voltage and full load condition with enough phase and gain margin. When the converter operates in CCM, the RHP zero is lowest in low input voltage and full load condition. The gain increases only about 6dB as the operating condition is changed from the lowest input voltage to the highest input voltage condition under universal input condition. When the operating mode changes from CCM to DCM, the RHP zero disappears making the system stable. Therefore, by designing the feedback loop with more than 45 degrees phase margin in low input voltage and full load condition, the stability over all the operating ranges can be guaranteed. The procedure to design the feedback loop is as follows

-40 dB 1Hz 10Hz 100Hz 1kHz 10kHz 100kHz

Figure 13. CCM flyback converter control-to output transfer function variation for different input voltages

(a) Determine the crossover frequency (fc). For CCM mode flyback, set fc below 1/3 of right half plane (RHP) zero to minimize the effect of the RHP zero. For DCM mode fc can be placed at a higher frequency, since there is no RHP zero. (b) When an additional LC filter is employed, the crossover frequency should be placed below 1/3 of the corner frequency of the LC filter, since it introduces a -180 degrees phase drop. Never place the crossover frequency beyond the corner frequency of the LC filter. If the crossover frequency is too close to the corner frequency, the controller should be designed to have a phase margin greater than 90 degrees when ignoring the effect of the post filter. (c) Determine the DC gain of the compensator (wi/wzc) to cancel the control-to-output gain at fc. (d) Place a compensator zero (fzc) around fc/3. (e) Place a compensator pole (fpc) above 3fc.

40 dB

fp

20 dB

Light load

fp

0 dB

Heavy load

-20 dB

fz

-40 dB 1Hz 10Hz 100Hz 1kHz

frz

f rz

10kHz

100kHz

Figure 14. CCM flyback converter control-to output transfer function variation for different loads

40 dB

Loop gain T

fp

40 dB

20 dB

fp

20 dB

Heavy load

0 dB

fzc fp fpc fc frz fz Compensator

0 dB

-20 dB

Light load

fz

-20 dB

Control to output

-40 dB 1Hz 10Hz 100Hz

fz

1kHz 10kHz 100kHz

-40 dB 1Hz 10Hz 100Hz 1kHz 10kHz 100kHz

Figure 15. DCM flyback converter control-to output transfer function variation for different loads

Figure 16. Compensator design

2003 Fairchild Semiconductor Corporation

10

APPLICATION NOTE

AN4137

When determining the feedback circuit component, there are some restrictions as follows. (a) The voltage divider network of R1 and R2 should be designed to provide 2.5V to the reference pin of the KA431. The relationship between R1 and R2 is given as

2.5 R 1 R 2 = ----------------------Vo1 2.5

ing the startup. While, too large a capacitor may increase the startup time. (b) Vcc resistor (Ra) : The typical value for Ra is 5-20. In the case of multiple outputs flyback converter, the voltage of the lightly loaded output such as Vcc varies as the load currents of other outputs change due to the imperfect coupling of the transformer. Ra reduces the sensitivity of Vcc to other outputs and improves the regulations of Vcc.

(36)

where Vo1 is the reference output voltage. (b) The capacitor connected to feedback pin (CB) is related to the shutdown delay time in an overload condition by

T delay = ( V SD 2.5 ) C B I delay

(37

where VSD is the shutdown feedback voltage and Idelay is the shutdown delay current. These values are given in the data sheet. In general, a 10 ~ 50 ms delay time is typical for most applications. Because CB also determines the high frequency pole (wpc) of the compensator transfer function as shown in equation (36), too large a CB can limit the control bandwidth by placing wpc at too low a frequency. Typical value for CB is 10-50nF. (c) The resistors Rbias and RD used together with the optocoupler H11A817A and the shunt regulator KA431 should be designed to provide proper operating current for the KA431 and to guarantee the full swing of the feedback voltage for the FPS device chosen. In general, the minimum cathode voltage and current for the KA431 are 2.5V and 1mA, respectively. Therefore, Rbias and RD should be designed to satisfy the following conditions.

V o1 V OP 2.5 ---------------------------------------- > I FB RD V OP ------------- > 1mA R bias

(38) (39)

where Vo1 is the reference output voltage, VOP is opto-diode forward voltage drop, which is typically 1V and IFB is the feedback current of FPS, which is typically 1mA. For example, Rbias< 1k and RD < 1.5k for Vo1=5V.

Miscellaneous

(a) Vcc capacitor (Ca) : The typical value for Ca is 10-50uF, which is enough for most application. A smaller capacitor than this may result in an under voltage lockout of FPS dur2003 Fairchild Semiconductor Corporation

11

AN4137

APPLICATION NOTE

- Summary of symbols Aw Ae Bsat Co(n) Dmax Eff fL fs Idspeak Idsrms Ids2 Iover Isec(n)rms ID(n)rms Icap(n)rms Io(n) KL(n) KRF Lm Llk Losssn Npmin Np Ns1 Ns(n) Po Pin Rc(n) Rsn RL Vlinemin Vlinemax VDCmin VDCmax Vdsnom Vo1 VF1 Vcc* VFa VD(n) Vo(n) VRO Vsn Vsn2 Vsn Vdsmax : Winding window area of the core in mm2 : Cross sectional area of the core in mm2 : Saturation flux density in tesla. : Output capacitor of the n-th output : Maximum duty cycle ratio : Estimated efficiency : Line frequency : Switching frequency of FPS : Maximum peak current of MOSFET : RMS current of MOSFET : Maximum peak drain current at the maximum input voltage condition. : FPS current limit level. : RMS current of the secondary winding for the n-th output : Maximum rms current of the rectifier diode for the n-th output : RMS Ripple current of the output capacitor for the n-th output : Output load current for the n-th output : Load occupying factor for the n-th output : Current ripple factor : Transformer primary side inductance : Transformer primary side leakage inductance : Maximum power loss of the snubber network in normal operation : The minimum number of turns for the transformer primary side to avoid saturation : Number of turns for primary side : Number of turns for the reference output : Number of turns for the n-th output : Maximum output power : Maximum input power : Effective series resistance (ESR) of the n-th output capacitor. : Snubber resistor : Effective total output load resistor of the controlled output : Minimum line voltage : Maximum line voltage : Minimum DC link voltage : Maximum DC line voltage : Maximum nominal MOSFET voltage : Output voltage of the reference output. : Diode forward voltage drop of the reference output. : Nominal voltage for Vcc : Diode forward voltage drop of Vcc winding : Maximum voltage of the rectifier diode for n-th output : Output voltage ripple for the n-th output : Output voltage reflected to the primary : Snubber capacitor voltage under minimum input voltage and full load condition : Snubber capacitor voltage under maximum input voltage and full load condition : Maximum Snubber capacitor voltage ripple : Maximum voltage stress of the MOSFET

2003 Fairchild Semiconductor Corporation

12

APPLICATION NOTE

AN4137

Appendix : Design example using FPS Design Assistant

Application Device Output Input voltage Output voltage (Max Current) Power

3.3V (2A) 5V (2A) 12V (1.5A) 18V (0.5A) 33V (0.1A)

Ripple spec

" 5% " 5% " 5% "5% "5%

Set-top Box

FSDM07652R

47W

85V-265VAC

$. Define the system specifications Minimum Line voltage (Vlinemin) Maximum Line voltage (Vlinemax) Line frequency (fL) Vo(n) $st output for feedback 2nd output 3rd output 4th output 5th output 6th output Maximum output power (Po) = Estimated efficiency (Eff)

85 V.rms 265 V.rms 60 Hz Io(n) 2.00 2.00 $.50 0.50 0.$0 Po(n) A A A A A A 7 $0 $8 9 3 0 W W W W W W KL(n) $4 2$ 38 $9 7 0

V V V V V V 46.9 W 70 %

3.3 5 $2 $8 33

% % % % % %

67.0 W Maximum input power (Pin) = ! The estimated efficiency (Eff) is set to be 0.7 considering the low voltage outputs (3.3V and 5V) 2. Determine DC link capacitor and DC link voltage range DC link capacitor (CDC) $50 uF

min Minimum DC link voltage (VDC ) = min

92 V 375 V

Maximum DC link voltage

(VDCmax)=

! Since the input power is 67 W, the DC link capacitor is set to be 150uF by 2uF/Watt.

3. Determine Maximum duty ratio (Dmax) Maximum duty ratio (Dmax) Max nominal MOSFET voltage = Output voltage reflected to primary (VRO)= (Vdsnom)

0.48 460 V 85 V

! Dmax is set to be 0.48 so that Vdsnom would be about 70% of BVdss (650V#0.7=455V) 4. Determine transformer primary inductance (Lm) Switching frequency of FPS (fs) 66 kHz 0.33 Ripple factor (KRF) 67$ uH Primary side inductance (Lm) = Maximum peak drain current (Idspeak) = RMS drain current

rms (Ids )

K RF = 1 ( DCM ) K RF < 1 (CCM )

I

I 2 I EDC

I EDC

2.0$ A $.07 A 375 V ##

K RF =

Maximum DC link voltage in CCM (VDCCCM)

2002 Fairchild Semiconductor Corporation

13

AN4137

APPLICATION NOTE

5. Choose the proper FPS considering the input power and current limit 2.50 A Typical current limit of FPS (Iover) 2.20 A > 2.0$ A ->O.K. ! Since the maximum peak drain current (Idspeak) is 2.0A, FSDM07652R is chosen, whose current limit level (Iover) is 2.5A. The current limit tolerance (12%) is considered. 6. Determine the proper core and the minimum primary turns Saturation flux density (Bsat) 0.35 T Cross sectional area of core (Ae) Minimum primary turns (Npmin)= mm2, $09.4 mm 43.8 T

2

Minimum Iover considering tolerance of $2%

! Ferrite core EER3530 is chosen (Ae=109.4 Aw=210mm2), which is a little bit larger than the core recommended in table 1 to provide enough winding window area.

7. Determine the number of turns for each output Vo(n) Vcc (Use Vcc start voltage) $st output for feedback 2nd output 3rd output 4th output 5th output 6th output VF : Forward voltage drop of rectifier diode Ungapped AL value (AL) Gap length (G) ; center pole gap = VF(n) # of turns $.2 V 6.9 => 7T 0.5 V 2 => 2T 0.5 V 2.9 => 3T $.2 V 6.9 => 7T $.2 V $0 T $0.$ => $.2 V $8.0 => $8 T 0V 0.0 => 0T Primary turns (Np)= 45 T --->enough turns 2$30 nH/T2 0.3463$ mm $2 3.3 5 $2 $8 33 0 V V V V V V V

! In general, the optimum turn ratio between 5V and 3.3V is 3/2, considering the diode forward voltage drop.

8. Determine the wire diameter for each winding Diameter 0.5 0.3 0.4 0.4 0.4 0.4 0.4 Parallel $T mm mm 2T mm 4T mm 4T mm 3T mm 2T mm $T mm T 2 $9.70 mm 0.$5 ID(n)rms $.$ 0.$ 3.5 3.7 2.8 0.9 0.2 #####

rms

Primary winding Vcc winding $st output winding 2nd output winding 3rd output winding 4th output winding 5th output winding 6th output winding Copper area (Ac) = Fill factor (KF) Required window area (Awr)

A A A A A A A A

(A/mm2) 5.44 0.7$ 6.97 7.30 7.30 3.76 $.55 #####

2 $3$.33 mm

! Since the windings for 3.3V and 5V are short with small number of turns, relatively large current densities (> 5A/mm2) are allowed. The fill factor is set to be 0.15 due to multiple outputs.

14

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4137

9. Choose the rectifier diode in the secondary side VD(n) Vcc diode $st output diode 2nd output diode 3rd output diode 4th output diode 5th output diode 6th output diode

Vcc winding 1st output (3.3V) 2nd output (5V) 3rd output (12V) 4st output (18V) 5st output (30V) UF4003 (200V /1A, VF=1V) SB540 (40V/5A, VF=0.55V) # 2 SB560 (60V/5A, VF=0.67V) # 2 EGP30D (200V/3A, VF=0.95V) EGP20D (200V/2A, VF=0.95V) UF4004 (400V /1A, VF=1V)

70 20 29 70 $03 $84 0

V V V V V V V

ID(n)rms 0.$0 3.50 3.67 2.75 0.95 0.$9 #####

A A A A A A A

Ultra Fast Recovery Diode Schottky Barrier Diode Schottky Barrier Diode Ultra Fast Recovery Diode Ultra Fast Recovery Diode Ultra Fast Recovery Diode

$0. Determine the output capacitor Co(n) $st output capacitor 2nd output capacitor 3rd output capacitor 4th output capacitor 5th output capacitor 6th output capacitor 2000 2000 330 470 47 uF uF uF uF uF uF RC(n) $00 $00 300 300 480 Icap(n) A A A A A A 'Vo(n) 0.64 0.67 $.53 0.52 0.$8 #####

m& 2.9 m& 3.$ m& 2.3 m& 0.8 m& 0.2 m& #####

V V V V V V

Since the voltage ripples for 3.3V, 5V and 12V exceed the ripple spec of " 5%, additional LC filter stage should be used for these three outputs. 220uF capacitor together with 2.2uH inductor are used for the post filter. To attenuate the voltage ripple caused by switching, the corner frequency of the post filter (fo) is set at about one decade below the switching frequency.

fo = 1 2 L p1C p1 = 10 6 2 2.2 220 = 7.2kHz

$$. Design RCD snubber Primary side leakage inductance (Llk) Maximum Voltage of snubber capacitor (Vsn) Maximum snubber capacitor voltage ripple Snubber resistor (Rsn)= Snubber capacitor (Csn)= Power loss in snubber resistor (Psn)=

max (Ids2) = Peak drain current at VDC

4.5 uH $90 5 33.$ 9.2 $.$ V % ( 0.$85 nF W (In Normal Operation)

$.75 A $72 V 547 V

Max Voltage of Csn at

VDCmax

(Vsn2)=

max (Vds )=

Max Voltage stress of MOSFET

! The snubber capacitor and snubber resistor are chosen as 10nF and 33k%, respectively. The maximum voltage stress on the MOSFET is designed to be 84% of 650V BVdss voltage of the FSDM07652R. The actual Vdsmax would be lower than this.

2002 Fairchild Semiconductor Corporation

15

AN4137

APPLICATION NOTE

$2. Design Feedback control loop Control-to-output Control-to-output Control-to-output Control-to-output DC gain = zero (wz) = RHP zero (wrz)= pole (wp)= 2 5000 rad/s => fz= 694765 rad/s => frz= 2$53 rad/s => fp= 5.6 ( $8 $ $.2 33 47 $.2 ( ( ( nF nF (

FPS vFB iD 1:1

796 Hz $$0,63$ Hz 343 Hz

vo1'

RD ibias Rbias

Voltage divider resistor (R$) Voltage divider resistor (R2)= Opto coupler diode resistor (RD) KA43$ Bias resistor (Rbias) Feeback pin capacitor (CB) = Feedback Capacitor (CF) = Feedback resistor (RF) = Feedback integrator gain (wi) = Compensator zero (wzc)= Compensator pole (wpc)=

60 40 Gain (dB) 20 0 $0 -20 -40 $00

vo1

CB

B

CF

RF

R1

KA431 R2

$$398 rad/s => fi= 3$29 rad/s => fzc= $0$0$ rad/s => fpc=

$,8$5 Hz 498 Hz $,608 Hz

0 $0 -30 Phase (degree) -60 -90 -$20 -$50 -$80 $00

$6 3.64$05 25 3.63 40 3.60099 63 3.53$67 $00 3.36222 $60 2.965$6 250 2.20575 400 $000 0.89557 630 -0.650$ $000 -2.0$85 $600 -2.90$6 2500 -3.3275 4000 -3.5257 frequency (Hz) 6300 -3.5983 $0000 -3.6$07 $6000 -3.5697 $000 25000 -3.4485 40000 -3.$334 63000 -2.448 $00000 -$.0745

4$ 37 33 29 25 2$ $8 $5 $3 $$ 9 6 3 -$ -5 -9 # # # #

44.7 $6 -2 -88.7 Control-to-output 40.9 25 -2 -88 36.8 Compensator 40 -4 -86.8 32.8 T (Close 63 -6 gain) -85 d loop 28.7 $00 -9 -82.2 24.4 $60 ## -77.9 20.3 250 ## -72.2 $5.9 400 ## $00000 -65.2 $0000 $2.$ 630 ## -59.7 8.75 $000 ## -58.3 5.74 $600 ## -62.$ 2.74 2500 ## -68.5 -0.8 4000 -8 -75.2 -4.5 6300 -7 -80.2 -8.4 $0000 -8 -83.7 -$2 $6000 ## -86 $0000 $00000 -$6 25000 ## -87.5 -20 40000 ## -88.4 -23 63000 ## -89 -26 $E+05 ## -89.4

# # # # # # # # # # # # # # # # # # # #

frequency (Hz)

! The control bandwidth is 4kHz. Since the crossover frequency is too close to the corner frequency of the post filter (fo=7.2 kHz), the controller is designed to have enough phase margin when ignoring the effect of the post filter.

16

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4137

Design Summary

For the FPS, FSDM07652R is chosen. This device has a fixed switching frequency of 66kHz. Startup and soft-start circuits are implemented inside the device. To limit the current, 10 ohms resistors (Ra and Rdamp) are used in series with Da and DR5. These damping resistors improve the regulations of the very lightly loaded outputs. Figure 17 shows the final schematic of the flyback converter designed by FPS Design Assistant.

VO5 33V

NS5 DR5

UF4004

Rdamp 10

Co5

47uF/ 50V

VO4 18V

NS4 DR4

EGP20D

Co4

470uF/25V

DR3 NS3

Lp3

EGP30D

VO3 12V

2.2 uH

Co3

330uF/25V

Cp3

220uF/ 25V

GBLA06

Rsn

CDC

150uF/400V

33k 2W

Csn

10nF 1kV

Np

Lp2

DR2

SB560

VO2 5V

2.2 uH

Dsn

NS2

UF4007

Co2

1000uF# 2 /10V

Cp2

220uF/ 10V

6

Vstr

1.5nF/275Vac

Drain Vcc

1

UF4003

Lp1

DR1

NS1

SB540

VO1 3.3V

2.2 uH

CL2

CL2

FPS (DM07652R)

R a 10

Da

Co1

1000uF# 2 /10V

Cp1

220uF/ 10V

Line Filter (33mH)

FB

GND

Ca

Na

33uF/35V

CL1

0.47uF/275Vac

1k

Rd

Rbias

H11A817A H11A817A

1.2k

RF KA431

AC line

1k

5.6k

R1

RL1 NTC 5D-13

1.5M

CB

47nF

CF

33nF

Fuse

18k

R2

Figure 17. The final schematic of the flyback converter

2003 Fairchild Semiconductor Corporation

17

AN4137

APPLICATION NOTE

Experimental Verification

In order to show the validity of the design procedure presented in this paper, the converter of the design example has been built and tested. All the circuit components are used as designed in the design example and the measured transformer characteristics are shown in table 3. Figure 18 shows the FPS drain current and DC link voltage waveforms at the minimum input voltage and full load condition. As can be seen, the maximum peak drain current (Idspeak) is 2A and the minimum DC link voltage (VDCmin) is about 90V. The designed values are 2.01A and 92V, respectively. Figure 19 shows the FPS drain current and voltage waveforms at the minimum input voltage and full load condition. As designed, the maximum duty ratio (Dmax) is about 0.5 and the maximum peak drain current (Idspeak) is 2A. Figure 20 shows the FPS drain current and voltage waveforms at the maximum input voltage and full load condition. The maximum voltage stress on the MOSFET is about 520V, which is lower than the designed value (547V). This is because of the lossy discharge of the inductor or the stray capacitance. Another reason is that the power conversion efficiency at the maximum input voltage is higher than the estimated efficiency used in step-1. As calculated in design step-4, the converter operates at the boundary between CCM and DCM under the maximum input voltage and full load condition (The maximum DC link voltage guaranteeing CCM at full load was obtained as 375V in design step-4). Figure 21 shows the current and voltage waveforms of the first output (3.3V) rectifier diode. The maximum reverse voltage of this diode was calculated as 20V in step-9 and the measured value is 23V. Table 4 shows the line regulation of each output. 3.3V and 5V output shows 3% and 4% regulations, respectively. Figure 22 shows the measured efficiency at the full load condition for different input voltages. The minimum efficiency is about 73% at the minimum input voltage condition better than the 70% target efficiency specified in step-1.

Figure 19. Waveforms of drain current and voltage at 85Vac and full load condition (time : 5us/div) Figure 18. Waveforms of drain current and DC link voltage at 85Vac and full load condition (time:2ms/div)

Core Primary side inductance Leakage inductance Resistance

EER3530 (ISU ceramics) 682 uH @ 70kHz 4.5 uH @70kHz with all other windings shorted. 0.76

Table 3. The measured transformer characteristics Figure 20. Waveforms of drain current and voltage at 265Vac and full load condition (time : 5us/div)

18

2002 Fairchild Semiconductor Corporation

APPLICATION NOTE

AN4137

Efficiency

0.81 0.80 0.79 0.78 0.77 0.76 0.75 0.74 0.73 0.72

85 115 145 175 205 235 265

Input voltage (Vac)

Figure 22. Measured efficiency Figure 21. Current and voltage waveforms of the first output (3.3V) rectifier diode at 265Vac and full load condition (time : 5us/div)

Input voltage 85Vac 115Vac 145Vac 175Vac 205Vac 235Vac 265Vac

Vo1 (3.3V)

3.21 V

Vo2 (5V)

5.18 V

Vo3 (12V)

12.88 V

Vo4 (18V)

19.7 V

Vo5 (33V)

35.7 V

-2.7 %

3.21 V

3.6 %

5.14 V

7.3 %

12.77 V

9.4 %

19.4 V

8.2 %

34.6 V

-2.7 %

3.21 V

2.8 %

5.11 V

6.4 %

12.67 V

7.8 %

19.2 V

4.8 %

34.1 V

-2.7 %

3.21 V

2.2 %

5.09 V

5.6 %

12.57 V

6.7 %

19.1 V

3.2 %

33.8 V

-2.7 %

3.21 V

1.8 %

5.08 V

4.8 %

12.52 V

5.9 %

19.0 V

2.4 %

33.6 V

-2.7 %

3.21 V

1.6 %

5.07 V

4.3 %

12.48 V

5.4 %

18.9 V

1.9 %

33.5 V

-2.7 %

3.21 V

1.4 %

5.06 V

4.0 %

12.47 V

5.1 %

18.9 V

1.6 %

33.5 V

-2.7 %

1.2 %

3.9 %

5.1 %

1.4 %

Table 4. Line regulation of each output at full load condition

2002 Fairchild Semiconductor Corporation

19

AN4137

APPLICATION NOTE

by Hang-Seok Choi / Ph. D FPS Application Group / Fairchild Semiconductor Phone : +82-32-680-1383 Facsimile : +82-32-680-1317 E-mail : hschoi@fairchildsemi.co.kr

DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPROATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com 1/13/04 0.0m 002 Stock#ANxxxxxxxxx 2003 Fairchild Semiconductor Corporation

Vous aimerez peut-être aussi

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsD'EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training ManualevaristoPas encore d'évaluation

- Design Battery ChargerDocument20 pagesDesign Battery Chargeranand_girgaonkar100% (1)

- PFC Boost Converter Design Guide - Infineon - Infineon-ApplicationNote - PFCCCMBoostConverterDesignGuide-An-V02 - 00-EnDocument31 pagesPFC Boost Converter Design Guide - Infineon - Infineon-ApplicationNote - PFCCCMBoostConverterDesignGuide-An-V02 - 00-Enkik020Pas encore d'évaluation

- Buck Boost ConverterDocument17 pagesBuck Boost Converteramohdzah100% (2)

- Intel Processor Power Delivery DesignDocument13 pagesIntel Processor Power Delivery DesignE.I.OSEPas encore d'évaluation

- Single Supply Op Amp ApplicationsDocument27 pagesSingle Supply Op Amp ApplicationsStephen Dunifer100% (12)

- +zener Voltage RegulationDocument4 pages+zener Voltage RegulationtrshaaaPas encore d'évaluation

- Caterpillar sr4 Generator Service ManualDocument6 pagesCaterpillar sr4 Generator Service Manuals ss100% (4)

- Simple FSKDocument6 pagesSimple FSKFaten AliPas encore d'évaluation

- DC Regulated Power Supply ExplainedDocument14 pagesDC Regulated Power Supply ExplainedMegha Projects100% (2)

- An 4137Document20 pagesAn 4137Andres RinconPas encore d'évaluation

- An 4134Document14 pagesAn 4134shri.bhairavkar6977Pas encore d'évaluation

- Funcionamiento Del 5Q1265RF en La FuenteDocument19 pagesFuncionamiento Del 5Q1265RF en La FuenteJorge Corrales100% (1)

- An 4140Document11 pagesAn 4140Anonymous j7toV6z7PPas encore d'évaluation

- Bien AP XungDocument11 pagesBien AP XungVan Thanh TranPas encore d'évaluation

- An 4140Document11 pagesAn 4140ommidbePas encore d'évaluation

- Universal Block DiagramDocument6 pagesUniversal Block Diagramapneetsandhu1234Pas encore d'évaluation

- Design Guideline For Flyback Charger Using FAN302HL/ULDocument20 pagesDesign Guideline For Flyback Charger Using FAN302HL/ULteomondoPas encore d'évaluation

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Document16 pagesApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaPas encore d'évaluation

- Step-ByStep Flyback SMPS DesignDocument6 pagesStep-ByStep Flyback SMPS DesignPhạm Văn TưởngPas encore d'évaluation

- Transformer Design Consideration For Off Line Flyback Converters Using Fairchild Power Switch (FPS™)Document10 pagesTransformer Design Consideration For Off Line Flyback Converters Using Fairchild Power Switch (FPS™)StefanvnvPas encore d'évaluation

- LM5032 INTERLEAVED BOOST CONVERTER DESIGNDocument12 pagesLM5032 INTERLEAVED BOOST CONVERTER DESIGNParvesh GautamPas encore d'évaluation

- An-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpDocument16 pagesAn-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpbmmostefaPas encore d'évaluation

- Compensation Method Peak Current Mode Control Buck AN028 enDocument13 pagesCompensation Method Peak Current Mode Control Buck AN028 ensadqazwsxPas encore d'évaluation

- Designing DC-DC Converters Based On ZETA TopologyDocument8 pagesDesigning DC-DC Converters Based On ZETA TopologyMayeth MacedaPas encore d'évaluation

- An Efficiency Primer For Switch-Mode, DC-DC Converter Power SuppliesDocument11 pagesAn Efficiency Primer For Switch-Mode, DC-DC Converter Power SuppliesJonathan JaegerPas encore d'évaluation

- Improved Power Quality AC-DC Converters With High Frequency Transformer IsolationDocument69 pagesImproved Power Quality AC-DC Converters With High Frequency Transformer IsolationZlatian RaduPas encore d'évaluation

- Trabajo 2Document18 pagesTrabajo 2ing_pemPas encore d'évaluation

- Application Note ANP 16: Loop Compensation of Voltage-Mode Buck ConvertersDocument9 pagesApplication Note ANP 16: Loop Compensation of Voltage-Mode Buck ConvertersNguyen Thanh TuanPas encore d'évaluation

- Group4 EECS511 Huang&SuDocument5 pagesGroup4 EECS511 Huang&SuDivya ReddyPas encore d'évaluation

- An 1162Document36 pagesAn 1162naniknanikPas encore d'évaluation

- Inrush_2016_R2Document9 pagesInrush_2016_R2AuslanderPas encore d'évaluation

- AND9218/D 5 Key Steps To Designing A Compact, High Efficiency PFC Stage Using The NCP1602Document19 pagesAND9218/D 5 Key Steps To Designing A Compact, High Efficiency PFC Stage Using The NCP1602Jonatan LunaPas encore d'évaluation

- Digital PSS Control for Flyback ConvertersDocument6 pagesDigital PSS Control for Flyback ConvertersSusellePas encore d'évaluation

- Maxim MAX5072/3 Buck/Boost Converter Configuration ToolDocument13 pagesMaxim MAX5072/3 Buck/Boost Converter Configuration ToolJc Jayamanikandan BPas encore d'évaluation

- 3.4.2 Output Capacitor: Out C, Max OutDocument14 pages3.4.2 Output Capacitor: Out C, Max OutReza RzPas encore d'évaluation

- An Ultra-Low-Power Digitally-Controlled Buck Converter ICDocument9 pagesAn Ultra-Low-Power Digitally-Controlled Buck Converter ICrmsharma1970Pas encore d'évaluation

- AND8182Document6 pagesAND8182carlos_eqnPas encore d'évaluation

- Modeling and Simulation of PFC ConvertersDocument93 pagesModeling and Simulation of PFC ConvertersSanjeev Singh100% (1)

- Design and Implementation of PFC CUK Converter-Based PMBLDCM DriveDocument5 pagesDesign and Implementation of PFC CUK Converter-Based PMBLDCM Drivesarav03Pas encore d'évaluation

- DC-DC Converters 2014-2015Document20 pagesDC-DC Converters 2014-2015MD. ASHIQUR RAHMAN 1602111Pas encore d'évaluation

- Implementing The TL431 Feedback LoopDocument10 pagesImplementing The TL431 Feedback LoopAnand KumarPas encore d'évaluation

- AN-4102: Colour TV Receiver SMPSDocument16 pagesAN-4102: Colour TV Receiver SMPSshri.bhairavkar6977Pas encore d'évaluation

- PWM To DC Voltage Conversion: Kyle Burgess 4/3/2015Document8 pagesPWM To DC Voltage Conversion: Kyle Burgess 4/3/2015NaranLoganPas encore d'évaluation

- Samsung Plasma Training ManualDocument57 pagesSamsung Plasma Training ManualDamiao100% (1)

- An 1173 PDFDocument21 pagesAn 1173 PDFM. T.Pas encore d'évaluation

- An 1173Document21 pagesAn 1173M. T.Pas encore d'évaluation

- Flyback Converter Design ThesisDocument8 pagesFlyback Converter Design Thesisleanneuhlsterlingheights100% (2)

- And8328 DDocument8 pagesAnd8328 DJonatan LunaPas encore d'évaluation

- 13.56 MHZ, Class D Push-Pull, 2KW RF GeneratorDocument17 pages13.56 MHZ, Class D Push-Pull, 2KW RF GeneratorettorepellegriniPas encore d'évaluation

- Document 1Document8 pagesDocument 1Ali HassanPas encore d'évaluation

- PFC Rectifier DesignDocument19 pagesPFC Rectifier DesignhellwellPas encore d'évaluation

- Single-Phase SEPIC Based PFC Converter For PMBLDCM Drive in Air-Conditioning SystemDocument6 pagesSingle-Phase SEPIC Based PFC Converter For PMBLDCM Drive in Air-Conditioning Systemsarav03Pas encore d'évaluation

- DC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Document22 pagesDC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Harkishen SinghPas encore d'évaluation

- Iscas06 Curr RefDocument4 pagesIscas06 Curr Refkareka_ccPas encore d'évaluation

- 90204diDocument8 pages90204diadialaktosPas encore d'évaluation

- Design Cicuit Power Electronic by PSIMDocument14 pagesDesign Cicuit Power Electronic by PSIMTrương Văn TrọngPas encore d'évaluation

- A High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationDocument5 pagesA High Efficiency Bridgeless Flyback PFC Converter For Adapter ApplicationAshwin Kumar JPas encore d'évaluation

- Power Systems-On-Chip: Practical Aspects of DesignD'EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardPas encore d'évaluation

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesD'EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesPas encore d'évaluation

- SMPS Boost Using MCU 91053bDocument6 pagesSMPS Boost Using MCU 91053bdgujarathiPas encore d'évaluation

- DS18B20 - Programmable Resolution 1 Wire ThermometerDocument22 pagesDS18B20 - Programmable Resolution 1 Wire ThermometerKathryn WorkmanPas encore d'évaluation

- PIC16F877ADocument26 pagesPIC16F877ALuis Alonso ValenciaPas encore d'évaluation

- 01211BDocument14 pages01211BrajeshgautPas encore d'évaluation

- An52478 001-52478Document15 pagesAn52478 001-52478Đặng Văn TàiPas encore d'évaluation

- Solar MPPTDocument16 pagesSolar MPPTKiran ZoroPas encore d'évaluation

- MPP Tat MegaDocument153 pagesMPP Tat MegaĐặng Văn TàiPas encore d'évaluation

- 125 Cau Hoi Tra Loi Khi Phong Van Xin Viec Bang Tieng AnhDocument91 pages125 Cau Hoi Tra Loi Khi Phong Van Xin Viec Bang Tieng AnhNam Nghĩa HưngPas encore d'évaluation

- Ghep Noi Mosfet Tăng Cong SuatDocument12 pagesGhep Noi Mosfet Tăng Cong SuatĐặng Văn TàiPas encore d'évaluation

- Tidu 219Document17 pagesTidu 219Joao Carlos DrumondPas encore d'évaluation

- Thu T Toán MPPT V I PicDocument5 pagesThu T Toán MPPT V I PicĐặng Văn TàiPas encore d'évaluation

- PIC Instruction ReferenceDocument14 pagesPIC Instruction ReferenceĐặng Văn TàiPas encore d'évaluation

- Driver Motor BrushlesDocument48 pagesDriver Motor BrushlesGONAJ2008Pas encore d'évaluation

- Evolutionary Programming Based Economic Dispatch For Units With Non Smooth Fuel Cost FunctionsDocument7 pagesEvolutionary Programming Based Economic Dispatch For Units With Non Smooth Fuel Cost FunctionsĐặng Văn TàiPas encore d'évaluation

- Mach Do LuongDocument1 pageMach Do LuongĐặng Văn TàiPas encore d'évaluation

- Pc817 DatasheetDocument5 pagesPc817 DatasheetprincebahariPas encore d'évaluation

- Fly BackDocument20 pagesFly BackĐặng Văn TàiPas encore d'évaluation

- Ifr 840Document8 pagesIfr 840Đặng Văn TàiPas encore d'évaluation

- LM7812 DatasheetDocument9 pagesLM7812 Datasheetdmente1757Pas encore d'évaluation

- General Description Product Summary: 30V P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V P-Channel MOSFETM Romadi SiregarPas encore d'évaluation

- Load Line Analysis PDFDocument2 pagesLoad Line Analysis PDFVikas GaurPas encore d'évaluation

- Irfb4321 IorDocument8 pagesIrfb4321 IorDavi FienniPas encore d'évaluation

- 01 Semiconductor TheoryDocument32 pages01 Semiconductor TheoryAnmay MishraPas encore d'évaluation

- PDF Create 8 Trial: AOD9N40Document6 pagesPDF Create 8 Trial: AOD9N40ewertonPas encore d'évaluation

- Fully Protected Power Mosfet Switch: IRSF3010Document11 pagesFully Protected Power Mosfet Switch: IRSF3010Alvaro FloresPas encore d'évaluation

- Product Catalog & Design Guide: Gas Discharge Tube (GDT) ProductsDocument60 pagesProduct Catalog & Design Guide: Gas Discharge Tube (GDT) ProductsMisko PiskoPas encore d'évaluation

- PSIM User Manual PDFDocument162 pagesPSIM User Manual PDFnhungdieubatchotPas encore d'évaluation

- EDC 2 Marks Q ADocument16 pagesEDC 2 Marks Q Akunaraj100% (3)

- Seminar Topic On Speed Control of DC Motor Using TRIACDocument18 pagesSeminar Topic On Speed Control of DC Motor Using TRIACRicha0001100% (1)

- Elect 3 PDFDocument22 pagesElect 3 PDFmudasirPas encore d'évaluation

- EAO Series 84 Full DataDocument50 pagesEAO Series 84 Full DataAidolan UlrichPas encore d'évaluation

- STP40N20-STF40N20: STB40N20 - STW40N20Document14 pagesSTP40N20-STF40N20: STB40N20 - STW40N20Rodrigo GarcetePas encore d'évaluation

- 3.4 Rectifier Circuits: Chapter 3. Diodes and RectifiersDocument16 pages3.4 Rectifier Circuits: Chapter 3. Diodes and RectifiersAlan PakarPas encore d'évaluation

- Spice Model of DiodeDocument20 pagesSpice Model of DiodeharizPas encore d'évaluation

- Ch01 PDFDocument14 pagesCh01 PDFTemesgen ZelekePas encore d'évaluation

- AUIRF3710Z AUIRF3710ZS: Automotive GradeDocument14 pagesAUIRF3710Z AUIRF3710ZS: Automotive GradeSaad LehlouPas encore d'évaluation

- Dome Camera Service ManualDocument49 pagesDome Camera Service ManualactivnetPas encore d'évaluation

- Ett Study GuideDocument8 pagesEtt Study Guidepatitay036817Pas encore d'évaluation

- Analysis of Electrical Characteristics of Solar Cell Employing Matlab/SimulinkDocument9 pagesAnalysis of Electrical Characteristics of Solar Cell Employing Matlab/SimulinkMarco Antonio Pérez FernándezPas encore d'évaluation

- Diode Applications GuideDocument51 pagesDiode Applications GuideRaniel Rey CantorPas encore d'évaluation

- Name of The Post: JOT-CUM-TA: Roll NoDocument13 pagesName of The Post: JOT-CUM-TA: Roll NoNandan SarkarPas encore d'évaluation

- TIU Diploma 2nd SEMDocument13 pagesTIU Diploma 2nd SEMTechno India UniversityPas encore d'évaluation

- Testing Schottky DiodeDocument3 pagesTesting Schottky DiodemaxxPas encore d'évaluation

- Power Transistor: SPP11N60S5, SPB11N60S5 SPI11N60S5 Cool MOS™Document12 pagesPower Transistor: SPP11N60S5, SPB11N60S5 SPI11N60S5 Cool MOS™Abo AdamPas encore d'évaluation

- Scavenging For EnergyDocument9 pagesScavenging For EnergymoonyraPas encore d'évaluation

- Tta Study MaterialDocument18 pagesTta Study Materialasheokand172Pas encore d'évaluation