Académique Documents

Professionnel Documents

Culture Documents

Luis Terrazas

Transféré par

Melisa PortilloDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Luis Terrazas

Transféré par

Melisa PortilloDroits d'auteur :

Formats disponibles

Abstract An analytical extrinsic gate capacitance model based on threedimensional numerical simulations for Triple Gate FinFET, was

s developed. The model considers the source/drain electrode and contact areas. It is compound for 9 capacitance components which describes the different fringing electrical couplings that appears inside the FinFET structure. The analytical model accurately calculates the total extrinsic gate capacitance as function of main geometrical parameters of Triple-Gate FinFET. Index Terms FinFETs, Extrinsic Capacitance, Fringing Gate Capacitance, Fringing Electric Field. I. INTRODUCTION The last years, FinFET has demonstrated be a promising candidate to carry on with downscaling of CMOS technology, due to his superior control of the short channel effects (SCE). Nevertheless, since their three-dimensional structure, FinFETs show high parasitic resistances and capacitances which lead to strong degradation of their analog and RF performance [1][2]. Improvements can be reached, especially concerning to reduction of the total extrinsic gate capacitance (Cgge). The FinFETs RF model is based on the well-known small-signal equivalent circuit (SS-EC) and implies an accurate determination both intrinsic and extrinsic parameters. Thus, a compact model which determine the DC and intrinsic RF parameters was demonstrated [3]. To complete the SS-EC, is requiered an accurate extrinsic capacitance model which are strongly dependent on the FinFET geometry. Recently, Wu and

Chan [1] developed a semi-analytical model to describe total extrinsic gate capacitance of double-gate FinFETs. Fig. 1a shows a schematic representation of the structure used and identifies the main FinFET geometrical parameters. Three capacitance components associated to the FinFET structure were considered, as Figs. 1b to 1d

Figure 1 Fi FET h i i i h 2 schematic representations of the different capacitance components associated to the 3-D structure.

the gate electrode to the internal side of h S/D fi x i I h the S/D electrode regions are not considered and thus some important parasitic capacitances are not modeled while they are not negligible. In this paper, based on 3-D numerical simulations, a semi-analytical model for the extrinsic gate capacitances for TripleGate FinFETs is presented. This model includes the S/D electrode and contact areas and the interactions between gates in order to overcome the limitations of previous models and thus provide a complete and accurate modeling of the total extrinsic gate capacitance valid for

a wide range of FinFET geometries.

II. THE COMPACT MODEL

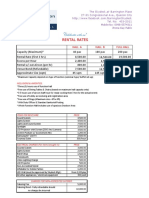

In a tridimensional FinFET structure there are some typical capacitor structures like: (I) parallel plate capacitor, (II) perpendicular plate capacitor, (III) flat plate non parallel capacitor, (IV) fringing field capacitive component, (V) Capacitancia de una lnea bifilar monofsica

Structure Expresion (I)

c)

d)

e)

f)

g)

h)

(II) ( (III) ( (IV) ( ) (V) ( )

Table 1. Simple capacitance expressions Figure 2. Schematic representations of the five capacitance components, C1-C9, considered in our proposed compact model.

)

i)

Including the S/D contact reas and the capacitance effects between gates, based on the classical capacitance formulations presented in Table I, we propose a compac model with nine extrinsic capacitance components as illustrated Figure 2.

The first component C1 (Fig. 2a) can be represented as flat-plate nonparallel structure, exhibing dependence with Lfin, Lext, Wfin, Tpoly, and tox, and can be expressed as:

(1) ( ( ( ) ) ( ))

a)

b)

( (

) )

)) (

( ( )

))

(4)

we divide these components in two cases, for inner case (between gates) was developed C1i and for the outer case C1e (for FinFET end) C2 component (Fig 2b), depends of Lext, Wfin, Tpoly, and tox, similarly to C1 have two cases and its base on perpendicular

C5 was obtained with perpendicular

plate capacitor case, thos component correspond from the side of the gate electrode located above the fin spacing and the top of the S/D contact regin

( ( ( ) )) (5)

plate capacitor case.

(2) ( ( ( ( ) ) ( ( )) ))

Four cases were developed considering that there are capacitive effect between the gates. The first one Considering a parallel plate capacitor we derive C6 component, which depends of separation between gates (2(Lext)+Wcon) with lenght Sfin+Wfin and high Tpoly+tox.

( )( ) (6)

( ( ( (

) )

( ( ))

))

C3 component was developed taking on account that both capacitances parallel plate and perpendicular plate occurs at the same time, showing dependance of Hfin, Sfin, Lext and tox

(3) ( ) ( )

For C7 component was based (V) case, by not considering cilinders, neglecting and taking r as gate width

( ( ) ) (7)

C4 come in to a flat plate non parallel

C8 and C9 component was developed observing that wasnt previously considered the effect of the gate side (Tpoly) to the internal contact portion and the lower adjacent gate

(8) ( ( )) ( (9) )

capacitance, which corresponds to the capacitance from the top of the gate electrode to the top the S/D contact regin and exhibits dependences with of Tpoly, Lext, Sfin and Wcon

( (

))

Because RF transistors consist of multi-fin devices, the total gate capacitance per gate finger is defined by the sum of the whole components expressed by (1)-(9), considering that we develop the model with inner and outer components we add the components as:

( ( ( ) ( ) ( ) [( ) ) ( ( )] ) )

Wcon, Sfin, Wfin, Lfin and Hfin. The compact model has been validated for a wide range of FinFETs dimensions. Simulation results show optimization paths to decrease the impact of extrinsic capacitances, such as the reduction of fin spacing Sfin, the S/D fin extension Lext as well as by increasing the fin aspect ratio (Hfin/Wfin). The proposed compact model is of great interest for designers considering FinFET technology for highspeed digital and RF applications. REFERENCES 1 M Ch A y i f geometry-dependent parasitics in multifin Double-G Fi FET IEEE TED v 54, no. 4, pp. 692-698, April 2007. 2 J C Ti I f extrinsic capacitances on FinFETs RF f i 2012 12 h SiRF 7376. 3 J Av Sig M f 8th ICCDCS. C S RF Fi FET i 2012

III. SIMULATIONS

Tridimensional finite element numerical simulations were performed in order to verify the developed compact. Simple structures were used to analyze each capacitance component, finally the full FinFET structure was used to verify the total gate capacitance.

IV. RESULTS

4 D G O -chip interconnectaware design and modeling methodology, based on high bandwidth transmission i vi i 2003 41 DAC 724727.

V. CONCLUSION

An analytical model for extrinsic gate capacitance for Triple-Gate FinFET is presented. The model considers he S/D contact region and includes five capacitance components. It is based on simple capacitor structures and describes the dependences with the main geometrical FinFET parameters: Lext,

Vous aimerez peut-être aussi

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Infrared Based Visitor CounterDocument21 pagesInfrared Based Visitor CounterRahul KumarPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- CMO 24 s2008 Annex IVB List of LABORATORY Requirements For ECEDocument31 pagesCMO 24 s2008 Annex IVB List of LABORATORY Requirements For ECEcathyPas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Roland TD-3 Service NotesDocument20 pagesRoland TD-3 Service NotesAlexanderPas encore d'évaluation

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Roubik Gregorian-Introduction To CMOS OP-AMPs and Comparators-Wiley (1999)Document369 pagesRoubik Gregorian-Introduction To CMOS OP-AMPs and Comparators-Wiley (1999)Maanas Khurana50% (2)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Dit University Laboratory Manual Practical Instruction SheetDocument4 pagesDit University Laboratory Manual Practical Instruction SheetDev Narayan UniyalPas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Recent Advances On Hybrid Integration of 2D Materials On Integrated Optics PlatformsDocument24 pagesRecent Advances On Hybrid Integration of 2D Materials On Integrated Optics PlatformsArka GhoshPas encore d'évaluation

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- DS-K1T804AMF Fingerprint Access Control TerminalDocument3 pagesDS-K1T804AMF Fingerprint Access Control TerminalLuis RomeroPas encore d'évaluation

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- BorgWarner DC Fast Charger 120kW (Iperion-120)Document2 pagesBorgWarner DC Fast Charger 120kW (Iperion-120)gjmentinkPas encore d'évaluation

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- 3 Embedded Systems - Raj KamalDocument37 pages3 Embedded Systems - Raj KamalAshokkumar ManickamPas encore d'évaluation

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- lm3524 PWM PDFDocument8 pageslm3524 PWM PDFIon MoldoveanuPas encore d'évaluation

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- 2.3.1.1 WAN Device Modules Instructions - IGDocument5 pages2.3.1.1 WAN Device Modules Instructions - IGJavier Sacán50% (2)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- V7N Drive With Devicenet Technical Manual: Models: Cimr-V7Nu Document Number: Tm.V7N.01Document198 pagesV7N Drive With Devicenet Technical Manual: Models: Cimr-V7Nu Document Number: Tm.V7N.01Julio FerminPas encore d'évaluation

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- 5.4 LTE950: FPFC Flexi Power Distribution Module: 5.4.1 BenefitsDocument2 pages5.4 LTE950: FPFC Flexi Power Distribution Module: 5.4.1 BenefitsReza BordbarPas encore d'évaluation

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- 3KW 5KW User Manual 20201012Document37 pages3KW 5KW User Manual 20201012Amith Prasanna0% (1)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- AE Previous Papers EEEDocument9 pagesAE Previous Papers EEESathiya RajPas encore d'évaluation

- Motorola Power Controller: by Sasi Kumar C Development EngineerDocument68 pagesMotorola Power Controller: by Sasi Kumar C Development EngineerVenkat RaoPas encore d'évaluation

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Hardware Overview (Chapter 2)Document74 pagesHardware Overview (Chapter 2)shkytenkoPas encore d'évaluation

- 1.boolean Expressions With VHDL (241-248)Document8 pages1.boolean Expressions With VHDL (241-248)a.ddgnPas encore d'évaluation

- Zoom A3 Manual 475877 PDFDocument44 pagesZoom A3 Manual 475877 PDFNPUIUPas encore d'évaluation

- Skydeck 2017 Rental RatesDocument1 pageSkydeck 2017 Rental RatesKatherinePas encore d'évaluation

- Indian Regional Navigation Satellite System (IRNSS)Document19 pagesIndian Regional Navigation Satellite System (IRNSS)neeraj aggarwalPas encore d'évaluation

- Atoll The RF Planning ToolDocument16 pagesAtoll The RF Planning Toolloc2002Pas encore d'évaluation

- Tone Drum Kit ManualDocument3 pagesTone Drum Kit ManualcrackintheshatPas encore d'évaluation

- Inam BEET 4833 CHP1-b-INTRODUCTION AND FUNDAMENTALS OF ANTENNADocument49 pagesInam BEET 4833 CHP1-b-INTRODUCTION AND FUNDAMENTALS OF ANTENNAKishen KunalanPas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Tmdrive - MV: Ac Drive SystemDocument10 pagesTmdrive - MV: Ac Drive SystemkaihaniPas encore d'évaluation

- Zwf22!02!051 Atm Over E1Document27 pagesZwf22!02!051 Atm Over E1likamelePas encore d'évaluation

- M 8212X1Document63 pagesM 8212X1Imran AlamPas encore d'évaluation

- Canon IR2530 Error CodesDocument10 pagesCanon IR2530 Error CodesnafeesPas encore d'évaluation

- DTEN D7 55": All-in-One Video Conferencing and Collaboration SolutionDocument1 pageDTEN D7 55": All-in-One Video Conferencing and Collaboration SolutionG & M Soft Technologies Pvt LtdPas encore d'évaluation

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- LT-493 FA-1025T Installation and Operation ManualDocument22 pagesLT-493 FA-1025T Installation and Operation ManualpaulPas encore d'évaluation

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)