Académique Documents

Professionnel Documents

Culture Documents

Decoder

Transféré par

techzonesCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Decoder

Transféré par

techzonesDroits d'auteur :

Formats disponibles

Decoder

Decoder

A decoder is a device which does the reverse operation of an encoder, undoing the encoding so that the original information can be retrieved. The same method used to encode is usually just reversed in order to decode. It is a combinational circuit that converts binary information from n input lines to a maximum of 2n unique output lines.

A Digitrax DH163AT DCC decoder in an Athearn locomotive before the shell goes on.

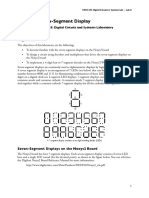

In digital electronics, a decoder can take the form of a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different. e.g. n-to-2n, binary-coded decimal decoders. Enable inputs must be on for the decoder to function, otherwise its outputs assume a single "disabled" output code word. Decoding is necessary in applications such as data multiplexing, 7 segment display and memory address decoding.

A 2-to-4 line single-bit decoder

The example decoder circuit would be an AND gate because the output of an AND gate is "High" (1) only when all its inputs are "High." Such output is called as "active High output". If instead of AND gate, the NAND gate is connected the output will be "Low" (0) only when all its inputs are "High". Such output is called as "active low output". A slightly more complex decoder would be the n-to-2n type binary decoders. These type of decoders are combinational circuits that convert binary information from 'n' coded inputs to a maximum of 2n unique outputs. We say a maximum of 2n outputs because in case the 'n' bit coded information has unused bit combinations, the decoder may have less than 2n outputs. We can have 2-to-4 decoder, 3-to-8 decoder or 4-to-16 decoder. We can form a 3-to-8 decoder from two 2-to-4 decoders (with enable signals). Similarly, we can also form a 4-to-16 decoder by combining two 3-to-8 decoders. In this type of circuit design, the enable inputs of both 3-to-8 decoders originate from a 4th input, which acts as a selector between the two 3-to-8 decoders. This allows the 4th input to enable either the top or bottom decoder, which produces outputs of D(0) through D(7) for the first decoder, and D(8) through D(15) for the second decoder. A decoder that contains enable inputs is also known as a decoder-demultiplexer. Thus, we have a 4-to-16 decoder produced by adding a 4th input shared among both decoders, producing 16 outputs.

Decoder

Row select

Most kinds of random-access memory use a n-to-2n decoder to convert the selected address on the address bus to one of the row address select lines.

Instruction decoder

In CPU design, the instruction decoder is the part of the CPU that converts the bits stored in the instruction register or, in CPUs that have microcode, the microinstruction into the control signals that control the other parts of the CPU. A simple CPU with 8 registers may use 3-to-8 logic decoders inside the instruction decoder to select two source registers of the register file to feed into the ALU as well as the destination register to accept the output of the ALU. A typical CPU instruction decoder also includes several other things.

Article Sources and Contributors

Article Sources and Contributors

Decoder Source: http://en.wikipedia.org/w/index.php?oldid=578399767 Contributors: 16@r, Adecold, Algocu, Alinja, Alphanis, Alynna Kasmira, BlueJester0101, BraneJ, Corvoe, Dancter, DmitTrix, DoostdarWKP, Drak1970, E-Kartoffel, Fahrettinkoc, Flammifer, Fuxx, Gaius Cornelius, GandalfDaGraay, Ghostwheel, Gracefool, Hazmat2, Hut 8.5, Iseesky, Istas, JQF, Jackol, Jim1138, Jordav, Juliancolton, JustUser, Jwigton, K.kesavan.87, Kenesis, Kenyon, KillerX, Lam Kin Keung, MK8, Mani1, Materialscientist, Med-, Momirt, OriginalJunglist, Pgk, Prashantgonarkar, QTCaptain, Radiojon, Roman12345, SaintNULL, SnowFire, Solareon, Squeezedlime, TVSRR, Tallinu, Tassedethe, TazzyTazzy, Tide rolls, Timotheus Canens, Tobias Bergemann, Vladimir Muravsky, Wahoofive, Wknight94, Yworo, , 95 anonymous edits

Image Sources, Licenses and Contributors

Image:DCC Decoder.jpg Source: http://en.wikipedia.org/w/index.php?title=File:DCC_Decoder.jpg License: Creative Commons Attribution-ShareAlike 3.0 Unported Contributors: Original uploader was TVSRR at en.wikipedia File:Decoder Example.svg Source: http://en.wikipedia.org/w/index.php?title=File:Decoder_Example.svg License: GNU Free Documentation License Contributors: Original uploader was BlueJester0101 at en.wikipedia

License

Creative Commons Attribution-Share Alike 3.0 //creativecommons.org/licenses/by-sa/3.0/

Vous aimerez peut-être aussi

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- DecoderDocument1 pageDecoderparassuPas encore d'évaluation

- Binary Decoder - DocxkenDocument11 pagesBinary Decoder - DocxkenLiezel JuarezPas encore d'évaluation

- Binary Decoder: Binary Decoders Are Another Type of Digital Logic Device That Has Inputs of 2-Bit, 3-Bit or 4-BitDocument7 pagesBinary Decoder: Binary Decoders Are Another Type of Digital Logic Device That Has Inputs of 2-Bit, 3-Bit or 4-BitJohn Brix BalisterosPas encore d'évaluation

- Binary DecoderDocument7 pagesBinary DecoderAlinChanPas encore d'évaluation

- Encoder and Decoder: A Project By:Priyanka Basak 3Rd Year, 6th Sem Roll:32Document13 pagesEncoder and Decoder: A Project By:Priyanka Basak 3Rd Year, 6th Sem Roll:32Indranil GangulyPas encore d'évaluation

- Decoder and EncoderDocument8 pagesDecoder and EncodersankulsybcaPas encore d'évaluation

- A 2-To-4 Binary DecodersDocument3 pagesA 2-To-4 Binary DecodersnagarajuPas encore d'évaluation

- Priority Encoder: 4-To-2 Bit Binary EncoderDocument6 pagesPriority Encoder: 4-To-2 Bit Binary EncoderAditya Prakash100% (1)

- Combinational CircuitsDocument5 pagesCombinational CircuitsRafena17Pas encore d'évaluation

- Combinational Circuits: 4 To 2 EncoderDocument5 pagesCombinational Circuits: 4 To 2 EncoderRafena MustaphaPas encore d'évaluation

- Assignment No:: Subject: Name: Rollno.Document25 pagesAssignment No:: Subject: Name: Rollno.Sharad Patil DholePas encore d'évaluation

- Control Unit - 89C52: Introduction About Micro ControllerDocument20 pagesControl Unit - 89C52: Introduction About Micro ControllerSubhashini AruchamyPas encore d'évaluation

- 14-Decoder Circuits-31-01-2023 PDFDocument15 pages14-Decoder Circuits-31-01-2023 PDFBack upPas encore d'évaluation

- Rfid Interface TO 8051: Deepak GuptaDocument4 pagesRfid Interface TO 8051: Deepak Guptamohitdaya14Pas encore d'évaluation

- Code Converters, Multiplexers, and DemultiplexersDocument34 pagesCode Converters, Multiplexers, and DemultiplexersjohnsamvlbPas encore d'évaluation

- My IndusDocument19 pagesMy IndusKusumakar Bodha100% (2)

- Dpco Book1Document4 pagesDpco Book1SELVAM SPas encore d'évaluation

- New Priority EncoderDocument5 pagesNew Priority EncoderHari PrasadPas encore d'évaluation

- DP - 26 DocumentationDocument64 pagesDP - 26 DocumentationViplav SangvaiPas encore d'évaluation

- Topic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Document93 pagesTopic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Aya AmirPas encore d'évaluation

- Questtext Choice1 Choice2 Choice3 Choice4 Subj: ComputerprinciplesDocument5 pagesQuesttext Choice1 Choice2 Choice3 Choice4 Subj: ComputerprinciplesTahajan M. HadjirulPas encore d'évaluation

- DE EXPERIMENT-8, Dhruv Tomar, 2K20, SE, 46Document6 pagesDE EXPERIMENT-8, Dhruv Tomar, 2K20, SE, 46Viking SanddPas encore d'évaluation

- Rəqəmsal SistemlərDocument30 pagesRəqəmsal SistemlərAsgeriPas encore d'évaluation

- Decoders: Dr. Mohammed Najm AbdullahDocument11 pagesDecoders: Dr. Mohammed Najm AbdullahxcPas encore d'évaluation

- The Digital Encoder: 4-To-2 Bit Binary EncoderDocument10 pagesThe Digital Encoder: 4-To-2 Bit Binary EncoderJohn Brix BalisterosPas encore d'évaluation

- Interfacing LectureDocument136 pagesInterfacing LectureTewodrosPas encore d'évaluation

- AttachmentDocument7 pagesAttachmentnandini swamiPas encore d'évaluation

- DecoderDocument6 pagesDecoderAparajitha Narayanan0% (1)

- Decoder and Encoder With ApplicationDocument38 pagesDecoder and Encoder With ApplicationParth KapadiaPas encore d'évaluation

- Chapter 1. OverviewDocument58 pagesChapter 1. OverviewmgitecetechPas encore d'évaluation

- L3: Multiplexer & Demultiplexer, Encoder & Decoder: Dr. Koushik BarmanDocument19 pagesL3: Multiplexer & Demultiplexer, Encoder & Decoder: Dr. Koushik BarmanShiv shankar SinghPas encore d'évaluation

- 3.unit III updatEDDocument66 pages3.unit III updatEDPrashant SarrafPas encore d'évaluation

- 3.3 Microcontroller:: Fig: 3.2: MicrocontrollersDocument20 pages3.3 Microcontroller:: Fig: 3.2: Microcontrollersnafisa sultanaPas encore d'évaluation

- ATMega8 UcDocument40 pagesATMega8 UcnrjchopraPas encore d'évaluation

- Avr Atmega 8 Uc: Lets Learn Fundamentals !!Document40 pagesAvr Atmega 8 Uc: Lets Learn Fundamentals !!malhiavtarsinghPas encore d'évaluation

- Answer To Review QuestionsDocument7 pagesAnswer To Review QuestionsRV PitogoPas encore d'évaluation

- Digital Visitor Counter Using 8051 MicrocontrollerDocument23 pagesDigital Visitor Counter Using 8051 MicrocontrollerChandra Bhanu83% (24)

- CA NotesDocument10 pagesCA NotesRuhitha Shanmugham VenkateswariPas encore d'évaluation

- MICROCONTROLLERDocument29 pagesMICROCONTROLLERhsbedi92Pas encore d'évaluation

- VHDL Lab RecordDocument13 pagesVHDL Lab RecordRajBhanPas encore d'évaluation

- IDT72V8988 - DataSheetDocument14 pagesIDT72V8988 - DataSheetDang KhuePas encore d'évaluation

- Unit II Special Purpose Programmable Peripherals and Their InterfacingDocument10 pagesUnit II Special Purpose Programmable Peripherals and Their InterfacingPraveen RathnamPas encore d'évaluation

- Practice4 (Adder & SustractorDocument7 pagesPractice4 (Adder & SustractorManolo-Hues Diaz SPas encore d'évaluation

- Lab ManualDocument7 pagesLab ManualraviPas encore d'évaluation

- Unit 5 NotesDocument25 pagesUnit 5 NoteskaustubhPas encore d'évaluation

- Comsats University Microprocessor Systems & Interfacing EEE-342Document8 pagesComsats University Microprocessor Systems & Interfacing EEE-342Bilal HabibPas encore d'évaluation

- XR16C854/854D: General DescriptionDocument55 pagesXR16C854/854D: General DescriptionAnonymous QakmLc3kTIPas encore d'évaluation

- Chapter 5Document12 pagesChapter 5Sonia MadueñoPas encore d'évaluation

- AVR TutorialDocument5 pagesAVR TutorialAkhil PtPas encore d'évaluation

- CH341 Asd 2Document12 pagesCH341 Asd 2ajoaomvPas encore d'évaluation

- Industrial Fault Indication System With Over Voltage Over TemperatureDocument46 pagesIndustrial Fault Indication System With Over Voltage Over Temperaturedivanshu16decPas encore d'évaluation

- Gates Half Adder Full Adder Combinational Circuits Decoder Encoder Multiplexer De-Multiplexer Stored Program Concept Flynn's ClassificationDocument17 pagesGates Half Adder Full Adder Combinational Circuits Decoder Encoder Multiplexer De-Multiplexer Stored Program Concept Flynn's ClassificationRitika SinghPas encore d'évaluation

- LGEC002 Door Lock System Using RFDocument8 pagesLGEC002 Door Lock System Using RFShivani MehrotraPas encore d'évaluation

- File 1406270302Document25 pagesFile 1406270302rupeshPas encore d'évaluation

- Micro Converter (Analog Device) 12-Bit Adcs and Dacs With Embedded High Speed 62-Kb Flash McuDocument20 pagesMicro Converter (Analog Device) 12-Bit Adcs and Dacs With Embedded High Speed 62-Kb Flash McushaileshPas encore d'évaluation

- Microprocessor ArchitectureDocument46 pagesMicroprocessor Architecture'Jaspreet SandhuPas encore d'évaluation

- ABACOM USB PIO UKDocument28 pagesABACOM USB PIO UKAkhmad AhmadPas encore d'évaluation

- 8085 PRJ Schematic 1Document44 pages8085 PRJ Schematic 1Jani ServiniPas encore d'évaluation

- Einstein Refrigerator PDFDocument4 pagesEinstein Refrigerator PDFtechzonesPas encore d'évaluation

- Leak Down TesterDocument3 pagesLeak Down TestertechzonesPas encore d'évaluation

- IIM December ExamDocument1 pageIIM December ExamtechzonesPas encore d'évaluation

- Syllabus R2013 PDFDocument105 pagesSyllabus R2013 PDFlogeshboy007Pas encore d'évaluation

- Syllabus R2013 PDFDocument105 pagesSyllabus R2013 PDFlogeshboy007Pas encore d'évaluation

- Engine Displacement PDFDocument3 pagesEngine Displacement PDFtechzones100% (1)

- United ArtistsDocument11 pagesUnited ArtiststechzonesPas encore d'évaluation

- Syllabus R2013 PDFDocument105 pagesSyllabus R2013 PDFlogeshboy007Pas encore d'évaluation

- IIM December ExamDocument1 pageIIM December ExamtechzonesPas encore d'évaluation

- Amiim ExamDocument2 pagesAmiim ExamtechzonesPas encore d'évaluation

- IIM December ExamDocument1 pageIIM December ExamtechzonesPas encore d'évaluation

- AMIIM Exam RulesDocument8 pagesAMIIM Exam RulestechzonesPas encore d'évaluation

- Syllabus R2013 PDFDocument105 pagesSyllabus R2013 PDFlogeshboy007Pas encore d'évaluation

- Android FilmDocument5 pagesAndroid FilmtechzonesPas encore d'évaluation

- Phosphine PDFDocument7 pagesPhosphine PDFtechzonesPas encore d'évaluation

- Indian Institute of Metals - Exam DetailsDocument3 pagesIndian Institute of Metals - Exam Detailstechzones50% (2)

- SundaattamDocument3 pagesSundaattamtechzonesPas encore d'évaluation

- High Temperature CorrosionDocument3 pagesHigh Temperature CorrosiontechzonesPas encore d'évaluation

- Differential Calculus-I: Note: 1. If K ( 0) Is The Curvature of A Curve at P, Then The RadiusDocument28 pagesDifferential Calculus-I: Note: 1. If K ( 0) Is The Curvature of A Curve at P, Then The RadiustechzonesPas encore d'évaluation

- Zingiberaceae: Ginger FamilyDocument5 pagesZingiberaceae: Ginger Familytechzones50% (2)

- Acacia Pycnantha: Golden WattleDocument7 pagesAcacia Pycnantha: Golden WattletechzonesPas encore d'évaluation

- Phosphine PDFDocument7 pagesPhosphine PDFtechzonesPas encore d'évaluation

- KagapujandarDocument4 pagesKagapujandartechzones100% (1)

- Phosphorus CycleDocument5 pagesPhosphorus CycletechzonesPas encore d'évaluation

- Computer SimulationDocument10 pagesComputer SimulationtechzonesPas encore d'évaluation

- Geothermal EnergyDocument11 pagesGeothermal EnergytechzonesPas encore d'évaluation

- Surface RunoffDocument8 pagesSurface RunofftechzonesPas encore d'évaluation

- FIFA World CupDocument18 pagesFIFA World CuptechzonesPas encore d'évaluation

- Atmospheric SciencesDocument5 pagesAtmospheric SciencestechzonesPas encore d'évaluation

- Geothermal EnergyDocument11 pagesGeothermal EnergytechzonesPas encore d'évaluation

- Computer Organization and Architecture LabExperimentsDocument31 pagesComputer Organization and Architecture LabExperimentsfun time [funny videos]Pas encore d'évaluation

- Viva QuestionsDocument19 pagesViva QuestionskslnPas encore d'évaluation

- Syllabus - Electrical Sem 4Document81 pagesSyllabus - Electrical Sem 4vcb.polykondagaonPas encore d'évaluation

- Combinational CircuitsDocument11 pagesCombinational CircuitsBruce LambPas encore d'évaluation

- BCD To 7 Segment DecoderDocument5 pagesBCD To 7 Segment DecoderAlberto CorralesPas encore d'évaluation

- Code Converters MuxDocument15 pagesCode Converters MuxMaitrik ShahPas encore d'évaluation

- 7-Segment Display: Parts and MaterialsDocument2 pages7-Segment Display: Parts and Materialsapi-19772149Pas encore d'évaluation

- Unit 3Document36 pagesUnit 3PrasannaKumar KaraNamPas encore d'évaluation

- Building Digital Logic Circuits Using Decoders: Objectives Lab TasksDocument3 pagesBuilding Digital Logic Circuits Using Decoders: Objectives Lab TasksARISHA 124Pas encore d'évaluation

- Ex 2Document26 pagesEx 2Ako C SeanPas encore d'évaluation

- Questions & Answers On Combinational CircuitsDocument36 pagesQuestions & Answers On Combinational Circuitskibrom atsbha75% (4)

- Active High and Active Low DecodersDocument14 pagesActive High and Active Low DecodersVigneswaran Vignesh0% (1)

- Lab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignDocument7 pagesLab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignAli HassanPas encore d'évaluation

- 7-Segment Display With DecoderDocument4 pages7-Segment Display With DecoderJames Kevin Ignacio100% (1)

- Building Blocks For Digital Design: Adders, Registers, and MultiplexersDocument109 pagesBuilding Blocks For Digital Design: Adders, Registers, and Multiplexersgkk001Pas encore d'évaluation

- Encoder & DecoderDocument36 pagesEncoder & Decoderetasuresh0% (2)

- Decoder and Encoder With ApplicationDocument38 pagesDecoder and Encoder With ApplicationParth KapadiaPas encore d'évaluation

- Ic 7445Document4 pagesIc 7445Srija NairPas encore d'évaluation

- Cadence Nclaunch LabDocument86 pagesCadence Nclaunch Labsweety987Pas encore d'évaluation

- BCD To 7 Segment LED Display Decoder CircuitDocument6 pagesBCD To 7 Segment LED Display Decoder CircuitMarx Lennin CabalticanPas encore d'évaluation

- Logisim TutorialDocument34 pagesLogisim TutorialJaniessy ZozobradoPas encore d'évaluation

- STLD Lab ExperimentsDocument30 pagesSTLD Lab Experimentslokesh krapaPas encore d'évaluation

- 4017 & 4026Document3 pages4017 & 4026Ronny SinagaPas encore d'évaluation

- CEJ - ECE 3rd - Unit No.1 - Decoder & Encoder - DSDDocument32 pagesCEJ - ECE 3rd - Unit No.1 - Decoder & Encoder - DSDsonu sreekumarPas encore d'évaluation

- Ecgr2156 Experiment 3 Seven Segment DecoderDocument6 pagesEcgr2156 Experiment 3 Seven Segment Decoderm shahPas encore d'évaluation

- CH 08Document82 pagesCH 08Luis Eduardo García QuesadaPas encore d'évaluation

- Laboratory Exercise 1: Switches, Lights, and MultiplexersDocument8 pagesLaboratory Exercise 1: Switches, Lights, and MultiplexerswaleeedPas encore d'évaluation

- Lab 8Document8 pagesLab 8Anonymous yG7oj20% (1)

- Linear and Digital Appilications LabDocument66 pagesLinear and Digital Appilications LabThomaselvaPas encore d'évaluation

- Chip War: The Quest to Dominate the World's Most Critical TechnologyD'EverandChip War: The Quest to Dominate the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (227)

- The Internet Con: How to Seize the Means of ComputationD'EverandThe Internet Con: How to Seize the Means of ComputationÉvaluation : 5 sur 5 étoiles5/5 (6)

- The Dark Net: Inside the Digital UnderworldD'EverandThe Dark Net: Inside the Digital UnderworldÉvaluation : 3.5 sur 5 étoiles3.5/5 (104)

- The Digital Marketing Handbook: A Step-By-Step Guide to Creating Websites That SellD'EverandThe Digital Marketing Handbook: A Step-By-Step Guide to Creating Websites That SellÉvaluation : 5 sur 5 étoiles5/5 (6)

- How to Do Nothing: Resisting the Attention EconomyD'EverandHow to Do Nothing: Resisting the Attention EconomyÉvaluation : 4 sur 5 étoiles4/5 (421)

- Defensive Cyber Mastery: Expert Strategies for Unbeatable Personal and Business SecurityD'EverandDefensive Cyber Mastery: Expert Strategies for Unbeatable Personal and Business SecurityÉvaluation : 5 sur 5 étoiles5/5 (1)

- Grokking Algorithms: An illustrated guide for programmers and other curious peopleD'EverandGrokking Algorithms: An illustrated guide for programmers and other curious peopleÉvaluation : 4 sur 5 étoiles4/5 (16)

- So You Want to Start a Podcast: Finding Your Voice, Telling Your Story, and Building a Community That Will ListenD'EverandSo You Want to Start a Podcast: Finding Your Voice, Telling Your Story, and Building a Community That Will ListenÉvaluation : 3.5 sur 5 étoiles3.5/5 (24)

- Web Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyD'EverandWeb Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyÉvaluation : 4 sur 5 étoiles4/5 (13)

- The Wires of War: Technology and the Global Struggle for PowerD'EverandThe Wires of War: Technology and the Global Struggle for PowerÉvaluation : 4 sur 5 étoiles4/5 (34)

- Python for Beginners: The 1 Day Crash Course For Python Programming In The Real WorldD'EverandPython for Beginners: The 1 Day Crash Course For Python Programming In The Real WorldPas encore d'évaluation

- More Porn - Faster!: 50 Tips & Tools for Faster and More Efficient Porn BrowsingD'EverandMore Porn - Faster!: 50 Tips & Tools for Faster and More Efficient Porn BrowsingÉvaluation : 3.5 sur 5 étoiles3.5/5 (23)

- How to Start a Blog with WordPress: Beginner's Guide to Make Money by Writing OnlineD'EverandHow to Start a Blog with WordPress: Beginner's Guide to Make Money by Writing OnlineÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Practical Industrial Cybersecurity: ICS, Industry 4.0, and IIoTD'EverandPractical Industrial Cybersecurity: ICS, Industry 4.0, and IIoTPas encore d'évaluation

- Ten Arguments for Deleting Your Social Media Accounts Right NowD'EverandTen Arguments for Deleting Your Social Media Accounts Right NowÉvaluation : 4 sur 5 étoiles4/5 (388)

- Nine Algorithms That Changed the Future: The Ingenious Ideas That Drive Today's ComputersD'EverandNine Algorithms That Changed the Future: The Ingenious Ideas That Drive Today's ComputersÉvaluation : 5 sur 5 étoiles5/5 (7)

- An Internet in Your Head: A New Paradigm for How the Brain WorksD'EverandAn Internet in Your Head: A New Paradigm for How the Brain WorksPas encore d'évaluation

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsD'EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsÉvaluation : 5 sur 5 étoiles5/5 (1)

- React.js Design Patterns: Learn how to build scalable React apps with ease (English Edition)D'EverandReact.js Design Patterns: Learn how to build scalable React apps with ease (English Edition)Pas encore d'évaluation