Académique Documents

Professionnel Documents

Culture Documents

Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7M

Transféré par

Kevin TateTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7M

Transféré par

Kevin TateDroits d'auteur :

Formats disponibles

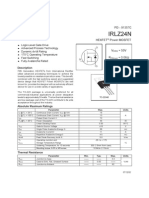

FDD8896 / FDU8896

April 2008

FDD8896 / FDU8896

N-Channel PowerTrench MOSFET 30V, 94A, 5.7m

General Description

This N-Channel MOSFET has been designed specifically to improve the overall efficiency of DC/DC converters using either synchronous or conventional switching PWM controllers. It has been optimized for low gate charge, low rDS(ON) and fast switching speed.

tm

Features

rDS(ON) = 5.7m , VGS = 10V, ID = 35A , VGS = 4.5V, ID = 35A rDS(ON) = 6.8m High performance trench technology for extremely low rDS(ON) Low gate charge

Applications

DC/DC converters

High power and current handling capability

D G S

I-PAK (TO-251AA) G D S

G

D-PAK TO-252 (TO-252)

MOSFET Maximum Ratings TC = 25C unless otherwise noted

Symbol VDSS VGS Parameter Drain to Source Voltage Gate to Source Voltage Drain Current Continuous (TC = 25oC, VGS = 10V) (Note 1) ID Continuous (TC = 25oC, VGS = 4.5V) (Note 1) Continuous (Tamb = 25oC, VGS = 10V, with R JA = 52oC/W) Pulsed EAS PD TJ, TSTG Single Pulse Avalanche Energy (Note 2) Power dissipation Derate above 25oC Operating and Storage Temperature 94 85 17 Figure 4 168 80 0.53 -55 to 175 A A A A mJ W W/oC

oC

Ratings 30 20

Units V V

Thermal Characteristics

RJC RJA RJA Thermal Resistance Junction to Case TO-252, TO-251 Thermal Resistance Junction to Ambient TO-252, TO-251 Thermal Resistance Junction to Ambient TO-252, 1in2 copper pad area 1.88 100 52

o o

C/W C/W

oC/W

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

Package Marking and Ordering Information

Device Marking FDD8896 FDU8896 F Device FDD8896 FDU8896 Package TO-252AA TO-251AA Reel Size 13 Tube Tape Width 12mm N/A Quantity 2500 units 75 units

Electrical Characteristics TC = 25C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BVDSS IDSS IGSS Drain to Source Breakdown Voltage Zero Gate Voltage Drain Current Gate to Source Leakage Current ID = 250A, VGS = 0V VDS = 24V VGS = 0V VGS = 20V TC = 150oC 30 1 250 100 V A nA

On Characteristics

VGS(TH) Gate to Source Threshold Voltage VGS = VDS, ID = 250A ID = 35A, VGS = 10V rDS(ON) Drain to Source On Resistance ID = 35A, VGS = 4.5V ID = 35A, VGS = 10V, TJ = 175oC 1.2 2.5 V 0.0047 0.0057 0.0057 0.0068 0.0075 0.0092

Dynamic Characteristics

CISS COSS CRSS RG Qg(TOT) Qg(5) Qg(TH) Qgs Qgs2 Qgd Input Capacitance Output Capacitance Reverse Transfer Capacitance Gate Resistance Total Gate Charge at 10V Total Gate Charge at 5V Threshold Gate Charge Gate to Source Gate Charge Gate Charge Threshold to Plateau Gate to Drain Miller Charge (VGS = 10V) VDD = 15V, ID = 35A VGS = 10V, RGS = 6.2 9 106 53 41 171 143 ns ns ns ns ns ns VDS = 15V, VGS = 0V, f = 1MHz VGS = 0.5V, f = 1MHz VGS = 0V to 10V VGS = 0V to 5V VGS = 0V to 1V VDD = 15V ID = 35A Ig = 1.0mA 2525 490 300 2.1 46 24 2.3 6.9 4.6 9.8 60 32 3.0 pF pF pF nC nC nC nC nC nC

Switching Characteristics

tON td(ON) tr td(OFF) tf tOFF Turn-On Time Turn-On Delay Time Rise Time Turn-Off Delay Time Fall Time Turn-Off Time

Drain-Source Diode Characteristics

VSD trr QRR Source to Drain Diode Voltage Reverse Recovery Time Reverse Recovered Charge ISD = 35A ISD = 15A ISD = 35A, dISD/dt = 100A/s ISD = 35A, dISD/dt = 100A/s 1.25 1.0 27 12 V V ns nC

Notes: 1: Package current limitation is 35A. 2: Starting TJ = 25C, L = 0.43mH, IAS = 28A, VDD = 27V, VGS = 10V.

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

Typical Characteristics TC = 25C unless otherwise noted

1.2 100 CURRENT LIMITED BY PACKAGE ID, DRAIN CURRENT (A) 0 25 50 75 100 125 150 175 75

POWER DISSIPATION MULTIPLIER

1.0

0.8

0.6

50

0.4

25

0.2

0 TC , CASE TEMPERATURE (oC)

0 25 50 75 100 125 150 175 TC, CASE TEMPERATURE (oC)

Figure 1. Normalized Power Dissipation vs Case Temperature

2 1 DUTY CYCLE - DESCENDING ORDER 0.5 0.2 0.1 0.05 0.02 0.01

Figure 2. Maximum Continuous Drain Current vs Case Temperature

ZJC, NORMALIZED THERMAL IMPEDANCE

PDM 0.1 t1 t2 NOTES: DUTY FACTOR: D = t1/t2 PEAK TJ = PDM x ZJC x RJC + TC 10-3 10-2 t, RECTANGULAR PULSE DURATION (s) 10-1 100 101

SINGLE PULSE 0.01 10-5 10-4

Figure 3. Normalized Maximum Transient Thermal Impedance

1000 TRANSCONDUCTANCE MAY LIMIT CURRENT IN THIS REGION VGS = 4.5V I = I25 175 - TC 150

TC = 25oC FOR TEMPERATURES ABOVE 25oC DERATE PEAK CURRENT AS FOLLOWS:

IDM, PEAK CURRENT (A)

100

30 10-5 10-4 10-3 10-2 t, PULSE WIDTH (s) 10-1 100 101

Figure 4. Peak Current Capability

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

Typical Characteristics TC = 25C unless otherwise noted

1000 10s ID, DRAIN CURRENT (A) 100 100s 10 OPERATION IN THIS AREA MAY BE LIMITED BY rDS(ON) 500 If R = 0 tAV = (L)(IAS)/(1.3*RATED BVDSS - VDD) If R 0 tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS - VDD) +1]

IAS, AVALANCHE CURRENT (A)

100

STARTING TJ = 25oC 10

1ms 10ms DC

1 SINGLE PULSE TJ = MAX RATED TC = 25oC 0.1 1 10 VDS, DRAIN TO SOURCE VOLTAGE (V)

STARTING TJ = 150oC 60 1 0.01

0.1 1 10 tAV, TIME IN AVALANCHE (ms)

100

Figure 5. Forward Bias Safe Operating Area

NOTE: Refer to Fairchild Application Notes AN7514 and AN7515

Figure 6. Unclamped Inductive Switching Capability

100 PULSE DURATION = 80s DUTY CYCLE = 0.5% MAX 80 ID, DRAIN CURRENT (A) TC = 25oC VGS = 5V 60 VGS = 10V 40 VGS = 3V VGS = 4V

100

80 ID , DRAIN CURRENT (A)

PULSE DURATION = 80s DUTY CYCLE = 0.5% MAX VDD = 15V

60 TJ = 25oC 40

20 TJ = 175oC 0 1.5 2.0 2.5 3.0 VGS , GATE TO SOURCE VOLTAGE (V) 3.5 TJ = -55oC

20 VGS = 2.5V 0 0 0.2 0.4 0.6 0.8 VDS , DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Transfer Characteristics

14 NORMALIZED DRAIN TO SOURCE ON RESISTANCE ID = 35A rDS(ON), DRAIN TO SOURCE ON RESISTANCE (m) 12 PULSE DURATION = 80s DUTY CYCLE = 0.5% MAX

Figure 8. Saturation Characteristics

1.6

PULSE DURATION = 80s DUTY CYCLE = 0.5% MAX

1.4

10

1.2

1.0

ID = 1A

0.8 VGS = 10V, ID = 35A

4 2 4 6 8 10 VGS, GATE TO SOURCE VOLTAGE (V)

0.6 -80

-40

0 40 80 120 TJ, JUNCTION TEMPERATURE (oC)

160

200

Figure 9. Drain to Source On Resistance vs Gate Voltage and Drain Current

Figure 10. Normalized Drain to Source On Resistance vs Junction Temperature

2004 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C1

FDD8896 / FDU8896

Typical Characteristics TC = 25C unless otherwise noted

1.2 VGS = VDS, ID = 250A NORMALIZED DRAIN TO SOURCE BREAKDOWN VOLTAGE 1.2 ID = 250A

NORMALIZED GATE THRESHOLD VOLTAGE

1.0

1.1

0.8

1.0

0.6

0.4 -80

-40

40

80

120

160

200

0.9 -80

-40

40

80

120

160

200

TJ, JUNCTION TEMPERATURE (oC)

TJ , JUNCTION TEMPERATURE (oC)

Figure 11. Normalized Gate Threshold Voltage vs Junction Temperature

5000 CISS = CGS + CGD

Figure 12. Normalized Drain to Source Breakdown Voltage vs Junction Temperature

10 VGS , GATE TO SOURCE VOLTAGE (V) VDD = 15V 8

C, CAPACITANCE (pF)

1000 CRSS = CGD

COSS CDS + CGD

4 WAVEFORMS IN DESCENDING ORDER: ID = 35A ID = 5A 0 10 20 30 Qg, GATE CHARGE (nC) 40 50

VGS = 0V, f = 1MHz 100 0.1 0 1 10 VDS , DRAIN TO SOURCE VOLTAGE (V) 30

Figure 13. Capacitance vs Drain to Source Voltage

Figure 14. Gate Charge Waveforms for Constant Gate Current

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

Test Circuits and Waveforms

VDS BVDSS L VARY tP TO OBTAIN REQUIRED PEAK IAS VGS DUT tP 0V RG IAS VDD VDD tP VDS

+

IAS 0.01 0 tAV

Figure 15. Unclamped Energy Test Circuit

Figure 16. Unclamped Energy Waveforms

VDS VDD L VGS VDS Qg(5) VDD DUT Ig(REF) VGS = 1V 0 Qg(TH) Qgs Ig(REF) 0 Qgd Qgs2 VGS = 5V Qg(TOT) VGS VGS = 10V

+

Figure 17. Gate Charge Test Circuit

Figure 18. Gate Charge Waveforms

VDS

tON td(ON) RL VDS 90% tr

tOFF td(OFF) tf 90%

VGS

VDD DUT 0

10%

10%

RGS VGS VGS 0 10% 50% PULSE WIDTH

90% 50%

Figure 19. Switching Time Test Circuit

Figure 20. Switching Time Waveforms

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

Thermal Resistance vs. Mounting Pad Area

The maximum rated junction temperature, TJM, and the thermal resistance of the heat dissipating path determines the maximum allowable device power dissipation, PDM, in an application. Therefore the applications ambient temperature, TA (oC), and thermal resistance RJA (oC/W) must be reviewed to ensure that TJM is never exceeded. Equation 1 mathematically represents the relationship and serves as the basis for establishing the rating of the part.

( T JM TA ) P DM = ----------------------------R JA

125 RJA = 33.32+ 23.84/(0.268+Area) EQ.2 100 RJA (oC/W) RJA = 33.32+ 154/(1.73+Area) EQ.3

75

(EQ. 1)

50

In using surface mount devices such as the TO-252 package, the environment in which it is applied will have a significant influence on the parts current and maximum power dissipation ratings. Precise determination of PDM is complex and influenced by many factors: 1. Mounting pad area onto which the device is attached and whether there is copper on one side or both sides of the board. 2. The number of copper layers and the thickness of the board. 3. The use of external heat sinks. 4. The use of thermal vias. 5. Air flow and board orientation. 6. For non steady state applications, the pulse width, the duty cycle and the transient thermal response of the part, the board and the environment they are in. Fairchild provides thermal information to assist the designers preliminary application evaluation. Figure 21 defines the RJA for the device as a function of the top copper (component side) area. This is for a horizontally positioned FR-4 board with 1oz copper after 1000 seconds of steady state power with no air flow. This graph provides the necessary information for calculation of the steady state junction temperature or power dissipation. Pulse applications can be evaluated using the Fairchild device Spice thermal model or manually utilizing the normalized maximum transient thermal impedance curve. Thermal resistances corresponding to other copper areas can be obtained from Figure 21 or by calculation using Equation 2 or 3. Equation 2 is used for copper area defined in inches square and equation 3 is for area in centimeters square. The area, in square inches or square centimeters is the top copper area including the gate and source pads.

25 0.01 (0.0645)

0.1 (0.645)

1 (6.45)

10 (64.5)

AREA, TOP COPPER AREA in2 (cm2)

Figure 21. Thermal Resistance vs Mounting Pad Area

R JA = 33.32 + -----------------------------------154 ( 1.73 + Area )

23.84 ( 0.268 + Area )

(EQ. 2)

Area in Inches Squared

R JA = 33.32 + ---------------------------------

(EQ. 3)

Area in Centimeters Squared

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

PSPICE Electrical Model

.SUBCKT FDD8896 2 1 3 ; rev July 2003 Ca 12 8 2.3e-9 Cb 15 14 2.3e-9 Cin 6 8 2.3e-9 Dbody 7 5 DbodyMOD Dbreak 5 11 DbreakMOD Dplcap 10 5 DplcapMOD Ebreak 11 7 17 18 32.6 Eds 14 8 5 8 1 Egs 13 8 6 8 1 Esg 6 10 6 8 1 Evthres 6 21 19 8 1 Evtemp 20 6 18 22 1 It 8 17 1 Lgate 1 9 4.6e-9 Ldrain 2 5 1.0e-9 Lsource 3 7 1.7e-9

S1A S2A 13 8 S1B CA 13 + EGS 6 8 EDS 14 13 S2B CB + 5 8 8 RVTHRES 14 IT VBAT + 22 15 17 ESG + LGATE GATE 1 RLGATE CIN EVTEMP RGATE + 18 22 9 20 6 MSTRO LSOURCE 8 RSOURCE RLSOURCE 12 RBREAK 18 RVTEMP 19 7 SOURCE 3 6 8 EVTHRES + 19 8 LDRAIN DPLCAP 10 RSLC1 51 ESLC 50 RDRAIN 21 16 RLDRAIN DBREAK 11 + 17 EBREAK 18 MWEAK MMED 5 DRAIN 2

RSLC2

5 51 -

RLgate 1 9 46 RLdrain 2 5 10 RLsource 3 7 17 Mmed 16 6 8 8 MmedMOD Mstro 16 6 8 8 MstroMOD Mweak 16 21 8 8 MweakMOD Rbreak 17 18 RbreakMOD 1 Rdrain 50 16 RdrainMOD 2.2e-3 Rgate 9 20 2.1 RSLC1 5 51 RSLCMOD 1e-6 RSLC2 5 50 1e3 Rsource 8 7 RsourceMOD 2e-3 Rvthres 22 8 RvthresMOD 1 Rvtemp 18 19 RvtempMOD 1 S1a 6 12 13 8 S1AMOD S1b 13 12 13 8 S1BMOD S2a 6 15 14 13 S2AMOD S2b 13 15 14 13 S2BMOD

Vbat 22 19 DC 1 ESLC 51 50 VALUE={(V(5,51)/ABS(V(5,51)))*(PWR(V(5,51)/(1e-6*500),10))} .MODEL DbodyMOD D (IS=5E-12 IKF=10 N=1.01 RS=2.6e-3 TRS1=8e-4 TRS2=2e-7 + CJO=8.8e-10 M=0.57 TT=1e-16 XTI=0.9) .MODEL DbreakMOD D (RS=8e-2 TRS1=1e-3 TRS2=-8.9e-6) .MODEL DplcapMOD D (CJO=9.4e-10 IS=1e-30 N=10 M=0.4) .MODEL MmedMOD NMOS (VTO=1.85 KP=10 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=2.1 T_ABS=25) .MODEL MstroMOD NMOS (VTO=2.34 KP=350 IS=1e-30 N=10 TOX=1 L=1u W=1u T_ABS=25) .MODEL MweakMOD NMOS (VTO=1.55 KP=0.05 IS=1e-30 N=10 TOX=1 L=1u W=1u RG=21 RS=0.1 T_ABS=25) .MODEL RbreakMOD RES (TC1=8.3e-4 TC2=-4e-7) .MODEL RdrainMOD RES (TC1=1e-4 TC2=8e-6) .MODEL RSLCMOD RES (TC1=9e-4 TC2=1e-6) .MODEL RsourceMOD RES (TC1=7.5e-3 TC2=1e-6) .MODEL RvthresMOD RES (TC1=-1.7e-3 TC2=-8.8e-6) .MODEL RvtempMOD RES (TC1=-2.6e-3 TC2=2e-7) .MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-4 VOFF=-3) .MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-3 VOFF=-4) .MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-2 VOFF=-0.5) .MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1 VON=-0.5 VOFF=-2) .ENDS Note: For further discussion of the PSPICE model, consult A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global Temperature Options; IEEE Power Electronics Specialist Conference Records, 1991, written by William J. Hepp and C. Frank Wheatley.

2008 Fairchild Semiconductor Corporation

DBODY

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

SABER Electrical Model

rev July 2003 template FDD8896 n2,n1,n3 =m_temp electrical n2,n1,n3 number m_temp=25 { var i iscl dp..model dbodymod = (isl=5e-12,ikf=10,nl=1.01,rs=2.6e-3,trs1=8e-4,trs2=2e-7,cjo=8.8e-10,m=0.57,tt=1e-16,xti=0.9) dp..model dbreakmod = (rs=8e-2,trs1=1e-3,trs2=-8.9e-6) dp..model dplcapmod = (cjo=9.4e-10,isl=10e-30,nl=10,m=0.4) m..model mmedmod = (type=_n,vto=1.85,kp=10,is=1e-30, tox=1) m..model mstrongmod = (type=_n,vto=2.34,kp=350,is=1e-30, tox=1) m..model mweakmod = (type=_n,vto=1.55,kp=0.05,is=1e-30, tox=1,rs=0.1) LDRAIN sw_vcsp..model s1amod = (ron=1e-5,roff=0.1,von=-4,voff=-3) DPLCAP 5 sw_vcsp..model s1bmod = (ron=1e-5,roff=0.1,von=-3,voff=-4) 10 sw_vcsp..model s2amod = (ron=1e-5,roff=0.1,von=-2,voff=-0.5) RLDRAIN RSLC1 sw_vcsp..model s2bmod = (ron=1e-5,roff=0.1,von=-0.5,voff=-2) 51 c.ca n12 n8 = 2.3e-9 RSLC2 c.cb n15 n14 = 2.3e-9 ISCL c.cin n6 n8 = 2.3e-9 dp.dbody n7 n5 = model=dbodymod dp.dbreak n5 n11 = model=dbreakmod dp.dplcap n10 n5 = model=dplcapmod spe.ebreak n11 n7 n17 n18 = 32.6 GATE spe.eds n14 n8 n5 n8 = 1 1 spe.egs n13 n8 n6 n8 = 1 spe.esg n6 n10 n6 n8 = 1 spe.evthres n6 n21 n19 n8 = 1 spe.evtemp n20 n6 n18 n22 = 1 i.it n8 n17 = 1 l.lgate n1 n9 = 4.6e-9 l.ldrain n2 n5 = 1.0e-9 l.lsource n3 n7 = 1.7e-9

CA 12 S1B 13 + EGS 6 8 EDS LGATE ESG + EVTEMP RGATE + 18 22 9 20 6 MSTRO CIN 8 6 8 EVTHRES + 19 8 50 RDRAIN 21 16 MWEAK MMED EBREAK + 17 18 DBREAK 11 DBODY

DRAIN 2

RLGATE

LSOURCE 7 RLSOURCE

SOURCE 3

RSOURCE S1A 13 8 S2A 14 13 S2B CB + 5 8 8 RVTHRES 14 IT VBAT + 22 15 17 RBREAK 18 RVTEMP 19

res.rlgate n1 n9 = 46 res.rldrain n2 n5 = 10 res.rlsource n3 n7 = 17

m.mmed n16 n6 n8 n8 = model=mmedmod, l=1u, w=1u, temp=m_temp m.mstrong n16 n6 n8 n8 = model=mstrongmod, l=1u, w=1u, temp=m_temp m.mweak n16 n21 n8 n8 = model=mweakmod, l=1u, w=1u, temp=m_temp res.rbreak n17 n18 = 1, tc1=8.3e-4,tc2=-4e-7 res.rdrain n50 n16 = 2.2e-3, tc1=1e-4,tc2=8e-6 res.rgate n9 n20 = 2.1 res.rslc1 n5 n51 = 1e-6, tc1=9e-4,tc2=1e-6 res.rslc2 n5 n50 = 1e3 res.rsource n8 n7 = 2e-3, tc1=7.5e-3,tc2=1e-6 res.rvthres n22 n8 = 1, tc1=-1.7e-3,tc2=-8.8e-6 res.rvtemp n18 n19 = 1, tc1=-2.6e-3,tc2=2e-7 sw_vcsp.s1a n6 n12 n13 n8 = model=s1amod sw_vcsp.s1b n13 n12 n13 n8 = model=s1bmod sw_vcsp.s2a n6 n15 n14 n13 = model=s2amod sw_vcsp.s2b n13 n15 n14 n13 = model=s2bmod v.vbat n22 n19 = dc=1 equations { i (n51->n50) +=iscl iscl: v(n51,n50) = ((v(n5,n51)/(1e-9+abs(v(n5,n51))))*((abs(v(n5,n51)*1e6/500))** 10)) } }

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

PSPICE Thermal Model

REV 23 July 2003 FDD8896T CTHERM1 TH 6 9e-4 CTHERM2 6 5 1e-3 CTHERM3 5 4 2e-3 CTHERM4 4 3 3e-3 CTHERM5 3 2 7e-3 CTHERM6 2 TL 8e-2 RTHERM1 TH 6 3.0e-2 RTHERM2 6 5 1.0e-1 RTHERM3 5 4 1.8e-1 RTHERM4 4 3 2.8e-1 RTHERM5 3 2 4.5e-1 RTHERM6 2 TL 4.6e-1

th

JUNCTION

RTHERM1

CTHERM1

RTHERM2

CTHERM2

SABER Thermal Model

SABER thermal model FDD8896T template thermal_model th tl thermal_c th, tl { ctherm.ctherm1 th 6 =9e-4 ctherm.ctherm2 6 5 =1e-3 ctherm.ctherm3 5 4 =2e-3 ctherm.ctherm4 4 3 =3e-3 ctherm.ctherm5 3 2 =7e-3 ctherm.ctherm6 2 tl =8e-2 rtherm.rtherm1 th 6 =3.0e-2 rtherm.rtherm2 6 5 =1.0e-1 rtherm.rtherm3 5 4 =1.8e-1 rtherm.rtherm4 4 3 =2.8e-1 rtherm.rtherm5 3 2 =4.5e-1 rtherm.rtherm6 2 tl =4.6e-1 }

RTHERM3 CTHERM3

RTHERM4

CTHERM4

RTHERM5

CTHERM5

RTHERM6

CTHERM6

tl

CASE

2008 Fairchild Semiconductor Corporation

FDD8896 / FDU8896 Rev. C2

FDD8896 / FDU8896

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidianries, and is not intended to be an exhaustive list of all such trademarks. ACEx Build it Now CorePLUS CorePOWER CROSSVOLT CTL Current Transfer Logic EcoSPARK EfficentMax EZSWITCH *

Fairchild Fairchild Semiconductor FACT Quiet Series FACT FAST FastvCore FlashWriter *

FPS F-PFS FRFET Global Power ResourceSM Green FPS Green FPS e-Series GTO IntelliMAX ISOPLANAR MegaBuck MICROCOUPLER MicroFET MicroPak MillerDrive MotionMax Motion-SPM OPTOLOGIC OPTOPLANAR

tm

PDP-SPM Power-SPM PowerTrench Programmable Active Droop QFET QS Quiet Series RapidConfigure Saving our world 1mW at a time SmartMax SMART START SPM STEALTH SuperFET SuperSOT-3 SuperSOT-6 SuperSOT-8 SuperMOS

The Power Franchise

tm

TinyBoost TinyBuck TinyLogic TINYOPTO TinyPower TinyPWM TinyWire SerDes UHC Ultra FRFET UniFET VCX VisualMax

* EZSWITCH and FlashWriter are trademarks of System General Corporation, used under license by Fairchild Semiconductor. DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILDS WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Advance Information Product Status Formative or In Design Definition This datasheet contains the design specifications for product development. Specifications may change in any manner without notice. This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design. This datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.

Rev. I34

2008 Fairchild Semiconductor Corporation FDD8896 / FDU8896 Rev. C2

Preliminary

First Production

No Identification Needed Obsolete

Full Production Not In Production

Vous aimerez peut-être aussi

- 110 Waveform Generator Projects for the Home ConstructorD'Everand110 Waveform Generator Projects for the Home ConstructorÉvaluation : 4 sur 5 étoiles4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsD'EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Ceramic InstallationDocument49 pagesCeramic InstallationKevin Tate100% (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Emerging Trends in VLSI Design: A Big Question..???Document102 pagesEmerging Trends in VLSI Design: A Big Question..???Madan R HonnalagerePas encore d'évaluation

- DeltaDocument97 pagesDeltaKevin TatePas encore d'évaluation

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Document11 pagesN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TatePas encore d'évaluation

- N 308 ApDocument11 pagesN 308 Apdragon-red0816Pas encore d'évaluation

- FDP 8896Document11 pagesFDP 8896condejhonnyPas encore d'évaluation

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDocument9 pagesFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloPas encore d'évaluation

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETDocument10 pagesFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezPas encore d'évaluation

- IRF8788Document9 pagesIRF8788Robert KovacsPas encore d'évaluation

- FD3055Document8 pagesFD3055maldomattPas encore d'évaluation

- Fdb045An08A0: N-Channel Powertrench MosfetDocument12 pagesFdb045An08A0: N-Channel Powertrench MosfetRocio HernandezPas encore d'évaluation

- IRF650B / IRFS650B: 200V N-Channel MOSFETDocument10 pagesIRF650B / IRFS650B: 200V N-Channel MOSFETbinoelPas encore d'évaluation

- IRF650B / IRFS650B: 200V N-Channel MOSFETDocument11 pagesIRF650B / IRFS650B: 200V N-Channel MOSFETMiloud ChouguiPas encore d'évaluation

- Irfp 260 NDocument9 pagesIrfp 260 NJolaine MojicaPas encore d'évaluation

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETDocument9 pagesFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57Pas encore d'évaluation

- Fdms0308Cs: N-Channel Powertrench SyncfetDocument8 pagesFdms0308Cs: N-Channel Powertrench Syncfetdreyes3773Pas encore d'évaluation

- Irfp 460 ADocument8 pagesIrfp 460 AKasun Darshana PeirisPas encore d'évaluation

- IRFZ34N Datasheet - KDocument8 pagesIRFZ34N Datasheet - KNairo FilhoPas encore d'évaluation

- 2N60Document8 pages2N60vdăduicăPas encore d'évaluation

- FET 75N75 TransistorDocument8 pagesFET 75N75 Transistorshahid iqbalPas encore d'évaluation

- Irfb4020Pbf: Digital Audio MosfetDocument8 pagesIrfb4020Pbf: Digital Audio Mosfetto_netiksPas encore d'évaluation

- SMD 357Document6 pagesSMD 357Marcoantonio AntonioPas encore d'évaluation

- FDMC86240 DatasheetDocument7 pagesFDMC86240 DatasheetYiannis PapadopoulosPas encore d'évaluation

- Irfz46n PDFDocument9 pagesIrfz46n PDFYunier FernandezPas encore d'évaluation

- IRF740B/IRFS740B: 400V N-Channel MOSFETDocument11 pagesIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldPas encore d'évaluation

- IRFP360LCDocument8 pagesIRFP360LCΗρακλης ΖερκελιδηςPas encore d'évaluation

- Dual N-Channel, Notebook Power Supply MOSFET: June 1999Document9 pagesDual N-Channel, Notebook Power Supply MOSFET: June 1999dreyes3773Pas encore d'évaluation

- IRF540NDocument7 pagesIRF540Nmichaelliu123456Pas encore d'évaluation

- Irfp 90 N 20 DDocument9 pagesIrfp 90 N 20 DAndré Frota PaivaPas encore d'évaluation

- N-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference DataDocument9 pagesN-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference Datalord mace tyrellPas encore d'évaluation

- Irf740b PDFDocument10 pagesIrf740b PDFMed SamiPas encore d'évaluation

- Irf 730 ADocument9 pagesIrf 730 Ajose_mamani_51Pas encore d'évaluation

- FQPF17P06: 60V P-Channel MOSFETDocument8 pagesFQPF17P06: 60V P-Channel MOSFETMahmoued YasinPas encore d'évaluation

- Irl 1004Document9 pagesIrl 1004Luiz RvPas encore d'évaluation

- Irfr3707Zpbf Irfu3707Zpbf: V R Max QGDocument11 pagesIrfr3707Zpbf Irfu3707Zpbf: V R Max QGJared RobisonPas encore d'évaluation

- International Rectifier IRFP2907Document9 pagesInternational Rectifier IRFP2907scribd20110526Pas encore d'évaluation

- DSA00197846 d412 m925Document7 pagesDSA00197846 d412 m925Oswaldo PortilloPas encore d'évaluation

- Irfz 48 VDocument8 pagesIrfz 48 VZoltán HalászPas encore d'évaluation

- Irf 3205 ZPBFDocument13 pagesIrf 3205 ZPBFOsman KoçakPas encore d'évaluation

- AO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect TransistorDocument8 pagesAO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773Pas encore d'évaluation

- Irf1405 DatasheetDocument9 pagesIrf1405 DatasheetE Alejandro G. BenavidesPas encore d'évaluation

- Irlz 24 NDocument9 pagesIrlz 24 NRobson PontinPas encore d'évaluation

- IRFZ48NDocument8 pagesIRFZ48NLuay IssaPas encore d'évaluation

- AOD404 N-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionDocument6 pagesAOD404 N-Channel Enhancement Mode Field Effect Transistor: Features General Descriptiondreyes3773Pas encore d'évaluation

- FDMC8200SDocument12 pagesFDMC8200Sdreyes3773Pas encore d'évaluation

- Irfi 3205 Power MosfetDocument9 pagesIrfi 3205 Power MosfetAndy WilsonPas encore d'évaluation

- Mos Field Effect Transistor: Switching N-Channel Power Mos Fet Industrial UseDocument8 pagesMos Field Effect Transistor: Switching N-Channel Power Mos Fet Industrial Useaalex28Pas encore d'évaluation

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument12 pagesN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical Datameroka2000Pas encore d'évaluation

- N-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DatathedrodPas encore d'évaluation

- IRF830A: Smps MosfetDocument8 pagesIRF830A: Smps MosfetRICHIHOTS2Pas encore d'évaluation

- AO4800 Dual N-Channel Enhancement Mode Field Effect TransistorDocument6 pagesAO4800 Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773Pas encore d'évaluation

- 9N50CDocument10 pages9N50CtecjotaPas encore d'évaluation

- Irfz 34 NLDocument10 pagesIrfz 34 NLguerrero_27Pas encore d'évaluation

- Dual N-Channel Enhancement Mode Phn210T Trenchmos TransistorDocument8 pagesDual N-Channel Enhancement Mode Phn210T Trenchmos TransistorCristian ViolaPas encore d'évaluation

- FDS4435BZDocument6 pagesFDS4435BZCornel PislaruPas encore d'évaluation

- Data Sheet IRFB42N20DDocument8 pagesData Sheet IRFB42N20DvalubaPas encore d'évaluation

- Irlr 7843Document12 pagesIrlr 7843Idris LMPas encore d'évaluation

- AmDg Series Soc Product BriefDocument3 pagesAmDg Series Soc Product BriefKevin TatePas encore d'évaluation

- PIC32 PinoutDocument1 pagePIC32 PinoutKevin Tate100% (1)

- Notebook Combo-Debug-Card User GuideDocument4 pagesNotebook Combo-Debug-Card User GuideKevin TatePas encore d'évaluation

- IP-2372, IP-2376, IP-2377 - DirectionsDocument6 pagesIP-2372, IP-2376, IP-2377 - DirectionsKevin TatePas encore d'évaluation

- BDMaster GUIDE Extract Encapsulated BiosDocument14 pagesBDMaster GUIDE Extract Encapsulated BiosKevin TatePas encore d'évaluation

- I-Launcher Guide For SEC Camera ENGDocument8 pagesI-Launcher Guide For SEC Camera ENGKevin TatePas encore d'évaluation

- CCFL InverterDocument12 pagesCCFL InverterKevin TatePas encore d'évaluation

- RJK 0351 Dpa DatasheetDocument7 pagesRJK 0351 Dpa DatasheetKevin TatePas encore d'évaluation

- PHD 98 N 03Document14 pagesPHD 98 N 03Kevin TatePas encore d'évaluation

- 09 N 03 LaDocument9 pages09 N 03 LaKevin TatePas encore d'évaluation

- Electronics SemiconductorsDocument22 pagesElectronics SemiconductorsA B ShindePas encore d'évaluation

- Pulse Generator G M: ContinuousDocument5 pagesPulse Generator G M: ContinuousMoi MohemedPas encore d'évaluation

- Electrical and Electronic Properties of SolidsDocument47 pagesElectrical and Electronic Properties of SolidsSoumyadeep PradhanPas encore d'évaluation

- 2006optical LithographyDocument41 pages2006optical Lithographyabhinav100% (1)

- Ee121 Lec4 - AnnotatedDocument12 pagesEe121 Lec4 - AnnotatedreneSantosIVPas encore d'évaluation

- Lectures 1-7 Diode Circuit ApplicationsDocument43 pagesLectures 1-7 Diode Circuit ApplicationsMohammad NamiqPas encore d'évaluation

- Gun DiodeDocument7 pagesGun Dioderaveendra_yandaPas encore d'évaluation

- EC402 NanoelectronicsDocument3 pagesEC402 NanoelectronicspakkiausPas encore d'évaluation

- Uln2003d in SMDDocument7 pagesUln2003d in SMDAkylbek KasymovPas encore d'évaluation

- A Ketin Info Mation FZ 900 R 16 KF 1: M R G RDocument4 pagesA Ketin Info Mation FZ 900 R 16 KF 1: M R G RrezaPas encore d'évaluation

- Microsemicorporation Apt10045jll Datasheets 2552Document5 pagesMicrosemicorporation Apt10045jll Datasheets 2552JerryPussykilla11Pas encore d'évaluation

- Unisonic Technologies Co., LTD: 100A, 30V N-Channel Power MosfetDocument8 pagesUnisonic Technologies Co., LTD: 100A, 30V N-Channel Power Mosfetกฤษดา ปินะสาPas encore d'évaluation

- Adobe Scan 13 Feb 2023Document10 pagesAdobe Scan 13 Feb 2023omar meroPas encore d'évaluation

- Chapter 6 The NMOS Family of Logic CircuitDocument54 pagesChapter 6 The NMOS Family of Logic Circuitutsav ashishPas encore d'évaluation

- Lab#11Document4 pagesLab#11Electro OpPas encore d'évaluation

- Ec1461 Vlsi DesignDocument17 pagesEc1461 Vlsi DesignArunkumarPas encore d'évaluation

- Tabela Dos Principais TiristoresDocument3 pagesTabela Dos Principais Tiristoresapi-3837584100% (1)

- SS8050 SMD Transistor NPN Y1 40V 1.5aDocument6 pagesSS8050 SMD Transistor NPN Y1 40V 1.5adinh vinh nguyenPas encore d'évaluation

- 1H Transistor PNP 10a 80V Darlington To 220 1579892328Document2 pages1H Transistor PNP 10a 80V Darlington To 220 1579892328Fuerza AereaPas encore d'évaluation

- CMOS Transistor Theory: Thanks To Prof. David HarrisDocument29 pagesCMOS Transistor Theory: Thanks To Prof. David HarrisHarshdeep BhatiaPas encore d'évaluation

- Analog Electronic (BEL 10203) : Faculty of Electrical & Electronic Engineering, UTHMDocument29 pagesAnalog Electronic (BEL 10203) : Faculty of Electrical & Electronic Engineering, UTHMRicky PaltaPas encore d'évaluation

- Edc JaganDocument196 pagesEdc JagansrinivasPas encore d'évaluation

- SVF10N65CF/K/KL - Datasheet: 10A, 650V N-Channel MosfetDocument9 pagesSVF10N65CF/K/KL - Datasheet: 10A, 650V N-Channel MosfetPramod DixitPas encore d'évaluation

- Fdpc5018Sg: Powertrench Power Clip 30V Asymmetric Dual N-Channel MosfetDocument12 pagesFdpc5018Sg: Powertrench Power Clip 30V Asymmetric Dual N-Channel MosfetDima RozhencovPas encore d'évaluation

- Phototransistor Optocouplers: Description CNY17-1 CNY17-3 CNY17-2 CNY17-4 FeaturesDocument11 pagesPhototransistor Optocouplers: Description CNY17-1 CNY17-3 CNY17-2 CNY17-4 Featuresluis_mariano8998Pas encore d'évaluation

- SyllabusDocument4 pagesSyllabusmariahPas encore d'évaluation

- MOS GATE Video SolutionDocument11 pagesMOS GATE Video SolutionGayatri BagadePas encore d'évaluation

- Jfet CharacteristicsDocument2 pagesJfet Characteristicsddddd14Pas encore d'évaluation

- IR 20153S - Driver para TransistorDocument15 pagesIR 20153S - Driver para TransistorTiago LeonhardtPas encore d'évaluation