Académique Documents

Professionnel Documents

Culture Documents

Pipelining (DSP Implementation) - Wikipedia, The Free Encyclopedia

Transféré par

Subanth WiiliamsDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Pipelining (DSP Implementation) - Wikipedia, The Free Encyclopedia

Transféré par

Subanth WiiliamsDroits d'auteur :

Formats disponibles

11/9/12 Pipelining (DSP implementation) - Wikipedia, the free encyclopedia

Pipelining (DSP implementation)

From Wikipedia, the free encyclopedia

Pipelining is an important technique used in several applications such as digital signal processing (DSP) systems, microprocessors, etc. It originates from the idea of a water pipe with continuous water sent in without waiting for the water in the pipe to come out. Accordingly, it results in speed enhancement for the critical path in most DSP systems. For example, it can either increase the clock speed or reduce the power consumption at the same speed in a DSP system.

Contents

1 Concept 2 Costs and Disadvantages 3 Comparison with Parallel Approaches 4 Pipelining in FIR Filters 5 Pipelining in 1st-Order IIR Filters 6 Other Pipelined DSP Systems 7 Reference

Concept

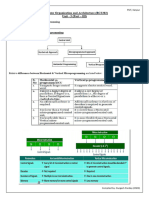

Conceptually, pipelining puts different function units working in parallel. In computer architectures, it usually represents an implementation technique allowing multiple instructions are overlapped in execution to be parallel. Consider an informal example in the following figure. A function includes three sub-function units (F0, F1 and F2). Assume that there are three tasks (T0, T1 and T2) being operated by these three function units and they can be operated independently. The time for each function unit to complete a task is the same and will occupy a slot in the schedule. In such condition, if we put these three units and tasks in a sequential order, the required time to complete them is five slots.

However, if we pipeline T0 to T2 in parallel, the aggregate time is reduced to three slots, which is smaller than in a sequential order.

en.wikipedia.org/wiki/Pipelining_(DSP_implementation) 1/5

11/9/12 Pipelining (DSP implementation) - Wikipedia, the free encyclopedia

Therefore, it is possible for an adequate pipelined design to achieve significant enhancement on speed.

Costs and Disadvantages

Pipelining does not decrease the processing time for a single task. Instead, we still need to cost the same runtime efforts on the same task when compared to a full sequential design. Please note that the advantage of pipelining is that it increases the throughput of the system when processing a stream of task. Nevertheless, applying too many pipelined functions usually leads to the increase of latency. The time required for a task to propagate through a full pipe prolongs. Further a pipelined system typically requires more resources and costs (buffers, circuits, processing units, memory etc.) to perform parallel working since the reuse of resources across different stages is restricted.

Comparison with Parallel Approaches

The other technique to enhance the efficiency of designs is called parallel techniques, which usually confuses with pipelining techniques. The core difference is that parallel techniques usually duplicate function units and distribute all the input tasks into different function units. Therefore, it can complete more tasks per unit time but suffers expensive resource costs. For the previous example, the parallel technique duplicate each function units into another two. Accordingly, all the tasks can be operated under duplicated function units with the same function simultaneously. The time to complete these three tasks is reduced to three slots.

Pipelining in FIR Filters

Consider a 3-tap FIR filter[1]:

which is as shown in the following figure. Assume the calculation time for multiplication units is Tm and Ta for add units. The critical path, representing the minimum time required for processing a new sample, is limited by 1 multiplication and 2 add function units. Therefore, the sample period is given by

en.wikipedia.org/wiki/Pipelining_(DSP_implementation)

2/5

However, such structure may not be suitable for the design with the requirement of high speed. To reduce the sampling period, we can introduce extra pipelining registers along the critical data path. Then the structure is partitioned into two stages and the data produced in the first stage will be stored in the introduced registers, delaying one clock to the second stage. The data in first three clocks is recorded in the following table. Under such pipelined structure, the sample period is reduced to .

Pipelining in 1st-Order IIR Filters

By combining look-ahead techniques and pipelining [2], we are able to enhance the sample rate of target design. Lookahead pipelining will add canceling poles and zeroes to the transfer function such that the coefficients of the following terms in the denominator of the transfer function are zero.

Then, the output sample y(n) can be computed in terms of the inputs and the output sample y(n- M) such that there are M delay elements in the critical loop. These elements are then used to pipeline the critical loop by M stages so that the

11/9/12 Pipelining (DSP implementation) - Wikipedia, the free encyclopedia

sample rate can be increased by a factor M. Consider the 1st-order IIR filter transfer function

The output y(n) can be computed in terms of the input u(n) and the previous output.

In a straightforward structure to design such function, the sample rate of this recursive filter is restricted by the calculation time of one multiply-add operation. To pipeline such design, we observe that H has a pole at

Therefore, in a 3-stage pipelined equivalent stable filter, the transfer function can be derived by adding poles and zeros at

and is given by

Therefore, the corresponding sample rate can be increased by a factor 3.

Other Pipelined DSP Systems

Pipelined Walsh-Fourier transform [3] Pipelined unitary transforms [4] Pipelined DFT [5] Pipelined FFT [6] etc.

Reference

1. ^ K.K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation, John Wiley, 1999 2. ^ Slides for VLSI Digital Signal Processing Systems: Design and Implementation John Wiley & Sons, 1999 (ISBN Number: 0-471-24186-5): http://www.ece.umn.edu/users/parhi/slides.html 3. ^ M. R. Ashouri and A. G. Constantinides, "A pipeline fast Walsh Fourier transform," in Proc. IEEE Int. Conf. ASSP Hartford, CT, May 9-11), pp. 515-518, 1977. 4. ^ Fino, B.J.; Algazi, V.R.; , "Parallel and pipeline computation of fast unitary transforms," Electronics Letters , vol.11, no.5, pp.93-94, March 6 1975 5. ^ Tzou, K.-H.; Morgan, N.P.; , "A fast pipelined DFT processor and its programming consideration," Electronic Circuits and Systems, IEE Proceedings G , vol.132, no.6, pp.273-276, December 1985 6. ^ H. L. Gorginsky and G. A. Works, "A pipeline fast Fourier transform," IEEE Trans. Comput., vol. C-19, pp. 10151019, Nov. 1970.

Retrieved from "http://en.wikipedia.org/w/index.php?title=Pipelining_(DSP_implementation)&oldid=516093453" Categories: Digital signal processing

en.wikipedia.org/wiki/Pipelining_(DSP_implementation) 4/5

11/9/12 Pipelining (DSP implementation) - Wikipedia, the free encyclopedia

This page was last modified on 5 October 2012 at 04:39. Text is available under the Creative Commons Attribution-ShareAlike License; additional terms may apply. See Terms of use for details. Wikipedia is a registered trademark of the Wikimedia Foundation, Inc., a non-profit organization.

en.wikipedia.org/wiki/Pipelining_(DSP_implementation)

5/5

Vous aimerez peut-être aussi

- The Letter and The Cosmos How The Alphabet Has Shaped The Western View of The WorldDocument285 pagesThe Letter and The Cosmos How The Alphabet Has Shaped The Western View of The Worldmarnekib100% (3)

- Peak Performance Cricket ExtractDocument5 pagesPeak Performance Cricket ExtractRui CunhaPas encore d'évaluation

- JCL RefresherDocument50 pagesJCL RefresherCosta48100% (1)

- Digital Signal Processing: Instant AccessD'EverandDigital Signal Processing: Instant AccessÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Managing Change Leading TransitionsDocument42 pagesManaging Change Leading TransitionsSecrets26Pas encore d'évaluation

- Power Semiconductor Controlled Drives - Gopal K Dubey PDFDocument514 pagesPower Semiconductor Controlled Drives - Gopal K Dubey PDFLevingstan Yesudhas84% (103)

- Well Logging 1Document33 pagesWell Logging 1Spica FadliPas encore d'évaluation

- Pipelining (DSP Implementation) : ConceptDocument7 pagesPipelining (DSP Implementation) : ConceptLokeshRathorPas encore d'évaluation

- Module 4Document12 pagesModule 4Bijay NagPas encore d'évaluation

- Aca Module 2Document35 pagesAca Module 2Shiva prasad100% (1)

- The Optimum Pipeline Depth For A Microprocessor: A. Hartstein and Thomas R. PuzakDocument7 pagesThe Optimum Pipeline Depth For A Microprocessor: A. Hartstein and Thomas R. PuzakSiddharth SinghPas encore d'évaluation

- Paralle ProcessingDocument8 pagesParalle ProcessingRavi RavikiranPas encore d'évaluation

- Pipeline and Vector Processing ExplainedDocument19 pagesPipeline and Vector Processing ExplainedriyazpashaPas encore d'évaluation

- Lecture Notes On Parallel Processing PipelineDocument12 pagesLecture Notes On Parallel Processing PipelineYowaraj ChhetriPas encore d'évaluation

- Instruction PipelineDocument16 pagesInstruction PipelineRamya RamasubramanianPas encore d'évaluation

- PipelineDocument30 pagesPipelineSushrutPas encore d'évaluation

- On-Chip Implementation of High Resolution High Speed Low Area Floating Point AdderSubtractor With Reducing Mean Latency For OFDM ApplicationsDocument6 pagesOn-Chip Implementation of High Resolution High Speed Low Area Floating Point AdderSubtractor With Reducing Mean Latency For OFDM ApplicationsDr. Rozita teymourzadeh, CEng.Pas encore d'évaluation

- Pipeline and Vector ProcessingDocument28 pagesPipeline and Vector ProcessingTerror BladePas encore d'évaluation

- Time and Area Optimization in Processor ArchitectuDocument12 pagesTime and Area Optimization in Processor Architectubashman6744Pas encore d'évaluation

- Advanced Computer Architecture 2Document17 pagesAdvanced Computer Architecture 2Pritesh PawarPas encore d'évaluation

- VI. Implicit Parallelism - Instruction Level VI. Implicit Parallelism Instruction Level Parallelism. Pipeline Superscalar & Vector P ProcessorsDocument26 pagesVI. Implicit Parallelism - Instruction Level VI. Implicit Parallelism Instruction Level Parallelism. Pipeline Superscalar & Vector P Processorstt_aljobory3911Pas encore d'évaluation

- BCS302 Unit-3 (Part-III)Document4 pagesBCS302 Unit-3 (Part-III)dp06vnsPas encore d'évaluation

- Survey On DLMS Adaptive Filter With Low DelayDocument5 pagesSurvey On DLMS Adaptive Filter With Low DelayshastryPas encore d'évaluation

- Round Robin Scheduling Algorithm Explained in 40 CharactersDocument6 pagesRound Robin Scheduling Algorithm Explained in 40 CharactersSikandar Javid100% (1)

- Pipe LiningDocument32 pagesPipe LiningveerendrasettyPas encore d'évaluation

- Instruction pipelining explainedDocument5 pagesInstruction pipelining explainedAyush KumarPas encore d'évaluation

- Computer Organization and Architecture: Addressing ModesDocument22 pagesComputer Organization and Architecture: Addressing Modesparvathyp220246ecPas encore d'évaluation

- A Synthesisable Quasi-Delay Insensitive Result Forwarding Unit For An Asynchronous ProcessorDocument8 pagesA Synthesisable Quasi-Delay Insensitive Result Forwarding Unit For An Asynchronous ProcessorHoogahPas encore d'évaluation

- Everything You Need to Know About PipeliningDocument5 pagesEverything You Need to Know About PipeliningRam RamPas encore d'évaluation

- Optimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviDocument13 pagesOptimal Circuits For Parallel Multipliers: Paul F. Stelling,,, Charles U. Martel, Vojin G. Oklobdzija,,, and R. RaviMathew GeorgePas encore d'évaluation

- Graph Theory Algorithms For Real Time Control of A Sewer NetworkDocument9 pagesGraph Theory Algorithms For Real Time Control of A Sewer NetworkKiller BabuPas encore d'évaluation

- Enhanced Tdma Based High Speed Bus Arbitrarion: Pankaj Dobwal (Mtvlsi 2011 20) Harsh Vishakarma (Mtvlsi 2011 11Document20 pagesEnhanced Tdma Based High Speed Bus Arbitrarion: Pankaj Dobwal (Mtvlsi 2011 20) Harsh Vishakarma (Mtvlsi 2011 11Harsh VishwakarmaPas encore d'évaluation

- Reducing Hardware Complexity of Parallel Prefix AddersDocument48 pagesReducing Hardware Complexity of Parallel Prefix AddersSai Teja100% (1)

- CA Classes-76-80Document5 pagesCA Classes-76-80SrinivasaRaoPas encore d'évaluation

- Pipelining: Introduction, Hazards, and ImplementationDocument13 pagesPipelining: Introduction, Hazards, and ImplementationReshma BJPas encore d'évaluation

- Ca 6Document19 pagesCa 6SUMAN BROOPas encore d'évaluation

- Introduction To Parallel ProcessingDocument11 pagesIntroduction To Parallel ProcessingSathish KumarPas encore d'évaluation

- Pipeline Architecture: C. V. RamamoorthyDocument42 pagesPipeline Architecture: C. V. Ramamoorthykarunya.varmaPas encore d'évaluation

- High-Speed Area-Efficient VLSI Architecture of Three-Operand Binary AdderDocument6 pagesHigh-Speed Area-Efficient VLSI Architecture of Three-Operand Binary Adderk NiroshaPas encore d'évaluation

- Pipeline ProcessingDocument28 pagesPipeline Processinganismitaray14Pas encore d'évaluation

- Parallel AdderDocument20 pagesParallel AddermdbelalrshdPas encore d'évaluation

- On The Impact of TCP and Per - Ow Scheduling On Internet PerformanceDocument26 pagesOn The Impact of TCP and Per - Ow Scheduling On Internet Performanceterminatory808Pas encore d'évaluation

- ConvolutionDocument6 pagesConvolutionAmar NathPas encore d'évaluation

- Assignment A (COMP90044)Document5 pagesAssignment A (COMP90044)tritha7Pas encore d'évaluation

- Lec18 PipelineDocument59 pagesLec18 PipelineAliGhandiPas encore d'évaluation

- Lec20 PDFDocument49 pagesLec20 PDFMustafa Rashik HasnainPas encore d'évaluation

- Paper NLT Partitioned Mine PWRD 2011Document8 pagesPaper NLT Partitioned Mine PWRD 2011Alexander SanchezPas encore d'évaluation

- System On Chip: Inside Processor Pipeline StallsDocument12 pagesSystem On Chip: Inside Processor Pipeline StallsPinagani SurajPas encore d'évaluation

- Pipeline Architecture PDFDocument42 pagesPipeline Architecture PDFChuang James100% (1)

- Wavepipelined InterconnectsDocument5 pagesWavepipelined InterconnectsbibincmPas encore d'évaluation

- Types of Operating System SchedulersDocument26 pagesTypes of Operating System SchedulersVa SuPas encore d'évaluation

- Synopsis On FFTDocument5 pagesSynopsis On FFTtanajeekPas encore d'évaluation

- Preprints: 11th International Workshop On REAL Time Networks RTN'12Document37 pagesPreprints: 11th International Workshop On REAL Time Networks RTN'12hoalongcongphap95Pas encore d'évaluation

- Global Clock Synchronization Method Based On Highest Clock Divergence in MANETDocument5 pagesGlobal Clock Synchronization Method Based On Highest Clock Divergence in MANETInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- Pipelining: Improving CPU Performance Through Simultaneous Instruction ExecutionDocument12 pagesPipelining: Improving CPU Performance Through Simultaneous Instruction ExecutionAradhyaPas encore d'évaluation

- Electronics: Asynchronous Floating-Point Adders and Communication Protocols: A SurveyDocument23 pagesElectronics: Asynchronous Floating-Point Adders and Communication Protocols: A SurveyHappu SahabPas encore d'évaluation

- Computer Architecture Prof. Madhu Mutyam Department of Computer Science and Engineering Indian Institute of Technology, MadrasDocument14 pagesComputer Architecture Prof. Madhu Mutyam Department of Computer Science and Engineering Indian Institute of Technology, MadrasElisée NdjabuPas encore d'évaluation

- Real Time Fast Algorithm of 2D DWT Based DSP TechnologyDocument5 pagesReal Time Fast Algorithm of 2D DWT Based DSP TechnologyInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- FHWA Office of Operations - Section 3.0 - Base Model DevelopmentDocument22 pagesFHWA Office of Operations - Section 3.0 - Base Model DevelopmentLuis Carlos Caicedo BarreraPas encore d'évaluation

- Compactly Encoding Unstructured Inputs With Differential CompressionDocument50 pagesCompactly Encoding Unstructured Inputs With Differential Compressionnz0ptkPas encore d'évaluation

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashPas encore d'évaluation

- Downlink Scheduler Basedon Deadlinesfor LTENetworksDocument5 pagesDownlink Scheduler Basedon Deadlinesfor LTENetworksImen DebbabiPas encore d'évaluation

- Computational Fluid Dynamics: Práticas de Engenharia Química IvDocument37 pagesComputational Fluid Dynamics: Práticas de Engenharia Química IvPedro SilvaPas encore d'évaluation

- Addition Algorithms For Vlsi - A Review: Kapilramgavali1, Sandeepdubey, Gaurav Shete, Sushant GawadeDocument8 pagesAddition Algorithms For Vlsi - A Review: Kapilramgavali1, Sandeepdubey, Gaurav Shete, Sushant GawadeKapilGavaliPas encore d'évaluation

- Insulation - InsulationDocument9 pagesInsulation - InsulationPaneendra KumarPas encore d'évaluation

- Sample New Age Dem PDFDocument6 pagesSample New Age Dem PDFSubanth WiiliamsPas encore d'évaluation

- EE2355 Design of Electrical Machines NotesDocument24 pagesEE2355 Design of Electrical Machines Notesmadhes14Pas encore d'évaluation

- Thyristor DC Drives. P.c.senDocument307 pagesThyristor DC Drives. P.c.senpalu259478% (9)

- Unit 1Document65 pagesUnit 1Kabi RockPas encore d'évaluation

- Anna University Report FormatDocument7 pagesAnna University Report Formatdilip_66690% (10)

- Ee2355 Dem Nol 2013Document24 pagesEe2355 Dem Nol 2013Anurag AryaPas encore d'évaluation

- EMTP Ref Model-FinalDocument61 pagesEMTP Ref Model-FinalRadhika PriyadarshiniPas encore d'évaluation

- EE2355 DEM Unit-I Solved ProblemsDocument3 pagesEE2355 DEM Unit-I Solved ProblemsSubanth WiiliamsPas encore d'évaluation

- EE2355 DEM 2marks 2013Document19 pagesEE2355 DEM 2marks 2013baks007Pas encore d'évaluation

- Dem May June 2013 QPDocument3 pagesDem May June 2013 QPSubanth WiiliamsPas encore d'évaluation

- Eee SyllabusDocument111 pagesEee SyllabusDhana SelvamPas encore d'évaluation

- Guidelines for M.E./M.Tech Phase I Report & Phase II ThesisDocument13 pagesGuidelines for M.E./M.Tech Phase I Report & Phase II Thesisபுருஷோத்தமன் சரவணன்Pas encore d'évaluation

- Paper 4Document6 pagesPaper 4Subanth WiiliamsPas encore d'évaluation

- UG - Except 8th Sem and UG PG 2 Sem PDFDocument1 pageUG - Except 8th Sem and UG PG 2 Sem PDFSam Devid Jero DuraisamyPas encore d'évaluation

- DSP ArchitectureDocument63 pagesDSP Architecturekrrakesh5Pas encore d'évaluation

- Coe1.annauniv - Edu Aucoe PDF 2015 Apr May UG PG Second Sem Am15 PDFDocument1 pageCoe1.annauniv - Edu Aucoe PDF 2015 Apr May UG PG Second Sem Am15 PDFSubanth WiiliamsPas encore d'évaluation

- WWW - Eit.lth - Se Fileadmin Eit Courses Eti180 Slides2011 Lec-PipeParDocument23 pagesWWW - Eit.lth - Se Fileadmin Eit Courses Eti180 Slides2011 Lec-PipeParSubanth WiiliamsPas encore d'évaluation

- Unit 3Document15 pagesUnit 3Subanth WiiliamsPas encore d'évaluation

- Part-A Answer All (5x2 10)Document1 pagePart-A Answer All (5x2 10)Subanth WiiliamsPas encore d'évaluation

- Spra 053Document34 pagesSpra 053Subanth WiiliamsPas encore d'évaluation

- Ec 1362-Microprocessors AndicrocontrollerDocument7 pagesEc 1362-Microprocessors Andicrocontrollerpurushoth@aeroPas encore d'évaluation

- ParallelismDocument4 pagesParallelismSubanth WiiliamsPas encore d'évaluation

- Evs Quest 1asecDocument1 pageEvs Quest 1asecSubanth WiiliamsPas encore d'évaluation

- Introduction To Real-Time ProgrammingDocument15 pagesIntroduction To Real-Time ProgrammingSubanth WiiliamsPas encore d'évaluation

- Parallel Processing (DSP Implementation) - Wikipedia, The Free EncyclopediaDocument5 pagesParallel Processing (DSP Implementation) - Wikipedia, The Free EncyclopediaSubanth WiiliamsPas encore d'évaluation

- Lab5 AssignmentDocument3 pagesLab5 AssignmentSelva KumarPas encore d'évaluation

- Syllabus MII LabDocument1 pageSyllabus MII LabSubanth WiiliamsPas encore d'évaluation

- Ranking Hospital - Do We Gain Reliability by Using Composite Rather Than Individual Indicators?Document9 pagesRanking Hospital - Do We Gain Reliability by Using Composite Rather Than Individual Indicators?Robert CoffinPas encore d'évaluation

- Chapter 1 Measurements: 1.1 Units of MeasurementDocument24 pagesChapter 1 Measurements: 1.1 Units of MeasurementEsmira Melić ŠutkovićPas encore d'évaluation

- Wave Hydro Dynamics Prof. V. Sundar Department of Ocean Engineering Indian Institute of Technology, MadrasDocument32 pagesWave Hydro Dynamics Prof. V. Sundar Department of Ocean Engineering Indian Institute of Technology, MadrasMuralidhar YarakalaPas encore d'évaluation

- Seminar Report On Satellite CommunicationDocument17 pagesSeminar Report On Satellite CommunicationHapi ER67% (6)

- 2VAA001654 - en S Control SPDSM04 Pulse Input ModuleDocument49 pages2VAA001654 - en S Control SPDSM04 Pulse Input ModuleanbarasanPas encore d'évaluation

- SQ3R Is A Reading Strategy Formed From Its LettersDocument9 pagesSQ3R Is A Reading Strategy Formed From Its Letterschatura1989Pas encore d'évaluation

- Background and Introduction of The ProblemDocument48 pagesBackground and Introduction of The ProblemElizebethPas encore d'évaluation

- Affine CipherDocument3 pagesAffine CipheramitpandaPas encore d'évaluation

- Quality Policy Nestle PDFDocument6 pagesQuality Policy Nestle PDFJonathan KacouPas encore d'évaluation

- HTTP API - SMS Help GuideDocument8 pagesHTTP API - SMS Help Guideaksh11inPas encore d'évaluation

- Soal Biokim IDocument9 pagesSoal Biokim INuraMalahayatiPas encore d'évaluation

- (Genus - Gender in Modern Culture 12.) Segal, Naomi - Anzieu, Didier - Consensuality - Didier Anzieu, Gender and The Sense of Touch-Rodopi (2009)Document301 pages(Genus - Gender in Modern Culture 12.) Segal, Naomi - Anzieu, Didier - Consensuality - Didier Anzieu, Gender and The Sense of Touch-Rodopi (2009)Anonymous r3ZlrnnHcPas encore d'évaluation

- Test Bank For Environmental Science For A Changing World Canadian 1St Edition by Branfireun Karr Interlandi Houtman Full Chapter PDFDocument36 pagesTest Bank For Environmental Science For A Changing World Canadian 1St Edition by Branfireun Karr Interlandi Houtman Full Chapter PDFelizabeth.martin408100% (16)

- Win10 Backup Checklist v3 PDFDocument1 pageWin10 Backup Checklist v3 PDFsubwoofer123Pas encore d'évaluation

- I-K Bus Codes v6Document41 pagesI-K Bus Codes v6Dobrescu CristianPas encore d'évaluation

- Journal of Statistical Planning and Inference: Akanksha S. KashikarDocument12 pagesJournal of Statistical Planning and Inference: Akanksha S. KashikarAkanksha KashikarPas encore d'évaluation

- Signal Sampling, Quantization, Binary Encoding: Oleh Albert SagalaDocument46 pagesSignal Sampling, Quantization, Binary Encoding: Oleh Albert SagalaRamos D HutabalianPas encore d'évaluation

- Installing OpenSceneGraphDocument9 pagesInstalling OpenSceneGraphfer89chopPas encore d'évaluation

- A&P Book - Aeronautical Charts and CompassDocument17 pagesA&P Book - Aeronautical Charts and CompassHarry NuryantoPas encore d'évaluation

- NPTEL Managerial Economics Video CourseDocument3 pagesNPTEL Managerial Economics Video CourseAmanda AdamsPas encore d'évaluation

- Final Project SociologyDocument14 pagesFinal Project Sociologyvikas rajPas encore d'évaluation

- DN 6720 PDFDocument12 pagesDN 6720 PDFChandan JhaPas encore d'évaluation

- Assessment of Knowledge, Attitude Andpractice Toward Sexually Transmitteddiseases in Boditi High School StudentsDocument56 pagesAssessment of Knowledge, Attitude Andpractice Toward Sexually Transmitteddiseases in Boditi High School StudentsMinlik-alew Dejenie88% (8)

- PESTEL Team Project (Group)Document9 pagesPESTEL Team Project (Group)Yadira Alvarado saavedraPas encore d'évaluation

- SPM Literature in English Tips + AdviseDocument2 pagesSPM Literature in English Tips + AdviseJessica NgPas encore d'évaluation