Académique Documents

Professionnel Documents

Culture Documents

Automat Is Me

Transféré par

omarkhan33Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Automat Is Me

Transféré par

omarkhan33Droits d'auteur :

Formats disponibles

MULTIPLEXEURS CIRCUITS ARITHMETIQUES

1- BUT :

Le but de cette manipulation est : -Raliser un multiplexeur deux voies avec des oprateurs logiques et vrifier le fonctionnement dun multiplexeur deux voies en circuit intgr. -Raliser des circuits arithmtiques (additionneurs et soustracteurs laide doprateurs logiques et vrifier le fonctionnement dun additionneur en circuit intgr.

2- LE MULTIPLEXEUR A 2 VOIES

n Le multiplexeur est un circuit combinatoire ! entres dinformation, n entres dadresse et 1 sortie.

Suivant l'tat de l'entre de slection A, la sortie S recopie soit l'entre D0, soit l'entre D1.

Supposons que pour A = 0, S = D0 et que pour A = 1, S = D1.

A 0 1 S D0 D1

Nous en dduisons l'quation de S suivante : S = D0 + D1A

Le circuit logique correspondant ".

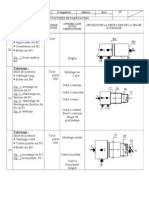

Multiplexeur 2 voies intgr :le 74LS157

Le circuit intgr #$L"%&# est un quadruple multiplexeur ! voies entre de slection commune.

Considrons la donne A constitue des bits A1, A2, A3 et A4, la donne B constitue des bits B1, B2, B3 et B4 et la donne Y constitue des bits Y1, Y2, Y3 et Y4. En fonctionnement normal, l'entre STROBE est maintenue Si l'entre SELECT est l'tat 0, la donne Y est !ale 0.

la donne A.

Si l'entre SELECT est

l'tat 1, la donne Y est !ale

la donne B.

"n multiple#eur peut donc ai!uiller des donnes constitues de plusieurs bits.

3-ADDITIONNEURS :

3-1 le demi-additionneur :

'u niveau du poids le plus bas( il n) a pas de retenus provenant du rang infrieur. *n peut donc se contenter dun s)st+me simple ralisant uniquement la somme de deux bits ' et ,. -n tel s)st+me est appel demi-additionneur. a .able de vrit

D$apr%s la table de vrit on a & S=A B

C=A.B b' (e circuit qui effectue la somme de deu# bits peut )tre obtenue en associant une porte OU Exclusif et une porte ET comme le montre &

3-2 Ladditionneur omplet :

.ous les tages autres que ltage correspondant au poids le plus faible impliquent la prise en compte de la retenue venant du rang immdiatement infrieur. Les s)st+mes de ce t)pe sont appels additionneurs complets. /ls ont dentres ' et , et 0 et deux fonctions de sortie et 0. .ravail demande a La table de vrit dun additionneur complet

Si = Ci . = Ci . ( = Ci = Ci

i. i.

i+

i.

i . Bi + Ci . Ai . Bi + i.( Bi i . Bi + Ai .

i . Ai . i

i + Ai . Bi + + i . (Ai Bi iBiCi + Ai iBi + Ai Bi

(Ai

Ci + 1 = AiBi +

iCi

= AiBi + Ci ( = AiBi + Ci (Ai

b' (es deu# e#pressions Si et Ci + 1 qui viennent d')tre calcules, nous dduisons le sc*ma lo!ique d'un additionneur complet &

3-3 !dditionneur en ir uit intgr :

Le circuit $112 est un additionneur $ bits. /l realise la somme des nombres '(a3a!a%a1 et ,(a3a!a%a1 .

4-SOUSTRACTEURS :

4-1 "emi-soustra teur

a .able de vrit : ' 1 1 % % , 1 % 1 % 4 1 % % 1 R 1 % 1 1

S=A

C=A.B b Le circuit :

4-2 Soustra teur omplet :

a .able de vrit :

' 1 1 1 1 % % % %

, 1 1 % % 1 1 % %

0 1 % 1 % 1 % 1 %

4 1 % % 1 % 1 1 %

0 1 % % % 1 1 1 %

45 ('6, 60 0 5',60 ('6, b Le circuit :

4- CONCLUSION :

Le multiplexeur comporte ! n entres d7information

n entres de slection (entre d7un nombre / en binaire % sortie (recopie de l7entre d7information (numro / sur la sortie

Les circuits arithmtiques sont dune grande importance non seulement dans les ordinateurs mais aussi dans un grand nombre de s)st+mes traitant les donnes numriques.

Vous aimerez peut-être aussi

- Cours - MATH - SF HDocument62 pagesCours - MATH - SF Homarkhan33Pas encore d'évaluation

- Les Liaisons EncastrementsDocument24 pagesLes Liaisons EncastrementsTounsi TwensaPas encore d'évaluation

- Cours Math SNDocument29 pagesCours Math SNomarkhan33Pas encore d'évaluation

- Cours Math SFDocument34 pagesCours Math SFomarkhan33Pas encore d'évaluation

- Cours Math TLDocument37 pagesCours Math TLomarkhan33Pas encore d'évaluation

- Chapitre 1Document5 pagesChapitre 1Chakib KaPas encore d'évaluation

- Exercices Sur La Transformee en Z: Exercice 1Document7 pagesExercices Sur La Transformee en Z: Exercice 1omarkhan33Pas encore d'évaluation

- Projet KamalDocument1 pageProjet Kamalomarkhan33Pas encore d'évaluation

- Cours Math SeDocument24 pagesCours Math Seomarkhan33Pas encore d'évaluation

- Cours Math TLDocument37 pagesCours Math TLomarkhan33Pas encore d'évaluation

- Gamme Corps Hydraulique CorrigeDocument4 pagesGamme Corps Hydraulique CorrigeMohamed DridiPas encore d'évaluation

- Cours OSDocument100 pagesCours OSomarkhan33Pas encore d'évaluation

- Cours - MATH - SF HDocument62 pagesCours - MATH - SF Homarkhan33Pas encore d'évaluation

- Les Game D'usinage de PFE by YounessDocument16 pagesLes Game D'usinage de PFE by Younessomarkhan33Pas encore d'évaluation

- Rapport Final PFE PDFDocument129 pagesRapport Final PFE PDFomarkhan33Pas encore d'évaluation

- Pfe - Amdec Machine PDFDocument77 pagesPfe - Amdec Machine PDFomarkhan3378% (88)

- 1 ErordreDocument4 pages1 ErordreSaad HamimiPas encore d'évaluation

- Pfe SALIHDocument70 pagesPfe SALIHomarkhan33Pas encore d'évaluation

- Séchoir A Lit FluidiséDocument49 pagesSéchoir A Lit Fluidiséomarkhan33100% (2)

- FDocument65 pagesFomarkhan33Pas encore d'évaluation

- Neuro PsychoDocument352 pagesNeuro PsychoNounou NouhadePas encore d'évaluation

- TURCS Et MONTENEGRiNS: F.LENORMANT, 1866 PARiSDocument524 pagesTURCS Et MONTENEGRiNS: F.LENORMANT, 1866 PARiSYasef BayPas encore d'évaluation

- Sturdza - Europe Orientale Et Le Role Historique Des MaurocordatoDocument519 pagesSturdza - Europe Orientale Et Le Role Historique Des Maurocordatobogdancretu21011978Pas encore d'évaluation

- Mohamed Sifaoui - Où Va L'algérie... Et Les Conséquences Pour La France PDFDocument248 pagesMohamed Sifaoui - Où Va L'algérie... Et Les Conséquences Pour La France PDFikonten4267% (3)

- Appel Fouad LarouiDocument4 pagesAppel Fouad LarouihattabsatPas encore d'évaluation

- Exercice Verbe Etre Et Avoir - Google SearchDocument1 pageExercice Verbe Etre Et Avoir - Google SearchWafa DridiPas encore d'évaluation

- ConjugaisonDocument3 pagesConjugaisonromeroniPas encore d'évaluation

- Fonctions Executives CB - 3 DiapoDocument19 pagesFonctions Executives CB - 3 DiapoFARHAT HAJERPas encore d'évaluation

- 2.2.4.11 Lab - Configuring Switch Security FeaturesDocument10 pages2.2.4.11 Lab - Configuring Switch Security FeaturesOumou DialloPas encore d'évaluation

- FR NeurologieDocument17 pagesFR Neurologiemaroxibo100% (1)

- 78842-Art3 Brienn N N Robidoux Et Al. 39192-V3N1 201705Document11 pages78842-Art3 Brienn N N Robidoux Et Al. 39192-V3N1 201705Rachid BenhmidouPas encore d'évaluation

- Comment Poser Des Questions FerméesDocument2 pagesComment Poser Des Questions FerméesDalila RgPas encore d'évaluation

- Organisation D'un Service D'audit InterneDocument49 pagesOrganisation D'un Service D'audit InterneSouha Layane100% (46)

- 7 Geometrie de L'espaceDocument16 pages7 Geometrie de L'espaceKakou Light MalanPas encore d'évaluation

- 3-Effort IntérieurDocument8 pages3-Effort IntérieurGOUAL SaraPas encore d'évaluation

- Sourah WaqiahDocument106 pagesSourah WaqiahFleur De Lune100% (4)

- Traitement de l'HTADocument15 pagesTraitement de l'HTABMA-medecinePas encore d'évaluation

- استشهادات تطبيق الكفاياتDocument80 pagesاستشهادات تطبيق الكفاياتselotmani100% (1)

- 10 ALADIAHDocument2 pages10 ALADIAHNicolasPas encore d'évaluation

- RecueilExamSMA5 M28Document14 pagesRecueilExamSMA5 M28Gustave KerryPas encore d'évaluation

- TDR Certificat Coach Professionnel - Level 1Document3 pagesTDR Certificat Coach Professionnel - Level 1nicaise djuePas encore d'évaluation

- 874-Article Text-3260-1-10-20230113Document17 pages874-Article Text-3260-1-10-20230113khadija rabibPas encore d'évaluation

- Ecritures Du Moi Lignes de Vie t1Document544 pagesEcritures Du Moi Lignes de Vie t1david balibalPas encore d'évaluation

- Dokumen - Tips Cours Mthodes 1 Variable Alatoire Et Loi de ProbabilitDocument10 pagesDokumen - Tips Cours Mthodes 1 Variable Alatoire Et Loi de Probabilitmayar mimiPas encore d'évaluation

- Examen2 Structure Machine 2Document1 pageExamen2 Structure Machine 2benhadjeba boumedyenPas encore d'évaluation

- Les Entraves A La Professionnalisation DDocument13 pagesLes Entraves A La Professionnalisation DFatoumata MaigaPas encore d'évaluation

- 1.3.1. La SubordinationDocument6 pages1.3.1. La SubordinationFrédéric LetellierPas encore d'évaluation

- Champ Lexical Du ThéâtreDocument1 pageChamp Lexical Du ThéâtreBurt Son100% (1)

- Cours IE - Fahd ASSILADocument45 pagesCours IE - Fahd ASSILAadnane.iherkachen100% (1)

- ISO9001Document66 pagesISO9001Mostafa BelaaroussiPas encore d'évaluation