Académique Documents

Professionnel Documents

Culture Documents

VHDL Piano Using Xilink Sparta Board

Transféré par

jasmine-rTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

VHDL Piano Using Xilink Sparta Board

Transféré par

jasmine-rDroits d'auteur :

Formats disponibles

FPGA PIANO USING VHDL

On Xilink Sparta Board

!

Jasmine A. Roberts

Columbia University, Electrical Engineering

! !

! ! !

Roberts, FPGA Piano Using VHDL

ABSTRACT

The main intention of the project was to implement an electric piano on a Spartan 3 development board using Xilinx Integrated Software Environment. The hardware was done using VHDL encoding. By use of a piezoelectric speaker with moderately high impedance, the piano was driven directly from the FPGA. Switches output four-bit digital logic code transferred to FPGA. The VHDL description is synthesized to logic and the 8 notes corresponding to the C scale in global music theory, and mapped to the gates of the FPGA.

INTRODUCTION

The notes are encoded on switches by the following segment of code: when when when when when when when when "10000000" "01000000" "00100000" "00010000" "00001000" "00000100" "00000010" others -- C -- D -- E -- F -- G -- A -- B none

The clock used is a 50 MHz input clock, the following are the waveforms on CLK_OUT and ONE_SHOT for EN = '1' and DIV = X"32". The toggle and trigger waveforms are also presented !"#$%#&'( ! !"# !"#! ! !

DIV=X32=50, CLK=50MHz, f=0.5 MHz With a frequency of 0.5 MHz for CLK_OUT ! CLK_OUT!!!!!!!!""""!!!!""""!!!!""""!!!!"""""!!!!""""!!!!!""""! TRIGGER!!!!!!!!#!!!#!!!!#!!!#!!!!#!!!#!!!!#!!!#!!!!#!!!#!!!!#!!!! TOGGLE!!!!!!!!!!""""!!!!""""!!!!""""!!!!"""""!!!!""""!!!!!""""! ONE_SHOT!!!!!!!!!!#!!!!!!!!#!!!!!!!#!!!!!!!!#!!!!!!!#!!!!!!!!! ! !

For a 1MHz input, the output frequency as a function of divider value is . These values were verified with the values used for the note decoder to define the notes of the piano.

f = CLK / DIV * .5 ONE_SHOT frequency = F/2 when when when when when when when when when when when "00001" "00010" "00011" "00100" "00101" "00110" "00111" "01000" "01001" "01010" "01011" => => => => => => => => => => => next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div <= <= <= <= <= <= <= <= <= <= <= x"0EEE"; x"0E18"; x"0D4E"; x"0C8E"; x"0BDA"; x"0B30"; x"0A8E"; x"09F7"; x"0968"; x"08E1"; x"0861"; -----------C3 C3# D3 D3# E3 F3 F3# G3 G3# A3 A3# DIV=3822 DIV=3608 DIV=3406 DIV=3214 DIV=3034 DIV=2864 DIV=2702 DIV=2551 DIV=2408 DIV=2273 DIV=2145 F=130.8 F=138.6 F=146.8 F=155.6 F=164.8 F=174.6 F=185 F=196 F=207.6 F=219.9 F=233.1

Roberts, FPGA Piano Using VHDL

when when when when when when when when when when when when when when when

"01100" "01101" "10000" "10001" "10010" "10011" "10100" "10101" "10110" "10111" "11000" "11001" "11010" "11011" "11100"

=> => => => => => => => => => => => => => =>

next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div next_div

<= <= <= <= <= <= <= <= <= <= <= <= <= <= <=

x"07E9"; x"0777"; x"07E9"; x"0777"; x"070C"; x"06A7"; x"0647"; x"05ED"; x"0598"; x"0547"; x"04FB"; x"04B4"; x"0470"; x"0431"; x"03F4";

----------------

B3 B3# C4b C4 C4# D4 D4# E4 F4 F4# G4 G4# A4 A4# B4

= C4 = B3

DIV=2025 F=246.9 DIV=1911 F=261.6 DIV=2025 F=246.9 DIV=1911 F=261.6 DIV=1804 F=277.1 DIV=1703 F=293.6 DIV=1607 F=311.1 DIV=1517 F=329.6 DIV=1432 F=349.1 DIV=1351 F=370 DIV=1275 F=392.1 DIV=1204 F=415.3 DIV=1136 F=440.1 DIV=1073 F=468.9 DIV=1012 F=494.1

RESULTS

Seven_seg.vhd contains a lookup table to map each note to the corresponding seven-segment outputs. It stores this value in an 8-bit buffer, seg_buf. It has 8 bits 4 bits per digit. This value is updated on the rising edge of the clock. A signal cur_dig is incremented on every rising edge of the clock. If cur_dig = 00, it sets dig_now to the first 4 bits of seg_buf, or the first display. If it is 01, it sets it to the second display. Otherwise, it displays nothing. It then decodes the dig_now to the corresponding signals that are sent to the 7-segment display, through another lookup table. Additional stimulus was added for various values of pb_in and switch_in and saved to the test bench. Code was added to simulate the switches to play different notes. Simulation results below:

! ! !

Roberts, FPGA Piano Using VHDL

! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! ! !

Roberts, FPGA Piano Using VHDL

! !

This design plays a few measures of Part of Your World from Disneys The Little Mermaid. The user interface was deleted (commented out so it could still be referenced to the encode notes) and played the output note from play_position to the signal note_select in piano.vhd. The notes are played at the latch output in note_play.vhd. A cascade of elseif statements executes the notes. Contained within the elsif statement are pointers to the notes found in the note lookup table. The tempo of the song was controlled by the frequency in hexadecimal. A half-note is one second, and is implemented by adding 50MHz to the previous signal. A quarter-note is implemented by adding 25MHz, a whole-note by adding 100MHz. Ideally, quarter-note triplets should be executed by incrementing by 16 !! 50/3), unfortunately, when a design using quarter-note triplets was implemented, the output was muddled. Therefore, an easier tempo was implemented. The solution would be to increase the speed of the clock used to count through the notes. The notes corresponding to the measure played are B A F C B A F C C E F.

!

CODE

! ! PIANO.VHD --- piano.vhd - FPGA Piano -library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; library UNISIM; use UNISIM.VComponents.all; entity piano is port ( CLK_IN pb_in switch_in SPK_N SPK_P led_out digit_out seg_out : : : : : : : : in std_logic; in std_logic_vector(3 downto 0); in std_logic_vector(7 downto 0); out std_logic; out std_logic; out std_logic_vector(7 downto 0); out std_logic_vector(3 downto 0); out std_logic_vector(7 downto 0)

Roberts, FPGA Piano Using VHDL

); end piano; architecture -- Xilinx component component; component component; component component; component component; component port ( Behavioral of piano is Native Components BUFG port ( I : in std_logic; O : out std_logic); end IBUFG port ( I : in std_logic; O : out std_logic); end IBUF OBUF port ( I : in std_logic; O : out std_logic); end port ( I : in std_logic; O : out std_logic); end : : : : : : : : : : : : : : : : : : : in in in in in in in out out out out out out out out out out out out std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic; std_logic_vector (7 downto 0); std_logic; std_logic);

DCM CLKIN CLKFB RST PSEN PSINCDEC PSCLK DSSEN CLK0 CLK90 CLK180 CLK270 CLKDV CLK2X CLK2X180 CLKFX CLKFX180 STATUS LOCKED PSDONE end component; -- My Components:

-- Clock Divider component clk_dvd port ( CLK : in std_logic; RST : in std_logic; DIV : in std_logic_vector(15 downto 0); EN : in std_logic; CLK_OUT : out std_logic; ONE_SHOT: out std_logic ); end component; -- Note decoder component note_gen port ( CLK : in RST : in NOTE_IN : in DIV : out ); end component;

std_logic; std_logic; std_logic_vector(4 downto 0); std_logic_vector(15 downto 0)

Roberts, FPGA Piano Using VHDL

-- 7-Segment Display for Notes component seven_seg port ( CLK : in std_logic; RST : in std_logic; NOTE_IN : in std_logic_vector(4 downto 0); SCAN_EN : in std_logic; DIGIT : out std_logic_vector(3 downto 0); SEG : out std_logic_vector(7 downto 0) ); end component; -- Signals signal CLK after DCM and BUFG signal CLK0 from pad signal CLK_BUF after IBUF signal GND signal RST signal PB after ibufs signal digit_l MUX before obuf signal switch switches after ibufs signal led ibufs signal seg_l segment select before : std_logic; : std_logic; : std_logic; : std_logic; : std_logic; : std_logic_vector(3 downto 0); : std_logic_vector(3 downto 0); : std_logic_vector(7 downto 0); : std_logic_vector(7 downto 0); : std_logic_vector(7 downto 0); obuf. -- 50MHz clock -- 50MHz clock -- 50MHz clock

-- Pushbuttons -- 7-seg digit -- Toggle -- LEDs after -- 7-seg

signal one_mhz : std_logic; -- 1MHz Clock signal one_mhz_1 : std_logic; -- pulse with f=1 MHz created by divider signal clk_10k_1 : std_logic; -- pulse with f=10kHz created by divider signal div : std_logic_vector(15 downto 0); -- variable clock divider for loadable counter signal note_in : std_logic_vector(4 downto 0); -- output of user interface. Current Note signal note_next : std_logic_vector(4 downto 0); -- Buffer holding current Note signal note_sel : std_logic_vector(3 downto 0); -- Encoding of switches. signal div_1 : std_logic; -- 1MHz pulse signal sound : std_logic; -- Output of Loadable Clock Divider. Sent to Speaker if note is playing. signal SPK : std_logic; -- Output for Speaker fed to OBUF begin GND <= '0'; RST <= PB(0); led(1) <= RST; running.

-- push button 1 is assigned the reset -- The led "on" indicates the program is

-- Combinational logic to turn the sound on and off

Roberts, FPGA Piano Using VHDL

process (div, sound) begin if (div = x"0000") then SPK <= GND; else SPK <= sound; end if; end process; -- Speaker output SPK_OBUF_INST : OBUF port map (I=>SPK, O=>SPK_N); SPK_P <= GND; -- Input/Output Buffers loop0 : for i in 0 to 3 generate pb_ibuf : IBUF port map(I => dig_obuf : OBUF port map(I => end generate ; loop1 : for i in 0 to 7 generate swt_obuf : IBUF port map(I => led_obuf : OBUF port map(I => seg_obuf : OBUF port map(I => end generate ; -- Global Clock Buffers -- Pad -> DCM CLKIN_IBUFG_INST : IBUFG port map (I=>CLK_IN, O=>CLK0); -- DCM -> CLK CLK0_BUFG_INST : BUFG port map (I=>CLK_BUF, O=>CLK); -- DCM for Clock deskew and frequency synthesis DCM_INST : DCM port map (CLKFB=>CLK, CLKIN=>CLK0, DSSEN=>GND, PSCLK=>GND, PSEN=>GND, PSINCDEC=>GND, RST=>RST, CLKDV=>open, CLKFX=>open, CLKFX180=>open, CLK0=>CLK_BUF, CLK2X=>open, CLK2X180=>open, CLK90=>open, CLK180=>open, CLK270=>open, LOCKED=>led(0), PSDONE=>open, STATUS=>open );

pb_in(i), O => PB(i)); digit_l(i), O => digit_out(i)); switch_in(i), O => switch(i)); led(i), O => led_out(i)); seg_l(i), O => seg_out(i));

Roberts, FPGA Piano Using VHDL

-- Divide 50Mhz to 1Mhz DIV_1M : clk_dvd port map ( CLK RST DIV EN CLK_OUT ONE_SHOT );

clock => => => => => => CLK, RST, x"0019", -- 25 '1', one_mhz, one_mhz_1

-- Divide 1Mhz to Various frequencies for the notes. DIV_NOTE : clk_dvd port map ( CLK => CLK, RST => RST, DIV => div, EN => one_mhz_1, CLK_OUT => sound, ONE_SHOT => div_1 ); -- Divide 1Mhz to 10k DIV_10k : clk_dvd port map ( CLK RST DIV EN CLK_OUT ONE_SHOT );

=> => => => => =>

CLK, RST, x"0032", -- 50 one_mhz_1, open, clk_10k_1 to clock divider for 1MHz clock. CLK, RST, note_in, div

-- Translate Encoded Note note_gen_inst : note_gen port map ( CLK => RST => NOTE_IN => DIV => );

-- Wire up seven-seg controller to display current note. seven_seg_inst : seven_seg port map ( CLK => CLK, RST => RST, NOTE_IN => note_in, SCAN_EN => clk_10k_1, DIGIT => digit_l, SEG => seg_l ); -- User Interface note_in <= note_next; process (CLK,RST) begin if (RST = '1') then note_next <= (others => '0'); elsif (CLK'event and CLK = '1') then case switch is when "10000000" => note_sel <= "0001"; -- C when "01000000" => note_sel <= "0011"; -- D

Roberts, FPGA Piano Using VHDL

when "00100000" when "00010000" when "00001000" when "00000100" when "00000010" when "00000001" when others end case;

=> => => => => => =>

note_sel note_sel note_sel note_sel note_sel note_sel note_sel

<= <= <= <= <= <= <=

"0101"; "0110"; "1000"; "1010"; "1100"; "1111"; "0000";

-------

E F G A B Play a song

-- Sharp -- Add one. PB(3) is the octave key. if (switch="00000001")then note_next <= "11111"; elsif (PB(2) = '1') then note_next <= PB(3) & note_sel + 1; -- Flat -- Minus one. elsif (PB(1) = '1') then note_next <= PB(3) & note_sel - 1; else note_next <= PB(3) & note_sel; end if; end if; end process; end Behavioral; NOTE_GEN.VHD --- note_gen.vhd - FPGA Piano -library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; library UNISIM; use UNISIM.VComponents.all; -- Note Generator -This is a lookup table of the different note values. entity note_gen is port ( CLK RST NOTE_IN DIV ); end note_gen;

: : : :

in in in out

std_logic; std_logic; std_logic_vector(4 downto 0); std_logic_vector(15 downto 0)

architecture Behavioral of note_gen is signal next_div : std_logic_vector(15 downto 0); signal clk_count: std_logic_vector(31 downto 0); begin -- Latch Output of DIV process (CLK,RST) begin if (RST = '1') then

Roberts, FPGA Piano Using VHDL

DIV <= x"0000"; clk_count <= x"00000000"; elsif (CLK'event and CLK='1') then if(next_div/=x"FFFF") then DIV <= next_div; elsif(next_div=x"FFFF" and clk_count<x"2FAF080") then --50MHz/ 1 sec B4 DIV <=x"03F4"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"5F5E100") then --100MHz/ 1 sec A4 DIV <= x"0470"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"8F0D180") then --150MHz/ 1 sec F4 DIV <= x"0598"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"BEBC200") then --200MHz/ 1 sec C4 DIV <= x"0777"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"EE6B280") then --250MHz/ 1 sec B4 DIV <=x"03F4"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"11E1A300") then --300MHz/ 1 sec A4 DIV <=x"0470"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"14DC9380") then --350MHz/ 1 sec F4 DIV <=x"0598"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"17D78400") then --400MHz/ 1 sec C4 DIV <=x"0777"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"1AD27480") then --450MHz/ 1 sec C4 DIV <=x"0777"; clk_count <= clk_count+1; elsif(next_div=x"0598" and clk_count<x"1DCD6500") then --500MHz/ 1 sec F4 DIV <=x"0598"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"20C85580") then --550MHz/ 1 sec E4 DIV <=x"05ED"; clk_count <= clk_count+1; elsif(next_div=x"FFFF" and clk_count<x"26BE3680") then --650MHz/ 2 sec F4 DIV <=x"0598"; elsif(next_div=x"FFFF" and clk_count<x"E01D0C0") then -275MHz/ 2 sec clk_count <= x"00000000"; end if;

Roberts, FPGA Piano Using VHDL

end if; end process; -- Lookup Table process (NOTE_IN) begin case NOTE_IN is when "00000" => next_div <= x"0000"; when "00001" => next_div <= x"0EEE"; when "00010" => next_div <= x"0E18"; when "00011" => next_div <= x"0D4E"; when "00100" => next_div <= x"0C8E"; when "00101" => next_div <= x"0BDA"; when "00110" => next_div <= x"0B30"; when "00111" => next_div <= x"0A8E"; when "01000" => next_div <= x"09F7"; when "01001" => next_div <= x"0968"; when "01010" => next_div <= x"08E1"; when "01011" => next_div <= x"0861"; when "01100" => next_div <= x"07E9"; when "01101" => next_div <= x"0777"; when "10000" => next_div <= x"07E9"; when "10001" => next_div <= x"0777"; when "10010" => next_div <= x"070C"; when "10011" => next_div <= x"06A7"; when "10100" => next_div <= x"0647"; when "10101" => next_div <= x"05ED"; when "10110" => next_div <= x"0598"; when "10111" => next_div <= x"0547"; when "11000" => next_div <= x"04FB"; when "11001" => next_div <= x"04B4"; when "11010" => next_div <= x"0470"; when "11011" => next_div <= x"0431"; when "11100" => next_div <= x"03F4"; when "11111" => next_div <= x"FFFF"; when others => next_div <= x"0000"; end case; end process; end Behavioral; !

----------------------------

C3 C3# D3 D3# E3 F3 F3# G3 G3# A3 A3# B3 B3# = C4 C4b = B3 C4 C4# D4 D4# E4 F4 F4# G4 G4# A4 A4# B4 B4

Vous aimerez peut-être aussi

- CH11 Digital LogicDocument59 pagesCH11 Digital LogicNguyen Phuc Nam Giang (K18 HL)Pas encore d'évaluation

- Makalah Line Tracking Robot (By Opick Hidayato)Document36 pagesMakalah Line Tracking Robot (By Opick Hidayato)Opick HidayatoPas encore d'évaluation

- BN124668392Document15 pagesBN124668392Hany WijayaPas encore d'évaluation

- HW4Document4 pagesHW4April NopPas encore d'évaluation

- Matlab R2016a Final x64 Full Version - KuyhAa - Gratis Download Software & Games TerbaruDocument7 pagesMatlab R2016a Final x64 Full Version - KuyhAa - Gratis Download Software & Games Terbaruمحمد عبد شهريPas encore d'évaluation

- MARIE Assembly Language Programming Lab ReportDocument4 pagesMARIE Assembly Language Programming Lab ReportAndre F. YousiffPas encore d'évaluation

- Soal LatihanDocument2 pagesSoal LatihanGebyPas encore d'évaluation

- 8.6.1 PTDocument6 pages8.6.1 PTGeral Enrrique Navarro ReyesPas encore d'évaluation

- Chapter 5 - The Processor, Datapath and ControlDocument23 pagesChapter 5 - The Processor, Datapath and ControlBijay MishraPas encore d'évaluation

- Remote Terminal Unit ( (RTU) )Document47 pagesRemote Terminal Unit ( (RTU) )luqmankim09Pas encore d'évaluation

- ExamDocument114 pagesExamVishnu KrishnaPas encore d'évaluation

- Silabus Kurikulum TSPDocument41 pagesSilabus Kurikulum TSPHendra AntomyPas encore d'évaluation

- Embedded Sys. & Robotics WorkshopDocument5 pagesEmbedded Sys. & Robotics WorkshopPriyanka SharmaPas encore d'évaluation

- Laporan Praktikum Line CodingDocument36 pagesLaporan Praktikum Line CodingAlna Destra ShafiraPas encore d'évaluation

- Studi Model Periodik Dan Stokastik Curah Hujan Harian Untuk Mencari Data Hilang (Studi Kasus Stasiun Hujan PH.119, Danau Way Jepara, Lampung Timur)Document17 pagesStudi Model Periodik Dan Stokastik Curah Hujan Harian Untuk Mencari Data Hilang (Studi Kasus Stasiun Hujan PH.119, Danau Way Jepara, Lampung Timur)Puan AgungPas encore d'évaluation

- Makalah CPU Dan StorageDocument9 pagesMakalah CPU Dan StorageAdi SuripiyantoPas encore d'évaluation

- Laporan Praktikum Komunikasi Data 2: Damas Yusli Arfani 2 Aec 217341056Document11 pagesLaporan Praktikum Komunikasi Data 2: Damas Yusli Arfani 2 Aec 217341056Dayuar DyaPas encore d'évaluation

- MEL G642-Compre Solution - 2 2016-17Document9 pagesMEL G642-Compre Solution - 2 2016-17Gaurav PatilPas encore d'évaluation

- William Stallings Computer Organization and Architecture 9 EditionDocument61 pagesWilliam Stallings Computer Organization and Architecture 9 EditionFahmida RahmanPas encore d'évaluation

- Parallel AdderDocument20 pagesParallel AddermdbelalrshdPas encore d'évaluation

- Paper Parallel Merge SortDocument8 pagesPaper Parallel Merge SortmoginhPas encore d'évaluation

- Oscilloscope and Signal Generator in LabviewDocument9 pagesOscilloscope and Signal Generator in LabviewAli ShafiquePas encore d'évaluation

- Arduino Example - Continuous Sampling Example - Discussion Forums - National InstrumentsDocument3 pagesArduino Example - Continuous Sampling Example - Discussion Forums - National InstrumentsMihai BogdanPas encore d'évaluation

- Computer Numerical Control (G & M Codes)Document12 pagesComputer Numerical Control (G & M Codes)Iqbal NugrohoPas encore d'évaluation

- 05 - Linked List Variation - Double Linked ListDocument30 pages05 - Linked List Variation - Double Linked ListrakhaaditPas encore d'évaluation

- Offset CrankDocument1 pageOffset CrankDwi DarsonoPas encore d'évaluation

- Naruto Ultimate Ninja Storm 4 Keyboard ControlsDocument1 pageNaruto Ultimate Ninja Storm 4 Keyboard ControlsRishijeeth KoppisettiPas encore d'évaluation

- VHDL Code For Flipflop D, JK, SR, TDocument7 pagesVHDL Code For Flipflop D, JK, SR, TPeter HerreraPas encore d'évaluation

- Convolutional CodesDocument26 pagesConvolutional CodesPiyush MittalPas encore d'évaluation

- 15 Contoh Aplikasi Genetic Algorithm Dalam Dunia NyataDocument9 pages15 Contoh Aplikasi Genetic Algorithm Dalam Dunia NyataSupriyanto, M.Kom100% (1)

- Moore Mealy Machine Lecture-1Document15 pagesMoore Mealy Machine Lecture-1ali yousafPas encore d'évaluation

- 11-Khusnul Khotimah-TT2E-MEC Dan Load FigureDocument22 pages11-Khusnul Khotimah-TT2E-MEC Dan Load Figurekhusnul khotimahPas encore d'évaluation

- Introduction To Actel FPGA Architecture PDFDocument8 pagesIntroduction To Actel FPGA Architecture PDFsaipranathiPas encore d'évaluation

- Data Flow TestingDocument40 pagesData Flow Testingvinaykuk6569100% (3)

- 9 - CFG SimplificationDocument7 pages9 - CFG Simplificationعلي عبد الحمزه100% (1)

- Computer System Architecture Chapter 1 6 by M Morris ManoDocument75 pagesComputer System Architecture Chapter 1 6 by M Morris ManokrishnanandPas encore d'évaluation

- Instruction Manual For Programming The CPU SimulatorDocument10 pagesInstruction Manual For Programming The CPU Simulatorrktiwary256034Pas encore d'évaluation

- Gerbang LogikaDocument26 pagesGerbang LogikaErnesto AntonioPas encore d'évaluation

- Unit - 5Document34 pagesUnit - 5Sanjay KumarPas encore d'évaluation

- Constellation QPSKDocument5 pagesConstellation QPSKVijayanand SPas encore d'évaluation

- Week 3-Sketching Application-.Pdf - 2Document6 pagesWeek 3-Sketching Application-.Pdf - 2marlon corpuzPas encore d'évaluation

- JK FF CounterDocument1 pageJK FF Counterzero okPas encore d'évaluation

- Design and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLDocument6 pagesDesign and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLIOSRjournalPas encore d'évaluation

- A Computer May Be Defined AsDocument3 pagesA Computer May Be Defined AssonikonicaPas encore d'évaluation

- Week 5 Unit9 English For ItDocument8 pagesWeek 5 Unit9 English For Itapi-262133173Pas encore d'évaluation

- Tiger SHARC ProcessorDocument36 pagesTiger SHARC ProcessorChintan PatelPas encore d'évaluation

- Analisis Sentimen Pembelajaran Daring Menggunakan Metode Naïve Bayes, KNN, Dan Decision TreeDocument7 pagesAnalisis Sentimen Pembelajaran Daring Menggunakan Metode Naïve Bayes, KNN, Dan Decision TreeJurnal JTIK (Jurnal Teknologi Informasi dan Komunikasi)Pas encore d'évaluation

- Kogge-Stone AdderDocument6 pagesKogge-Stone AdderVijay Dhar MauryaPas encore d'évaluation

- 02 Message Passing Interface TutorialDocument34 pages02 Message Passing Interface TutorialFrederic MenezesPas encore d'évaluation

- Poset & LatticeDocument15 pagesPoset & LatticeDab ErqPas encore d'évaluation

- L 9 Timer Programming: ObjectivesDocument3 pagesL 9 Timer Programming: ObjectivesChris CastroPas encore d'évaluation

- Dspa 17ec751 M5Document34 pagesDspa 17ec751 M5digital lovePas encore d'évaluation

- Digital Design Through Verilog HDL Course Outcomes For LabDocument1 pageDigital Design Through Verilog HDL Course Outcomes For LabSyed AshmadPas encore d'évaluation

- Vlsi Verilog - Fir Filter Design Using VerilogDocument5 pagesVlsi Verilog - Fir Filter Design Using VerilogNanda KumarPas encore d'évaluation

- Verilog Basic ExperimentsDocument62 pagesVerilog Basic ExperimentsGaurav Soni0% (1)

- EX. NO: 1 Date: Implementation of Basic Logic Gates in FpgaDocument66 pagesEX. NO: 1 Date: Implementation of Basic Logic Gates in FpgaPrateek SinghPas encore d'évaluation

- Guitar Tuner With An Arduino: by EE421ACDCDocument9 pagesGuitar Tuner With An Arduino: by EE421ACDCKerem AydınPas encore d'évaluation

- PCF8591 1Document7 pagesPCF8591 1Ashesh PradhanPas encore d'évaluation

- Data Communications Using A Fiber Optic-Based SystemDocument4 pagesData Communications Using A Fiber Optic-Based Systemjasmine-rPas encore d'évaluation

- Sources of Signal Loss in Fiber-Optic Based Communication SystemsDocument3 pagesSources of Signal Loss in Fiber-Optic Based Communication Systemsjasmine-rPas encore d'évaluation

- Physical Characteristics of Optical FibersDocument7 pagesPhysical Characteristics of Optical Fibersjasmine-rPas encore d'évaluation

- Quantum Tunneling Through A BarrierDocument12 pagesQuantum Tunneling Through A Barrierjasmine-rPas encore d'évaluation

- Account of The Horsburgh LighthouseDocument135 pagesAccount of The Horsburgh LighthouseDr. ShaharilPas encore d'évaluation

- Biographical Data - Bruce K Forbes - ARCHIBUSDocument3 pagesBiographical Data - Bruce K Forbes - ARCHIBUSjancukjancukPas encore d'évaluation

- Flex LinkDocument0 pageFlex LinkMarco ViniciusPas encore d'évaluation

- Thinksystem Storage GuidebookDocument44 pagesThinksystem Storage Guidebooklawjohn73Pas encore d'évaluation

- Use of PowerShell Scripting To Automate Engineering TasksDocument14 pagesUse of PowerShell Scripting To Automate Engineering TasksnileshchordiyaPas encore d'évaluation

- TCP Optimization Through FEC, ARQ and Transmission Power TradeoffsDocument12 pagesTCP Optimization Through FEC, ARQ and Transmission Power TradeoffshelbakouryPas encore d'évaluation

- Presentation Layer & Session LayerDocument51 pagesPresentation Layer & Session LayerAnonymous fp8NP80% (1)

- Top 10 Strategic Technology Trends For 2017: A Gartner Trend Insight ReportDocument18 pagesTop 10 Strategic Technology Trends For 2017: A Gartner Trend Insight ReportpantmukulPas encore d'évaluation

- RTLS Installation Manual: Date Modified: June 4, 2014Document52 pagesRTLS Installation Manual: Date Modified: June 4, 2014Asif Belal100% (1)

- 8432123130593405Document46 pages8432123130593405Nida PatelPas encore d'évaluation

- Art AppreciationDocument3 pagesArt AppreciationJoven GonzalesPas encore d'évaluation

- FRANKFORT. The Art and Architecture of The Ancient Orient PDFDocument228 pagesFRANKFORT. The Art and Architecture of The Ancient Orient PDFErnesto Castro Cordoba100% (1)

- 365 Ais - Database.model - file.PertemuanFileContent LOGMAT 8Document32 pages365 Ais - Database.model - file.PertemuanFileContent LOGMAT 8Asep MiftahudinPas encore d'évaluation

- 5900 MRF OverviewDocument76 pages5900 MRF OverviewVilasak Itpt100% (1)

- Gprs Attach PDP Sequence DiagramDocument4 pagesGprs Attach PDP Sequence Diagramapi-3838344100% (1)

- 1-Reinforced Concrete Equations1Document5 pages1-Reinforced Concrete Equations1Mohamad DuhokiPas encore d'évaluation

- Chapter 13Document44 pagesChapter 13V.m. RajanPas encore d'évaluation

- Led LightDocument32 pagesLed LightHugo Hernandez GustherPas encore d'évaluation

- SCHEMATIC SYSTEM CHILLER PLANT 3 (MERO) - ModelDocument1 pageSCHEMATIC SYSTEM CHILLER PLANT 3 (MERO) - ModelIlham HarisPas encore d'évaluation

- Mietskaserne 1Document26 pagesMietskaserne 1Luiza Sassi100% (1)

- Ex 3 - TCP Udp Chat ServerDocument3 pagesEx 3 - TCP Udp Chat ServerrmuthusamiPas encore d'évaluation

- Theoderich's Description of The Holy Places.Document110 pagesTheoderich's Description of The Holy Places.r.figueroa.Pas encore d'évaluation

- BMCDocument89 pagesBMCAshish BPas encore d'évaluation

- BCM 6332 35 ChipDocument3 pagesBCM 6332 35 ChipHoang LePas encore d'évaluation

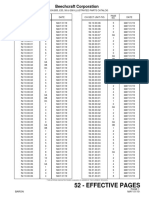

- 52 - Effective Pages: Beechcraft CorporationDocument156 pages52 - Effective Pages: Beechcraft Corporationaviacion gnaPas encore d'évaluation

- AISC Intro Steel Bridge Design r1 Handout 2perDocument67 pagesAISC Intro Steel Bridge Design r1 Handout 2perDarline Cano CardonaPas encore d'évaluation

- Quick Start GuideDocument21 pagesQuick Start GuiderameshPas encore d'évaluation

- Blue BedroomDocument1 pageBlue BedroomGwen Lyh OlegarioPas encore d'évaluation

- Bpcltenders - Eproc.in Product PublicDash ViewFlag RegisteredBiddersDetails-1-30Document30 pagesBpcltenders - Eproc.in Product PublicDash ViewFlag RegisteredBiddersDetails-1-30mmbemechPas encore d'évaluation

- Report On Book My FarmDocument25 pagesReport On Book My FarmpkPas encore d'évaluation

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsD'EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsPas encore d'évaluation

- Chip War: The Quest to Dominate the World's Most Critical TechnologyD'EverandChip War: The Quest to Dominate the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)D'EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Évaluation : 5 sur 5 étoiles5/5 (1)

- Computer Science: A Concise IntroductionD'EverandComputer Science: A Concise IntroductionÉvaluation : 4.5 sur 5 étoiles4.5/5 (14)

- Chip War: The Fight for the World's Most Critical TechnologyD'EverandChip War: The Fight for the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XD'EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XÉvaluation : 3 sur 5 étoiles3/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102D'EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Évaluation : 5 sur 5 étoiles5/5 (2)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102D'EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Pas encore d'évaluation

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesD'EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesPas encore d'évaluation

- Amazon Web Services (AWS) Interview Questions and AnswersD'EverandAmazon Web Services (AWS) Interview Questions and AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFD'EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFPas encore d'évaluation

- Programming with STM32: Getting Started with the Nucleo Board and C/C++D'EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Évaluation : 3.5 sur 5 étoiles3.5/5 (3)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxD'EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxPas encore d'évaluation

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertD'EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsD'EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesD'EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesPas encore d'évaluation

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideD'EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideÉvaluation : 1 sur 5 étoiles1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002D'EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Évaluation : 5 sur 5 étoiles5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]D'EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Évaluation : 5 sur 5 étoiles5/5 (1)

- Real-Time UML Workshop for Embedded SystemsD'EverandReal-Time UML Workshop for Embedded SystemsÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Raspberry Pi for Python Programmers Cookbook - Second EditionD'EverandRaspberry Pi for Python Programmers Cookbook - Second EditionPas encore d'évaluation

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsD'EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsPas encore d'évaluation

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XD'EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XÉvaluation : 5 sur 5 étoiles5/5 (1)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714737415?v=1)