Académique Documents

Professionnel Documents

Culture Documents

PRBS

Transféré par

shabi0904Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

PRBS

Transféré par

shabi0904Droits d'auteur :

Formats disponibles

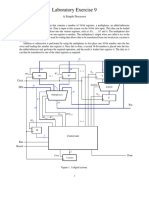

PRBS( Pseudo Random Binary Sequence Generator) VHDL Code and VHDL Testbench Creation PRBS Generator:

Pseudo random binary sequence is essentially a random sequence of binary numbers. So PRBS generator is nothing but random binary number generator. It is random in a sense that the value of an element of the sequence is independent of the values of any of the other elements. It is 'pseudo' because it is deterministic and after N elements it starts to repeat itself, unlike real random sequence The implementation of PRBS generator is based on the linear feedback shift register (LFSR). The PRBS generator produces a predefined sequence of 1's and 0's, with 1 and 0 occurring with the same probability. A sequence of consecutive n*(2^n -1) bits comprise one data pattern, and this pattern will repeat itself over time. A PRBS generator is implemented in VHDL, using LFSRs.(Linear feedback Shift Registers which is made up of D-Flip-flops).Here is an example of How it can be done using VHDL.

VHDL Code for D Flip Flop

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dff is Port ( CLK : in std_logic; RSTn : in std_logic; D : in std_logic; Q : out std_logic); end dff;

architecture Behavioral of dff is begin process(CLK) begin if CLK'event and CLK='1' then if RSTn='1' then Q <= '1'; else Q <= D; end if; end if; end process; end Behavioral;

VHDL CODE FOR PRBS Generator using LFSR:

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

entity lfsr is Port ( CLK : in STD_LOGIC; RSTn : in STD_LOGIC; data_out : out STD_LOGIC_VECTOR (15 downto 0)); end lfsr; architecture Behavioral of lfsr is component dff Port ( CLK : in std_logic; RSTn : in std_logic; D : in std_logic; Q : out std_logic); end component; signal data_reg : std_logic_vector(15 downto 0); signal tap_data : std_logic;

begin process(CLK) begin tap_data <= (data_reg(1) xor data_reg(2)) xor (data_reg(4) xor data_reg(15)); end process;

stage0: dff port map(CLK, RSTn, tap_data, data_reg(0));

g0:for i in 0 to 14 generate

stageN: dff port map(CLK, RSTn, data_reg(i), data_reg(i+1));

end generate;

data_out <= data_reg after 3 ns; end Behavioral;

VHDL Test Bench for Simulation: LIBRARY ieee; USE ieee.std_logic_1164.ALL;

ENTITY testprbs IS END testprbs; ARCHITECTURE behavior OF testprbs IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT lfsr PORT( CLK : IN std_logic; RSTn : IN std_logic; data_out : OUT std_logic_vector(15 downto 0) ); END COMPONENT; signal CLK : std_logic := '0'; signal RSTn : std_logic := '0'; signal data_out : std_logic_vector(15 downto 0); -- Clock period definitions constant CLK_period : time := 10 ns; BEGIN -- Instantiate the Unit Under Test (UUT) uut: lfsr PORT MAP ( CLK => CLK, RSTn => RSTn, data_out => data_out ); CLK_process :process begin CLK <= '0'; wait for CLK_period/2; CLK <= '1'; wait for CLK_period/2; end process;

-- Stimulus process stim_proc: process begin

wait for 10 ns; wait for CLK_period*1; RSTn <= '1'; wait for CLK_period*1; RSTn <= '0'; wait; end process; END;

Vous aimerez peut-être aussi

- To Design An Adaptive Channel Equalizer Using MATLABDocument43 pagesTo Design An Adaptive Channel Equalizer Using MATLABAngel Pushpa100% (1)

- AlexanderCh17final R1Document21 pagesAlexanderCh17final R1Salih IncePas encore d'évaluation

- Digital Signal ProcessingDocument23 pagesDigital Signal ProcessingSanjay PalPas encore d'évaluation

- Aim - Write A Program To Simulate Pure-Pursuit Problem of Continuous System Simulation. CodeDocument18 pagesAim - Write A Program To Simulate Pure-Pursuit Problem of Continuous System Simulation. CodeSK KashyapPas encore d'évaluation

- 6-A Prediction ProblemDocument31 pages6-A Prediction ProblemPrabhjot KhuranaPas encore d'évaluation

- DSP Matlab ProgramsDocument50 pagesDSP Matlab ProgramsDhiraj Thakur67% (3)

- EEE321 - Digital Signal Processing - LAB 5Document6 pagesEEE321 - Digital Signal Processing - LAB 5Tâm NguyễnPas encore d'évaluation

- 4bit ComparatorDocument7 pages4bit ComparatorDavis Spat TambongPas encore d'évaluation

- Signals and SystemsDocument72 pagesSignals and Systemsajas777BPas encore d'évaluation

- White Box SolDocument10 pagesWhite Box Solsaman0% (1)

- 7 Numerical Methods 3 Newton Raphson and Second OrderDocument19 pages7 Numerical Methods 3 Newton Raphson and Second OrderCarl PPas encore d'évaluation

- 2.2 Pushdown AutomataDocument32 pages2.2 Pushdown AutomataSuphiyan RabiuPas encore d'évaluation

- DSP Lab Manual Final Presidency UniversityDocument58 pagesDSP Lab Manual Final Presidency UniversitySUNIL KUMAR0% (1)

- Experiment 2: Aim: To Implement and Analyze Merge Sort Algorithm. TheoryDocument5 pagesExperiment 2: Aim: To Implement and Analyze Merge Sort Algorithm. Theorydeepinder singhPas encore d'évaluation

- Physical Chemistry Homework HelpDocument14 pagesPhysical Chemistry Homework HelpEdu Assignment Help100% (1)

- Unit-2 DBMSDocument28 pagesUnit-2 DBMSSiddhartha ShetyPas encore d'évaluation

- Computer OrganisationDocument71 pagesComputer OrganisationAnuragGuptaPas encore d'évaluation

- Lab-09 and 10 PDFDocument14 pagesLab-09 and 10 PDFAman RashdiPas encore d'évaluation

- Jacobi MethodDocument2 pagesJacobi MethodJuancho SotilloPas encore d'évaluation

- C Program To Implement Evaluation of Postfix Expression Using StackDocument2 pagesC Program To Implement Evaluation of Postfix Expression Using StackSaiyasodharan0% (1)

- Laboratory No. 9:: Simple Calculator (Final Lab)Document10 pagesLaboratory No. 9:: Simple Calculator (Final Lab)2017 01051Pas encore d'évaluation

- Saveetha Institute of Medical and Technical Sciences: Unit V Plotting and Regression Analysis in RDocument63 pagesSaveetha Institute of Medical and Technical Sciences: Unit V Plotting and Regression Analysis in RMuzakir Laikh KhanPas encore d'évaluation

- DSP Practical FileDocument18 pagesDSP Practical FileDivyaPas encore d'évaluation

- Department of Electrical Engineering EE365L: Communication SystemsDocument20 pagesDepartment of Electrical Engineering EE365L: Communication SystemsAbrahan ShahzadPas encore d'évaluation

- Unit Iii: Analysis of Discrete Time SignalsDocument22 pagesUnit Iii: Analysis of Discrete Time SignalsAnbazhagan SelvanathanPas encore d'évaluation

- 1 3Document59 pages1 3Anteneh AtumoPas encore d'évaluation

- Wiener Filter 1Document11 pagesWiener Filter 1Vanidevi ManiPas encore d'évaluation

- Free-Samples - Amie - Chapters - Single Stage and Multi Stage Amplifiers-Sec-B-EcDocument38 pagesFree-Samples - Amie - Chapters - Single Stage and Multi Stage Amplifiers-Sec-B-EcSivakumar PothirajPas encore d'évaluation

- Z TansformDocument65 pagesZ TansformThe Aviator00Pas encore d'évaluation

- Solution of Algebraic & Transcendental Equation: After Reading This Chapter, You Should Be Able ToDocument18 pagesSolution of Algebraic & Transcendental Equation: After Reading This Chapter, You Should Be Able ToImrul Hasan100% (1)

- Laboratory Experiment For Digital ElectronicsDocument1 pageLaboratory Experiment For Digital ElectronicsPiyush RajPas encore d'évaluation

- Data Communication and Computer Networks DCCN - Eee314: Lab 2: IP Addressing Scheme and VLSMDocument5 pagesData Communication and Computer Networks DCCN - Eee314: Lab 2: IP Addressing Scheme and VLSMUzzamPas encore d'évaluation

- Digital System Design by Using VERILOGDocument13 pagesDigital System Design by Using VERILOGkpkarthi2001Pas encore d'évaluation

- DSP Lab Sheet 2 PDFDocument50 pagesDSP Lab Sheet 2 PDFSreekrishna DasPas encore d'évaluation

- Illumination ModelDocument43 pagesIllumination ModelPradeepPas encore d'évaluation

- MExer01 FinalDocument11 pagesMExer01 Finaljohannie ukaPas encore d'évaluation

- Pushdown AutomataDocument26 pagesPushdown AutomataRavi TejaPas encore d'évaluation

- Digital ClockDocument11 pagesDigital ClockAmiin Gadari100% (4)

- Lab9 VHDLDocument8 pagesLab9 VHDLFasli CoolPas encore d'évaluation

- Experiment No-8: Write A MATLAB Program To Plot The Following FunctionDocument2 pagesExperiment No-8: Write A MATLAB Program To Plot The Following FunctionUnknown424Pas encore d'évaluation

- NS2 Simulation Using Distance Vector Routing ProtocolDocument2 pagesNS2 Simulation Using Distance Vector Routing ProtocolKavin Cavin0% (1)

- Unit-Iv: Pushdown Automata (PDA)Document9 pagesUnit-Iv: Pushdown Automata (PDA)Venkata Rao SPas encore d'évaluation

- Hardwired Control Unit: A Case-Study Report Submitted For The Requirement ofDocument23 pagesHardwired Control Unit: A Case-Study Report Submitted For The Requirement ofShinde D PoojaPas encore d'évaluation

- DSP 2 Marks Q&a1Document38 pagesDSP 2 Marks Q&a1shankarPas encore d'évaluation

- Ec8361-Adc Lab ManualDocument118 pagesEc8361-Adc Lab ManualmuminthajPas encore d'évaluation

- Unit - Iv MultivibratorsDocument41 pagesUnit - Iv MultivibratorsSanjana PulapaPas encore d'évaluation

- NMC Handout - 3Document17 pagesNMC Handout - 3NIKHIL NIKHIPas encore d'évaluation

- Mosfet 1Document33 pagesMosfet 1Palash SwarnakarPas encore d'évaluation

- Multi Resolution Based Fusion Using Discrete Wavelet Transform.Document27 pagesMulti Resolution Based Fusion Using Discrete Wavelet Transform.saranrajPas encore d'évaluation

- UNIT 3 GRAPHS Class NotesDocument24 pagesUNIT 3 GRAPHS Class NotesSUDHA SPas encore d'évaluation

- NumericalMethodsforEngineers PDFDocument160 pagesNumericalMethodsforEngineers PDFQuick TornadoPas encore d'évaluation

- OFDM and Cyclic Pre X - A Hands-On Demonstration Using MatlabDocument4 pagesOFDM and Cyclic Pre X - A Hands-On Demonstration Using MatlabzakiPas encore d'évaluation

- Lec-6-7 - Races and Cycles in ASM DesignDocument6 pagesLec-6-7 - Races and Cycles in ASM DesignShubham GuptaPas encore d'évaluation

- Digital Communication Systems: ECE-4001 TASK-3Document12 pagesDigital Communication Systems: ECE-4001 TASK-3Aniket SaxenaPas encore d'évaluation

- Vertex Cover ProblemDocument4 pagesVertex Cover ProblemB.K.MishraPas encore d'évaluation

- Elmore Delay in RC Networks: September 16, 2010Document3 pagesElmore Delay in RC Networks: September 16, 2010Siddharth SabharwalPas encore d'évaluation

- Carrera de Ingeniería Electrónica Arquitectura de ComputadoresDocument25 pagesCarrera de Ingeniería Electrónica Arquitectura de ComputadoresNatalia PoloPas encore d'évaluation

- 005 - K. C. Chang - Digital Systems - 4 A 15Document13 pages005 - K. C. Chang - Digital Systems - 4 A 15Rooster MXPas encore d'évaluation

- Async FifoDocument33 pagesAsync FifoAnuj RajPas encore d'évaluation

- Li Fi The Future Technology in Wireless CommunicationDocument4 pagesLi Fi The Future Technology in Wireless CommunicationPankajatSIBMPas encore d'évaluation

- Field Programmable Gate Array: Full Adder Implementation Using FPGADocument32 pagesField Programmable Gate Array: Full Adder Implementation Using FPGAshabi0904Pas encore d'évaluation

- Know Yourself:: Tibetan Personality TestDocument24 pagesKnow Yourself:: Tibetan Personality TestmaheshboobalanPas encore d'évaluation

- Trans JourDocument9 pagesTrans JourLorena SierraPas encore d'évaluation

- Design and Implementation of TARF A Trust-Aware Routing Framework For WSNDocument4 pagesDesign and Implementation of TARF A Trust-Aware Routing Framework For WSNJAYAPRAKASHPas encore d'évaluation

- Bookch9 Fpga - 24Document2 pagesBookch9 Fpga - 24shabi0904Pas encore d'évaluation

- Know Yourself:: Tibetan Personality TestDocument24 pagesKnow Yourself:: Tibetan Personality TestmaheshboobalanPas encore d'évaluation

- (162751105) Vlsi-1Document7 pages(162751105) Vlsi-1shabi0904Pas encore d'évaluation

- PCL Font ManualDocument30 pagesPCL Font ManualmibasurinPas encore d'évaluation

- MP 8253,54 Timer SlidesDocument30 pagesMP 8253,54 Timer SlidesAnuj GuptaPas encore d'évaluation

- Manual NortelDocument482 pagesManual NortelosePas encore d'évaluation

- File 1394536498Document8 pagesFile 1394536498ismarlinPas encore d'évaluation

- Pragmatic Odoo OpenERP Amazon AWS Platform - PragmaticDocument15 pagesPragmatic Odoo OpenERP Amazon AWS Platform - PragmaticCalvin MulaudziPas encore d'évaluation

- 1.C GS 4210 24P2Sv2 - S PDFDocument7 pages1.C GS 4210 24P2Sv2 - S PDFSathiya Priya NatrajPas encore d'évaluation

- Gaussian Minimum Shift Keying (GMSK) : Raafat Ali Supervisor: Dr. Nizar ZarkaDocument17 pagesGaussian Minimum Shift Keying (GMSK) : Raafat Ali Supervisor: Dr. Nizar ZarkahiriPas encore d'évaluation

- Cisco Premium 350-401 by - VCEplus 100q-DEMODocument45 pagesCisco Premium 350-401 by - VCEplus 100q-DEMOAran Palayan100% (1)

- Sheet 01Document5 pagesSheet 01Rania NabilPas encore d'évaluation

- IBM Cognos Analytics Getting Started GuideDocument25 pagesIBM Cognos Analytics Getting Started GuideRoger ClarkPas encore d'évaluation

- Analog Ic Layout 1 1385Document54 pagesAnalog Ic Layout 1 1385v4vktryPas encore d'évaluation

- 2.3.3.5 Lab - Configuring A Switch Management AddressDocument8 pages2.3.3.5 Lab - Configuring A Switch Management AddressNicolas Bonina33% (3)

- PCB Reverse EngineeringDocument2 pagesPCB Reverse Engineeringbill1022Pas encore d'évaluation

- Mobile Communications Technologies - EbookDocument44 pagesMobile Communications Technologies - EbookCommsbrief Limited OfficialPas encore d'évaluation

- Feedback SrsDocument8 pagesFeedback SrsVinay Vyas0% (2)

- ORACLE Section 1 Quiz AnswersDocument4 pagesORACLE Section 1 Quiz AnswersAndreea Lobontiu100% (1)

- 6236 Implementing and Maintaining Microsoft SQL Server 2008 Reporting ServicesDocument444 pages6236 Implementing and Maintaining Microsoft SQL Server 2008 Reporting Servicessportiefke84Pas encore d'évaluation

- User'S Guide Pluglink 9650-Wt-Solarlink AdapterDocument24 pagesUser'S Guide Pluglink 9650-Wt-Solarlink Adapterismael94Pas encore d'évaluation

- C++ Developer - Full DescriptionDocument2 pagesC++ Developer - Full DescriptionAshner NovillaPas encore d'évaluation

- Combo FixDocument4 pagesCombo FixAna MateiPas encore d'évaluation

- Operational Qualification TemplateDocument9 pagesOperational Qualification TemplateBhuvana RamananPas encore d'évaluation

- Introduction To FPGADocument16 pagesIntroduction To FPGAapi-19457371100% (1)

- Panel Control SystemDocument4 pagesPanel Control SystemRirin EltamaPas encore d'évaluation

- Assignment 1Document7 pagesAssignment 1Altaf KondakamaralaPas encore d'évaluation

- GSM To LTE Cell Reselection - Capitalisation - PA1Document19 pagesGSM To LTE Cell Reselection - Capitalisation - PA1narendraiit2003Pas encore d'évaluation

- Iphone: Fuzzing and Payloads: Charlie MillerDocument66 pagesIphone: Fuzzing and Payloads: Charlie MillerAndresPas encore d'évaluation

- Definition - What Does Northbound Interface (NBI) Mean?Document6 pagesDefinition - What Does Northbound Interface (NBI) Mean?Bikash बिकासPas encore d'évaluation

- Nokia 9500 MPR MPT Short-Haul R6-1 ANSI Data Sheet enDocument2 pagesNokia 9500 MPR MPT Short-Haul R6-1 ANSI Data Sheet enSiva KumarPas encore d'évaluation

- EPOX Mtherboard EP-4PGAIDocument96 pagesEPOX Mtherboard EP-4PGAIJohn PeckPas encore d'évaluation

- Test 1 SDocument2 pagesTest 1 SsaimanobhiramPas encore d'évaluation

- Python Programming For Beginners: Learn The Basics Of Python Programming (Python Crash Course, Programming for Dummies)D'EverandPython Programming For Beginners: Learn The Basics Of Python Programming (Python Crash Course, Programming for Dummies)Évaluation : 5 sur 5 étoiles5/5 (1)

- Learn Python Programming for Beginners: Best Step-by-Step Guide for Coding with Python, Great for Kids and Adults. Includes Practical Exercises on Data Analysis, Machine Learning and More.D'EverandLearn Python Programming for Beginners: Best Step-by-Step Guide for Coding with Python, Great for Kids and Adults. Includes Practical Exercises on Data Analysis, Machine Learning and More.Évaluation : 5 sur 5 étoiles5/5 (34)

- Machine Learning: The Ultimate Beginner's Guide to Learn Machine Learning, Artificial Intelligence & Neural Networks Step by StepD'EverandMachine Learning: The Ultimate Beginner's Guide to Learn Machine Learning, Artificial Intelligence & Neural Networks Step by StepÉvaluation : 4.5 sur 5 étoiles4.5/5 (19)

- Excel Essentials: A Step-by-Step Guide with Pictures for Absolute Beginners to Master the Basics and Start Using Excel with ConfidenceD'EverandExcel Essentials: A Step-by-Step Guide with Pictures for Absolute Beginners to Master the Basics and Start Using Excel with ConfidencePas encore d'évaluation

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsD'EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Clean Code: A Handbook of Agile Software CraftsmanshipD'EverandClean Code: A Handbook of Agile Software CraftsmanshipÉvaluation : 5 sur 5 étoiles5/5 (13)

- How to Make a Video Game All By Yourself: 10 steps, just you and a computerD'EverandHow to Make a Video Game All By Yourself: 10 steps, just you and a computerÉvaluation : 5 sur 5 étoiles5/5 (1)

- Grokking Algorithms: An illustrated guide for programmers and other curious peopleD'EverandGrokking Algorithms: An illustrated guide for programmers and other curious peopleÉvaluation : 4 sur 5 étoiles4/5 (16)

- Once Upon an Algorithm: How Stories Explain ComputingD'EverandOnce Upon an Algorithm: How Stories Explain ComputingÉvaluation : 4 sur 5 étoiles4/5 (43)

- Hacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.D'EverandHacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.Évaluation : 5 sur 5 étoiles5/5 (2)

- GAMEDEV: 10 Steps to Making Your First Game SuccessfulD'EverandGAMEDEV: 10 Steps to Making Your First Game SuccessfulÉvaluation : 4.5 sur 5 étoiles4.5/5 (12)

- Understanding Software: Max Kanat-Alexander on simplicity, coding, and how to suck less as a programmerD'EverandUnderstanding Software: Max Kanat-Alexander on simplicity, coding, and how to suck less as a programmerÉvaluation : 4.5 sur 5 étoiles4.5/5 (44)

- What Algorithms Want: Imagination in the Age of ComputingD'EverandWhat Algorithms Want: Imagination in the Age of ComputingÉvaluation : 3.5 sur 5 étoiles3.5/5 (41)

- The Advanced Roblox Coding Book: An Unofficial Guide, Updated Edition: Learn How to Script Games, Code Objects and Settings, and Create Your Own World!D'EverandThe Advanced Roblox Coding Book: An Unofficial Guide, Updated Edition: Learn How to Script Games, Code Objects and Settings, and Create Your Own World!Évaluation : 4.5 sur 5 étoiles4.5/5 (2)

- Software Engineering at Google: Lessons Learned from Programming Over TimeD'EverandSoftware Engineering at Google: Lessons Learned from Programming Over TimeÉvaluation : 4 sur 5 étoiles4/5 (11)

- Blockchain Basics: A Non-Technical Introduction in 25 StepsD'EverandBlockchain Basics: A Non-Technical Introduction in 25 StepsÉvaluation : 4.5 sur 5 étoiles4.5/5 (24)

- Coders at Work: Reflections on the Craft of ProgrammingD'EverandCoders at Work: Reflections on the Craft of ProgrammingÉvaluation : 4 sur 5 étoiles4/5 (151)

- Software Development: BCS Level 4 Certificate in IT study guideD'EverandSoftware Development: BCS Level 4 Certificate in IT study guideÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Blockchain: The complete guide to understanding Blockchain Technology for beginners in record timeD'EverandBlockchain: The complete guide to understanding Blockchain Technology for beginners in record timeÉvaluation : 4.5 sur 5 étoiles4.5/5 (34)