Académique Documents

Professionnel Documents

Culture Documents

A 5.8 GHZ Fully-Integrated Power Amplifier For 802.11a WLAN System

Transféré par

Ham Radio HSMMDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

A 5.8 GHZ Fully-Integrated Power Amplifier For 802.11a WLAN System

Transféré par

Ham Radio HSMMDroits d'auteur :

Formats disponibles

A 5.8 GHz Fully-Integrated Power Amplifier for 802.

11a WLAN System

G. C. Lin and Z. M. Lin

Abstract-In this paper, a 5.8 GHz fully-integrated power amplifier is designed and implemented in a 0.18-m radio frequency CMOS process. The power amplifier is formed by a cascaded class-D pre-amplifier and a class-E amplifier to drive the output power stage. The designed PA delivered an output power of 13.86 dBm with a power-added efficiency (PAE) of 20% and a power gain of 26.66 dB.

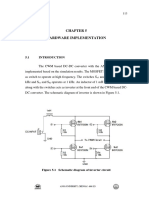

VDD LdS VdS CS LS R M1 CP

Vin

I. INTRODUCTION

Fig. 1. The growing demands for high throughput in wireless local area networks (WLANs) has generated increasing interest in the IEEE 802.1la [l] standards. This protocol provides data rates up to 54Mb/s using a 20-MHz channel bandwidth in the 5-GHz unlicensed national information infrastructure (UNII) hand. Wireless transmitters often utilize power amplifiers (PAS) as the final amplification stage. Together with the high gain provided, the nonlinear PAS also cause distortions to the input signal both in-hand and out-of-hand, which have serious impact on the communication quality. Therefore, accurate PA modeling is needed to help troubleshoot the impairments and optimize the trade-off between the efficiency and nonlinearity [2]. A tradeoff exists between efficiency and linearity in conventional switching PAs and conducting PAs. Switching PAs, such as class-D, -E, and -F are very efficient, but highly non-linear [3]. On the other hand, conducting PAs, such as class-A, -B, and -C are highly linear but are very inefficient [4]. This work investigates the feasibility of designing a class-E PA with a high gain pre-amplifier to achieve high efficient and high PAE for WLAN system. Section III presents the designed PA and points out the main design problems. Section IV presents the simulation results of the proposed PA and final conclusions are given in section V. A basic class-E stage.

II. CLASS-E OPERATION

Fig. 1 shows a class-E PA stage. The active device operates as a switch. The input signal Vin toggles the switch periodically with approximately 50% duty cycle. When the switch M1 is on, a linearly increasing current is built up through the inductor LdS. At the moment M1 is turned off, this current is steered into the capacitor CP, causing the voltage across the switch Vds to rise. The tuned network is designed such that in steady state, VdS returns to zero with a zero slope, immediately before M1 is turned on. CS and LS operates as the band-pass filter and selectively passes the fundamental component of VdS to the load, creating a sinusoidal output that is synchronized in phase and frequency with the input. In addition, the switch voltage and the switch current are never simultaneously nonzero. Since the instantaneous power dissipation of the switch is the product of these two quantities, the switch is ideally lossless, and all the power from the dc supply is delivered to the radio-frequency output.

III. CIRCUIT DESIGN

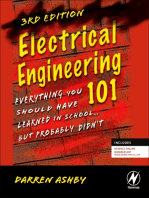

A schematic of the designed PA is shown in Fig. 2. The output stage of the power amplifier is a class-E amplifier, and the driver stage is a pre-amplifier that is composed of a cascaded class-D amplifier. A class-E stage would require a square wave driving signal that the class-D [5] chains are used in order to meet the demand. In addition, a class-D amplifier has the highest gain when the biases of the input and output are set to the mid-point between VDD and the ground.

G. C. Lin and Z. M. Lin are with the Graduate Institute of Integrated Circuit Design, National Changhua University of Education, Changhua, Taiwan, R.O.C. E-mail: zmlin@cc.ncue.edu.tw

VDD

VDD

` L3

MP1 C1 RFin L1 MN1 RF CB RF

MP2 CB RF

MP3 L2 M1 C2 C3

C4

L4 CL

MN2

MN3

Fig. 2.

Schematic of the designed PA

The input and the output of each class-D amplifier are connected through a feedback resistor RF in order to equalize the bias of the output to the bias of the input. To separate the bias of each class-D amplifier, class-D amplifiers are cascaded through dc blocking capacitors CB. By doing this, the gain degradation of each amplifier is prevented. As the output bias of the last class-D amplifier is used for the input bias of the power stage, no additional gate bias of the power transistors is needed. The transistor of each class-D amplifier is two times larger than that of the previous class-D amplifier and the size of the first one is set very small. Thus the gain of the power amplifier could be elevated. The output stage used a traditional class-E amplifier. The size of M1 is designed as large as possible in order to obtain higher output power.

IV. SIMULATION RESULTS

The performance of the PA was simulated using Advance Design System (ADS) software with 1.8V supply voltage in TMSC CMOS 0.18-m technology. Fig. 3 shows the chip layout photograph of the PA. A small-signal gain of more than 27.5 dB is simulated at 5.8 GHz, as shown in Fig. 4. The input reflection coefficient S11 and output reflection coefficient S22 are better than -14 dB over the frequency band as shown in Fig. 5. Fig. 6 shows the output power and PAE performance with a single-tone input signal. A 15.7 dBm saturated output power is achieved with a maximum PAE of 25.1%. As depicted in Fig. 7, the power gain and output power of PldB are 26.66 dB and 13.86 dBm, respectively. 20% PAE is achieved with that output power of PldB as shown in Fig. 8. Fig. 9 exhibits the total current in accordance with an output power and the power amplifier uses a low quiescent current of Class AB mode in this work. The total current of 67 mA is achieved with the output power of PldB. As shown in Fig. 10, the simulated third-order IMD which is frequency- dependent distortion is less than -42 dBc for the frequency 5.8 GHz. Table I shows the summary of the performances compared with the reported works.

Fig. 3.

Layout of the PA.

Fig. 4. Small-signal gain of the class-E power amplifier at VDD=1.8V.

Fig. 5. Input return loss and output return loss of the class-E power amplifier at VDD=1.8V.

Fig. 8 PAE versus output power.

Fig. 6.

Output power and PAE versus input power.

Fig. 9.

Supply current versus output power.

Fig. 7. Power gain versus output power.

Fig. 10. Third-order IMD corresponding to output power.

TABLE I

COMPARISON OF PA PERFORMANCE This work

[6]

[7]

[8]

Process

0.18m 0.18m 0.18m 0.18m

Frequency(GHz) Supply Voltage(V) Power Gain(dB)

1.95

5.85

5.8

3.3

1.8

3.3

1.8

25.5

15

18.5

26.66

Pout-1dB(dBm) PAE(%)

20.8

20

25

13.86

26.7

42.2

20

20

Pdiss(total)(mW) Size(mm2)

528

207

339.9

120.6

European Conference on Wireless Technology, pp. 289 292, 2004. [3] Steve Cripps, RF Power Amplifiers for Wireless Communications, Artech House, 1999, pp. 47 50. [4] Behzad Razavi, RF Microelectronics, Prentice Hall, 1998, pp. 302 313. [5] J. Jang, C. Park, H. Kim, and S. Hong, A CMOS RF Power Amplifier Using an Off-Chip Transmision Line Transformer with 62% PAE, IEEE on Microwave and Wireless Components Letters, vol. 17, pp. 385 387, May 2007. [6] H. Solar, R. Berenguer, I. Adin, U. Alvarado, and I. Cendoya, A Fully Integrated 26.5 dBm CMOS Power Amplifier for IEEE 802.11a WLAN Standard with on-chip "power inductors", IEEE MTT-S International on Microwave Symposium Digest, pp. 1875 1878, June 2006. [7] Ping-Chun Yeh, Kuei-Cheng Lin, C.Y.LEE*, and Hwann-Kaeo Chiou., A 1.8-v monolithic SiGe hbt power amplifier with a novel proposed linearizing bias circuit, 2004 IEEE Asia-Pacific Conference on Circuits and Systems, pp. 305 308, December 2004. [8] J. H. Kim, Y. S. Noh, and C. S. Park, A low quiescent current 3.3V operation linear MMIC power amplifier for 5 GHz WLAN applications, IEEE MTT-S International on Microwave Symposium Digest, pp. 867 870, June 2003.

1.1 2.2

1.4 0.8 0.9 0.9

V. CONCLUSION

A 5.8 GHz class-E CMOS PA fabricated in a TSMC 0.18um standard CMOS process with a cascaded class-D pre-amplifier for IEEE 802.11a WLAN application is presented. High gain and low quiescent current are achieved by using the cascaded class-D amplifier and the application of the proposed composition. A total power dissipation of 120.6 mW is consumed for an output power of 15.7 dBm with a maximum PAE of 25.1%. The power amplifier exhibits 26.66 dB power gain, 13.86 dBm P1dB, and 20% PAE. The third-order IMD is less than -42 dBc with the output PldB for the frequency of 5.8 GHz. ACKNOWLEDGEMENT This work was supported in part by the National Chip Implementation Center and by the National Science Council of Taiwan, R.O.C., under Grants 96-2221-E-018-024.

REFERENCES [1] Wireless LAN Medium Access Control (MAC) and Phyxicul Layer (PHY) specifications: High-speed Physical Layer in the 5 GHz Bund, IEEE Std 802.11a-1999, Sept. 1999. J. Liu, H. Arslan, L. P. Dunleavy, A. Webster, and J. Paviol, Impact of carrier frequency dependent power amplifier behavior on 802.11a WLAN system,

[2]

Vous aimerez peut-être aussi

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- Analytical Comparison of Predistorter Circuits For DS-CDMA PADocument5 pagesAnalytical Comparison of Predistorter Circuits For DS-CDMA PAInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- 10 GHz Two-stage Class A RF Power Amplifier in a 0.25 μm CMOS ProcessDocument5 pages10 GHz Two-stage Class A RF Power Amplifier in a 0.25 μm CMOS Processmdr911Pas encore d'évaluation

- Class-C Power Amplifier Design For GSM ApplicationDocument5 pagesClass-C Power Amplifier Design For GSM ApplicationJose David CastroPas encore d'évaluation

- PID2697681Document4 pagesPID2697681nguyentienduy1512Pas encore d'évaluation

- A High Efficiency Broadband Class-E Power Amplifier Using A Reactance Compensation TechniqueDocument3 pagesA High Efficiency Broadband Class-E Power Amplifier Using A Reactance Compensation Techniquegagan9385Pas encore d'évaluation

- A 2.4 GHZ Fully Integrated Cascode-Cascade Cmos Doherty Power AmplifierDocument3 pagesA 2.4 GHZ Fully Integrated Cascode-Cascade Cmos Doherty Power AmplifierMehdi ZebdiPas encore d'évaluation

- A 900Mhz RF Energy Harvesting Module: Taris Thierry, Vigneras Valérie Fadel LudivineDocument4 pagesA 900Mhz RF Energy Harvesting Module: Taris Thierry, Vigneras Valérie Fadel Ludivinekavirasu1990Pas encore d'évaluation

- Enhancing The Inefficiency of An RF Power Amp The Envelope Tracking ET SystemDocument11 pagesEnhancing The Inefficiency of An RF Power Amp The Envelope Tracking ET System张博Pas encore d'évaluation

- Design of 4 Watt Power AmplifierDocument3 pagesDesign of 4 Watt Power AmplifierTapas Sarkar100% (1)

- Class D Amplifiers: Fundamentals of Operation and Recent DevelopmentsDocument10 pagesClass D Amplifiers: Fundamentals of Operation and Recent DevelopmentsEssil ElfradiPas encore d'évaluation

- MPD CircuitDocument12 pagesMPD CircuitnanakwadwoPas encore d'évaluation

- 2P8 0911 PDFDocument3 pages2P8 0911 PDFJohn C. YoungPas encore d'évaluation

- The Design of Power Amplifier For 5.8 GHZ Wireless LAN Application Using GaAs SubstrateDocument4 pagesThe Design of Power Amplifier For 5.8 GHZ Wireless LAN Application Using GaAs SubstrateHam Radio HSMMPas encore d'évaluation

- A Linear Programmable Gain Amplifier For Biomedical ApplicationsDocument4 pagesA Linear Programmable Gain Amplifier For Biomedical ApplicationsInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- P M D-A A: Martin Pospisilik, Jiri Kasacek, Michaela Mikulicova, Milan AdamekDocument6 pagesP M D-A A: Martin Pospisilik, Jiri Kasacek, Michaela Mikulicova, Milan Adamekisauro yardani altamiranda martinezPas encore d'évaluation

- A Fully Integrated 3.5GHz Single Chip GaN Doherty PA For Sub-6GHz 5GDocument14 pagesA Fully Integrated 3.5GHz Single Chip GaN Doherty PA For Sub-6GHz 5GOscar StewardPas encore d'évaluation

- Efficient Audio Power AmplificationDocument10 pagesEfficient Audio Power AmplificationvmsaPas encore d'évaluation

- Analog Isolation D AmpDocument7 pagesAnalog Isolation D AmpDirceu Rodrigues JrPas encore d'évaluation

- A High Gain, Fully Differential Single Stage Folded Cascade Op-Amp With 1GHZ BandwidthDocument5 pagesA High Gain, Fully Differential Single Stage Folded Cascade Op-Amp With 1GHZ BandwidthJournal of Telecommunications0% (1)

- Low Noise Power Amplifier Circuit Design For 5Ghz To 6 GHZDocument4 pagesLow Noise Power Amplifier Circuit Design For 5Ghz To 6 GHZisma8070% (1)

- RF Harvesting EnergyDocument4 pagesRF Harvesting EnergyIvar JmPas encore d'évaluation

- Pulse-Density Modulation For RF Applications: The Radio-Frequency Power Amplifier (RF PA) As A Power ConverterDocument6 pagesPulse-Density Modulation For RF Applications: The Radio-Frequency Power Amplifier (RF PA) As A Power ConverteriMiklaePas encore d'évaluation

- What Is PWM and Why Is It UsefulDocument4 pagesWhat Is PWM and Why Is It UsefulBagus HarperPas encore d'évaluation

- ClasssA AmpDocument7 pagesClasssA AmpRamPas encore d'évaluation

- Design of Fully Integrated Digitally Controlled CMOS Voltage AmplifierDocument10 pagesDesign of Fully Integrated Digitally Controlled CMOS Voltage AmplifierHarsh GuptaPas encore d'évaluation

- HFE0111 FirasDocument6 pagesHFE0111 Firaschiase83Pas encore d'évaluation

- A 0.2-2.6 GHZ Wideband Noise-ReductionDocument3 pagesA 0.2-2.6 GHZ Wideband Noise-ReductionMohammad MousavikPas encore d'évaluation

- 4 Glynn and Devlin An X Band Gan Pa Mmic For PDocument8 pages4 Glynn and Devlin An X Band Gan Pa Mmic For PRAJAPas encore d'évaluation

- The Design and Simulation of 2.294dB Noise-Figure RF Wideband PHEMT LNA Employing 2-Stage Cascade With Single FeedbackDocument7 pagesThe Design and Simulation of 2.294dB Noise-Figure RF Wideband PHEMT LNA Employing 2-Stage Cascade With Single FeedbackPaul ShinePas encore d'évaluation

- A Fully Matched Ku-Band 9W PHEMT MMIC High Power AmplifierDocument4 pagesA Fully Matched Ku-Band 9W PHEMT MMIC High Power Amplifierln zPas encore d'évaluation

- Design of 2 4 GHZ Mmic Feed Forward AmplDocument7 pagesDesign of 2 4 GHZ Mmic Feed Forward AmplYAAKOV SOLOMONPas encore d'évaluation

- 12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionDocument11 pages12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionOz Heat86% (7)

- Clas E Inductor Amplifeir PDFDocument7 pagesClas E Inductor Amplifeir PDFHoracio Dorantes ReyesPas encore d'évaluation

- Power Amplifier Application NoteDocument3 pagesPower Amplifier Application NoteSanthos KumarPas encore d'évaluation

- Doherty PA 2012Document7 pagesDoherty PA 2012Saad MohsinPas encore d'évaluation

- A 2.4 GHZ Gaas-Hbt Class-E Mmic Amplifier With 65% PaeDocument4 pagesA 2.4 GHZ Gaas-Hbt Class-E Mmic Amplifier With 65% PaeKevin Dany100% (1)

- A 10-Ghz High-Efficiency Active Antenna Sub-ArrayDocument4 pagesA 10-Ghz High-Efficiency Active Antenna Sub-Arraysuzzi16Pas encore d'évaluation

- A Digital Envelope Modulator For A WLAN OFDM Polar Transmitter in 90 NM CMOSDocument8 pagesA Digital Envelope Modulator For A WLAN OFDM Polar Transmitter in 90 NM CMOSSaidatul IzyaniePas encore d'évaluation

- Class D Com FonteDocument29 pagesClass D Com FontenicchioPas encore d'évaluation

- 665 PA - NotesDocument31 pages665 PA - Notesthap_dinhPas encore d'évaluation

- Expt 6Document3 pagesExpt 6sabitavabiPas encore d'évaluation

- An1028 PDFDocument2 pagesAn1028 PDFkuazu100% (1)

- 118A GaN HEMT Class AB RF Power AmplifierDocument4 pages118A GaN HEMT Class AB RF Power AmplifierNarasimha SunchuPas encore d'évaluation

- Low Power Cmos VgaDocument7 pagesLow Power Cmos VgaMohammad Ayatullah MaktoomPas encore d'évaluation

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADocument4 pagesA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghPas encore d'évaluation

- 130nm CMOS Technology Design of Passive UHF RFID Tag inDocument4 pages130nm CMOS Technology Design of Passive UHF RFID Tag inDuc DucPas encore d'évaluation

- Power Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationDocument5 pagesPower Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationM APas encore d'évaluation

- CN0216Document5 pagesCN0216Ram VillaPas encore d'évaluation

- Design of The High-Performance RF TX IEEE 802.11ax PDFDocument3 pagesDesign of The High-Performance RF TX IEEE 802.11ax PDFMerlin Gilbert RajPas encore d'évaluation

- A 45 DB Variable Gain Low Noise MMIC AmplifierDocument4 pagesA 45 DB Variable Gain Low Noise MMIC AmplifierutilitytrackPas encore d'évaluation

- A 0.32μW, 76.8 DB SNDR Programmable GainDocument6 pagesA 0.32μW, 76.8 DB SNDR Programmable GainRajeePas encore d'évaluation

- Eect6326 Final ProjectDocument17 pagesEect6326 Final ProjectsrikanthPas encore d'évaluation

- AN282 Systemizing RF Power Amplifier DesignDocument6 pagesAN282 Systemizing RF Power Amplifier DesignfahkingmoronPas encore d'évaluation

- BD Class D ModulationDocument18 pagesBD Class D ModulationDiego Cowes100% (1)

- A 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSDocument4 pagesA 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSThanos van RamPas encore d'évaluation

- Hardware Implementation: A1 A2 b1 b2Document19 pagesHardware Implementation: A1 A2 b1 b2Santhosh KumarPas encore d'évaluation

- 3 Design and Simulation of First Order Sigma-Delta ModulatorDocument4 pages3 Design and Simulation of First Order Sigma-Delta Modulatorlim hyPas encore d'évaluation

- Positive FeedbackDocument4 pagesPositive FeedbackAmir Baghi RahinPas encore d'évaluation

- AREDN A High Speed Data NetworkDocument5 pagesAREDN A High Speed Data NetworkHam Radio HSMMPas encore d'évaluation

- Ath9k and Ath9k - HTC DebuggingDocument4 pagesAth9k and Ath9k - HTC DebuggingHam Radio HSMMPas encore d'évaluation

- Mesh Networking and AREDNDocument5 pagesMesh Networking and AREDNHam Radio HSMMPas encore d'évaluation

- The Design of Power Amplifier For 5.8 GHZ Wireless LAN Application Using GaAs SubstrateDocument4 pagesThe Design of Power Amplifier For 5.8 GHZ Wireless LAN Application Using GaAs SubstrateHam Radio HSMMPas encore d'évaluation

- Fully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsDocument4 pagesFully Integrated Doherty Power Amplifiers For 5 GHZ Wireless-LANsHam Radio HSMMPas encore d'évaluation

- MKG-0906-AR92xx MFG GuideDocument66 pagesMKG-0906-AR92xx MFG GuideHam Radio HSMMPas encore d'évaluation

- AR93xx ART2 Reference Guide MKG-15527Document140 pagesAR93xx ART2 Reference Guide MKG-15527Ham Radio HSMMPas encore d'évaluation

- MKG 0375 AR92xxEEPROMDocument52 pagesMKG 0375 AR92xxEEPROMHam Radio HSMM100% (1)

- Atheros CalibrationDocument26 pagesAtheros CalibrationHam Radio HSMMPas encore d'évaluation

- Atheros Client Utility Help: Model AR5BMB5Document30 pagesAtheros Client Utility Help: Model AR5BMB5Ham Radio HSMMPas encore d'évaluation

- RFHandbookDocument210 pagesRFHandbookvidu100% (2)

- Switchless Bi-Directional AmplifierDocument4 pagesSwitchless Bi-Directional AmplifierHam Radio HSMMPas encore d'évaluation

- MKG 1194 ARTReferenceDocument40 pagesMKG 1194 ARTReferenceHam Radio HSMMPas encore d'évaluation

- High-Speed Multimedia Goes Beyond The Linksys WRT54GDocument1 pageHigh-Speed Multimedia Goes Beyond The Linksys WRT54GHam Radio HSMMPas encore d'évaluation

- Switch Less Bidirectional RF Amplifier For 2.4 GHZ Wireless Sensor NetworksDocument7 pagesSwitch Less Bidirectional RF Amplifier For 2.4 GHZ Wireless Sensor NetworksHam Radio HSMMPas encore d'évaluation

- IJMNDI Emergency Router 27626Document10 pagesIJMNDI Emergency Router 27626Ham Radio HSMMPas encore d'évaluation

- ANT APE4518R19v06 2333 DatasheetDocument2 pagesANT APE4518R19v06 2333 Datasheetluciano100% (1)

- Schematich Acer - E5-473 - A4WAB - LA-C341P - r10Document57 pagesSchematich Acer - E5-473 - A4WAB - LA-C341P - r10Double Helix100% (1)

- 2551 Blind Rev 17 English ManualDocument16 pages2551 Blind Rev 17 English ManualKadek Dwi PermanaPas encore d'évaluation

- Optocouplers Cross Reference PDFDocument3 pagesOptocouplers Cross Reference PDFJose BenavidesPas encore d'évaluation

- KSTAR Utility System Solution 2023Document10 pagesKSTAR Utility System Solution 2023Sid-Ali RatniPas encore d'évaluation

- 02 SEP671 REL670 Exercise 1 Distance Protection CharacteristicsDocument26 pages02 SEP671 REL670 Exercise 1 Distance Protection CharacteristicsMarcos Casanova LopezPas encore d'évaluation

- SRP3200-3200SS EnglishDocument68 pagesSRP3200-3200SS EnglishAlexander VillanuevaPas encore d'évaluation

- Ac To DC Converter Project ReportDocument75 pagesAc To DC Converter Project ReportPranav Tripathi79% (14)

- DM3600 - DM3601 VHF-UHF1-UHF2 Datasheet in English LanguageDocument2 pagesDM3600 - DM3601 VHF-UHF1-UHF2 Datasheet in English LanguageAlan AdnanPas encore d'évaluation

- Mxyxyzy DatasheetDocument6 pagesMxyxyzy DatasheetJosePas encore d'évaluation

- Catalogo Xecro 2011-v21.2Document136 pagesCatalogo Xecro 2011-v21.2Tomás GPas encore d'évaluation

- Education: Professional ProfileDocument1 pageEducation: Professional ProfileAditya PandeyPas encore d'évaluation

- Manual Osciloscopio DS138Document4 pagesManual Osciloscopio DS138modeloeconomicoPas encore d'évaluation

- Ashwoods Battery Management SystemDocument6 pagesAshwoods Battery Management SystemChittaranjan BaralPas encore d'évaluation

- RPMAC Cooling Tower MotionDocument58 pagesRPMAC Cooling Tower Motionmridu ranjanPas encore d'évaluation

- 80p248477linuxandroidpmicchargersoftwareuserguide 1848228326 PDFDocument47 pages80p248477linuxandroidpmicchargersoftwareuserguide 1848228326 PDFAdhiezzz GamingPas encore d'évaluation

- Relay Interlocking (Metal - Carbon Relays)Document276 pagesRelay Interlocking (Metal - Carbon Relays)Aaditya PrakashPas encore d'évaluation

- User Manual: UPS ON LINE EA900 G4 (1-1) 6 - 10 KVADocument44 pagesUser Manual: UPS ON LINE EA900 G4 (1-1) 6 - 10 KVArabia akramPas encore d'évaluation

- Application of DC Shunt MotorsDocument6 pagesApplication of DC Shunt MotorsMatthew Freeman100% (1)

- Reliable Performance, Reduced Labour Stress and Less Work: Delaval Milking Point Mp300Document4 pagesReliable Performance, Reduced Labour Stress and Less Work: Delaval Milking Point Mp300toula88Pas encore d'évaluation

- CR 1010 KgjaehqqeDocument12 pagesCR 1010 KgjaehqqeFernando GómezPas encore d'évaluation

- Final Year Project Group 9Document54 pagesFinal Year Project Group 9lalisaa margaaPas encore d'évaluation

- IPC 4552 Cuprins - ENIG PDFDocument3 pagesIPC 4552 Cuprins - ENIG PDFMarlon CornejoPas encore d'évaluation

- Startup Giude MVS-3000Document59 pagesStartup Giude MVS-3000Christian Stevanus50% (2)

- Sepic Converter: Prepared ByDocument30 pagesSepic Converter: Prepared BychaitanyaPas encore d'évaluation

- Ligo System Installation Guide V3 Newestpage 1 of 14Document14 pagesLigo System Installation Guide V3 Newestpage 1 of 14ZzzdddPas encore d'évaluation

- Walker 7070Document2 pagesWalker 7070bobPas encore d'évaluation

- Central PBXDocument540 pagesCentral PBXHernan SaprodPas encore d'évaluation

- Motorola Gp68 Users ManualDocument44 pagesMotorola Gp68 Users ManualStivy Sarmiento BolañoPas encore d'évaluation

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionD'EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionÉvaluation : 4.5 sur 5 étoiles4.5/5 (543)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersD'Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersÉvaluation : 5 sur 5 étoiles5/5 (1)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tD'EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tÉvaluation : 4.5 sur 5 étoiles4.5/5 (27)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionD'EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionÉvaluation : 4 sur 5 étoiles4/5 (331)

- The Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidenceD'EverandThe Journeyman Electrician Exam Study Guide: Proven Methods for Successfully Passing the Journeyman Electrician Exam with ConfidencePas encore d'évaluation

- Arduino and Raspberry Pi Sensor Projects for the Evil GeniusD'EverandArduino and Raspberry Pi Sensor Projects for the Evil GeniusPas encore d'évaluation

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonD'EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonÉvaluation : 5 sur 5 étoiles5/5 (2)

- A Mind at Play: How Claude Shannon Invented the Information AgeD'EverandA Mind at Play: How Claude Shannon Invented the Information AgeÉvaluation : 4 sur 5 étoiles4/5 (53)

- Foundations of Western Civilization II: A History of the Modern Western World (Transcript)D'EverandFoundations of Western Civilization II: A History of the Modern Western World (Transcript)Évaluation : 4.5 sur 5 étoiles4.5/5 (12)

- Practical Troubleshooting of Electrical Equipment and Control CircuitsD'EverandPractical Troubleshooting of Electrical Equipment and Control CircuitsÉvaluation : 4 sur 5 étoiles4/5 (5)

- The Fast Track to Your Extra Class Ham Radio License: Covers All FCC Amateur Extra Class Exam Questions July 1, 2020 Through June 30, 2024D'EverandThe Fast Track to Your Extra Class Ham Radio License: Covers All FCC Amateur Extra Class Exam Questions July 1, 2020 Through June 30, 2024Pas encore d'évaluation

- The Homeowner's DIY Guide to Electrical WiringD'EverandThe Homeowner's DIY Guide to Electrical WiringÉvaluation : 5 sur 5 étoiles5/5 (2)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeD'EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeÉvaluation : 4.5 sur 5 étoiles4.5/5 (10)

- Beginner's Guide to Reading Schematics, Fourth EditionD'EverandBeginner's Guide to Reading Schematics, Fourth EditionÉvaluation : 3.5 sur 5 étoiles3.5/5 (10)

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialD'EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialÉvaluation : 3.5 sur 5 étoiles3.5/5 (3)

- Guide to the IET Wiring Regulations: IET Wiring Regulations (BS 7671:2008 incorporating Amendment No 1:2011)D'EverandGuide to the IET Wiring Regulations: IET Wiring Regulations (BS 7671:2008 incorporating Amendment No 1:2011)Évaluation : 4 sur 5 étoiles4/5 (2)

- Empires of Light: Edison, Tesla, Westinghouse, and the Race to Electrify the WorldD'EverandEmpires of Light: Edison, Tesla, Westinghouse, and the Race to Electrify the WorldÉvaluation : 4 sur 5 étoiles4/5 (87)

- Off-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemD'EverandOff-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemPas encore d'évaluation

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsD'EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Retro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsD'EverandRetro Gaming with Raspberry Pi: Nearly 200 Pages of Video Game ProjectsPas encore d'évaluation

- Multiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...D'EverandMultiplexed Networks for Embedded Systems: CAN, LIN, FlexRay, Safe-by-Wire...Pas encore d'évaluation