Académique Documents

Professionnel Documents

Culture Documents

CIrcuitos Secuenciales

Transféré par

Jasmany FaritTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

CIrcuitos Secuenciales

Transféré par

Jasmany FaritDroits d'auteur :

Formats disponibles

Prctica 6.

Circuitos Secuenciales

1

Prctica 6. Circuitos Secuenciales

I. Ejercicios tericos

1. Dar las salidas (Q e inverso de Q) del cronograma de la figura

1 correspondiente al biestable R-S sncrono activado por nivel

alto.

Figura 1. Cronograma de una R-S sncrono

2. Dar las salidas del cronograma de la figura 2 correspondiente

al biestable D asncrono.

Figura 2. Cronograma de un biestable D asncrono

3. Dar las salidas del cronograma de la figura 3 correspondiente

al biestable J-K asncrono.

Figura 3. Cronograma de un biestable J-k asncrono

4. Completar el cronograma de la figura 5 que corresponde al

circuito de la figura 4 y que se comporta como un biestable D

Prctica 6. Circuitos Secuenciales

2

realizado con un CI 7476 que no es ms que un biestable J-K tipo

Master-Slave.

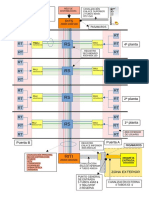

Figura 4. Biestable D implementado

con un biestable J-K C.I. 7476

Figura 5. Cronograma correspondiente

a la figura 4

5. Si a un biestable D del tipo 7474 se le introducen las seales

del cronograma siguiente, completar el cronograma obteniendo

las seales de salida.

Figura 6. Cronograma de funcionamiento del biestable D tipo 7474

6. Dado el siguiente cronograma, que corresponde a un biestable

comercial, obtener su tabla de funcionamiento e indicar su

funcin. De qu circuito integrado se trata?

Figura 7. Cronograma correspondiente al biestable X-Y

Prctica 6. Circuitos Secuenciales

3

7. Representar el cronograma y tabla de verdad correspondiente

a un biestable D activado por nivel bajo. La entrada del clock o

reloj es una seal cuadrada con frecuencia y amplitud constante.

II. Ejercicios prcticos

1. Dar el diseo lgico, tabla de verdad, cronograma de la figura

8 y montaje del R-S asncrono con puertas NOR.

Figura 8. Cronograma del biestable R-S

2. Dar el diseo lgico, tabla de verdad y montaje del R-S

asncrono con puertas NAND.

3. Dar el diseo lgico, tabla de verdad y montaje del J-K

asncrono con puertas lgicas de la figura 9.

Figura 9. Biestable J-K asncrono con puertas lgicas

4. Dar el diseo lgico, tabla de verdad, cronograma de la figura

1 y montaje de un R-S sncrono activado por nivel alto.

Prctica 6. Circuitos Secuenciales

4

Comprobar si el cronograma obtenido coincide con el obtenido

en el ejercicio 1 de la parte de ejercicios tericos.

5. Dar el diseo lgico, tabla de verdad, cronograma de la figura

6 y montaje de un biestable D sncrono activado a nivel alto

con puertas lgicas. Comprobar si el cronograma obtenido

coincide con el obtenido en el ejercicio 5 de la parte de

ejercicios tericos

6. Dar el diseo lgico, tabla de verdad, cronograma de la figura

10 y montaje de un biestable D sncrono activado por flanco

ascendente con puertas lgicas e incluir adems para el clock

el montaje de un antirrobote.

Figura 10. Cronograma del biestable D sncrono

7. Dar el diseo lgico, tabla de verdad y montaje de un

biestable J-K sincronizado por flanco maestro-esclavo con

puertas lgicas.

8. Montar con el integrado 7474 de la familia TTL el biestable D y

dar su tabla de verdad (realizar el montaje del antirrebote

para el clock).

Tabla 1. Tabla de verdad del biestable D

Entradas Salida

CLR PR CLK D Q

T

1 1 X 0

1 1 X 1

0 1 X X

1 0 X X

Prctica 6. Circuitos Secuenciales

5

9. Dar el diseo lgico, tabla de verdad y montaje de un J-K

sincronizado por flanco de bajada con el circuito integrado

74LS76 (realizar el montaje del antirrebote para el clock).

Entradas Salidas

PR CLR J K CK Q

T-1

Q

T

1 1 0 0 0

1 1 0 0 1

1 1 0 1 0

1 1 0 1 1

1 1 1 0 0

1 1 1 0 1

1 1 1 1 0

1 1 1 1 1

0 1 X X X X

1 0 X X X X

0 0 X X X X

Tabla 2. Tabla de verdad del biestable J-K sincronizado por flanco

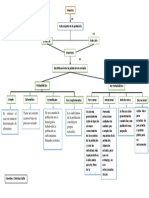

10. Obtener la tabla de verdad del circuito de la figura 11,

analizando todos los posibles valores que pueden darse en las

entradas X, Y y Q

t-1

. Comprobar si corresponde a alguno de

los biestables que se han estudiado en este tema.

Figura 11. Tabla de verdad y esquema lgico del biestable X-Y

Prctica 6. Circuitos Secuenciales

6

11. Montar el biestable de la figura 12 correspondiente a un J-K

sincronizado por nivel y dar su tabla de verdad.

Tabla 3. Tabla de verdad del biestable

J-K

Figura 12. Esquema lgico del

biestable J-K sincronizado por nivel

12. Suponiendo que la entrada del circuito de la figura 13 se le

introducen una serie de impulsos de frecuencia y amplitud

constante, realizar el cronograma de tiempos de para cada

una de las salidas.

Figura 13. Diseo lgico del problema 12.

Prctica 6. Circuitos Secuenciales

7

13. Construir un biestable J-K asncrono a partir de una bscula

R-S con puertas NOR.

Vous aimerez peut-être aussi

- BiestablesDocument8 pagesBiestablesanon_251086732Pas encore d'évaluation

- Ejercicios PDFDocument3 pagesEjercicios PDFpedrotoledoPas encore d'évaluation

- Segurola Martinez Arkaitz AI05 Tarea5.2Document5 pagesSegurola Martinez Arkaitz AI05 Tarea5.2Arkaitz Segurola MartinezPas encore d'évaluation

- Examen Resuelto PDFDocument10 pagesExamen Resuelto PDFAntonio MoyaPas encore d'évaluation

- Tramits Legalitzar Instalacion BT EspañaDocument24 pagesTramits Legalitzar Instalacion BT Españawildor01Pas encore d'évaluation

- CO KNX 002 Manual UsuarioDocument13 pagesCO KNX 002 Manual UsuarioDaniel EspinozaPas encore d'évaluation

- Manual X10Document54 pagesManual X10Catalin GhicPas encore d'évaluation

- Iei Tarea5.1Document11 pagesIei Tarea5.1Luis AlvarezPas encore d'évaluation

- Tarea 2.1Document2 pagesTarea 2.1Jarvi gil100% (3)

- Tema 1 Domótica Con El PLC S7-200Document11 pagesTema 1 Domótica Con El PLC S7-200victor_torresPas encore d'évaluation

- Examen 2020Document5 pagesExamen 2020Juan Vega GallegoPas encore d'évaluation

- Problemas Prevision Potencia IEBDocument5 pagesProblemas Prevision Potencia IEBpili gema AvilaPas encore d'évaluation

- Distribucion IIDocument62 pagesDistribucion IIgupazin75gmailPas encore d'évaluation

- Unidad8 Actividad12 PDFDocument151 pagesUnidad8 Actividad12 PDFsepiaaaaPas encore d'évaluation

- Ejercicios ICT Actividad 9 Álvaro GarcíaDocument6 pagesEjercicios ICT Actividad 9 Álvaro GarcíaAlejandro Muñoz LópezPas encore d'évaluation

- Problemas Diseño Combinacionales PDFDocument7 pagesProblemas Diseño Combinacionales PDFXiomaraPas encore d'évaluation

- K8dgn983cdtjmu834clm20gbcehkn6t31e9q20c1h PDFDocument29 pagesK8dgn983cdtjmu834clm20gbcehkn6t31e9q20c1h PDFEDWI CORTESNPas encore d'évaluation

- E TAREA7.1 Luis Alvarez Zhinin PDFDocument2 pagesE TAREA7.1 Luis Alvarez Zhinin PDFLuis AlvarezPas encore d'évaluation

- Iei05 Tarea1Document6 pagesIei05 Tarea1Javier LanserosPas encore d'évaluation

- BBBBBDocument11 pagesBBBBBcobra1962Pas encore d'évaluation

- Actividades 5.1Document7 pagesActividades 5.1Raul Pasamar SanchezPas encore d'évaluation

- Practicas x10Document8 pagesPracticas x10MasterHackero /Tu canal de hacks de juegos/Pas encore d'évaluation

- Esquema PrácticaDocument1 pageEsquema PrácticaJuan Antonio Lázaro Gámez100% (1)

- Ejercicio 3Document11 pagesEjercicio 3Michael Chuquiruna MuñozPas encore d'évaluation

- Iei01 - Tarea - 1.1 - DAVID LORENZO DOMINGUEZDocument7 pagesIei01 - Tarea - 1.1 - DAVID LORENZO DOMINGUEZdavidPas encore d'évaluation

- BOBINADODocument8 pagesBOBINADOBrandon Mamani BlancoPas encore d'évaluation

- Diseño de Una Red de Cableado EstructuradoDocument5 pagesDiseño de Una Red de Cableado EstructuradoJose Luis GraneroPas encore d'évaluation

- Manual x10 Aw12Document6 pagesManual x10 Aw12Juan Andrade TasendePas encore d'évaluation

- TEMA 3 Automatismos Cableados - EsquemasDocument14 pagesTEMA 3 Automatismos Cableados - EsquemasTed MoranPas encore d'évaluation

- EIE 02 Tarea2Document2 pagesEIE 02 Tarea2chefiPas encore d'évaluation

- Ejercicios Sistemas de Arranque Motores EléctricosDocument2 pagesEjercicios Sistemas de Arranque Motores EléctricosNickPas encore d'évaluation

- Iei02 Tarea2Document12 pagesIei02 Tarea2miuv100% (1)

- Resolver PROB DE TRAFO OJO 1Document3 pagesResolver PROB DE TRAFO OJO 1Victoria BaptistaPas encore d'évaluation

- Ict01 Tarea02 CarlosalbertocastroplataDocument8 pagesIct01 Tarea02 CarlosalbertocastroplataCarlos Alberto Castro PlataPas encore d'évaluation

- U6 Actividades ICTDocument2 pagesU6 Actividades ICTtxoskePas encore d'évaluation

- Calculos de Ganancia de AmplificadoresDocument8 pagesCalculos de Ganancia de AmplificadoresFrancisco CastilloPas encore d'évaluation

- ICTV04. - Componentes de Las Instalaciones de RTV en Edificios Destinados A Viviendas...Document102 pagesICTV04. - Componentes de Las Instalaciones de RTV en Edificios Destinados A Viviendas...MikelPas encore d'évaluation

- U10 Test ICTDocument2 pagesU10 Test ICTtxoskePas encore d'évaluation

- Examen Final MF - 0825 - 2 29 de Octubre 2015Document4 pagesExamen Final MF - 0825 - 2 29 de Octubre 2015enriquePas encore d'évaluation

- Iei Tarea3.1instalación InteriorDocument10 pagesIei Tarea3.1instalación InteriorLuis AlvarezPas encore d'évaluation

- Manual de Usuario Variador Omron 3g3mx2Document27 pagesManual de Usuario Variador Omron 3g3mx2Juan Felipe Barreto VivasPas encore d'évaluation

- Ict - Tarea 6 U2 y U3 - 2ieaDocument4 pagesIct - Tarea 6 U2 y U3 - 2ieaHamza GadourPas encore d'évaluation

- Unidad 5 Domo Eric Rogel PDFDocument10 pagesUnidad 5 Domo Eric Rogel PDFChristian De LeónPas encore d'évaluation

- Iei02 Tarea1Document9 pagesIei02 Tarea1miuv100% (2)

- Análisis de La Hoja de Características de Un Decodificador 7447Document2 pagesAnálisis de La Hoja de Características de Un Decodificador 7447Roberto PiñeiroPas encore d'évaluation

- CalculoRTV ICT2Document13 pagesCalculoRTV ICT2Jose PascualPas encore d'évaluation

- Autómatas ProgramablesDocument6 pagesAutómatas ProgramablesaquiumPas encore d'évaluation

- Modulo IV Respuesta en FrecuenciaDocument40 pagesModulo IV Respuesta en FrecuenciaEdison Valbuena MorenoPas encore d'évaluation

- Tarea 7Document6 pagesTarea 7Francisco CastilloPas encore d'évaluation

- Manual de Instalacion TDA30Document412 pagesManual de Instalacion TDA30miltonsan83Pas encore d'évaluation

- Caracteristicas de Conexion de CompuertasDocument6 pagesCaracteristicas de Conexion de CompuertasArthur Thony LtgPas encore d'évaluation

- Examen Tema 3 DomoticaDocument5 pagesExamen Tema 3 DomoticaPepePas encore d'évaluation

- 5 El Diodo Zener EstabilizacionDocument13 pages5 El Diodo Zener EstabilizacionМигель КастижоPas encore d'évaluation

- Trabajo DiodosDocument18 pagesTrabajo DiodosDiego J García SPas encore d'évaluation

- Electronica Circuitos Contadores DigitalesDocument6 pagesElectronica Circuitos Contadores Digitalescaan121Pas encore d'évaluation

- Circuitos Contadores PDFDocument6 pagesCircuitos Contadores PDFWilson Apaza YucraPas encore d'évaluation

- Circuitos Contadores PDFDocument6 pagesCircuitos Contadores PDFmars1972100% (1)

- Flip FlopsDocument47 pagesFlip FlopssbuesoPas encore d'évaluation

- LAB 4 - U5a Bàsculas y Flip Flops ANDO - 04abr18Document1 pageLAB 4 - U5a Bàsculas y Flip Flops ANDO - 04abr18MatíasPas encore d'évaluation

- Practica SecuencialesDocument23 pagesPractica SecuencialesJimmy MartinezPas encore d'évaluation

- Practica de Programacion en EnsambladorDocument43 pagesPractica de Programacion en EnsambladorJasmany FaritPas encore d'évaluation

- Arbol de ProblemasDocument1 pageArbol de ProblemasJasmany FaritPas encore d'évaluation

- Ejercicios de Mapas de KarnaughDocument1 pageEjercicios de Mapas de KarnaughJasmany FaritPas encore d'évaluation

- Lab 5 Digital 1 06062013Document6 pagesLab 5 Digital 1 06062013Jasmany FaritPas encore d'évaluation

- Codigo Hamming PresentaciónDocument17 pagesCodigo Hamming PresentaciónJasmany Farit100% (1)

- Creacion de Una Persona IdealDocument18 pagesCreacion de Una Persona IdealJasmany FaritPas encore d'évaluation

- Estereoisomeria Optica (Prof. Podesta)Document9 pagesEstereoisomeria Optica (Prof. Podesta)Jasmany FaritPas encore d'évaluation

- Mochila y AsignaciónDocument107 pagesMochila y AsignaciónJOEL ALEX UÑAPILLCO MERMAPas encore d'évaluation

- MON2000 ManualDocument464 pagesMON2000 ManualebcinstaPas encore d'évaluation

- RIP Versión 2Document4 pagesRIP Versión 2javier canoPas encore d'évaluation

- Flujo de Informacion Del Sistema de CostosDocument2 pagesFlujo de Informacion Del Sistema de CostosLotus Flowers100% (4)

- BDDDocument14 pagesBDDEdinson EscobarPas encore d'évaluation

- Funciones Asociadas Al Manejo de CadenasDocument8 pagesFunciones Asociadas Al Manejo de CadenasFrancisco JavierPas encore d'évaluation

- El Ciclo Del AguaDocument3 pagesEl Ciclo Del AguanoemilalomaPas encore d'évaluation

- Espionaje InformáticoDocument8 pagesEspionaje InformáticoPiere AndrePas encore d'évaluation

- T3 - Proyecto - Analizador Lexico SintacticoDocument1 pageT3 - Proyecto - Analizador Lexico SintacticoVicman1890Pas encore d'évaluation

- La Planeación OperacionalDocument2 pagesLa Planeación Operacionaltayson huamanPas encore d'évaluation

- 6-Modelo LinealizadoDocument12 pages6-Modelo LinealizadoJaime Adolfo Mejia LeónPas encore d'évaluation

- BII-PB-Tema 9-Lenguajes de Marca o EtiquetaDocument12 pagesBII-PB-Tema 9-Lenguajes de Marca o EtiquetaFrancisco Dominguez SanchezPas encore d'évaluation

- Internet WorkingDocument65 pagesInternet WorkingDiego Mustto MostaceroPas encore d'évaluation

- NTC Iso 14001 LiderazgoDocument9 pagesNTC Iso 14001 LiderazgoJavier SaNzhez GaRciaPas encore d'évaluation

- Curso ActionScript 3.0 en Flash CS3 (AulaDirectiva)Document11 pagesCurso ActionScript 3.0 en Flash CS3 (AulaDirectiva)AulaDirectiva100% (84)

- Practica 15Document20 pagesPractica 15Brenda Cruz MataPas encore d'évaluation

- Arista Santiago Miriam GiovanaDocument1 pageArista Santiago Miriam GiovanaGovana AristaPas encore d'évaluation

- Actividad4 - Álgebra Superior4. Ecuaciones CuadráticasDocument9 pagesActividad4 - Álgebra Superior4. Ecuaciones CuadráticasMoises Guizar Rubio50% (4)

- storage/emulated/0/Download/FACTURA - TELEVISIÓN (Marzo 2021)Document2 pagesstorage/emulated/0/Download/FACTURA - TELEVISIÓN (Marzo 2021)paulaPas encore d'évaluation

- 441Document2 pages441beberlin barberan50% (2)

- Metodos NumericosDocument5 pagesMetodos Numericosecobo243075Pas encore d'évaluation

- Informe Final 1-LAB CIRCUITOS ELECTRICOSDocument6 pagesInforme Final 1-LAB CIRCUITOS ELECTRICOSRaul Villano ObregónPas encore d'évaluation

- Taller - WindowsDocument3 pagesTaller - WindowsAlfredo Hernandez RamosPas encore d'évaluation

- Solucionario de La Ficha 20Document18 pagesSolucionario de La Ficha 20GUZMANPas encore d'évaluation

- Ccna 1 Chapter 7 v5 RespuestasDocument8 pagesCcna 1 Chapter 7 v5 RespuestasAPPS , LIBROS , JUEGOS ETCPas encore d'évaluation

- Terrestre: Código de RastreoDocument1 pageTerrestre: Código de Rastreojuanpablo reyesPas encore d'évaluation

- Díptico Final ComputacionDocument2 pagesDíptico Final Computacionluisvel88Pas encore d'évaluation

- Mapa Conceptual de ProbabilidadDocument1 pageMapa Conceptual de ProbabilidadCristian CallePas encore d'évaluation

- A1 Caso Ejemplo-1-Cobit PDFDocument24 pagesA1 Caso Ejemplo-1-Cobit PDFRocksPas encore d'évaluation