Académique Documents

Professionnel Documents

Culture Documents

Logic Design

Transféré par

Chaudhary WaseemDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Logic Design

Transféré par

Chaudhary WaseemDroits d'auteur :

Formats disponibles

(A constituent college of Sri Siddhartha University)

2012-13

Department of Electronics & Communication

LOGIC DESIGN LAB MANUAL

III SEM BE

Name : Sem : . Sec:

Logic Design Lab Manual

Contents

Exp No 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15.

Title Simplification, Realization of Boolean Expression Using Logic Gates/Universal Gates Half/Full Adder and Half/Full Subtractors. Parallel Adder/Subtractor. BCD To Excess-3 And Excess-3 To BCD code converter Binary-to-Gray And Gray-to-Binary code converter Multiplexer Using IC 74153 De-multiplexer Using IC 74139 Comparators Encoder & Decoder Flip-Flops Asynchronous counters Synchronous counters Decade and binary counters Shift Registers Johnson Counter/ Ring Counter

Page No. 1-2 3-7 9-11 13-15 17-19 21-24 25-28 29-31 33-35 37-39 41-44 45-46 47-53 55-58 59-60

Department of E&C, SSIT, Tumkur

Logic Design Lab manual GIVEN EXPRESSION: Y=(A,B,C,D)= (5,7,9,11,13,15)

Implementation: Using Basic Gates:

Using Universal Gates:

Department of E&C, SSIT, Tumkur

Page 1

Logic Design Lab manual

EXPERIMENT NO. 1:

DATE: / /

SIMPLIFICATION, REALIZATION OF BOOLEAN EXPRESSION USING LOGIC GATES/UNIVERSAL GATES

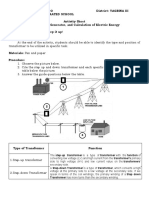

AIM: To Simplify and Realize Boolean Expressions Using Logic Gates/Universal Gates. APPARATUS REQUIRED:- IC Trainer Kit, patch chords, IC7408, IC7432 , IC7400, IC7402, IC 7404,IC 7486. Procedure: 1. Place the IC in the socket of the trainer kit. 2. Make the connections as shown in the circuit diagram. 3. Apply the different combinations of input according to truth table and verify the output. Simplification of expression:Y=(A,B,C,D)= (5,7,9,11,13,15) Write the expression using K-map Y=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD Y =ABD (C+C)+ABD(C+C)+ABD(C+C) Y =ABD+ABD+ABD Y =BD(A+A)+ABD Y=BD+ABD Y=D(B+AB) Y=D(A+B) Y =AD+BD Exercise: Simplify and realize the following POS expn. and implement using nand gates only: Y(A,B,C,D)=(5,7,9,11,13,15)

Department of E&C, SSIT, Tumkur

Page 2

Logic Design Lab manual Half Adder Logic Diagram A 0 0 1 1 Circuit Diagram USING BASIC AND XOR GATES Truth Table B Sum (S) Carry (C) 0 0 0 1 1 0 0 1 0 1 0 1

USING NAND GATES ONLY

Department of E&C, SSIT, Tumkur

Page 3

Logic Design Lab manual

EXPERIMENT NO. 2:

DATE: / /

HALF/FULL ADDER AND HALF/FULL SUBTRACTORS.

Aim: - To realize half/full adder and half/full subtractor. i. ii. Using X-OR and basic gates Using only nand gates.

Apparatus Required: IC Trainer Kit, patch chords , IC 7486, IC 7432, IC 7408, IC 7400, etc. Procedure: 1. Verify the gates. 2. Make the connections as per the circuit diagram. 3. Switch on VCC and apply various combinations of input according to the truth table. 4. Note down the output readings for half/full adder and half/full subtractor sum/difference and the carry/borrow bit for different combinations of inputs.

Exercise: Implement half/full adder and half/full adder circuits using NOR gates only. Which is better, NAND or NOR? Why?

Department of E&C, SSIT, Tumkur

Page 4

Logic Design Lab manual

Full Adder Logic Diagram Ci 0 0 0 0 1 1 1 1 Circuit Diagram USING BASIC AND XOR GATES A 0 0 1 1 0 0 1 1 B 0 1 0 1 0 1 0 1 Truth Table Sum (S) Carry (Co) 0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 1

USING NAND GATES ONLY

Department of E&C, SSIT, Tumkur

Page 5

Logic Design Lab manual Half subtractor Logic Diagram

Truth Table A B 0 0 1 1 Circuit Diagram USING BASIC AND XOR GATES 0 1 0 1 Diff (D) 0 1 1 0 Borrow (B0) 0 1 0 0

USING NAND GATES ONLY

A B

DIFF

BORROW

Department of E&C, SSIT, Tumkur

Page 6

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 7

Logic Design Lab manual Full subtractor

Logic Diagram:

Truth Table

Circuit Diagram (USING BASIC AND XOR GATES)

(USING NAND GATES ONLY)

Department of E&C, SSIT, Tumkur

Page 8

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 9

Logic Design Lab manual Pin Detail: -

7483

Adder: -

Truth Table: A3 A2 A1 A0 B3 B2 B1 B0 C4 (V) S3(V) S2(V) S1(V) S0(V) 0 0 1 1 0 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 0 1 1 1 0 0 0 0 1 0 1 1 1 1 1 0 1 0 1 1 0 1 1 1 0 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 1 0 0 0 0

Department of E&C, SSIT, Tumkur

Page 10

Logic Design Lab manual

EXPERIMENT NO. 3:

DATE: / /

PARALLEL ADDER/SUBTRACTOR

AIM: - To realize IC 7483 as parallel adder / Subtractor. Apparatus Required: IC Trainer Kit, patch chords, IC 7483, IC 7404, etc. Procedure: 1. Apply the inputs to A0 to A3 and B0 to B3. 2. Connect C0 to the Ground. 3. Check the output sum on the S0 to S3 and also C4. 4. For subtraction connect C0 to Vcc, Apply the B input through NOT gate, which gives the complement of B. 5. The truth table of adder and Subtractor are noted down.

Exercise: Implement parallel adder/subtractor using IC 7483 and xor gates.

Department of E&C, SSIT, Tumkur

Page 11

Logic Design Lab manual Subtractor:-

Truth Table for Subtractor

A3 A2 A1 A0 B3 B2 B1 B0 C4(V) S3(V) S2(V) S1(V) S0(V) 0 0 0 1 1 0 1 0 0 0 1 0 1 1 0 0 1 1 0 0 0 0 0 0 1 0 0 1 1 1 0 1 0 1 1 1 1 1 0 1 1 1 0 1 0 0 0 1 0 1 0 0 1 1 0 0 1 1 0 0 1 0 0 0 1

Department of E&C, SSIT, Tumkur

Page 12

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 13

Logic Design Lab manual BCD To Excess-3: Truth Table For Code Conversion: Inputs B3 B2 B1 B0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 E3 (v) 0 0 0 0 0 1 1 1 1 1 Outputs E2 (v) 0 1 1 1 1 0 0 0 0 1 E1 (v) 1 0 0 1 1 0 0 1 1 0 E0 (v) 1 0 1 0 1 0 1 0 1 0

1 0 0 1 Circuit diagram using NAND gates

only:

Department of E&C, SSIT, Tumkur

Page 14

Logic Design Lab manual EXPERIMENT NO. 4: DATE: / /

BCD TO EXCESS-3 AND EXCESS-3 TO BCD CODE CONVERTER AIM: - To study and verify BCD to excess 3 code and excess-3 to BCD code conversion using NAND gates.

APPARATUS REQUIRED: IC Trainer Kit, patch chords, IC 7400, IC 7404, etc.

Procedure: - (BCD Excess 3 and Vice Versa) 1. Make the connections as shown in the fig. 2. Pin [14] of all ICS are connected to +5V and pin [7] to the ground. 3. The inputs are applied at E3, E2, E1, and E0 and the corresponding outputs at B3, B2, B1, and B0 are taken for excess 3 to BCD. 4. The inputs are applied at B3, B2, B1, and B0 and the corresponding outputs are E3, E2, E1 and E0 for BCD to excess 3. 5. Truth tables are verified.

Exercise: Implement BCD to excess-3 and excess-3 to BCD code converter using parallel adder IC 7483.

Department of E&C, SSIT, Tumkur

Page 15

Logic Design Lab manual

Excess-3 To BCD :Truth Table For Code Conversion: Inputs Outputs

E3 E2 E1 E0 B3 (v) B2 (v) B1 (v) B0(v) 0 0 0 0 0 1 1 1 1 0 1 1 1 1 0 0 0 0 1 0 0 1 1 0 0 1 1 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1

1 1 0 0 1 Circuit diagram using NAND gates only:

Department of E&C, SSIT, Tumkur

Page 16

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 17

Logic Design Lab manual

Binary to Gray:

Circuit diagram using EX-OR Gates:

Department of E&C, SSIT, Tumkur

Page 18

Logic Design Lab manual

EXPERIMENT NO. 5:

DATE: / /

BINARY-TO-GRAY AND GRAY-TO-BINARY CODE CONVERTER

AIM: - To convert given binary numbers to gray codes. APPARATUS REQUIRED: IC Trainer Kit, patch chords, IC 7486, etc PROCEDURE: 1. The circuit connections are made as shown in fig. 2. Pin (14) is connected to +Vcc and Pin (7) to ground. 3. In the case of binary to gray conversion, the inputs B0, B1, B2 and B3 are given at respective pins and outputs G0, G1, G2, G3 are taken for all the 16 combinations of the input. 4. In the case of gray to binary conversion, the inputs G0, G1, G2 and G3 are given at respective pins and outputs B0, B1, B2, and B3 are taken for all the 16 combinations of inputs. 5. The values of the outputs are tabulated.

Exercise: Implement binary to gray and gray to binary code converter using nand gates only.

Department of E&C, SSIT, Tumkur

Page 19

Logic Design Lab manual Gray to binary: Truth-table: G3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 G2 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 G1 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 G0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 B3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Circuit Diagram using EX-OR Gates

Department of E&C, SSIT, Tumkur

Page 20

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 21

Logic Design Lab manual

Pin Details: -

Truth Table: CHANNEL A INPUTS

a Ioa I1a I2a I3a

CHANNEL B O/P

Za(v) a Iob

SELECT LINES

S1 S2

INPUTS

SELECT O/P LINES

I1b

I2b

I3b

S1

S2

Za(v)

1 0 0 0 0 0 0 0 0

X 0 1 X X X X X X

X X X 0 1 X X X X

X X X X X 0 1 X X

X X X X X X X 0 1

X 0 0 0 0 1 1 1 1

X 0 0 1 1 0 0 1 1

0 0 1 0 1 0 1 0 1

1 0 0 0 0 0 0 0 0

X 0 1 X X X X X X

X X X 0 1 X X X X

X X X X X 0 1 X X

X X X X X X X 0 1

X 0 0 0 0 1 1 1 1

X 0 0 1 1 0 0 1 1

0 0 1 0 1 0 1 0 1

Department of E&C, SSIT, Tumkur

Page 22

Logic Design Lab manual

EXPERIMENT NO. 6: MULTIPLEXER USING IC 74153 Aim: - To verify the truth table of multiplexer using 74153

DATE: / /

To study the arithmetic circuits half-adder and half Subtractor, full adder and full Subtractor using multiplexer. Apparatus Required: IC Trainer Kit, patch chords, IC 74153, IC 74139, IC 7404, etc. Procedure: 1. The Pin [16] is connected to + Vcc. 2. Pin [8] is connected to ground. 3. The inputs are applied either to A input or B input. 4. If MUX A has to be initialized, Ea is made low and if MUX B has to be initialized, Eb is made low. 5. Based on the selection lines one of the inputs will be selected at the output and thus the truth table is verified. 6. In case of half adder using MUX, sum and carry is obtained by applying a constant inputs at I0a, I1a, I 2a, I 3a and I 0b, I 1b, I 2b and I3b and the corresponding values of select lines are changed as per table and the output is taken at Z0a as sum and Z0b as carry. 7. In this case, the channels A and B are kept at constant inputs according to the table and the inputs A and B are varied. Making Ea and Eb zero and the output is taken at Za, and Zb. 8. In full adder using MUX, the input is applied at Cn-1, An and Bn. According to the table corresponding outputs are taken at Cn and Dn.

Department of E&C, SSIT, Tumkur

Page 23

Logic Design Lab manual Half Adder Using 74153 Half Subtractor Using 74153:

Full Adder Using 74153: -

Full Subtractor Using 74153: -

Department of E&C, SSIT, Tumkur

Page 24

Logic Design Lab manual Truth Tables: Full Adder An Bn Cn-1 Sn (V) Cn (V) Half adder A B Sn (V) Cn (V) 0 0 0 1 1 0 1 1 0 1 1 0 0 0 0 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 0 1 0 0 1 0 0 0 1 0 1 1 1

Full subtractror An Bn Cn-1 Dn (V) Bn (V) Half subtractor A B Dn (V) Bn (V) 0 0 0 1 1 0 1 1 0 1 1 0 0 1 0 0 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 0 1 0 0 1 0 1 1 1 0 0 0 1

Department of E&C, SSIT, Tumkur

Page 25

Logic Design Lab manual Pin details:

Truth Table For Demux: CHANNEL A Inputs Outputs Inputs CHANNEL B Outputs

a S1a S0a Y0a Y1a Y2a Y3a 1 0 0 0 0 X 0 0 1 1 X 0 1 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0

b S1b S0b Y0b Y1b Y2b Y3b 1 0 0 0 0 X 0 0 1 1 X 0 1 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0

Half subtractor:-

Department of E&C, SSIT, Tumkur

Page 26

Logic Design Lab manual EXPERIMENT NO. 7: DE-MULTIPLEXER USING IC 74139 DATE: / /

Aim: - To verify the truth table of de-multiplexer using 74139. To study the arithmetic circuits half-adder and half Subtractor, full adder and full Subtractor using de- multiplexer. Apparatus Required: IC Trainer Kit, patch chords, IC 74153, IC 74139, IC 7404, etc Procedure: 1. The inputs are applied to either a input or b input 2. The demux is activated by making Ea low and Eb low. 3. The truth table is verified.

Department of E&C, SSIT, Tumkur

Page 27

Logic Design Lab manual Full subtractor using IC 74139:-

Truth Table Half Subtractor A B Dn (V) Bn (V) 0 0 0 1 1 0 1 1 0 1 1 0 0 1 0 0

Full Subtractor An 0 0 0 0 1 1 1 1 Bn 0 0 1 1 0 0 1 1 Cn1 0 1 0 1 0 1 0 1 Dn (V) 0 1 1 0 1 0 0 1 Bn (V) 0 1 1 1 0 0 0 1

Department of E&C, SSIT, Tumkur

Page 28

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 29

Logic Design Lab manual One Bit Comparator: Truth-table Y0 A 0 0 1 1 Two Bit Comparator: B (A<B) (A>B) (A=B) 0 1 0 1 0 1 0 0 0 0 1 0 1 0 0 1 Y1 Y2

A1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

A0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

B1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Y2(A=B) 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

Y1(A>B) 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0

Y0(A<B) 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 1

Department of E&C, SSIT, Tumkur

Page 30

Logic Design Lab manual Date: __/__/____

Experiment No:8

COMPARATORS

Aim: - To verify the truth table of one bit and two bit comparators using logic gates and four bit and eight bit comparators using IC 7485.

Apparatus Required: IC 7485, IC 7404, IC 7408, etc.

Procedure: 1. Verify the gates. 2. Make the connections as per the circuit diagram. 3. Switch on Vcc. 4. Applying i/p and Check for the outputs. 5. The voltameter readings of outputs are taken and tabulated in tabular column. 6. The o/p are verified. Exercise: Implement one bit, two bit comparator circuit using nand gates only. Write the function table for 8 bit comparator .

Department of E&C, SSIT, Tumkur

Page 31

Logic Design Lab manual 4-bit Comparator LOGIC DIAGRAM:

FUNCTION TABLE : Comparing Cascading I/Ps I/Ps

Outputs

A>B A=B A<B A>B A=B A<B A>B X 1 X 0 0 1 X X 0 1 0 0 0 X X 0 X 1 0 1 X 1 1 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 1

A=B

A<B

8-Bit Comparator: LSB MSB

Department of E&C, SSIT, Tumkur

Page 32

Logic Design Lab manual

PIN DETAILS:-

Department of E&C, SSIT, Tumkur

Page 33

Logic Design Lab manual

FUNCTION TABLE:

EI H L L L L L L L L L

0 X H X X X X X X X L

1 X H X X X X X X L H

INPUTS 2 3 4 X X X H H H X X X X X X X X X X X L X L H L H H H H H H H H

5 X H X X L H H H H H

6 X H X L H H H H H H

7 X H L H H H H H H H

A2 H H L L L L H H H H

OUTPUTS A1 A0 GS H H H H H H L L L L H L H L L H H L L L L L H L H L L H H L

E0 H L H H H H H H H H

Department of E&C, SSIT, Tumkur

Page 34

Logic Design Lab manual

Experiment No: 9 ENCODER & DECODER

DATE: __/__/____

AIM:-To convert a given octal input to the binary output and to study the LED display using 7447 7-segment decoder/ driver.

APPARATUS REQUIRED: IC 74148, IC 7447, 7-segment display, etc.

PROCEDURE: - ( Priority Encoder) 1. Connections are made as per circuit diagram. 2. The octal inputs are given at the corresponding pins. 3. The outputs are verified at the corresponding output pins.

PROCEDURE: - (Decoder) 1. Connections are made as per the circuit diagram. 2. Connect the pins of IC 7447 to the respective pins of the LED display board. 3. Give different combinations of the inputs and observe the decimal numbers displayed on the board.

Exercise: Implement the following expression using decoder and logic gates.

Department of E&C, SSIT, Tumkur

Page 35

Logic Design Lab manual BCD TO SEVEN SEGMENT DECODER CIRCUIT DIAGRAM WITH LED DISPLAY

Department of E&C, SSIT, Tumkur

Page 36

Logic Design Lab manual TRUTH-TABLE: DECIMAL DIGIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 INPUTS D 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 C 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 LED DISPLAY VALUE 0 1 2 3 4 5 6 7 8 9 SEVEN SEGMENTS LEVEL a 1 0 1 1 0 1 0 1 1 1 b 1 1 1 1 1 0 0 1 1 1 c 1 1 0 1 1 1 1 1 1 1 d 1 0 1 1 0 1 1 0 1 0 e 1 0 1 0 0 0 1 0 1 0 f 1 0 0 0 1 1 1 0 1 1 g 0 0 1 1 1 1 1 0 1 1

No seg. glows

Department of E&C, SSIT, Tumkur

Page 37

Logic Design Lab manual

Circuit Diagram: - (Master Slave JK Flip-Flop)

Truth Table:- (Master Slave JK Flip-Flop) Preset Clear 0 1 1 1 1 1 D Flip-Flop:1 0 1 1 1 1 J K Clock Qn+1 X X 1 0 Qn 0 1

Qn + 1

0 1 Set Reset No Change Reset Set Toggle

X X X X 0 0 0 1 1 0 1 1

Qn

1 0 Qn

Qn

7410

Truth Table:Preset Clear D Clock Qn+1 1 1 1 1 0 1 0 1

Qn + 1

1 0

Department of E&C, SSIT, Tumkur

Page 38

Logic Design Lab manual Date: __/__/____

Experiment No: 10 FLIP-FLOPS

Aim: Verification of truth-tables of the following types of flip-flops using NAND gates and using IC 7476: i. JK Master Slave FF ii. D-FF iii. T-FF iv. SR-FF

Apparatus Required: IC 7410, IC 7400, IC 7476, etc.

Procedure: 1. Connections are made as per circuit diagram. 2. The truth table is verified for various combinations of inputs.

Exercise: Write the timing diagrams for all the above Flip-Flops

Department of E&C, SSIT, Tumkur

Page 39

Logic Design Lab manual T Flip-Flop:-

Truth Table:-

Preset Clear T Clock Qn+1 1 1 SR Flip-flop: 1 1 0 1 Qn

Qn + 1 Qn

Qn

Qn

Truth-table:

Department of E&C, SSIT, Tumkur

Page 40

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 41

Logic Design Lab manual Circuit Diagram: - 3-Bit Asynchronous Up Counter

Truth-table: 3-bit Asynchronous up counter Clock QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 8 0 0 0 9 0 0 1 Circuit Diagram: - 3-Bit Asynchronous Down Counter

Department of E&C, SSIT, Tumkur

Page 42

Logic Design Lab manual Experiment No: 11 ASYNCHRONOUS COUNTERS Date: __/__/____

Aim: Realization of 3-bit asynchronous up/down counters and design of Mod-N counter design. Apparatus Required: IC 7408, IC 7476, IC 7400, IC 7432 etc.

Procedure: 1. Connections are made as per circuit diagram. 2. Clock pulses are applied one by one at the clock I/P and the O/P is observed at QA, QB & QC for IC 7476. 3. Truth table is verified.

Department of E&C, SSIT, Tumkur

Page 43

Logic Design Lab manual

Truth-table: 3-bit Asynchronous down counter Clock QC QB QA 0 1 1 1 1 1 1 0 2 1 0 1 3 1 0 0 4 0 1 1 5 0 1 0 6 0 0 1 7 0 0 0 8 1 1 1 9 1 1 0 Mod 5 Asynchronous up Counter:-

Truth-table: Mod 5 Asynchronous counter Clock QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 0 0 0

Department of E&C, SSIT, Tumkur

Page 44

Logic Design Lab manual Mod 3 Asynchronous up Counter:-

Truth-table: Clock QB QA 0 0 0 1 0 1 2 1 0 3 0 0 Mod 4 Asynchronous down Counter:QA QB

7432

Vcc

Pre Pre

Q 7476 Q

J

clk

Q 7476 Q

Clr

clk

clk

K

Clr

Vcc

Truth-table: Clock QB QA 0 1 1 1 1 0 2 0 1 3 0 0

Department of E&C, SSIT, Tumkur

Page 45

Logic Design Lab manual

State Diagram

Department of E&C, SSIT, Tumkur

Page 46

Logic Design Lab manual

Experiment No: 12 Date: __/__/____

SYNCHRONOUS COUNTERS

Aim: Design and Realization of 3-bit synchronous counters. Apparatus Required: IC 7408, IC 7476, IC 7400, IC 7432, etc. Design steps : 1. Write the truth-table or state diagram. 2. From truth-table/state-diagram, derive the state transition table. 3. Decide the no. and type of flip-flops to be used. 4. Using the corresponding excitation tables, derive the input and output equations and simplify using K-maps. 5. Using the derived simplified input and output expressions with flipflops, draw the circuit diagram. Procedure: 1. Connections are made as per circuit diagram. 2. Clock pulses are applied simultaneously at the clock I/Ps of all 7476 ICs used in the circuit and the O/P is observed at the outputs of ICs 7476. 3. Truth table is verified.

Department of E&C, SSIT, Tumkur

Page 47

Logic Design Lab manual

Internal Diagram of IC 7490

Department of E&C, SSIT, Tumkur

Page 48

Logic Design Lab manual Experiment No: 13 DECADE AND BINARY COUNTERS Date: __/__/____

Aim: Realization of decade and binary counters. Apparatus Required: IC 7408, IC 7476, IC 7400, IC 7432, IC 7490, IC 74192, IC 74193 etc. Procedure (IC 74192, IC 74193):1. Connections are made as per the circuit diagram except the connection from output of NAND gate to the load input. 2. The data (0011) = 3 is made available at the data i/ps A, B, C & D respectively. 3. The load pin made low so that the data 0011 appears at QD, QC, QB & QA respectively. 4. Now connect the output of the NAND gate to the load input. 5. Clock pulses are applied to count up pin and the truth table is verified. 6. Now apply (1100) = 12 for 12 to 5 counter and remaining is same as for 3 to 8 counter.

Department of E&C, SSIT, Tumkur

Page 49

Logic Design Lab manual

Circuit Diagram for Decade Counter

Department of E&C, SSIT, Tumkur

Page 50

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 51

Logic Design Lab manual

Circuit diagram for Preset value=8, N=6 (To count from 8 to 3)

Department of E&C, SSIT, Tumkur

Page 52

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 53

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 54

Logic Design Lab manual

Department of E&C, SSIT, Tumkur

Page 55

Logic Design Lab manual Circuit Diagram: - Shift Left Clock Serial i/p QA QB QC QD 1 2 3 4 1 0 1 1 X X X 1 X X 1 0 X 1 0 1 1 0 1 1

SIPO (Right Shift):-

Clock Serial i/p QA QB QC QD 1 2 3 4 0 1 1 1 0 1 1 1 X 0 1 1 X X 0 1 X X X 0

SISO:Serial i/p do=0 d1=1 d2=1 d3=1 X X X

Clock 1 2 3 4 5 6 7

QA QB QC 0 1 1 1 X X X X 0 1 1 1 X X X X 0 1 1 1 X

QD X X X 0=do 1=d1 1=d2 1=d3

Department of E&C, SSIT, Tumkur

Page 56

Logic Design Lab manual Experiment No: 14 SHIFT REGISTERS Date: __/__/____

Aim:-

Realization of 3-bit counters as a sequential circuit and Mod-N counter design (7476, 7490, 74192, 74193).

Apparatus Required: IC 7495, etc.

Procedure: Serial In Parallel Out:5. Connections are made as per circuit diagram. 6. Apply the data at serial i/p 7. Apply one clock pulse at clock 1 (Right Shift) observe this data at QA. 8. Apply the next data at serial i/p. 9. Apply one clock pulse at clock 2, observe that the data on QA will shift to QB and the new data applied will appear at QA. 10. Repeat steps 2 and 3 till all the 4 bits data are entered one by one into the shift register.

Serial In Serial Out:1. Connections are made as per circuit diagram. 2. Load the shift register with 4 bits of data one by one serially. 3. At the end of 4th clock pulse the first data d0 appears at QD. 4. Apply another clock pulse; the second data d1 appears at QD. 5. Apply another clock pulse; the third data appears at QD. 6. Application of next clock pulse will enable the 4th data d3 to appear at QD. Thus the data applied serially at the input comes out serially at QD

Department of E&C, SSIT, Tumkur

Page 57

Logic Design Lab manual

PISO:-

Mode Clock Parallel i/p 1 0 0 0 PIPO:1 2 3 4 1 0 1 1 X X X X X X X X X X X X 1 X X X

Parallel o/p 0 1 X X 1 0 1 X 1 1 0 1

A B C D QA QB QC QD

Clock Parallel i/p 1 1 0 1 1 1

Parallel o/p 0 1 1

A B C D QA QB QC QD

Department of E&C, SSIT, Tumkur

Page 58

Logic Design Lab manual Parallel In Parallel Out:1. 2. 3. 4. Connections are made as per circuit diagram. Apply the 4 bit data at A, B, C and D. Apply one clock pulse at Clock 2 (Note: Mode control M=1). The 4 bit data at A, B, C and D appears at QA, QB, QC and QD respectively.

Parallel In Serial Out:1. Connections are made as per circuit diagram. 2. Apply the desired 4 bit data at A, B, C and D. 3. Keeping the mode control M=1 apply one clock pulse. The data applied at A, B, C and D will appear at QA, QB, QC and QD respectively. 4. Now mode control M=0. Apply clock pulses one by one and observe the data coming out serially at QD. Left Shift:1. Connections are made as per circuit diagram. 2. Apply the first data at D and apply one clock pulse. This data appears at QD. 3. Now the second data is made available at D and one clock pulse applied. The data appears at QD to QC and the new data appears at QD. 4. Step 3 is repeated until all the 4 bits are entered one by one. 5. At the end 4th clock pulse the 4 bits are available at QA, QB, QC and QD.

Department of E&C, SSIT, Tumkur

Page 59

Logic Design Lab manual

Circuit Diagram: - Ring Counter

Mode Clock QA QB QC QD 1 0 0 0 0 0 1 2 3 4 5 6 1 0 0 0 1 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0

repeats

Johnson Counter:-

Mode Clock QA QB QC QD 1 0 0 0 0 0 0 0 0 0 1 2 3 4 5 6 7 8 9 10 1 1 1 1 0 0 0 0 1 0 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0

repeats

Department of E&C, SSIT, Tumkur

Page 60

Logic Design Lab manual Experiment No: 15 JOHNSON COUNTERS / RING COUNTER Date: __/__/____

Aim:-

Design and testing of Ring counter/ Johnson counter.

Apparatus Required: IC 7495, IC 7404, etc.

Procedure: 1. Connections are made as per the circuit diagram. 2. Apply the data 1000 at A, B, C and D respectively. 3. Keeping the mode M = 1, apply one clock pulse. 4. Now the mode M is made 0 and clock pulses are applied one by one and the truth table is verified. 5. Above procedure is repeated for Johnson counter also.

Department of E&C, SSIT, Tumkur

Page 61

Logic Design Lab manual

Useful IC Pin details 7400(NAND) 7402(NOR)

7404(NOT)

7408(AND)

7432(OR)

7486(XOR)

Department of E&C, SSIT, Tumkur

Page 62

Logic Design Lab manual

7410(3-i/p NAND)

7420(4-i/p NAND)

Department of E&C, SSIT, Tumkur

Page 63

Vous aimerez peut-être aussi

- Digital Electronics LabmanualDocument66 pagesDigital Electronics LabmanualToaster97Pas encore d'évaluation

- Exp10 BCDAdderDocument4 pagesExp10 BCDAddervk2you009Pas encore d'évaluation

- Assignment No:-11 Date: Assignment Name:-Design & Implement 4-Bit BCD AdderDocument5 pagesAssignment No:-11 Date: Assignment Name:-Design & Implement 4-Bit BCD AdderAnindya Mahata100% (2)

- BCD To 7 Segment Display ProjectnewDocument5 pagesBCD To 7 Segment Display ProjectnewSaeed Ali ShahaniPas encore d'évaluation

- DELD Lab Manual 2020Document120 pagesDELD Lab Manual 2020shinchan noharaPas encore d'évaluation

- RP Jain Adc DacDocument27 pagesRP Jain Adc DacAnand SinghPas encore d'évaluation

- Einfochips Interview QuestionsDocument1 pageEinfochips Interview Questionsshafi hasmani100% (1)

- Verilog CodeDocument60 pagesVerilog CodePriyanka JainPas encore d'évaluation

- Reg - No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05Document11 pagesReg - No:18BEC0175 ECE 3002 VLSI System Design Task. No: 05Kotha Hemanth100% (1)

- 8 Bit Alu Using Gdi TechniqueDocument7 pages8 Bit Alu Using Gdi TechniqueTADIBOINA PAVAN KUMARPas encore d'évaluation

- Mark Allocation 2013Document2 pagesMark Allocation 2013janu13Pas encore d'évaluation

- Hybrid Low Radix Encoding-Based Approximate Booth MultipliersDocument33 pagesHybrid Low Radix Encoding-Based Approximate Booth MultipliersAKASHDEEP MITRA100% (1)

- ALU ReportDocument11 pagesALU ReportAzad Kiyal100% (2)

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentDocument43 pagesECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaPas encore d'évaluation

- Astable Using 555Document2 pagesAstable Using 555SumithPas encore d'évaluation

- Experiment 7: Magnitude ComparatorsDocument5 pagesExperiment 7: Magnitude Comparatorsanirudh lakshminarasimhanPas encore d'évaluation

- Ei-2406 Isd Lab Manual (2013)Document47 pagesEi-2406 Isd Lab Manual (2013)Rahul GRPas encore d'évaluation

- Seven Segment Display Document PDFDocument16 pagesSeven Segment Display Document PDFRekha MudalagiriPas encore d'évaluation

- DSDV MODULE 3 Implementation FabricsDocument17 pagesDSDV MODULE 3 Implementation Fabricssalman shariffPas encore d'évaluation

- 0 - MPMC Lab Manual A.Y. 2020-21 R-18Document53 pages0 - MPMC Lab Manual A.Y. 2020-21 R-18Karthik BoggarapuPas encore d'évaluation

- Verify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)Document8 pagesVerify Four Voltage and Current Parameters For TTL and Cmos (Ic 74Lsxx, 74Hcxx)sonalibhagwatkar100% (1)

- Module 4 - Number Systems and Boolean AlgebraDocument8 pagesModule 4 - Number Systems and Boolean AlgebraSuyog ChavanPas encore d'évaluation

- D Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALDocument41 pagesD Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALArrnaav Singh RathoreePas encore d'évaluation

- Experiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectDocument3 pagesExperiment-11 BCD Code To 7-Segment Decoder 11-1 ObjectMohammed Dyhia AliPas encore d'évaluation

- DLD Lab 1Document5 pagesDLD Lab 1گيدوڙو ماڇيPas encore d'évaluation

- 4 Bit BCD AdderDocument7 pages4 Bit BCD AdderJagnur SinghPas encore d'évaluation

- Design of Traffic Light Controller Using Timer CircuitDocument3 pagesDesign of Traffic Light Controller Using Timer CircuitVinooja cPas encore d'évaluation

- Final C++ ManualDocument36 pagesFinal C++ ManualHarish G CPas encore d'évaluation

- (148163546) Stick Diagram and LayoutDocument9 pages(148163546) Stick Diagram and LayoutRohitParjapat0% (1)

- Implementation of A Logic Circuit From 8x3 Encoder and A Multiplexer.Document4 pagesImplementation of A Logic Circuit From 8x3 Encoder and A Multiplexer.Mohayminul Al-HamimPas encore d'évaluation

- Low-Power and Area-Efficient Carry Select AdderDocument21 pagesLow-Power and Area-Efficient Carry Select AdderrajidisahithiPas encore d'évaluation

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDocument5 pagesLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- DC Motor CTRL Using Single SwitchDocument44 pagesDC Motor CTRL Using Single SwitchAbhijeet NayakPas encore d'évaluation

- MPMC Lab ManualDocument107 pagesMPMC Lab ManualReena RajPas encore d'évaluation

- Experiment-10 (Adder & Subtractor)Document7 pagesExperiment-10 (Adder & Subtractor)M BalajiPas encore d'évaluation

- Object CounterDocument39 pagesObject CounterNARESH WALIA100% (1)

- Ecl 203 MCQDocument3 pagesEcl 203 MCQresham k vPas encore d'évaluation

- Ec8361-Adc Lab ManualDocument118 pagesEc8361-Adc Lab ManualmuminthajPas encore d'évaluation

- Electrical Engineering: Project ReportDocument51 pagesElectrical Engineering: Project ReportVasu ThakurPas encore d'évaluation

- Embedded Systems Lab 18ECL66: Demonstrate The Use of An External Interrupt To Toggle An LED On/OffDocument16 pagesEmbedded Systems Lab 18ECL66: Demonstrate The Use of An External Interrupt To Toggle An LED On/OffJAYANTH JPas encore d'évaluation

- Hardware Software Codesign Question PaperDocument2 pagesHardware Software Codesign Question PaperRaviPas encore d'évaluation

- BCS302 Set 2Document2 pagesBCS302 Set 2megumifushiguru999Pas encore d'évaluation

- Design A 4-Bit Johnson's Counter Using D Flip-FlopsDocument6 pagesDesign A 4-Bit Johnson's Counter Using D Flip-Flopslokesh krapaPas encore d'évaluation

- Case Study of An Embedded System For A Smart CardDocument1 pageCase Study of An Embedded System For A Smart CardParas Khanal0% (1)

- Experiment No. 14: Laboratory Hand Book Implementation of Siso, Sipo, Piso and Pipo Shift RegisterDocument9 pagesExperiment No. 14: Laboratory Hand Book Implementation of Siso, Sipo, Piso and Pipo Shift Register5611 M.Mubeen M.yaseenPas encore d'évaluation

- Verilog HDL - 18ec56 AssignmentDocument2 pagesVerilog HDL - 18ec56 Assignmentsureshfm1Pas encore d'évaluation

- Ipv6 Examples NumericalsDocument8 pagesIpv6 Examples NumericalsAbhishek RegmiPas encore d'évaluation

- Microcontroller Based Weighing MachineDocument7 pagesMicrocontroller Based Weighing MachineNaveen NaniPas encore d'évaluation

- Digital Quiz System: ES212: Digital Logic Design Project Report TitleDocument14 pagesDigital Quiz System: ES212: Digital Logic Design Project Report TitleMughees MehmoodPas encore d'évaluation

- Number SeriesDocument96 pagesNumber Serieshoney1002Pas encore d'évaluation

- Lachoo Memorial College of Science and Technology (Autonomous) JodhpurDocument16 pagesLachoo Memorial College of Science and Technology (Autonomous) JodhpurGuruji rj19Pas encore d'évaluation

- Expt No.:3 Date: Design and Implementation of Multiplexer and Demultiplexer Using Logic Gates Aim: Apparatus RequiredDocument7 pagesExpt No.:3 Date: Design and Implementation of Multiplexer and Demultiplexer Using Logic Gates Aim: Apparatus Requiredrsabitha ECE-HICET100% (1)

- Digital Dice Is Final DFFFFFFFFFFDocument3 pagesDigital Dice Is Final DFFFFFFFFFFKaran ShahPas encore d'évaluation

- Epc Module-5 (B) ThyristorsDocument16 pagesEpc Module-5 (B) Thyristorskaranphutane2254Pas encore d'évaluation

- Fpga ManualDocument7 pagesFpga ManualRahul SharmaPas encore d'évaluation

- Logic Design Lab Manual 10ESL38 3rd Sem 2013Document61 pagesLogic Design Lab Manual 10ESL38 3rd Sem 2013vishvakirana75% (4)

- BTL Logic Design Lab Manual 10ESL38 3rd Sem 2011Document67 pagesBTL Logic Design Lab Manual 10ESL38 3rd Sem 2011Manjunath JiPas encore d'évaluation

- Logic Design Lab ManualDocument72 pagesLogic Design Lab ManualHitha Gangatkar100% (1)

- Logic Design Lab Manual 10ESL38 3rd Sem 2011 PDFDocument61 pagesLogic Design Lab Manual 10ESL38 3rd Sem 2011 PDFvka_prince100% (1)

- Digital Ic TesterDocument28 pagesDigital Ic TesterChris ManojPas encore d'évaluation

- Teletek Intruder Alarm PDFDocument12 pagesTeletek Intruder Alarm PDFBabali MedPas encore d'évaluation

- Computers As Components 2nd Edi - Wayne WolfDocument815 pagesComputers As Components 2nd Edi - Wayne WolfShubham RajPas encore d'évaluation

- Analyzing Circuits Lab II DLD 2021-2Document7 pagesAnalyzing Circuits Lab II DLD 2021-2octavie ahmedPas encore d'évaluation

- Tayug I Substation Operating Procedures and GuidelinesDocument6 pagesTayug I Substation Operating Procedures and GuidelinesTrenchera SubstationPas encore d'évaluation

- Ij UxDocument308 pagesIj UxRagdex RockPas encore d'évaluation

- Energizer L92: Product Datasheet Product DatasheetDocument2 pagesEnergizer L92: Product Datasheet Product DatasheetDot N SpotPas encore d'évaluation

- A.C. Frequency Sonometer by MR - Charis Israel AnchaDocument3 pagesA.C. Frequency Sonometer by MR - Charis Israel AnchaCharis Israel AnchaPas encore d'évaluation

- Unilap Iso 5 KV: The Insulation ExpertDocument2 pagesUnilap Iso 5 KV: The Insulation Expertflorin071100% (1)

- Activity Sheet Session 9-MORADO, NANETTEDocument4 pagesActivity Sheet Session 9-MORADO, NANETTENanette MoradoPas encore d'évaluation

- 3.2 Genertaor and Excitation SystemDocument42 pages3.2 Genertaor and Excitation Systemonur.sezerPas encore d'évaluation

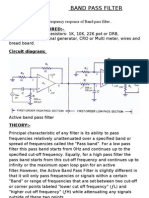

- Band Pass FilterDocument3 pagesBand Pass FilterShruti MathurPas encore d'évaluation

- CMC156$DatasheetDocument4 pagesCMC156$DatasheetLam Duy TienPas encore d'évaluation

- Mda DSP PDFDocument2 pagesMda DSP PDFMohamed AboelmagdPas encore d'évaluation

- Name: Reshma Vyankat Suryawanshi. Subject: PPT Presentation On Applications of DC Drives. Roll No.: BE16F03F055. Guided By: Dr. N. R. Bhasme SirDocument15 pagesName: Reshma Vyankat Suryawanshi. Subject: PPT Presentation On Applications of DC Drives. Roll No.: BE16F03F055. Guided By: Dr. N. R. Bhasme Sirreshma suryawanshiPas encore d'évaluation

- Typical MRP ProblemDocument4 pagesTypical MRP Problemashwin josephPas encore d'évaluation

- RENR5042 C11 C13 TroubleshootingDocument196 pagesRENR5042 C11 C13 TroubleshootingAndrei Bleoju100% (39)

- TCH & SD OptimizationDocument18 pagesTCH & SD Optimizationyadav_dheeraj19815Pas encore d'évaluation

- Network of Networks: Submitted by Mohammed Sadique.P.H REG:082600176Document11 pagesNetwork of Networks: Submitted by Mohammed Sadique.P.H REG:082600176Shahzoor NizarPas encore d'évaluation

- Designing Conduit RunsDocument6 pagesDesigning Conduit Runsnimaboat4589Pas encore d'évaluation

- RDC6334G Biref EnglishDocument4 pagesRDC6334G Biref EnglishJuanjo AcvdoPas encore d'évaluation

- Abhijeet ShindeDocument5 pagesAbhijeet ShindeAbhijeet ShindePas encore d'évaluation

- Discover The Small Switch Mode Power Supplies Modification SecretsDocument10 pagesDiscover The Small Switch Mode Power Supplies Modification Secretscarlos1670201480% (5)

- MVB enDocument1 pageMVB enferliverpoolPas encore d'évaluation

- Group 4: Diagnosis and Identification of Faulty SystemDocument35 pagesGroup 4: Diagnosis and Identification of Faulty SystemPrecious GamerPas encore d'évaluation

- Manual Tecnico Nussbaum 2.28 - SL - Until - 2.50 - SL - II - 05-2011 - EDocument75 pagesManual Tecnico Nussbaum 2.28 - SL - Until - 2.50 - SL - II - 05-2011 - Emiraporlaventan50% (2)

- Muhammad Farrukh QAMAR - Written TestDocument43 pagesMuhammad Farrukh QAMAR - Written TestRana Muhammad Ashfaq KhanPas encore d'évaluation

- Silicon N Channel MOSFET Tetrode BF 998: FeaturesDocument8 pagesSilicon N Channel MOSFET Tetrode BF 998: FeatureshaPas encore d'évaluation

- BAT42W, BAT43W: Vishay SemiconductorsDocument4 pagesBAT42W, BAT43W: Vishay SemiconductorsmariopilarPas encore d'évaluation

- Feeder CatalogDocument30 pagesFeeder CatalogAhmed ShabanPas encore d'évaluation