Académique Documents

Professionnel Documents

Culture Documents

1ra Unidad

Transféré par

Melissa ClarkTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

1ra Unidad

Transféré par

Melissa ClarkDroits d'auteur :

Formats disponibles

1ra UNIDAD

Introduccin al

Microprocesador

1

1.1 LA EVOLUCIN DEL MICROPROCEADOR

Antes de comentar los microprocesadores modernos, se debe primero entender qu fue lo

que puso a estos dispositivos en primer plano. La historia dice que los antiguos babilonios

empezaron a usar el baco, (calculadora primitiva hecha con cuentas o esferas

ahuecadas), alrededor del ao !! a. de "#. #on el tiempo, esta sencilla calculadora,

estimul$ a la humanidad para perfeccionar una maquinaria calculadora en que se

utilizaban engranes % ruedas (&las 'ascal en 1()*). +e continuaron los progresos con las

gigantescas m,quinas computadoras de las dcadas de 1-)! % 1-!, construidas con

relevadores % tubos de vac.o (bulbos). /,s adelante, se utilizaron los transistores % los

componentes electr$nicos de estado s$lido para construir las poderosas computadoras de

la dcada de 1-(!. #on el advenimiento de los circuitos integrados se lleg$ al perfecciona0

miento del microprocesador % de los sistemas de microcomputadoras.

El microprocesador de 4 bits

1n 1-21, 3ntel #orporation % el talento creativo de /arcian 1. 4off lanzaron el primer

microprocesador5 el )!!), de ) bits. 1ste controlador integrado, programable en un solo

encapsulado era insuficiente, seg6n las normas actuales, porque s$lo direccionaba )!-(

localidades de ) bits en la memoria. 1l )!!) conten.a un con7unto de instrucciones que

ofrec.an s$lo ) instrucciones diferentes. #omo consecuencia, el )!!) s$lo se pod.a

emplear en aplicaciones limitadas, como en los primeros 7uegos de video % en

controladores pequeos basados en microprocesadores. #uando surgieron aplicaciones

m,s comple7as para el microprocesador, el )!!) result$ inadecuado.

El microprocesador de 8 bits

/,s tarde, en 1-21, al percatarse que el microprocesador era un producto viable para

comercializaci$n, 3ntel #orporation produ7o el 8!!8, el primer microprocesador de 8 bits. 1l

tamao ampliado de la memoria (1(9&) % las instrucciones adicionales (un total de )8) en

este nuevo microprocesador brindaron la oportunidad de muchas aplicaciones m,s

avanzadas (19 es igual a 1!*) % un byte es un n6mero de 8 bits).

#onforme los ingenieros desarrollaban usos m,s demandantes para el

microprocesador, la memoria % el 7uego de instrucciones m,s o menos pequeos del 8!!8

pronto limitaron su utilidad. 'or tanto, en 1-2:, 3ntel #orporation introdu7o el 8!8!, el

primero de los microprocesadores modernos de 8 bits. 'ronto, otras empresas empezaron

a lanzar sus propias versiones de los procesadores de ) % de 8 bits. 1n la tabla 101 se

enumeran muchos de estos primeros microprocesadores.

*

;'ero qu ten.a de especial el 8!8!< =o s$lo direccionaba m,s en la memoria %

e7ecutaba m,s instrucciones, % con diez veces m,s rapidez que el 8!!8. >na suma que

tardaba *! s en un sistema basado en un 8!!8, s$lo necesitaba *.! s en un sistema

basado en un 8!8!. Adem,s, el 8!8! era compatible con la l$gica transistor0transistor

(??L) lo cual significaba que se pod.a interconectar con componentes de l$gica ??L

est,ndar. ?odas estas venta7as introdu7eron la era del 8!8! % la poca siempre en

e@pansi$n del microprocesador.

3ntel #orporation introdu7o en 1-22, una nueva versi$n del 8!8!5 el 8!8. Aunque

s$lo ligeramente m,s avanzado que el 8!8!, el 8!8 direcciona la misma cantidad de

memoria, e7ecuta m,s o menos el mismo n6mero de instrucciones % suma en 1.: s en

lugar de *.! s. Las principales venta7as del 8!8 son el generador de relo7 % el

controlador del sistema integrados, que eran componentes e@ternos en un sistema basado

en el 8!8!. ?an s$lo 3ntel ha vendido m,s de 1!! millones de piezas del microprocesador

8!8. Atras empresas, como =1#, A/B, ?oshiba e 4itachi tambin fabrican, ba7o licencia,

una versi$n del microprocesador 8!8. 1stas caracter.sticas han hecho del 8!8 uno de

los microprocesadores 3ntel m,s conocidos.

El microprocesador de 16 bits

1n 1-28, 3ntel #orporation lanz$ el microprocesador 8!8( % m,s o menos un ao m,s

tarde, el 8!88. Ambos dispositivos son microprocesadores de 1( bits, que e7ecutan

instrucciones en escasos )!! nsC una gran me7or.a en relaci$n con la velocidad de

e7ecuci$n del 8!8. 1l 8!8( % el 8!88 tienen tambin capacidad para direccionar a un 1/

b%te (8 bits) o una memoria de 1*9 palabra (1( bits de ancho). Las velocidades m,s altas

de e7ecuci$n % el tamao de memoria m,s grande, permitieron al 8!8( % al 8!88 sustituir a

mini computadoras pequeas en muchas aplicaciones.

>na necesidad importante que aceler$ la evoluci$n del microprocesador de 1( bits

fue la multiplicaci$n % la divisi$n por hardDare. 1stas funciones no est,n disponibles en la

ma%or parte de los microprocesadores de 8 bits, e@cepto el motorola /#(8!-, que puede

multiplicar, pero no dividir. 'ero el microprocesador de 1( bits evolucion$ tambin por

otras razones. Afrece un espacio direccionable de memoria m,s grande que el

microprocesador de 8 bits, lo cual le permite efectuar operaciones mu% comple7as para las

cuales no ha% espacio en ()9 b%tes de memoria. 1l 8!8( % el 8!88 tienen un gran n6mero

:

de registros internos, accesibles a *!! ns, por comparaci$n con los 8! que se necesitan

para llegar hasta un registro en un microprocesador de 8 bits. 1stos registros adicionales

permiten escribir softDare con mucha m,s eficiencia. Asimismo, los programas de

aplicaci$n del softDare (sistemas administrativos basados en datos, listados, procesadores

de palabras % verificadores de ortograf.a) empezaron a requerir m,s de los ()9 b%tes de

memoria disponibles en el microprocesador de 8 bits. 1l momento hab.a llegado para el

microprocesador de 1( bits.

La evoluci$n del microprocesador de 1( bits no termin$ en el 8!8( % el 8!88, sino

que continu$ con la introducci$n del 8!18(, una versi$n altamente integrada del 8!8(. 1l

microprocesador 8!18( de 1( bits es uno de los m,s conocidos de 3ntel. 1l 8!18( se

utiliza en muchas aplicaciones de sistemas de control, pero no como el microprocesador

principal en los sistemas de computadoras personales. +i se encuentra el 8!18( en una

computadora personal es s$lo en una tar7eta enchufable en la tar7eta madre que podr.a

controlar una memoria en disco duro o una interfase para comunicaciones.

1l m,s reciente microprocesador de 1( bits producido por 3ntel es el 8!*8(, una

versi$n me7orada del 8!8(, que contiene una unidad de administraci$n de memoria %

direcciona a una memoria de 1(/ en lugar de 1 / b%te. La velocidad de relo7 del 8!*8( se

ha aumentado tambin a 1( /4z, en las 6ltimas versiones producidas por 3ntel. La versi$n

b,sica del 8!8( % del 8!88 e7ecutaba hasta *. /3' (millones de instrucciones por

segundo), en tanto la versi$n b,sica del 8!*8( e7ecuta hasta 8 /3'.

El microprocesador de 32 bits

La versi$n m,s reciente del microprocesador es el de :* bits (consulte en la tabla 10* la

lista de todos los microprocesadores 3ntel). 3ntel produce en la actualidad dos versiones

principales5 el 8!:8( % el 8!)8(. 1l 8!:8( fue el primer microprocesador de :* bits

producido por 3ntel, cu%a principal venta7a es una frecuencia de relo7 mucho m,s alta (::

)

/4z en el 8!:8( % (( /4z en la versi$n de doble relo7 del 8!)8(), as. como un espacio

mucho ma%or en la memoria ()E b%tes).

1l microprocesador 8!)8( contiene b,sicamente un 8!:8( me7orado, un

coprocesador aritmtico (para la versi$n BF del 8!)8() % una memoria cach interna de

89 b%tes. 1l 8!:8( e7ecuta muchas instrucciones en * ciclos de relo7, mientras que el

8!)8( e7ecuta muchas instrucciones en un solo ciclo de relo7. 1stas me7oras, combinadas

con un relo7 de (( /4z (8!)8(BF*) permiten que las instrucciones se e7ecuten a ) /3',

de acuerdo con 3ntel #orporation. 1sto puede compararse con el 8!8, presentado 1*

aos antes que el 8!)8(, que e7ecutaba las instrucciones a una velocidad de alrededor de

!. /3'. 1stas me7oras en la velocidad continuaron con las versiones m,s nuevas del

microprocesador de :* bits conforme sea disponible. La pr$@ima generaci$n ('entium)

promete lograr velocidades de 1!! /3'.

1.! AR"UI#EC#URA $%ICA DEL MICROPROCEADOR

La programaci$n e interfase eficiente requiere una comprensi$n clara de la arquitectura

b,sica de la familia de microprocesadores % de los sistemas de computaci$n basados en

microprocesadores de 3ntel. 1n esta secci$n se presenta una descripci$n detallada de la

arquitectura b,sica de estos microprocesadores.

Arquitectura interna bsica

Los microprocesadores modernos, igual que los anteriores, buscan instrucciones en la

memoria, pero lo hacen en una forma totalmente nueva. Los microprocesadores modernos

est,n estructurados de modo que contengan muchas m,s unidades internas de

procesamiento, cada una de las cuales efect6a una tarea espec.fica. (?ngase en cuenta

que cada una de estas unidades de procesamiento es, en realidad, un microprocesador

para fines especiales.) 1sto significa que el microprocesador moderno puede a menudo

procesar cierto n6mero de instrucciones en forma simult,nea, en diversas etapas de la

e7ecuci$n. 1sta capacidad recibe a menudo el nombre de paralelismo.

1n la figura 101(a) se ilustra el funcionamiento normal de un 8!8, que es t.pico de

la ma%or parte de los microprocesadores de 8 bits. =$tese que las instrucciones se

recuperan de la memoria con una operaci$n de lectura. Luego, mientras el 8!8 e7ecuta la

instrucci$n, el sistema de memoria est, ocioso. La familia de microprocesadores 3ntel,

empezando con el 8!8( % el 8!88, aprovecha este tiempo de memoria ociosa buscando

con anticipaci$n la siguiente instrucci$n mientras e7ecuta la actual. 1sto acelera la

e7ecuci$n total de un programa.

1n la figura 101(b) se ilustra la secuencia de eventos en el microprocesador 8!)8(.

+e notar, que el canal est, casi siempre ocupado. +e ver, tambin que el 8!)8( tiene

m,s de una unidad interna. #ada unidad est, destinada a funcionar en paralelo con

instrucciones en diversas fases de la e7ecuci$n.

La unidad de interfase del canal (&3>), es la que tiene la funci$n de leer las

instrucciones % de leer o escribir datos entre el microprocesador % la memoria. La salida de

la &3> se conecta con una memoria cach de 89 b%tes, en donde se almacenan los datos

e instrucciones m,s recientes. La salida de la memoria cach alimenta un prerrecuperador

con una cola de :* b%tes de instrucciones. 1sto significa que el microprocesador puede

tener :* b%tes de instrucciones sin e7ecutar en el prerrecuperador. 1n la salida del

prerrecuperador se encuentra un decodificador de instrucciones que de codifica las

instrucciones para que las utilicen las diversas unidades de e7ecuci$n dentro del

microprocesador. 1stas unidades de e7ecuci$n inclu%en la unidad de punto flotante, la

unidad de control % prueba de protecci$n % la unidad de paginaci$n, la unidad de

segmentaci$n % el desplazador de barril, % la AL>.

La figura 10* ilustra la multitud de unidades que est,n dentro del microprocesador

8!)8(. Los microprocesadores m,s antiguos ten.an una sola unidad que controlaba la

interfase del canal % efectuaba todas las operaciones. 1l 8!)8( contiene unidades

especializadas que, en forma individual, efect6an estas funciones a fin de poder realizar

m,s de una operaci$n a la vez. 1n el futuro, estar, contenido m,s de un microprocesador,

como el 8!)8(, en una unidad para incrementar, adicionalmente, la velocidad del sistema

para las secuencias de instrucciones que no son dependientes.

(

Arquitectura del sistema

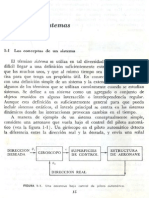

1n la figura 10: se ilustra la arquitectura del sistema de un microprocesador moderno. +e

ver, que las comunicaciones entre el sistema % el microprocesador ocurren por medio de

estos canales5 direcciones, datos % control. 1l canal de direcciones suministra una

direcci$n en la memoria para la memoria del sistema o el espacio de entrada/salida (1G+)

para los dispositivos de 1G+ del sistema. 1l canal de datos transfiere stos entre el

microprocesador % la memoria % los dispositivos de 1G+ conectados en el sistema. 1l canal

de control suministra seales de control que hacen que en la memoria o el espacio de 1G+

efect6en una operaci$n de lectura o de escritura. Las seales de control que hacen

posible la lectura o escritura en la memoria o el espacio de 1G+ var.an mu% poco entre un

miembro % otro de la familia.

2

>n e@amen cuidadoso de la figura 10: revelar, que el ancho del canal de datos % el

de direcciones var.an entre una versi$n % otra del microprocesador. 1n la tabla 10: se

enumeran estas variaciones para comparaci$n % tambin la velocidad de relo7 cuando hizo

su aparici$n el microprocesador. Bespus de la versi$n inicial de cada microprocesador,

se pusieron a disposici$n versiones con frecuencias de relo7 m,s altas.

8

1l ancho del canal de datos determina cu,ntos b%tes se transfieren a la vez entre el

microprocesador % la memoria, mientras que el ancho del canal de direcciones determina

cu,nta memoria direcciona el microprocesador. 1n general, cuanto m,s ancho sea el

canal de datos, m,s r,pido es el microprocesador. 1n las futuras generaciones de

microprocesadores % de microcomputadoras se tendr,n canales de datos de () %, quiz,,

de 1*8 bits.

1.& LA MEMORIA ' EL MICROPROCEADOR

1l espacio de direccionamiento de un sistema basado en un microprocesador, se

denomina memoria l$gica o memoria f.sica. La estructura de la memoria l$gica es

diferente, en casi todos los casos, que la estructura de la memoria f.sica. La memoria

l$gica es el sistema de memoria tal como lo ve el programador, mientras que la memoria

f.sica es la estructura real en el hardDare en el sistema de memoria.

Memoria lgica

1l espacio b,sico de la memoria l$gica es el mismo en todos los microprocesadores 3ntel.

La memoria l$gica se numera por b%tes. 1n la figura 10) se ilustra el mapa de la memoria

l$gica de todos los miembros de la familia 3ntel. +e ver, que la 6nica diferencia es que

algunos miembros contienen m,s memoria que otros. Adem,s, se debe tener en cuenta

que la memoria f.sica puede diferir de la memoria l$gica en muchos sistemas.

La memoria l$gica del 8!8(, 8!88 % 8!18( empieza en la localidad !!!!!4 % llega

hasta la HHHHH4. 1ste intervalo de direcciones especifica el 1/ de b%tes de memoria

disponible en estos sistemas. La memoria l$gica del 8!*8( % el 8!:8(+F empieza en la

localidad de memoria !!!!!!4 % llega hasta la ubicaci$n HHHHHH4 para tener un total de

1(/ b%tes de memoria. 1l 8!:8(+L contiene :*/b%tes de memoria que empiezan en la

localidad !!!!!!4 % terminan en la 1HHHHHH4. 1l 8!:8(BF, 8!)8(+F % 8!)8(BF

contienen memoria que empieza en la localidad !!!!!!!!4 % termina en la HHHHHHHH4,

para un total de )E b%tes de memoria (1E I 1,024M y 1M= 1,024K).

-

#uando estos microprocesadores direccionan una palabra de 1( bits en la

memoria, se accesan dos b%tes consecutivos. 'or e7emplo, la palabra en la localidad

!!1**4 se almacena en los b%tes !!1**4 % !!1*:4C el b%te menos significativo se

almacena en la localidad !!1**4. +i se accesa a una palabra doble de :* bits, esta

palabra doble la contienen cuatro b%tes consecutivos. 'or e7emplo, la doble palabra

almacenada en la localidad !!1*!4 se almacena en los b%tes !!1*!4, !!1*14, !!1**4 %

!!1*:4C el b%te menos significativo se almacena en !!1*!4 % el b%te m,s significativo en

!!1*:4.

Memoria fsica

Las memorias f.sicas de los miembros de la familia 3ntel difieren en ancho. La

memoria del 8!88 es de 8 bits de anchoC las memorias del 8!8(, 8!18(, 8!*8( % 8!:8(+F

tienen 1( bits de anchoC las memorias del 8!:8(BF % 8!)8( son de :* bits de ancho. 'ara

la programaci$n, no ha% diferencia en el ancho de la memoria porque la memoria l$gica

siempre es de 8 bits de anchoC pero, como se puede ver en la figura 10, ha% una

diferencia para el diseador del hardDare.

1!

La memoria est, organizada en bancos de memoria en todas las versiones del

microprocesador, e@cepto el 8!88 que tiene un solo banco de memoria. >n banco de

memoria es una secci$n de 8 bits de ancho. Los microprocesadores de 1( bits tienen dos

bancos de memoria para formar una secci$n de memoria de 1( bits de ancho, , la cual se

direcciona por b%tes o por palabras. Los microprocesadores de :* bits tienen cuatro de

bancos de memoria, pero se les direcciona como b%tes, palabras o dobles palabras.

a memoria en la computadora personal

#ualquier estudio de la familia 3ntel requiere entender la estructura de la memoria de la

computadora personal. Bebido a que la computadora personal original estuvo basada en

el microprocesador 8!88, se considera que su memoria principal tiene una longitud de 1/

b%te. 1sta memoria principal se llama memoria real. =unca se toler$ una ampliaci$n de la

memoria hasta que L3/ (Lotus03ntel0/icrosoft) crearon un est,ndar para un sistema de

memoria ampliada (1/+).

La memoria ampliada se coloc$ en un marco de pgina vac.o (()9 b%tes) ubicado

entre la memoria de s$lo lectura (JA/) del &3A+ (+istema b,sico de entradaGsalida) en el

11

sistema. #on este marco de p,gina de ()9 b%tes, el est,ndar L3/ permite acceso a un

n6mero ilimitado de p,ginas de memoria ampliada de ()9 b%tes, si bien el acceso a esas

p,ginas es lento. 1l sistema de memoria ampliada se volvi$ obsoleto con el advenimiento

del microprocesador 8!*8( % otros m,s nuevos, aunque todav.a est, soportado por los

antiguos sistemas basados en 8!8( % 8!88.

#on los nuevos 8!*8(, 8!:8( K 8!)8( se pueden direccionar memorias por encima

del primer b%te 1/. 1sta memoria adicional, llamada sistema de memoria etendida (F/+)

contiene 1/ b%tes adicionales en el sistema de 8!*8( % 8!:8(+F, % ),!-/ b%tes en los

sistemas de 8!:8(BF % 8!)8(. 1l sistema F/+ ha sustituido al sistema 1/+ de las

primeras computadoras personales.

1n la figura 10( se muestra un mapa de memoria de una computadora personal con

la memoria etiquetada por zonas. Los primeros ()!9 b%tes del sistema de memoria en

todas las computadoras personales, se llama el rea de programa transitorio (?'A). 1l

?'A contiene una memoria JA/ (lectura y escritura) para almacenar las aplicaciones de

softDare, el sistema operativo % diversos programas que controlan los dispositivos de 1G+.

Bespus del ?'A est, almacenada la zona de sistemas que contiene varios &3A+

(sistema bsico de entrada/salida) para controlar el sistema, una JA/ de video % zonas

abiertas que se pueden utilizar para un marco de p,gina de 1/+ % con opciones

instalables en el sistema de la computadora. 1ncima de esta zona de memoria de 1/

b%te, est, el sistema de memoria e@tendida, que tiene sistemas para discos en cacheo %

otros segmentos de datos definidos por el sistema operativo.

1.( OR)ANI*ACIN IN#ERNA

La programaci$n requiere un claro entendimiento de la estructura de los registros internos

de la familia de microprocesadores 3ntel. 1n la figura 102 se ilustra el arreglo de registros

internos del microprocesador. 1ste arreglo se aplica a todas las versiones del

microprocesador. ?enga en cuenta que las partes sombreadas s$lo est,n disponibles en

1*

los microprocesadores 8!:8( % 8!)8(. 1l arreglo de registros internos consta de tres

grupos de registros5 registros de uso general, apuntadores % registros de .ndice % registros

de segmentos. Adem,s de esos grupos, ha% tambin un registro de banderas que seala

las condiciones respecto al funcionamiento de la unidad aritmtica % l$gica (AL>).

!egistros de propsito general

Los registros de prop!sito general se utilizan en la forma en que desee el programador.

#ada registro para uso general se puede direccionar como un, registro de :* bits (1AF,

1&F, 1#F % 1BF), como uno de 1( bits (AF, &F, #F % BF) o como uno de 8 bits (A4, AL,

&4, &L, #4, #L, B4L % BL). +e debe tener en cuenta que s$lo el 8!:8( % el 8!:8)

contienen el grupo de registros de :* bits. 1n algunas de las instrucciones que se e@plican

en cap.tulos posteriores tambin se utilizan los registros de uso general para tareas

espec.ficas. 'or esta raz$n, a cada uno se le da su nombre (Acumulador, &ase, #ontar %

Batos). 1n lengua7e ensamblador, al registro de uso general siempre se le denomina con

combinaciones de dos o de tres letras. 'or e7emplo, al acumulador se le denomina 1AF,

AF, A4 o AL.

Las funciones primarias de los registros de prop$sito general inclu%en5

A" #Acumulador$% a menudo conserva el resultado temporal despus de una operaci$n

aritmtica o l$gica. ?ambin se le direcciona como 1AF, A4 o AL.

&" #&ase$% a menudo conserva la direcci$n base (desplazamiento) de los datos que ha%

en la memoria o la direcci$n base de una tabla de datos referenciados por la instrucci$n

para convertir (FLA?). ?ambin se le direcciona como, 1&F, &4 o &L.

'" #'ontador$% contiene el conteo de ciertas instrucciones para corrimientos (#L) % rota0

ciones del n6mero de b%te s (#F) para las operaciones repetidas de cadena % un contador

(#F o 1#F) para la instrucci$n LAA'. ?ambin se le direcciona como 1#F, #4 o #L.

D+ #(atos$% es un registro de uso general que tambin contiene la parte mas significativa

de un producto despus de una multiplicaci$n de 1( $ :* bitsC la parte mas significativa del

dividendo antes de la divisi$n % el n6mero de puerto de 1G+ para instrucci$n variable de

1G+. ?ambin se le direcciona como 1BF, B4 o BL.

1:

!egistros apuntadores e ndices

Aunque los registros apuntadores e .ndices son tambin de uso general, se utilizan m,s a

menudo para apuntar a la localidad de la memoria que contiene los datos del operando de

muchas instrucciones.

Los registros apuntadores e .ndices inclu%en5

)* #Apuntador de pila$+ +e emplea para direccionar datos en una pila de memoria de

L3HA (6ltimo en entrar, primero en salir). 1sto ocurre m,s a menudo cuando se e7ecutan

1)

las instrucciones '>+4 % 'A' cuando se llama (#ALL) o se regresa (J1?) de una

subrutina desde un programa principal. 1ste registro es tambin el registro 1+' de :* bits.

&* #Apuntador de base$+ 1s un apuntador de uso general que se utiliza a menudo para

direccionar a una matriz de datos en una pila de memoria. 1ste registro es tambin el

registro 1&' de :* bits.

), #,ndice de fuente$+ +e emplea para direccionar datos fuente en forma indirecta para

utilizarlos con las instrucciones de cadenas o arreglos. 1ste registro es tambin el registro

1+3 de :* bits.

(, #,ndice de destino$+ +e suele emplear para direccionar datos destino en forma

indirecta, para utilizarlos con las instrucciones de cadenas o arreglos. 1ste registro es

tambin el registro 1B3 de :* bits.

,* #Apuntador de instrucciones$+ +e utiliza siempre para direccionar a la siguiente

instrucci$n que va a e7ecutar el microprocesador. 'ara formar la localidad real de la

siguiente instrucci$n se suma el contenido de 3' con #+ (por) 1!4, como se describe en la

siguiente secci$n. 1ste registro es tambin el registro 13' de :* bits.

A menudo se hace direccionamiento indirecto de datos por medio de cuatro de estos cinco

registros de 1( bits, pero nunca con el apuntador de instrucciones.

El registro de banderas

Las banderas indican la condici$n del microprocesador a la vez que controlan su

funcionamiento. 1n la figura 108 se ilustran los registros de banderas de todas las

versiones de los microprocesadores 8!8( a 8!)8(. +e debe tener en cuenta que las

banderas son compatibles hacia arriba desde el 8!8(G8!88 hasta el 8!)8(. 1l 8!8(08!*8(

contiene un registro de banderas, HLAE (1( bits) % los 8!:8(08!)8( contienen un registro

1HLAE (registro de banderas e@tendido, de :* bits).

Los bits de bandera cambian despus de e7ecutar muchas de las instrucciones

aritmticas % l$gicas. Algunas de las banderas se utilizan para controlar ciertas

caracter.sticas del microprocesador. A continuaci$n aparece una lista con cada bit de

bandera, con una breve descripci$n de su funci$n. A medida que se dan a conocer

instrucciones en cap.tulos posteriores, se dar,n detalles adicionales de los bits

indicadores.

1

' #acarreo$+ 3ndica un acarreo despus de una suma o un LprstamoL despus de una

resta. La bandera de acarreo tambin indica condiciones de error en ciertos programas %

procedimientos.

* #paridad$+ 1s un cero para una paridad impar % un 1 para paridad par. La paridad es un

conteo de LunosL e@presado como un n6mero par o impar. 'or e7emplo, si un n6mero

1(

contiene : bits con uno binario, tiene paridad impar. +i un n6mero contiene cero bits de

uno, se considera que tiene paridad par.

A #acarreo au-iliar$+ ?iene un acarreo despus de una suma o un LprstamoL despus de

una resta entre las posiciones de los bits : % ) en el resultado. 1ste indicador mu%

especializado se prueba con las instrucciones BAA % BA+ para a7ustar el valor de AL

despus de una suma o resta &#B. 1l microprocesador, no utiliza en otra forma el bit de

bandera A.

. #cero$+ 3ndica que el resultado de una operaci$n aritmtica o l$gica es cero. +i M I 1, el

resultado es cero % si M I !, el resultado no es cero.

) #signo$+ 3ndica el signo aritmtico del resultado despus de una suma o una resta. +i

+I1, la bandera de signo se activa % el resultado es negativo. +i +I!, la bandera de signo

se des activa % el resultado es positivo. +e debe tener en cuenta que el valor de la

posici$n del bit m,s significativo se coloca en el bit de signo para cualquier instrucci$n que

afecte las banderas.

/ #trampa$+ #uando se activa la bandera de trampa, se habilita la caracter.stica de

depuraci$n del microprocesador. /,s adelante aparecen ma%ores detalles de esta

caracter.stica.

I #interrupcin$+ #ontrola el funcionamiento de la terminal de la entrada de 3=?J

(interrupci$n). +i II1, se habilita la entrada 3=?J % si II!, se deshabilita la entrada 3=?J.

1l estado de la bandera I se controla con las instrucciones +?3 (activar la bandera I) % #L3

(desactivar la bandera I).

( #direccin$+ #ontrola la selecci$n de incremento o decremento de los registros B3 o +3

durante las instrucciones de cadenas o arreglos. +i BI1 ha% decremento autom,tico en

los registros % si BI! ha% incremento. La bandera B se activa con las instrucciones +?B

(activar direcci$n) o se borra con #LB (quitar direcci$n).

0 #sobreflu1o$+ 1s una condici$n que ocurre cuando se suman o restan n6meros con

signo. >n sobreflu7o indica que el resultado ha e@cedido de la capacidad de la m,quina.

'or e7emplo, si se suma un 2H4 (N1*2) a !14 (N1) el resultado es 8!4 (01*8)

1

. 1ste

resultado representa una situaci$n de sobreflu7o sealado por la bandera para la suma

con signo. 'ara operaciones sin signo, no se toma en cuenta esta bandera.

,0* #ni2el de pri2ilegio de entrada3salida$+ +e utiliza en el funcionamiento en modo

protegido para seleccionar el nivel de privilegio de los dispositivos de 1G+. +i el nivel de

privilegio actual es de ma%or prioridad que el del 3A'LC entonces se e7ecuta la operaci$n

de 1G+. +i el nivel del 3A'L es menor que el nivel de privilegio actual, ocurre una

1

"sto es para operaciones con signo magnitud (recordar "lectr!nica #igital 1), donde en un byte ($ bits binarios) %ue es utili&ado para

representar un numero 'eadecimal, se utili&a el bits ms signi(icati)o para representar el signo, si este bits es 1 el n*mero es negati)o

y si es 0 es numero es positi)o.

12

interrupci$n % ocasiona que se suspenda la e7ecuci$n. +e debe tener en cuenta que un

3A'L de !! es el de ma%or prioridad % un 3A'L de 11 es el menor prioridad.

4/ #tarea anidada$+ 3ndica que la tarea que est, en curso est, anidada dentro de otra

tarea en el funcionamiento en modo protegido. 1sta bandera se activa cuando el softDare

anida la tarea.

!5 #reanudar$+ +e emplea con la depuraci$n para controlar la reanudaci$n de la e7ecuci$n

despus de la siguiente instrucci$n.

6M #modo 2irtual$+ +elecciona el funcionamiento en modo virtual en un sistema con modo

protegido. >n sistema de modo virtual permite m6ltiples particiones de la memoria con

BA+.

A' #comprobacin de alineacin$+ +i se direcciona a una palabra o palabra doble en

una direcci$n impar (b%te) o no m6ltiplo de cuatro para doble palabra, se activa esta

bandera. +$lo el microprocesador 8!)8(+F contiene el bit de comprobaci$n de alineaci$n

cu%o empleo primordial es con el coprocesador numrico ane@o.

!egistros de segmentos

>nos registros adicionales, a los que se da el nombre de registros de segmentos, generan

direcciones en la memoria 7unto con otros registros en el microprocesador. 4a% ) o (

registros de segmentos en las diversas versiones de los microprocesadores 8!8(08!)8(.

>n registro de segmento funciona de una manera diferente en el modo0real, por

comparaci$n con el funcionamiento del microprocesador en modo protegido. /,s adelante

en este cap.tulo se dan detalles de su funci$n en modos real % protegido. A continuaci$n

aparece una lista de cada registro de segmento 7unto con su funci$n en el sistema5

') #cdigo$+ 1l segmento de c$digo es una secci$n de la memoria que tiene los

programas % procedimientos utilizados por los programas. 1l registro de segmento de

c$digo define la direcci$n inicial de la secci$n de memoria que tiene el c$digo. 1n el

funcionamiento en modo real, define el inicio de una secci$n de memoria de ()9 b%tes %

en el modo protegido selecciona un descriptor que describe la direcci$n inicial % la longitud

de la secci$n de memoria que tiene el c$digo. 1l segmento de c$digo esta limitado a ()9

b%tes de longitud en el 8!8808!*8( % a )E b%tes en el 8!:8(G8!)8(.

() #datos$+ 1l segmento de datos es una secci$n de la memoria que contiene la ma%or

parte de los datos utilizados por un programa. +e les accesa en el segmento de datos con

un desplazamiento o con el contenido de otros registros que tienen la direcci$n del

desplazamiento.

E) #e-tra o adicional$+ 1l segmento e@tra o adicional de datos lo utilizan algunas instruc0

ciones para cadenas.

18

)) #pila$+ 1l segmento de pila define la superficie de la memoria utilizada para la pila. La

ubicaci$n del punto inicial de entrada a la pila, se determina por el registro apuntador de la

pila. 1l registro &' tambin direcciona los datos que ha% dentro del segmento de pila.

5) 7 8)+ 1stos registros de segmento adicionales est,n disponibles en los

microprocesadores 8!:8( % 8!)8( a fin de contar con dos segmentos adicionales de

memoria para acceso con los programas.

1., DIRECCIONAMIEN#O DE LA MEMORIA

(,!E'',04AM,E4/0 E4 M0(0 !EA

Los microprocesadores 8!*8(08!)8( funcionan en el modo real o en el protegido. Los

8!8(, 8!88 % 8!18( s$lo funcionan en el modo real. 1n esta secci$n se detalla el

funcionamiento del microprocesador en el modo real. 1l funcionamiento en el modo real

permite que el microprocesador s$lo direccione al primer 1/ b%te de espacio en la

memoria, aunque sea un microprocesador 8!)8(. 1n los sistemas de funcionamiento

/+BA+ o '#BA+ se supone que el microprocesador funciona en el modo real en todo

momento. 1l funcionamiento en el modo real permite que el softDare de aplicaci$n escrito

para el 8!8( u 8!88 que s$lo contienen 1 / b%te de memoria, funcionen en los

microprocesadores 8!*8(, 8!:8( % 8!)8(. 1n todos los casos, cada uno de los

microprocesadores empieza a funcionar en modo real en forma impl.cita (default), siempre

que se aplica la corriente o si se restablece el microprocesador.

e-.entos / despla0a.ientos

>na direcci$n de segmento % una direcci$n de desplazamiento, generan una direcci$n en

la memoria en el modo real. ?odas las direcciones en la memoria en modo real consisten

de un segmento % un desplazamiento. 1l segmento ubicado en uno de los registros de

segmento

*

, define la direcci$n inicial de cualquier segmento de memoria de ()9 b%tes. La

direcci$n de desplazamiento selecciona una localidad dentro del segmento de memoria de

()9 b%tes. 1n la figura 10-, se ilustra c$mo el esquema de direccionamiento de segmento

m,s desplazamiento selecciona una localidad en la memoria. 1n esta ilustraci$n se

muestra un segmento de memoria que empieza en la localidad 1!!!!4 % termina en la

1HHHH4, de ()9 b%tes de longitud. ?ambin se muestra la forma en que un

despla&amiento de H!!!4 selecciona la localidad 1H!!!4 en el sistema de la memoria. +e

ver, que la direcci$n de desplazamiento es la distancia desde el inicio del segmento.

1l registro de segmento de la figura 10-, contiene 1!!!4, con lo que apunta a una

direcci$n inicial 1!!!!4. 1n el modo real, a cada registro de segmento se le agrega un 0+

en su e@tremo derecho, para formar una direcci$n de memoria de *! bits que le permite

*

Los registros internos de los ' de 1( bits dan los ()9, si el bus de dato es de 8 bits tenemos los ()9b%tes

1-

colocar el inicio del segmento en casi cualquier localidad dentro del primer /b%te de

memoria. 'or e7emplo, si un segmento de registro contiene una 1*!!4, direcciona a un

segmento de memoria de ()9 b%tes que empieza en la localidad 1*!!!4. Asimismo, si un

registro de segmento contiene una 1*!14 direcciona a un segmento de memoria que

comienza en la localidad 1*!1!4. Bebido al !4, que se agrega en forma interna, los

segmentos pueden empezar en cualquier m6ltiplo de 1( b%tes en el sistema de memoria.

A menudo, a este l.mite de 1( b%tes se le llama un prra(o de memoria.

Bebido a que un segmento de memoria en modo real tiene ()9 b%tes de longitud,

una vez que se conoce la direcci$n inicial, para encontrar la direcci$n final se agrega una

HHHH4 a la direcci$n inicial. 'or e7emplo, si un registro de segmento contiene ,000+, la

primera direcci$n en el segmento es :!!!!4 % la 6ltima direcci$n es :!!!!4 N HHHH4 o

:HHHH4. 1n la tabla 10) se presentan algunos e7emplos de contenidos de registros de

segmento % las direcciones inicial % final de los segmentos de memoria, seleccionadas por

cada direcci$n de segmento.

#A$LA 11( 17emplos de direcciones

de segmento -egistro de segmento #irecci!n inicial #irecci!n (inal

*!!!4 *!!!!4 *HHHH4

*1!!4 *1!!!4 :!HHH4

A&!!4 A&!!!& &AHHH4

1*:)4 1*:)!4 **::H4

La direcci$n del desplazamiento se suma a la del segmento para ubicar una

direcci$n en el segmento. 'or e7emplo, si la direcci$n de segmento es 1!!!4 % la direcci$n

de desplazamiento es 2000+, el microprocesador direcciona la localidad de memoria

1*!!!4. La direcci$n del segmento % del desplazamiento, a veces, se escribe 1000.2000

para una direcci$n de segmento de 1000+ y un desplazamiento de 2000+.

*!

Jegistros de segmento % desplazamiento impl.citos

1l microprocesador tiene un grupo de reglas que se aplican siempre que se direcciona a la

memoria. 1stas reglas, que se aplican en el modo real o en el protegido, definen la

combinaci$n de registro de segmento % de desplazamiento, que se utilizan en ciertos

modos de direccionamiento. 'or e7emplo, el registro de segmento de c$digo se emplea

siempre con el apuntador de instrucciones para direccionar la siguiente instrucci$n a

e7ecutar en un programa. 1sta combinaci$n es #+53' o #+513', seg6n sean el

microprocesador % el modo de funcionamiento. 1l registro de segmento de c$digo define el

principio de un segmento de c$digo % el apuntador de instrucciones apunta a la siguiente

instrucci$n dentro del segmento de c$digo a e7ecutar por el microprocesador. 'or e7emplo,

si #+I1)!!4C 3'G13'I1*!!4, el microprocesador busca % lee la siguiente instrucci$n en la

localidad 1)!!!4 N 1*!!4 o sea 1*!!4 en la memoria.

Atro direccionamiento impl.cito es el de la pila. +e hace referencia a los datos de la

pila por medio del segmento de pila % por localidad de la memoria a la cual direccciona el

apuntador de la pila (+'G1+') o el apuntador de base. 1stas combinaciones se refieren

como ++5+' (++51+') o ++5&' (++51&'). 'or e7emplo, si ++I2000+ y &'G1&'I,000+,

el microprocesador direcciona a la localidad *:!!!4 en la memoria del segmento de pila

direccionada por el registro &'G1&'. +e debe tener en cuenta que en el modo real, s$lo

los 1( bits en la e@trema derecha del registro e@tendido direccionan a una localidad dentro

del segmento de memoria. =unca ponga un n6mero ma%or que HHHH4 en un registro de

desplazamiento si el microprocesador funciona en el modo real. +i en el modo real se

direcciona a una memoria ma%or que 1!!!!!4 (o 1!HH1H4 si est, instalado el sistema

43/1/) ocasionar, que el microprocesador interrumpa el programa e indique un error.

1n la tabla 10 se ilustran otros direccionamientos impl.citos para la memoria para

microprocesadores 8!8(08!*8(. 1n la tabla 10( se muestran los direccionamientos

impl.citos en los microprocesadores 8!:8( % 8!)8(. +e debe tener en cuenta que los

microprocesadores 8!:8( % 8!)8( tienen una selecci$n mucho ma%or de las

combinaciones de segmento % desplazamiento que los microprocesadores 8!8(08!*8(.

#a2la 11, +egmento % desplazamientos impl.citos

del 8!8(08!*8(

#a2la 113 +egmento % desplazamiento, impl.citos

del 8!:8( % 8!)8(

*1

Los 8!8(08!*8( permiten tener cuatro segmentos de memoriaC el 8!:8( % el 8!)8(

permiten ( segmentos de memoria. 1n la figura 101! se ilustra un sistema que contiene )

segmentos de memoria. +e debe tener en cuenta que los segmentos de memoria pueden

tocarse o incluso traslaparse si no se requieren ()9 b%tes de memoria para un segmento.

'iense que los segmentos son como ventanas que se pueden mover en cualquier

superficie de la memoria para accesar a datos o c$digo.

+uponga que un programa de aplicaci$n requiere 1!!!4 b%tes de memoria para su

c$digo, 1-!4 b%tes de memoria para sus datos % *!!4 b%tes de memoria para su pila.

1sta aplicaci$n no requiere un segmento adicional. #uando el Bos coloca este programa

en la memoria, se carga el ?'A en la primera zona disponible encima de los mane7adores

% otros programas de la ?'A. 1n la figura 1011 se muestra la forma en que esta aplicaci$n

se almacena en el sistema de memoria. Los segmentos muestran una superposici$n o

traslape debido a que la cantidad de datos que ha% en ellos no requiere ()9 b%tes de

memoria. La vista lateral de los segmentos muestra con claridad el traslape % la forma en

que los segmentos se pueden desplazar a cualquier parte de la memoria. 'or fortuna para

todos, el BA+ calcula % asigna las direcciones en el segmento. 1sto se e@plica en un

**

cap.tulo m,s adelante en que se dan detalles del funcionamiento del ensamblador, del

&3A+ % del BA+ para un programa en lengua7e ensamblador.

1l direccionamiento de segmento % desplazamiento permite la relocalizaci$n

1l sistema de direccionamiento de segmento % desplazamiento parece ser demasiado

complicado. +. lo es pero tambin ofrece una venta7a al sistema. 1l sistema un tanto

complicado de direccionamiento de segmento % desplazamiento, permite el cambio de

lugar de los programas en el sistema de memoria. >n programa relocali&able es el que se

puede poner en cualquier zona de la memoria % e7ecutarlo sin cambio. Los datos

relocali&ables son los que se pueden colocar en cualquier zona de la memoria % utilizarlos

sin ning6n cambio en el programa. 1l sistema de direccionamiento de segmento %

desplazamiento permite relocalizar los programas % los datos sin cambiar nada,

absolutamente, en un programa o en los datos. 1sto es perfecto para utilizarlo en un

*:

sistema de computadora para uso general, cuando no todas las m,quinas contienen las

mismas zonas de memoria. La estructura de la memoria de la computadora personal es

diferente entre una m,quina % otra, por lo cual requieren softDare % datos que se puedan

relocalizar.

Bebido a que las localidades de memoria se les direcciona dentro de un segmento

con una direcci$n de desplazamiento, el segmento se puede cambiar sin cambiar ninguna

de las direcciones de desplazamiento. 'ara lograrlo, se mueve todo el programa, como

bloque, a una nueva zona % s$lo se cambia el contenido de los registros de segmento. +i

una instrucci$n est, ) b%tes arriba del inicio del segmento, su direcci$n de desplazamiento

es ). +i se mueve todo el programa a una nueva zona en la memoria, esta direcci$n de

desplazamiento ) todav.a apunta a los ) b%tes que est,n arriba del inicio del segmento. Lo

6nico que se necesita cambiar es el contenido del registro de segmento para relocalizar el

programa en una nueva zona de la memoria. 1sta facilidad de relocalizaci$n ha hecho que

las computadoras personales basadas en microprocesadores de 3ntel sean mu% potentes %

mu% comunes. +i no se tuviera esta caracter.stica, habr.a que volver a escribir o alterar un

programa antes de moverlo. 1sto necesitar, tiempo adicional o requerir.a un programa

para cada una de las muchas configuraciones diferentes de los sistemas de computadora.

(,!E'',04AM,E4/0 (E A MEM0!,A E4 M0(0 *!0/E8,(0

1l direccionamiento de la memoria en modo protegido (s$lo 8!*8(, 8!:8( % 8!)8()

permite acceso a los datos % programas ubicados arriba del primer /b%te de memoria. 1l

direccionamiento de esta secci$n e@tendida del sistema de memoria (la memoria encima

del primer /b%te de memoria se denomina memoria etendida o /M0), requiere un

cambio en el sistema de direccionamiento de segmento % desplazamiento, utilizado con el

direccionamiento de la memoria en modo real. #uando se direcciona a los datos %

programas en la memoria ampliada, todav.a se utilizan la direcci$n de desplazamiento

para accesar la informaci$n ubicada dentro del segmento. La direcci$n del segmento, que

se describi$ en relaci$n con el direccionamiento de la memoria en modo real, %a no est,

presente en el modo protegido. 1n lugar de la direcci$n del segmento, el registro del

segmento contiene un selector que selecciona un descriptor1 ste describe la ubicaci$n,

longitud % derechos de acceso al segmento de memoria. Bebido a que el registro de

segmento % la direcci$n de desplazamiento todav.a accesan a la memoria, las

instrucciones en el modo protegido se ven iguales que en el modo real. 1n la pr,ctica, la

ma%or parte de los programas escritos para funcionar en el modo real, funcionar,n sin

ning6n cambio en el modo protegido. La diferencia entre los modos est, en la forma en

que el registro de segmento accesa el segmento de memoria.

electores / descriptores

1l selector ubicado en el registro del segmento selecciona a uno de los 81-* descriptores

en la tabla de descriptores. 1l descriptor describe la ubicaci$n, longitud % derechos de

acceso de un segmento de memoria. 1l registro de segmento, en forma indirecta, todav.a

*)

selecciona un segmento de memoria, pero no lo hace en forma directa como en el modo

real.

+e utilizan dos tablas de descriptores con los registros de segmento5 una contiene

descriptores globales %, la otra, contiene descriptores locales. Los descriptores globales

contienen segmentos que se aplican a todos los programas, mientras que los descriptores

locales suelen ser e@clusivos de una aplicaci$n. #ada tabla de descriptores contiene 8,1-*

descriptores con lo cual ha% disponible en cualquier momento un total de 1(,:8)

descriptores. Bebido a que un descriptor describe un segmento de memoria, ello permite

describir hasta 1(,:8) segmentos de memoria para cada aplicaci$n.

1n la figura 101* se muestra el formato de un descriptor para los microprocesadores

8!*8( % 8!:8(G8!)8(. +e ver, que cada descriptor tiene una longitud de 8 b%tes, con lo

cual las tablas de descriptores globales % locales tienen, cada una, una longitud m,@ima

de ()9 b%tes. Los descriptores para el 8!*8( % los 8!:8(G8!)8( tienen ligeras diferencias

entre s., pero el descriptor 8!*8( es compatible en forma ascendente con los

microprocesadores 8!:8( % 8!)8(.

La parte de direcci$n base del descriptor, se utiliza para indicar la ubicaci$n del

inicio del segmento de memoria. 1n el microprocesador 8!*8(, la direcci$n de base es

una direcci$n de *) bits, con lo cual los segmentos pueden empezar en cualquiera de sus

1(/ b%tes de memoria. 1n el 8!:8( % 8!)8( se utiliza una direcci$n de base de :* bits,

que permite que los segmentos empiecen en cualquiera de las localidades de los )E b%tes

de memoria. +e ver, c$mo la direcci$n base del descriptor del 8!*8( es compatible hacia

arriba con el descriptor del 8!:8(G8!)8(.

1l l.mite de segmento contiene la 6ltima direcci$n de desplazamiento que se

encuentre en un segmento. 'or e7emplo, si un segmento empieza en la localidad de

memoria H!!!!4 % termina en la ubicaci$n H!!!HH4, la direcci$n base es H!!!!!4 % el

l.mite es HH4. 1n el microprocesador 8!*8(, la direcci$n base es H!!!!!4 % el l.mite es

!!H4. 1n los microprocesadores 8!:8(G8!)8(, la direcci$n de base es !!H!!!!!4 % el

l.mite es !!!HH4. +e ver, que el l.mite para el 8!*8( es de 1( bits % el l.mite para

8!:8(G8!)8( es de *! bits. 1l 8!*8( accesa a segmentos de memoria que tengan

longitud entre 1 b%te % ()9 b%tes. 1l 8!:8(G8!)8( accesan a segmentos de memoria con

longitud desde 1 b%te hasta 1/ b%te o desde )9 b%tes hasta )E b%tes.

*

1n el descriptor de 8!:8(G8!)8( ha% una caracter.stica que no tiene el descriptor

del 8!*8(5 el bit E o bit de granularidad. +i EIA, el l.mite especifica un l.mite de segmento

con longitud entre 1 b%te % 1/ b%te de longitud. +i EI1, el valor del l.mite se multiplica por

)9 b%tes. +i EI1, el l.mite puede ser cualquier m6ltiplo de )9 b%tes. 1sto permite tener

una longitud de segmento entre )9 % )E b%tes, en etapas de )9 b%tes. La raz$n de que

esta longitud de segmento sea de ()9 b%tes en el 8!*8(, es que la direcci$n de

desplazamiento es siempre de 1( bits, mientras que la direcci$n de desplazamiento

cuando se traba7a con 8!:8(G8!)8( en modo protegido, es de :* bits. 1sta direcci$n de

desplazamiento de :* bits permite tener longitudes de segmento de )E b%tes % la

direcci$n de desplazamiento de 1( bits, permite tener segmentos de ()9 b%tes de

longitud.

1l bit AO en el descriptor de 8!:8(G8!)8( lo utiliza el sistema operativo e indica que

el segmento est, disponible (AOI1) o no disponible (AOI!). 1l bit B indica la forma en que

las instrucciones del 8!:8(G8!)8( accesan al registro % a los datos de memoria en el

modo protegido. +i BI!, entonces en el 8!:8(G8!)8( se supone que las instrucciones son

de 1( bits, compatibles con los microprocesadores 8!8(08!*8(. 1sto significa que en las

instrucciones emplean direcciones de desplazamiento de 1( bits % registros de 1( bits.

1ste modo, a menudo, se llama modo de instrucci$n de 1( bits. +i BI1, entonces en el

8!:8(G8!)8( supone que las instrucciones son de :* bits. 1l modo de instrucci!n de :*

bits, supone que todos los desplazamientos, as. como todos los registros, son de :* bits.

1l sistema operativo /+BA+ o el '#BA+ requieren que las instrucciones se utilicen

siempre en el modo de instrucci$n de 1( bits.

1l b%te de derechos de acceso (figura 101:) controla el acceso al segmento de

memoria. 1ste b%te describe c$mo funciona el segmento en el sistema. +e puede ver lo

completo que es el control del segmento. +i el segmento es de datos, se puede especificar

el sentido del crecimiento. +i el segmento crece m,s all, de su l.mite, se interrumpe el

programa del microprocesador. 1s posible especificar tambin si en un segmento de datos

se puede escribir o est, protegido contra escritura. 1l segmento de c$digo se controla en

una forma similar % se le puede inhibir la lectura.

*(

Los descriptores los elige en la tabla de descriptores el registro de segmento. 1n la

figura 101) se ilustra c$mo funciona el registro de segmento en el sistema con modo

protegido. 1l registro de segmento contiene un campo selector de 1: bits, un bit selector

en la tabla % un campo del nivel de privilegio solicitado. 1l selector de 1: bits escoge uno

de los 8,1-* descriptores en la tabla de descriptores. 1l bit ?3 selecciona, %a sea la tabla

de descriptores globales (?3I!) o la tabla de descriptores locales (?3I1). 1l nivel de

privilegio solicitado (J'L) le solicita el grado de privilegio de acceso a un segmento de la

memoria. 1l grado m,s alto de privilegio es !! % el m,s ba7o es 11. +i el grado de

privilegio solicitado concuerda o tiene una prioridad ma%or que el grado de privilegio

establecido por el b%te de derechos de acceso, se concede el acceso. 'or e7emplo, si el

grado de privilegio solicitado es 1! % el b%te de derechos de acceso, tiene el grado de

privilegio en 11, entonces se logra el acceso porque 1! es un grado de privilegio con

ma%or prioridad que el 11. Los grados de privilegio se emplean en instalaciones con

usuarios m6ltiples.

1n la figura 101 se ilustra la forma en que el registro de segmento, que contenga

un se lector, selecciona un descriptor en la tabla de descriptores globales. La entrada en la

tabla de descriptores globales selecciona un segmento en el sistema de memoria. 1n esta

ilustraci$n, B+ contiene !!!84, que accesa al descriptor n6mero 1 en la tabla de

descriptores locales, con el empleo de un nivel de privilegio solicitado de !!. 1l descriptor

n6mero 1 contiene un descriptor 8!*8( que define la direcci$n de base como 1!!!!!4,

con un l.mite de segmento de !!HH4. 1sto significa que un valor de !!!8 en B+, hace que

el microprocesador utilice las localidades de la memoria 1!!!!!4 hasta 1!!!HH4 para el

segmento de datos con la tabla de descriptor de este e7emplo.

*2

Re-istros in4isi2les para el pro-ra.a

Las tablas de descriptores globales % locales se encuentran en el sistema de memoria.

'ara poder accesar a la direcci$n de estas tablas % especificada, el 8!*8(, 8!:8( % 8!)8(

contienen registros invisibles para el programa. A los registros in)isibles para el programa

no se les direcciona en forma directa por el softDare del sistema. 1n la figura 101( se

ilustran los registros invisibles para el programa tal como aparecen en los

microprocesadores 8!*8(, 8!:8( % 8!)8(. 1stos registros controlan al microprocesador

cuando funciona en el modo protegido.

#ada registro de segmento contiene una parte invisible para el programa que se

emplea en el modo protegido. 1s una memoria cach que se carga con la direcci$n de

base, el l.mite % los derechos de acceso cada vez que se cambia el n6mero en el registro

de segmento. #uando se carga un nuevo n6mero en un registro de segmento, el

microprocesador accesa a una tabla de descriptores % carga el descriptor en la parte de la

cach invisible para el programa en el registro de segmento. +e le retiene all. % se emplea

para accesar al segmento de memoria hasta que se cambie otra vez el n6mero en el

segmento. 1sto permite que el microprocesador accese en forma repetida a un segmento

de memoria sin consultar la tabla de descriptores para cada acceso.

*8

Los registros EB?J (registro de tabla de descriptores globales) e 3B?J (registro de

tabla de descriptores de interrupci!n) contienen la direcci$n base de la tabla de

descriptores % su l.mite. 1l l.mite de cada tabla de descriptores es de 1( bits en los

microprocesadores 8!*8(, 8!:8( % 8!)8(, porque la longitud m,@ima de la tabla es de

()9 b%tes. #uando se desea funcionamiento en el modo protegido, se carga la direcci$n

de la tabla de descriptores globales % su l.mite en el EB?J. Antes de emplear el mtodo

protegido ha% que inicializar la tabla de descriptores de interrupci$n % el 3B?J.

La ubicaci$n de la tabla de descriptores locales se selecciona en la tabla de

descriptores globales. +e inicial iza a uno de los descriptores globales para direccionar a la

tabla de descriptores locales. 'ara accesar a la tabla de descriptores locales, se carga el

LB?J (registro de tabla de descriptores locales) con un selector, igual que se carga un

selector en un registro de segmento. 1ste selector accesa a la tabla de descriptores

globales % carga la direcci$n base, el l.mite % los derechos de acceso de la tabla de

descriptores locales en la secci$n de cach del L?BJ.

1l registro de tarea (?J) accesa a un descriptor que define una tarea. >na tarea,

casi siempre, es un procedimiento o un programa de aplicaci$n. 1l descriptor del

procedimiento o del programa de aplicaci$n se almacena en la tabla de descriptores

globales en la secci$n de cach del L?BJ, a fin de controlar el acceso por medio de los

niveles de privilegio.

*-

Vous aimerez peut-être aussi

- Unidad No1Document17 pagesUnidad No1Jennifer RiveraPas encore d'évaluation

- Promodel1 PDFDocument14 pagesPromodel1 PDFMelissa ClarkPas encore d'évaluation

- Aec 610Document35 pagesAec 610Marc ToralPas encore d'évaluation

- Simulacion - Ejercicios Unidad 1-3Document1 pageSimulacion - Ejercicios Unidad 1-3Melissa ClarkPas encore d'évaluation

- Simulacion - Ejercicios Unidad 1-3Document1 pageSimulacion - Ejercicios Unidad 1-3Melissa ClarkPas encore d'évaluation

- Microprocesador 8086Document15 pagesMicroprocesador 8086Melissa ClarkPas encore d'évaluation

- 1ra UnidadDocument29 pages1ra UnidadMelissa ClarkPas encore d'évaluation