Académique Documents

Professionnel Documents

Culture Documents

Test Pattern

Transféré par

vinyrose0 évaluation0% ont trouvé ce document utile (0 vote)

25 vues7 pagespattern

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentpattern

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

25 vues7 pagesTest Pattern

Transféré par

vinyrosepattern

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 7

ISSN (Print) : 2320 3765

ISSN (Online) : 2278 8875

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 2, Issue 5, May 2013

Copyright to IJAREEIE www.ijareeie.com 1933

TEST PATTERN GENERATION USING

PSEUDORANDOM BIST

GaneshBabu.J

1

, Radhika.P

2

PG Student [VLSI], Dept. of ECE, SRM University, Chennai, Tamilnadu, India

1

Assistant Professor [O.G], Dept. of ECE, SRM University, Chennai, Tamilnadu, India

2

ABSTRACT: Pseudorandom built-in self test (BIST) generators have been widely utilized to test integrated circuit and

systems. In this Project an accumulator-based-3 weight test pattern generation scheme is presented and proposed

scheme generates set of test patterns with weights 0, 0.5 and 1. These accumulators are mostly found in current VLSI

chips and that the scheme can be efficiently to drive the hardware of BIST pattern generation. The hardware

requirements for this project are FPGA SPARTAN 3 and the software which are used as Modelsim and Xilinx . Finally

test patterns are produced for 5bit and c880 testbench circuits.

Keywords: Three weights 0-0.5-1, Accumulator, c880, D flipflop.

I. INTRODUCTION

BIST is a design-for-testability technique that places the testing functions physically with the circuit under test (CUT).

The basic BIST architecture requires the addition of three hardware blocks to a digital circuit: a test pattern generator, a

response analyzer, and a test controller. The test pattern generator generates the test patterns for the CUT. Examples of

pattern generators are a ROM with stored patterns, a counter, and a linear feedback shift register (LFSR). A typical

response analyzer is a comparator with stored responses or an LFSR used as a signature analyzer. It compacts and

analyzes the test responses to determine correctness of the CUT. A test control block is necessary to activate the test

and analyze the responses. However, in general, several test-related functions can be executed through a test controller

circuit.A digital system is tested and diagnosed during its lifetime on numerous occasions. Such a test and diagnosis

should be quick and have very high fault coverage. One way to ensure this is to specify such a testing to as one of the

system functions, so now it is called Built In Self Test (BIST). With properly designed BIST, the cost of added test

hardware will be more than balanced by the benefits in terms of reliability and reduced maintenance cost. For BIST, we

would require that the test patterns be generated on the system/chip itself. However, this should be done keeping in

mind that the additional hardware is minimized. One extreme is to use exhaustive testing using a counter and storing

the results for each fault simulation at a place on the chip (like ROM). An n input circuit would then require 2^n

combinations which can be very tiresome on the system with respect to the space and the time. Also, more the number

of transitions, the power consumed will be more.

II. TEST PATTERN GENERATION THROUGH ACCUMULATOR BASED 3 WEIGHT.

A new weighted random pattern design for testability is described where the shift register latches distributed

throughout the chip are modified so that they can generate biased pseudo-random patterns upon demand. A two-bit

code is transmitted to each weighted random pattern shift register latches to determine its specific weight. The weighted

random pattern test is then divided into groups, where each group is activated with a different set of weights. The

weights are dynamically adjusted during the course of the test to "go after" the remaining untested faults.An

accumulator-based 3-weight test pattern generation scheme is presented; the proposed scheme generates set of patterns

with weights 0, 0.5, and 1. Since accumulators are commonly found in current VLSI chips, this scheme can be

efficiently utilized to drive down the hardware of built in self test pattern generation, as well. Comparisons with

previously presented schemes indicate that the proposed scheme compares favorably with respect to the required

hardware.

ISSN (Print) : 2320 3765

ISSN (Online) : 2278 8875

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 2, Issue 5, May 2013

Copyright to IJAREEIE www.ijareeie.com 1934

Fig. 1.Test Vectors Generation through A[i].

OPERATION OF THE CELL:

I. For A[i] =1 , We give set[i]=1 and reset[i]=0 and hence A[i]=1 and B[i]=0. Then the output is equal

to 1,and Cin will be equal to Co. Cin is transferred to the Cout.

II. For A[i] =0 , We give set[i]=0 and reset[i]=1 and hence A[i]=0 and B[i]=1. Then the output is equal

to 0, and here Cin is equal to Cout. Cin is transferred to the Cout.

III. For A[i] = - , set[i] =0 and reset[i] =0. The D input of the flip-flop of register B is driven by either 1

or 0, depending on the value that will be added to the accumulator inputs in order to generate

satisfactorily random patterns to the inputs of the CUT.

ISSN (Print) : 2320 3765

ISSN (Online) : 2278 8875

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 2, Issue 5, May 2013

Copyright to IJAREEIE www.ijareeie.com 1935

III. TEST PATTERNS FOR BENCH MARK C880 CIRCUITS

C880 BENCH MARK CIRCUIT:

According to this paper, our future work is to check the performance of the bench mark circuit c880. The

Bench mark circuit consists of 60 inputs, 26 outputs, and 383 gates. Its an 8-bit ALU with high level model. The core

of this 8-bit ALU is an 8-bit 74283-style adder. To analyse the C880 we have to modify our proposed test pattern

architecture. Because C880 consist of 60 inputs but our proposed testing hardware provides of demo test pattern only.

PROPOSED SYSTEM ADVANTAGES:

It does not impose any requirements about the design of the adder

It does not require any modification of the adder.

Does not affect the operating speed of the adder.

PROPOSED SYSTEM APPLICATION:

Test to Integrated Circuits and Systems

BIST Applications

IV. SIMULATION RESULTS

ModelSim is a simulation tool for hardware design which provides behavioural simulation of a number of languages,

i.e., Verilog, VHDL, and System C. Verilog HDL is an industry standard language used to create analog, digital, and

mixed-signal circuits. HDLs are languages which are used to describe the functionality of a piece of hardware as

opposed to the execution of sequential instructions like that in a regular software application.

Verilog code is generated for this accumulator circuit using 6.4c.Then RTL schematic is produced using XILINK 13.2.

These test patterns are implemented in FPGA SPARTAN 3(XC3S400 PQ 208).

ISSN (Print) : 2320 3765

ISSN (Online) : 2278 8875

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 2, Issue 5, May 2013

Copyright to IJAREEIE www.ijareeie.com 1936

4.1: Generation of 5 bit test patterns

4.2:Output bits of Session Counter in c880 benchmark

ISSN (Print) : 2320 3765

ISSN (Online) : 2278 8875

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 2, Issue 5, May 2013

Copyright to IJAREEIE www.ijareeie.com 1937

4.3:Test patterns For c880 bench mark Circuits

Fig4.4 RTL schematic view

ISSN (Print) : 2320 3765

ISSN (Online) : 2278 8875

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 2, Issue 5, May 2013

Copyright to IJAREEIE www.ijareeie.com 1938

Fig 4.4(a) Expanded RTL of 4.1

4.5: Technology View

ISSN (Print) : 2320 3765

ISSN (Online) : 2278 8875

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 2, Issue 5, May 2013

Copyright to IJAREEIE www.ijareeie.com 1939

V. CONCLUSION

We have presented an accumulator-based 3-weight (0, 0.5, and 1) test-per-clock generation scheme, which can be

utilized to efficiently generate weighted patterns without altering the structure of the adder. It does not impose any

requirements about the design of the adder and operating speed is not affected. Benchmark net-lists demonstrate that

the fault coverage of the proposed pattern generator is significantly higher compared to conventional pattern generation

techniques.

REFERENCES

[1] S. Wang, Low hardware overhead scan based 3-weight weighted random BIST, in Proc. IEEE Int. Test Conf., 2001, pp. 868877.

[2] Voyiatzis, D. Gizopoulos, and A. Paschalis, Accumulator-based weighted pattern generation, presented at the IEEE Int. Line Test Symp.,

Saint Raphael, French Riviera, France, Jul. 2005.

[3] Stroele, A self test approach using accumulators as test pattern generators, in Proc. Int. Symp. Circuits Syst., 1995, pp. 21202123.

[4] K. Yamaguchi, M. Inoue, and H. Fujiwara, Hierarchical BIST: Testper-clock BIST with low overhead, Electron. Commun. Japan (PartII:

Electron.), vol. 90, no. 6, pp. 4758, Jun. 2007.

[5] O. Novk, Z. Plva, J. Nosek, A. Hlawiczka, T. Garbolino, and K.Gucwa, Test-per-clock logic BIST with semi-deterministic test patternsand

zero-aliasing compactor, J. Electron. Testing: Theor. Appl.,vol. 20, no. 1, pp. 109122, Feb. 2004.

Vous aimerez peut-être aussi

- 1SMA10CAT3G Series, SZ1SMA10CAT3G Series 400 Watt Peak Power Zener Transient Voltage SuppressorsDocument5 pages1SMA10CAT3G Series, SZ1SMA10CAT3G Series 400 Watt Peak Power Zener Transient Voltage SuppressorsvinyrosePas encore d'évaluation

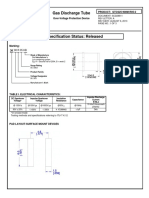

- Gas Discharge Tube: PRODUCT: GTCS25-900M-R05-2Document3 pagesGas Discharge Tube: PRODUCT: GTCS25-900M-R05-2vinyrosePas encore d'évaluation

- P Spice PrimerDocument30 pagesP Spice PrimervinyrosePas encore d'évaluation

- Pipelining and Parallel ProcessingDocument37 pagesPipelining and Parallel ProcessingvinyrosePas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Quality Function DeploymentDocument21 pagesQuality Function DeploymentNitika BhatiaPas encore d'évaluation

- Drexler 1988Document12 pagesDrexler 1988HnewPas encore d'évaluation

- Best Uni Hand Book For Bridge DesignDocument239 pagesBest Uni Hand Book For Bridge DesignThong Nguyen100% (2)

- Font Information (All Fonts)Document5 pagesFont Information (All Fonts)ShakeelaPas encore d'évaluation

- Certification Memorandum: Criteria For The Determination of The EASA Level of Involvement in Product CertificationDocument79 pagesCertification Memorandum: Criteria For The Determination of The EASA Level of Involvement in Product Certificationsezgin bayramPas encore d'évaluation

- 0824743083Document5 071 pages0824743083Shiv Kumar RathorePas encore d'évaluation

- Advanced in The VLSI Design Flow PDFDocument47 pagesAdvanced in The VLSI Design Flow PDFEzhilarasan KaliyamoorthyPas encore d'évaluation

- Práctica de InglésDocument7 pagesPráctica de InglésAlonso quijanoPas encore d'évaluation

- Parts Catalog: iR2020S/2020J/2020i/2020/ 2016j/2016i/2016Document104 pagesParts Catalog: iR2020S/2020J/2020i/2020/ 2016j/2016i/2016Vishrut ChhajerPas encore d'évaluation

- 3.5.rapid PrototypingDocument6 pages3.5.rapid PrototypingDhanush Karthik RajanPas encore d'évaluation

- Study Questions - Persuasive Health TechnologyDocument25 pagesStudy Questions - Persuasive Health TechnologyGasia KorikianPas encore d'évaluation

- BIM Execution Plan ExampleDocument20 pagesBIM Execution Plan ExampleDarell IvanderPas encore d'évaluation

- Bachelor of Applied Science (Architectural Science) 2019Document19 pagesBachelor of Applied Science (Architectural Science) 2019stimPas encore d'évaluation

- Scantronic 9448 User GuideDocument12 pagesScantronic 9448 User Guidethunderstorm60Pas encore d'évaluation

- Detecon Study Next-Generation Telco Product Lifecycle Management: How To Overcome Complexity in Product Management by Implementing Best-Practice PLMDocument66 pagesDetecon Study Next-Generation Telco Product Lifecycle Management: How To Overcome Complexity in Product Management by Implementing Best-Practice PLMDetecon International100% (2)

- 355 Nittr NSQF Based Syllabus PDFDocument233 pages355 Nittr NSQF Based Syllabus PDFPrince GautamPas encore d'évaluation

- OnPrem SAP S4HANA Activate End To End Steps 1588902192 PDFDocument17 pagesOnPrem SAP S4HANA Activate End To End Steps 1588902192 PDFChandrababu Naidu BoyapatiPas encore d'évaluation

- PRT507 Unit Outline 2014Document6 pagesPRT507 Unit Outline 2014NING YUEPas encore d'évaluation

- Grade 10 Practical WorkDocument24 pagesGrade 10 Practical WorkYTExtremeBoy opPas encore d'évaluation

- Guide To Application: Chartered Engineer Ceng Chartered Environmentalist Cenv Chartered Scientist CsciDocument20 pagesGuide To Application: Chartered Engineer Ceng Chartered Environmentalist Cenv Chartered Scientist CsciMuhammad Imran KhanPas encore d'évaluation

- Rural Study Guidelines Handout by Ar. Pradeep Reddy NavakotiDocument3 pagesRural Study Guidelines Handout by Ar. Pradeep Reddy NavakotipradeepPas encore d'évaluation

- 01 - Introduction To Architectural DesignDocument55 pages01 - Introduction To Architectural Designdarel amalla100% (1)

- B7 CAD TSOL by FayolDocument6 pagesB7 CAD TSOL by Fayolsetawot509Pas encore d'évaluation

- Disposable Cassette System For ATM CurrencyDocument60 pagesDisposable Cassette System For ATM CurrencyguichovenomPas encore d'évaluation

- Quality Checker Job DescriptionDocument8 pagesQuality Checker Job Descriptionqualitymanagement246Pas encore d'évaluation

- Semester 1 FEB2016 Final Examination Timetable (Listing)Document69 pagesSemester 1 FEB2016 Final Examination Timetable (Listing)Madison HazePas encore d'évaluation

- B.Arch Programme, IX Semester Theory of Urban Design ARCH503Document22 pagesB.Arch Programme, IX Semester Theory of Urban Design ARCH503Vanshika DograPas encore d'évaluation

- This Is The End CGT 411 Emerging Technologies Processes ReviewDocument12 pagesThis Is The End CGT 411 Emerging Technologies Processes Reviewapi-279820538Pas encore d'évaluation

- Textbook Ars 203 Textbook 1 w01 Studi Tapak Dan LingkunganDocument11 pagesTextbook Ars 203 Textbook 1 w01 Studi Tapak Dan LingkunganWeldri Berto OcmafiyonPas encore d'évaluation

- OpenLivingLab Days 2019 Conference ProceedingsDocument482 pagesOpenLivingLab Days 2019 Conference ProceedingsEuropean Network of Living Labs80% (5)