Académique Documents

Professionnel Documents

Culture Documents

Informe 1

Transféré par

Jonnathan AriasDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Informe 1

Transféré par

Jonnathan AriasDroits d'auteur :

Formats disponibles

1

PRACTICA # 1: TRANSISTOR FET Y MOSFET

Universidad Politecnica Salesiana

Laboratorio De Electronica Analogica II

Oscar David Sari Villa

osari@est.ups.edu.ec

I. OBJETIVOS:

Disear, calcular y comprobar el funcionamiento de

los siguientes circuitos con el transistor FET.

Polarizacin con dos fuentes.

Con resistencia de source.

Sin resistencia de source.

Autopolarizacin:

Con divisor de tensin.

Con fuente doble.

Disear, calcular y simular la polarizacin de los

transistores Mosfet.

Mosfet Incremental.

Mosfet Decremental.

II. RESUMEN:

En esta prctica se realiz la polarizacin del

transistor FET, para eso realizamos el mismo

procedimiento que cuando empezamos a utilizar

los transistores BJT, de igual manera comenzamos

con los tipos de polarizacin que existen, de qu

manera los podemos polarizar, que caractersticas

son necesarias para su adecuado funcionamiento,

debemos tomar en cuenta que en este tipo de

transistores se presentan nuevas modificaciones

por lo cual debemos tener presente que en ciertos

casos algunos elementos pueden ser innecesarios.

III. INTRODUCCION:

Para empezar con la prctica primero analizamos

bajo qu condiciones trabaja en transistor FET,

que caractersticas se obtiene mediante catlogo.

Primero empezamos con la polarizacin con dos

fuentes, en esta configuracin utilizamos una

fuente como la alimentacin principal que

llamamos VDD, la otra va a la entrada de GATE

(G) pero dicha fuente se conecta con la

polarizacin inversa para dotar de un voltaje

negativo a GATE.

Para estas polarizaciones tambin existe la

presencia de una resistencia de source que

vendra a ser como la resistencia de emisor en los

transistores BJT y de la misma manera que en los

transistores BJT dicha resistencia nos va a

presentar un efecto en el circuito que debe ser

tomado en cuenta al momento de realizar los

clculos y en ciertos casos tambin va a afectar en

la curva de trabajo.

IV. MARCO TERICO:

Funcionamiento:

El Transistor Fet

El JFET es un dispositivo unipolar, ya que en su

funcionamiento slo intervienen los portadores

mayoritarios. Existen 2 tipos de JFET: de "canal N"

y "de canal P".

Figura 1: Smbolos de los transistores JFET, canal

N y canal P.

En el caso del JFET de canal N, la unin puerta

canal, se encuentra polarizada en inversa, por lo

que prcticamente no entra ninguna corriente a

travs del terminal de la puerta.

El JFET de canal p, tiene una estructura inversa a

la de canal n; siendo por tanto necesaria su

polarizacin de puerta tambin inversa respecto al

de canal n.

Zona lineal

Si en la estructura del transistor de canal n se

aplica una tensin VDS mayor que cero, aparecer

una corriente circulando en el sentido del drenaje

al surtidor, corriente que llamaremos ID. El valor de

dicha corriente estar limitado por la resistencia del

canal N de conduccin. En este caso pueden

2

distinguirse dos situaciones, segn sea VDS

grande o pequea en comparacin con VDS.

ID = Corriente de Drenaje

IDSS = Corriente de Drenaje de Saturacin

VGS = Voltaje Puerta-Fuente

VP = Voltaje de ruptura o Pinch Voltage.

Id=Idss1-VGSVp2

Curvas Caractersticas Del Transistor De Efecto

De Campo.

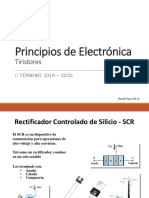

Transistor Mosfet

Las prestaciones del transistor MOSFET son

similares a las del JFET, aunque su principio de

operacin y su estructura interna son diferentes.

Existen cuatro tipos de transistores MOS:

Enriquecimiento de canal N

Enriquecimiento de canal P

Empobrecimiento de canal N

Empobrecimiento de canal P

Los smbolos son:

La caracterstica constructiva comn a todos los

tipos de transistor MOS es que el terminal de

puerta (G) est formado por una estructura de tipo

Metal/xido/Semiconductor. El xido es aislante,

con lo que la corriente de puerta es prcticamente

nula, mucho menor que en los JFET. Por ello, los

MOS se emplean para tratar seales de muy baja

potencia.

Principio De Operacin:

De entre todos los tipos de transistores MOS

existentes se va a analizar el principio de

funcionamiento de dos de ellos: los NMOS de

enriquecimiento y empobrecimiento.

Esquemas y Clculos:

a. Polarizacin con Doble Fuente

Datos

VDD

12V

RD1

1.2k

Q2

2N3370

V1

2 V

3

(

)

(

) ()

b. Auto polarizacin con resistencia source

Datos

b. Auto polarizacin sin RS

Datos

d. Polarizacin con divisor de tensin.

Datos

, I D=3mA

VDD

12V

RD3

640

Q3

2N3370

RD4

120

VDD

12V

RD

470

Q1

2N3370

VDD

12V

RD2

640

Q4

2N3370

RE

120

R1

5k

R2

640

4

)

(

) ()

RD=RS

( )

()

e. Polarizacin con fuente doble positiva y

negativa.

Datos

V

f. Mosfet Tipo Decremental:

VDD=24V, VDS=12V, R2=10M, Vp=-3V

VGS=-1V, IDSS=40.5mA, VRS=2V.

)

VDD

5V

RD5

640

Q5

2N3370

RD6

120

VCC

5V

VCC

24V

RS

440

Q1

BSP149

RD

2.2k

R2

240M

R1

10M

5

g. Mosfet Tipo Incremental:

V. LISTA DE MATERIALES Y EQUIPOS

Materiales:

Resistencias de:

1K, 1.5K, 2.2K, 3.3K, 180, 470

($0.12)

4 Transistor FET MPF 102 ($2.80)

Presupuesto $2.92

Equipos y herramientas:

Pinzas, pela cable, Protoboard.

Multimetro.

Fuente de CC (+12V, +5V, -5V).

Software de simulacin (Multisim).

VI. DESARROLLO

Tablas, Mediciones y Graficas:

Polarizacin con dos fuentes

Medidos Simulados Calculados

VDD 12.01 V 12 V 12 V

VDS 5.68 V 5.97 V 6 V

VGS -0.75 V -0.73 V -0.73 V

VRD 6.3 V 6.02 V 6 V

ID 3.72 mA 3.54 mA 3.5 mA

Ingreso:

Salida:

Autopolarizacin con resistencia de source

Medidos Simulados Calculados

VDD 12.02 V 12 V 12 V

VDS 5.99 V 5.93 V 6 V

VGS -1.04 V -0.95 V -1 V

ID 7.59 mA 7.99 mA 7.74 mA

Ingreso:

Q2

2N6659

VCC

24V

RS1

440

RD1

2.2k

R3

240M

R4

10M

6

Salida:

Autopolarizacin sin resistencia de source

Medidos Simulados Calculados

VDD 11.99 V 12 V 12 V

VDS 6.01 V 6.18 V 6 V

VGS 0 V 0 V 0 V

VRD 5.98 V 6.17 V 6 V

ID 13.35 mA 13.4 mA 13 mA

Ingreso:

Salida:

Con divisor de tensin

Medidos Simulados Calculados

VDD 19.83 V 20 V 20 V

VDS 10.08 V 10.09 V 10 V

VGS -0.69 V -0.53 V -0.58 V

ID 3 mA 2.98 mA 3 mA

Ingreso:

Salida:

Polarizacin con fuente simtrica;

Medidos Simulados Calculados

VDD 11.98 V 12 V 12 V

VDS 4.31 V 4.45 V 4 V

VGS -0.74 V -0.8 V -1 V

VSS -4 V -4 V -4 V

ID 2.63 mA 2.55 mA 2.65 mA

7

Ingreso:

Salida:

VII. SIMULACIONES

a. Polarizacin con dos fuentes.

Simulaciones

VDD 12 V

VDS 5.97 V

VGS -0.73 V

ID 3.54 mA

b. Autopolarizacin con R de source

Simulaciones

VDD 12 V

VDS 5.93 V

VGS 0.957 V

ID 7.99 mA

c. Autopolarizacin sin R de source

Simulaciones

VDD 12 V

VDS 5.87 V

VGS 0 V

ID 13.1 mA

c. Polarizacin con divisor de tensin.

8

Simulaciones

VDD 20 V

VDS 10.092 V

VGS -0.534V

ID 2.98 mA

d. Polarizacin con fuente doble positiva y

negativa.

Simulaciones

VDD 12 V

VDS 4.45 V

VGS -0.8 V

ID 2.55 mA

VSS 4 V

Simulaciones de los transistores Mosfet:

Mosfet Tipo Decremental:

VIII. ANALISIS

Como podemos ver en las distintas graficas

obtenidas a partir de los datos Simulados,

Calculados y Medidos, las variaciones de voltaje y

de corriente son muy bajas, por lo general en el

orden de valores menores a 0.5.

Con estos resultados comprobamos que si hay

como disear los circuitos de polarizacin del FET

en un punto de trabajo especfico y obtener gran

exactitud en los valores de salida.

Para facilitar los clculos nos hemos impuesto que

el punto de trabajo sea la midad del voltaje de

entrada, con ello las obtendremos desde el inicio

los valores de Id y Vds.

ANALYSIS

As we can see in the different ones you obtained

starting from the Feigned, Calculated and

Measured data, the voltage variations and of

current they are very low, in general in the order of

smaller securities at 0.5.

With these results we check that if it is necessary

as to design the circuits of polarization of the FET

in a specific working point and to obtain great

accuracy in the exit securities.

To facilitate the calculations we have imposed

ourselves that the working point is the midad of the

entrance voltage, with we will obtain them to it from

the beginning the securities of you Go and you

IX. CONCLUCIONES

Se pudo comprobar que la corriente de drain que

depende del voltaje gate source, obedece casi

exactamente a la ecuacin de shockley.

Id=Idss1-VGSVp2

Se puede observar que la curva caracterstica a la

salida del FET es muy similar a la de un BJT.

Puedo decir que para que las mediciones de esta

prctica sean aceptables y tengan el menor

nmero de errores en las mismas con respecto a

los clculos tuvimos que ajustar las resistencias lo

ms posible a las calculadas teniendo en algunos

casos que poner las resistencias en serie o en

paralelo ya que los valores de las mismas si se

alejaban mucho cambian los valores de corriente y

voltaje a rangos que no son aceptables; es decir

que para el Transistor FET funcione correctamente

las resistencias deben ser lo ms exactas posibles.

Los valores de los JFET pueden ser diferentes

aunque sean del mismo tipo por lo que primero

tuvimos que obtener los valores reales de Vp y de

IDSS.

CONCLUCION

The measured values resemble each other to

those calculated and feigned, alone with a small

9

error margin due to the resistances or to the

characteristics of FET.

It could be proven that the drain current that

depends on the voltage gate source, obeys the

Shockley equation almost exactly.

Id=Idss1-VGSVp2

One can observe that the characteristic curve to

the exit of FET is very similar to that of a BJT.

I can say that so that the mensuration of this

practice are acceptable and have the smallest

number of errors in the same ones with regard to

the calculations we had to adjust the resistances

the most possible thing to those calculated having

in some cases that to put the resistances in series

or in parallel since the values of the same ones if

they went away a lot they change the current

values and voltage to ranges that are not

acceptable; that is to say that for the Transistor

FET works the resistances correctly they should be

the most exact possible.

The values of JFET can be different although they

are of the same type for that that first we had to

obtain the real values of Vp and of IDSS.

X. BIBLIOGRAFIA

[1] Titulo: ANALISIS INTRODUCTORIO DE

CIRCUITOS. Boylestad, Robert. 8va Edicin,

Vous aimerez peut-être aussi

- PREINFORME6Document2 pagesPREINFORME6Andres EstebanPas encore d'évaluation

- Informe Amplificador BJTDocument5 pagesInforme Amplificador BJTdaniPas encore d'évaluation

- Informe Antena ClaroDocument3 pagesInforme Antena ClaroJorge Samaniego VeraPas encore d'évaluation

- G1 Larrea Criollo Eddy RedesIIDocument33 pagesG1 Larrea Criollo Eddy RedesIILeonardoPas encore d'évaluation

- Segundo Trabajo Fallos SecuenciasDocument45 pagesSegundo Trabajo Fallos SecuenciasRenato García TejadaPas encore d'évaluation

- Iluminacion Interior. DiapositivasDocument25 pagesIluminacion Interior. DiapositivasArian Padilla ChavezPas encore d'évaluation

- Clase 3 - Magnitudes LuminosasDocument19 pagesClase 3 - Magnitudes LuminosasaallooffPas encore d'évaluation

- 5 Flujo de PotenciaDocument57 pages5 Flujo de PotenciaJulio Tello AguilarPas encore d'évaluation

- Estandares TIA-EIA 1Document10 pagesEstandares TIA-EIA 1torjaquintero100% (1)

- Samaniego Velez María Jose Tarea1 1009609504 PDFDocument6 pagesSamaniego Velez María Jose Tarea1 1009609504 PDFMaria Jose Samaniego VelezPas encore d'évaluation

- LAB 3 Redes de AcopleDocument4 pagesLAB 3 Redes de AcopleJeisson RodriguezPas encore d'évaluation

- Organismos Que Rigen El Cableado EstructuradoDocument21 pagesOrganismos Que Rigen El Cableado EstructuradoDELFREZPas encore d'évaluation

- Práctica 4-InformeDocument2 pagesPráctica 4-InformeDarwin Salazar Guerrero100% (1)

- Inversores PDFDocument91 pagesInversores PDFAngie EstupiñanPas encore d'évaluation

- Sistemas Dinamicos de Orden SuperiorDocument23 pagesSistemas Dinamicos de Orden SuperiorJenny ZenobiPas encore d'évaluation

- Informe AntenasDocument19 pagesInforme AntenasLuisColinaPas encore d'évaluation

- Proyecto II Unidad PDFDocument85 pagesProyecto II Unidad PDFNando ToapantaPas encore d'évaluation

- PFC Jaime Prieto ZapardielDocument77 pagesPFC Jaime Prieto ZapardielNeder RodrigoPas encore d'évaluation

- Articulo Seguidor SolarDocument5 pagesArticulo Seguidor SolarJaphet González BerronesPas encore d'évaluation

- Metodos de Arranque de Motores de InducciónDocument6 pagesMetodos de Arranque de Motores de InducciónGissela Abata100% (2)

- Informe Visita Tecnica El IngaDocument5 pagesInforme Visita Tecnica El IngaCarlos AguilarPas encore d'évaluation

- Magnitudes y Unidades FotométricasDocument10 pagesMagnitudes y Unidades Fotométricasstefany patriciaPas encore d'évaluation

- Informe Redes PetriDocument5 pagesInforme Redes PetriSergio David Moya HilariónPas encore d'évaluation

- Tipos de Conectores de Fibra ÓpticaDocument6 pagesTipos de Conectores de Fibra ÓpticaMilton CoaritePas encore d'évaluation

- 4Document8 pages4Rodrigo Rojas SoberPas encore d'évaluation

- Parametros ElectricosDocument52 pagesParametros ElectricosgastonmdqPas encore d'évaluation

- Informe de Visita Tecnica Estación Base ConchitasDocument9 pagesInforme de Visita Tecnica Estación Base ConchitasMarcos Cavalierr JaraPas encore d'évaluation

- Accidente de BhopalDocument3 pagesAccidente de BhopalCristhian Zúñiga RuizPas encore d'évaluation

- Generador SincronoDocument19 pagesGenerador SincronoGustavo PaizPas encore d'évaluation

- Multivibrador Astable y MonoestableDocument4 pagesMultivibrador Astable y MonoestableVANESSA JAZMIN MORA MARTINEZPas encore d'évaluation

- Introduccion A Los Circuitos Retroalimentados PDFDocument23 pagesIntroduccion A Los Circuitos Retroalimentados PDFAlfredo HueskPas encore d'évaluation

- Ensayo de CentralesDocument20 pagesEnsayo de CentralesPool MedinaPas encore d'évaluation

- Introduccion Al La Electronica de Potencia PDFDocument393 pagesIntroduccion Al La Electronica de Potencia PDFIvan LemoinePas encore d'évaluation

- Sylabus Potencia2 2007B UNSA ArequipaDocument4 pagesSylabus Potencia2 2007B UNSA ArequipaJuan VelascoPas encore d'évaluation

- Laboratorio - Integrador y Diferenciador Con AoDocument4 pagesLaboratorio - Integrador y Diferenciador Con AomarlonPas encore d'évaluation

- Tipos de Conectores de Fibra ÓpticaDocument7 pagesTipos de Conectores de Fibra ÓpticaLeonel HerreraPas encore d'évaluation

- Mejora Del Factor de PotenciaDocument5 pagesMejora Del Factor de PotenciacualquieraqueseaPas encore d'évaluation

- Tercer Parcial Med II 2007-2Document4 pagesTercer Parcial Med II 2007-2Vimar Percca LopezPas encore d'évaluation

- Problemas Disp Elec Alta TensionDocument3 pagesProblemas Disp Elec Alta TensionJuan CarlOs Culqui MelendezPas encore d'évaluation

- Circuitos RLCDocument5 pagesCircuitos RLCBayron SantoyaPas encore d'évaluation

- Distribución de La Tensión Aplicada A La Carga de Una Cadena de AisladoresDocument3 pagesDistribución de La Tensión Aplicada A La Carga de Una Cadena de AisladoresmartinmejiasolanoPas encore d'évaluation

- Fusible GCDocument1 pageFusible GCluisPas encore d'évaluation

- Calculo de PanelesDocument8 pagesCalculo de PanelesMoises Marsos100% (1)

- Lineas de Transmision en ColombiaDocument42 pagesLineas de Transmision en ColombiacesarPas encore d'évaluation

- Proyecto Sistemas de DistribucionDocument11 pagesProyecto Sistemas de DistribucionIvan Rivera ArgumedoPas encore d'évaluation

- Implementación de Seguidor Solar en Dos Ejes para El Sistema Fotovoltaico de La Escuela de Ingeniería Eléctrica de La UESDocument138 pagesImplementación de Seguidor Solar en Dos Ejes para El Sistema Fotovoltaico de La Escuela de Ingeniería Eléctrica de La UESGustavo RiosPas encore d'évaluation

- Rectificador TrifásicoDocument5 pagesRectificador TrifásicoAngel VazquezPas encore d'évaluation

- Electronica Industrial Editado PDFDocument586 pagesElectronica Industrial Editado PDFWilmer León MNPas encore d'évaluation

- Convertidores DC ACDocument7 pagesConvertidores DC ACEnriqueTámaraPas encore d'évaluation

- Control de Velocidad de Los Motres de Induccion MonofasicoDocument11 pagesControl de Velocidad de Los Motres de Induccion MonofasicoJuan Alvarado LujanPas encore d'évaluation

- Informe Elementos de Un TransductorDocument4 pagesInforme Elementos de Un TransductorLuis ChicaizaPas encore d'évaluation

- Análisis de Utilidad de Estandarización de Protecciones Eléctricas en Motores, Estipuladas en El Código Eléctrico Nacional (José Ángel Pérez León)Document11 pagesAnálisis de Utilidad de Estandarización de Protecciones Eléctricas en Motores, Estipuladas en El Código Eléctrico Nacional (José Ángel Pérez León)JLPirela1000Pas encore d'évaluation

- Informe Pantalla HMIDocument5 pagesInforme Pantalla HMIjeanPas encore d'évaluation

- Guia de Laboratorio de Resistencias, Condensadores y DiodosDocument6 pagesGuia de Laboratorio de Resistencias, Condensadores y DiodosangheloPas encore d'évaluation

- Variador de Frecuencia ResumenDocument7 pagesVariador de Frecuencia ResumenBrodka2Pas encore d'évaluation

- Maquinas Electricas Informe 9Document9 pagesMaquinas Electricas Informe 9Daniel PeñaPas encore d'évaluation

- Mis Apuntes de MaquinasElectricas Cap2 TransformadorDocument22 pagesMis Apuntes de MaquinasElectricas Cap2 TransformadorElizabeth ArenasPas encore d'évaluation

- Practica (1) Laboratorio Analogica II PDFDocument8 pagesPractica (1) Laboratorio Analogica II PDFEdwin MBPas encore d'évaluation

- Diseno Con Transistores - UNIDAD 1 12 FebDocument59 pagesDiseno Con Transistores - UNIDAD 1 12 FebJose Manuel Palma AhujaPas encore d'évaluation

- Practica 1Document13 pagesPractica 1Xavier UyaguariPas encore d'évaluation

- Ficha WordDocument2 pagesFicha WordJonnathan AriasPas encore d'évaluation

- Trabajo Final PediatriaDocument19 pagesTrabajo Final PediatriaJonnathan AriasPas encore d'évaluation

- Fibra Optica en El EcuadorDocument5 pagesFibra Optica en El EcuadorJonnathan AriasPas encore d'évaluation

- Informe Practica 1Document3 pagesInforme Practica 1Jonnathan AriasPas encore d'évaluation

- AC5TODOSDocument3 pagesAC5TODOSJonnathan AriasPas encore d'évaluation

- Manual+s7+s1200 +siemensDocument378 pagesManual+s7+s1200 +siemensJonnathan AriasPas encore d'évaluation

- SuperficiescilindcuadricrevDocument23 pagesSuperficiescilindcuadricrevLuis FernandoPas encore d'évaluation

- Solido WordDocument10 pagesSolido WordJonnathan AriasPas encore d'évaluation

- Trabajo Práctico N 1Document4 pagesTrabajo Práctico N 1Yane carvajalPas encore d'évaluation

- Laboratorio 11Document6 pagesLaboratorio 11Maria Edilma ParraPas encore d'évaluation

- P3 Arranque M-Iii Con Desconexión TemporizadaDocument12 pagesP3 Arranque M-Iii Con Desconexión TemporizadaAngel GSPas encore d'évaluation

- Que Es y Como Funciona Un TiristorDocument11 pagesQue Es y Como Funciona Un Tiristoramado9100% (1)

- Lab1Document1 pageLab1VICTOR ZURITA MALLCUPas encore d'évaluation

- Practica 8Document7 pagesPractica 8Ruben RLPas encore d'évaluation

- Circuitos ElectronicosDocument9 pagesCircuitos ElectronicosDiegoBernalPedrazaPas encore d'évaluation

- Informe N°3Document20 pagesInforme N°3ALEXIS CASTROPas encore d'évaluation

- Presentacion Transistor BJT Emisor ComunDocument13 pagesPresentacion Transistor BJT Emisor ComungfdsacxzPas encore d'évaluation

- Primer Parcial de PROYECTO IMA (Alberto Renteria)Document4 pagesPrimer Parcial de PROYECTO IMA (Alberto Renteria)Alberto RsPas encore d'évaluation

- Cuaderno de Informe Semana 7-Saavedra Vega MatíasDocument17 pagesCuaderno de Informe Semana 7-Saavedra Vega MatíasMatías Saavedra VegaPas encore d'évaluation

- DIT Perú - Protecciones en Potencia - 3d. Ejemplos de CoordinacionDocument22 pagesDIT Perú - Protecciones en Potencia - 3d. Ejemplos de CoordinacionBruno SamosPas encore d'évaluation

- Eecol ElectricDocument6 pagesEecol ElectricEladio BurgosPas encore d'évaluation

- TiristoresDocument22 pagesTiristoresDiego NaulaPas encore d'évaluation

- Esquemas FusiblesDocument29 pagesEsquemas FusiblesOscar MontenegroPas encore d'évaluation

- Activación Secuencial de Cuatro Relés Con Potenciómetro y PulsadorDocument6 pagesActivación Secuencial de Cuatro Relés Con Potenciómetro y PulsadorDaniel Gil CastilloPas encore d'évaluation

- Configuraciones Transistores BipolaresDocument8 pagesConfiguraciones Transistores Bipolarespintoj_20% (2)

- Tableros de Alumbrado y Centros de CargaDocument27 pagesTableros de Alumbrado y Centros de Cargajesus izquierdo ortizPas encore d'évaluation

- Transistor DarlingtonDocument3 pagesTransistor DarlingtonCesar Idvorsky Gutiérrez CachiquePas encore d'évaluation

- ELE211 Guia 3Document4 pagesELE211 Guia 3Sammy PolancoPas encore d'évaluation

- Conceptos de Polarizacion en BJTDocument76 pagesConceptos de Polarizacion en BJTMarco Antonio Rosales VelazquezPas encore d'évaluation

- Manual de Esquemas de Circuitos de Corriente Aire Acondicionado Derby (2005) E5Document5 pagesManual de Esquemas de Circuitos de Corriente Aire Acondicionado Derby (2005) E5TomasPas encore d'évaluation

- A3 8P BKD Fusibles y Rels PDF PDF Relé Fusible (Eléctrico) 7Document1 pageA3 8P BKD Fusibles y Rels PDF PDF Relé Fusible (Eléctrico) 7Nuredin RiberaPas encore d'évaluation

- Características de Los Transistores BJTDocument5 pagesCaracterísticas de Los Transistores BJTFrank BarajasPas encore d'évaluation

- BJT AcDocument62 pagesBJT AcBrayan ParraPas encore d'évaluation

- Mosfet D Amplificador 2N7000Document10 pagesMosfet D Amplificador 2N7000luismena09051982Pas encore d'évaluation

- GJH1211001R8220 k6 22z 80Document5 pagesGJH1211001R8220 k6 22z 80Gustavo CharajaPas encore d'évaluation

- Reporte - Lentitud ProvinciasDocument2 pagesReporte - Lentitud ProvinciasErick GomezPas encore d'évaluation

- CONCEPTO CONTACT PARTING TIME Segun C37-10, IEEE551 y SteevensonDocument3 pagesCONCEPTO CONTACT PARTING TIME Segun C37-10, IEEE551 y SteevensonAngel GonzalezPas encore d'évaluation

- BJT FormularioDocument1 pageBJT FormularioIaron Bar TalPas encore d'évaluation