Académique Documents

Professionnel Documents

Culture Documents

Getting Started With Icarus Verilog

Transféré par

ZohebMasood0 évaluation0% ont trouvé ce document utile (0 vote)

137 vues6 pagesThis document provides instructions for getting started with Icarus Verilog on Windows. It discusses downloading and installing Icarus Verilog, which includes a Verilog compiler and simulator. It then demonstrates a simple example of writing a D flip-flop Verilog module, a tester module to generate inputs, and a testbench module to connect them. It explains compiling and simulating the design to view output waveforms in GTKWave.

Description originale:

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentThis document provides instructions for getting started with Icarus Verilog on Windows. It discusses downloading and installing Icarus Verilog, which includes a Verilog compiler and simulator. It then demonstrates a simple example of writing a D flip-flop Verilog module, a tester module to generate inputs, and a testbench module to connect them. It explains compiling and simulating the design to view output waveforms in GTKWave.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

137 vues6 pagesGetting Started With Icarus Verilog

Transféré par

ZohebMasoodThis document provides instructions for getting started with Icarus Verilog on Windows. It discusses downloading and installing Icarus Verilog, which includes a Verilog compiler and simulator. It then demonstrates a simple example of writing a D flip-flop Verilog module, a tester module to generate inputs, and a testbench module to connect them. It explains compiling and simulating the design to view output waveforms in GTKWave.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 6

codeitdown.

com

Web Development & More

Getting started with Icarus Verilog on

Windows

August 25, 2013

More Jose Vargas

Icarus Verilog is a Verilog standard IEEE-1364 compiler that targets Linux but works almost as well on Windows. It's

lightweight, free soware and includes a virtual machine that simulates the design. This tutorial goes through the

process of downloading, installing and using Icarus Verilog to write a simple program, compile it, simulate it and

view the simulation results on a timing diagram. It assumes no previous knowledge on Verilog, but prior

programming experience is recommended.

Installing Icarus Verilog

Download Icarus Verilog latest stable release for Windows from: bleyer.org/icarus

Installing Icarus Verilog is as easy as installing any other Windows program. Just hit next, but be sure to select GTK

Wave (full installation) and "Add Executables to Windows Path" option. You should be able to use it from a

Command Prompt by now. On Windows Vista/7/8 press Windows key and type cmd to open a command prompt.

Just type "iverilog" and you should get a message saying "iverilog: no source files" and some instructions. Type

"gtkwave" and the GTKWave GUI should open. This program is used to view the simulation results graphically on a

timing diagram.

If these commands are not recognized but the installation was successful chances are the executables were not

added to Windows Path. See How to set the Path on Windows to add "C:\iverilog\bin" to Path manually.

Writing a simple program

Now you are ready to write your first Verilog program. For this tutorial we'll write a D type flip-flop description, that

is, a Verilog module that works like a D flip-flop. At the same time you'll learn some of the basic Verilog concepts by

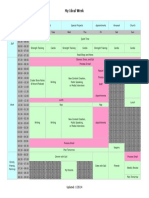

example. You'll also write a tester module to reproduce the following D flip-flop timing diagram:

Getting started with Icarus Verilog on Windows | ... http://codeitdown.com/icarus-verilog-on-windows/

1 of 6 30/10/2013 11:56

Verilog programs are separated in modules, which are functional blocks that have inputs, outputs and internal

logic. You can think of them like the blocks on a circuit's block diagram, but in this case they work. There are two

types of Verilog modules: behavioral modules and structural modules. Both may have the same behaviour but are

dierent in the way they are written as you'll see throughout the example.

For the flip-flop program three modules are used: the flip-flop module, tester module and testbench module. The

last two are modules you'll need on almost every design in order to test your circuit.

Flip-flop module

Represents a simple D type flip-flop. Receives a clock signal and D signal as inputs and outputs Q and QN signals.

The outputs may change on the positive clock edge. The code for this module is:

From this code, you can see the basic structure of every Verilog module. It starts with a declaration: module

dff(d,clk,q,qn); and ends with endmodule. The declaration states the module's name and both its

inputs and outputs. In the module we must declare which variables are inputs and which are outputs, using

"input" and "output".

Variables in Verilog are wires or regs. A wire, like a real wire, has no memory. Thus Verilog wire variables do not

retain their values by themselves. The reg keyword gives variables the ability to hold their values aer they are

assigned, until their value is changed, of course. We want this behaviour for the flip-flop's outputs so q and qn are

defined as regs. If we use a wire the output is never seen by other blocks. It loses its value immediatly aer any

assignment. There is no need to define variables as wires, because they are all wires by default.

The way the inner logic of the module is written deppends on wether it is behavioral or structural. The flip-flop

module is an example of behavioral code. That is, you describe the behavior the module should have. To do it, use

initial and always blocks. The code within an initial block is executed once, when the flip-flop is created. In the

example it's used to define q=0 and qn=1 initially. By default in Verilog the variables are undefined (represented by

an "x"), not zero, not one. If we did'nt use this initial block q and qn would be le undefined until they are assigned

//dff modules represents a D type flip-flop

module dff(d,clk,q,qn);

input d,clk;

output q,qn;

reg q,qn;

//Initialize flip-flop outputs

initial begin q=0; qn=1; end

//Change output on positive clock edge

always @(posedge clk)

begin

q <= d;

qn <= !d;

end

endmodule

Flip-flop module

Getting started with Icarus Verilog on Windows | ... http://codeitdown.com/icarus-verilog-on-windows/

2 of 6 30/10/2013 11:56

for the first time.

The code within an always block is executed when a condition is met. In this case, when the clock has a positive

edge, q and qn are reassigned. This describes completely the flip-flop's logic. As you can see, it is simple. When the

condition is not met, Verilog keeps the outputs' values.

As a rule of thumb, when writing a behavioral module, define outputs as wires.

Verilog has control structures like while, if-else, case, for and repeat (similar to for) like most programming

languages. These assist you on writting your behavioral code. For example, replacing the flip-flop module's always

block by:

produces exactly the same behaviour. Some things changed. Now the always condition is always @(clk)

instead of always @(posedge clk) . This means that now the always block is executed every time clk

changes its value, on positive and negative edges. An always block can be triggered by any number of variables. For

example, @(clk or d) would trigger it whenever clk or d change. This is used in combinational logic where the

output is recalculated whenever an input changes. Back to the example, if clk == 1 then the edge is positive.

We check it using an if statement. Note that adding the "begin" and "end" keywords is necessary when any block

(always, initial, if, for...) has more than one instruction. If omitted for the "if" statement above the second

instruction: qn <= !d; would be executed always (it would be ouside of the if statement). These two keywords

act like the curly brackets on many programming languages.

Tester module

This module tests the flip-flop by generating the clock and D signal of the timing diagram above and dumping the

Q and QN signals of the flip-flop. It's outputs are the flip-flop's inputs and viceversa.

always @(clk)

begin

if(clk == 1)

begin

q <= d;

qn <= !d;

end

end

//Tester module sends a periodic clock signal to the flip-flop

module tester(q,qn,clk,d);

input q,qn;

output clk,d;

reg clk,d;

//Run the test once

initial

begin

clk=0;

//Dump results of the simulation to ff.cvd

Tester module

Getting started with Icarus Verilog on Windows | ... http://codeitdown.com/icarus-verilog-on-windows/

3 of 6 30/10/2013 11:56

This module is behavioral too as we have initial and always blocks. You should be able to undestand most of the

code. However, there are a few new concepts here. The $dumpfile and $dumpvars commands tell the Verilog

simulator (more on this ahead) to log the module's variables to the specified file, "d.vcd" in this case. You may

also be wondering what the #s do. These are Verilog delays. The delay the following instruction by a given amount

of time. For example, #4 clk=!clk; within an always block changes "clk" every four time units from 0 to 1,

producing a square wave. The time unit is a second by default.

Without using delays there is no way of making the program work. This is the way to control time in the design. You

may add delays to any instruction. For example, you could model the flip-flop's delay by adding some to its always

block. It's now easy to understand how the d=0; #9 d=1; #1 d=0; #1 d=1; ... lines produce the D

signal we want.

Finally, the $finish command tells the simulator to stop the simulation once the D signal was generated. If this

command was omitted the simulation would continue indefinetly because this time the always block has no

condition (there is no @ like in the flip-flop module).

Testbench module

This module just connects the tester module to the flip-flop module:

It is the most simple of the modules, but it's very dierent. This time it's structural code, that is, you define the

structure of the circuit. It's like describing the circuit diagram. In this case the final circuit is simply the flip-flop

connected to the tester. To create a flip flop use dff ff1(d,clk,q,qn);. First goes the module name,

followed by the part name, which could be almost any string, followed by the wires that connect to the module in

parenthesis. These must follow the order in the module's declaration. In a structural module we use wires. Regs are

not necessary because they are defined inside the dierent modules.

$dumpfile("dff.vcd");

$dumpvars;

//Generate input signal d

d=0; #9 d=1; #1 d=0; #1 d=1; #2 d=0; #1 d=1; #12 d=0;

#1 d=1; #2 d=0; #1 d=1; #1 d=0; #1 d=1; #1 d=0; # 7 d=1;

#8 $finish;

end

//Generate periodic clock signal

always

begin

#4 clk=!clk;

end

endmodule

//Test bench connects the flip-flop to the tester module

module testbench;

wire clk,d,q,qn;

dff ff1(d,clk,q,qn);

tester tst1(q,qn,clk,d);

endmodule

Test bench module

Getting started with Icarus Verilog on Windows | ... http://codeitdown.com/icarus-verilog-on-windows/

4 of 6 30/10/2013 11:56

Compiling and simulating

Go ahead and copy/paste the modules into a text file, order doesn't matter. Call the file "d.v". The .v extension is

standard for Verilog files, but isn't required by the compiler. To compile open a Command Prompt at your working

directory (where you saved the file). A quick way to open a command prompt at any directory is to hold shi and

right-click the folder, then click "Open Command Window Here". Type:

The "-o" tells Icarus Verilog to "save output to the following file". The output is then saved to "d". This file is not

executable. It has to be run using vvp, the Icarus Verilog simulator which is the one that actually produces

simulation results, zeros and ones for each of the model variables, as a function of time. To run the simulation type:

This is what outputs the d.vcd file with all the simulation results. However if you open this file with your text editor

you'll see it's not easy to understand. To generate an easy-to-understand timing diagram from this file we use

GTKWave.

GTKWave does have a GUI. To open it press Windows key and type "gtkwave". Then click File -> Open New Tab and

chose the d.vcd file. Now you must add the variables in order to see their timing diagram. Click on "testbench" at

the le (SST panel) and then select all the variables using Ctrl or Shi and "Insert" them.

If everything is okay you should get a timing diagram exactly as the one at the beggining of the tutorial, just like the

following:

When testing your programs you'll have to go to the compiling-simulating-loading process every few minutes.

Remember you can use the up-down arrow keys while in the command prompt to access the last commands and

compile/simulate. On GTKWave use File->Reload Waveform to reload the .vcd file and refresh the timing diagrams

without having to reload each variable. By using these tips the whole proccess will take you a few seconds.

It's over. Now feel free to change the code around to see what happens. Mastering the use of delays, wires and regs

iverilog -o dff dff.v

vvp dff

Getting started with Icarus Verilog on Windows | ... http://codeitdown.com/icarus-verilog-on-windows/

5 of 6 30/10/2013 11:56

6

Like

Tweet Tweet

3

1

takes some time. See Verilog in One Day for a more in depth explanation of the language.

If you enjoyed this post, please consider leaving a comment or

subscribing to the RSS feed to have future articles delivered to your feed

reader.

Getting started with Icarus Verilog on Windows | ... http://codeitdown.com/icarus-verilog-on-windows/

6 of 6 30/10/2013 11:56

Vous aimerez peut-être aussi

- Projects With Microcontrollers And PICCD'EverandProjects With Microcontrollers And PICCÉvaluation : 5 sur 5 étoiles5/5 (1)

- Introduction To Verilog: What Is A Hardware Schematic ?Document5 pagesIntroduction To Verilog: What Is A Hardware Schematic ?Novelyn RabinoPas encore d'évaluation

- BE EXPERT IN JAVA Part- 2: Learn Java programming and become expertD'EverandBE EXPERT IN JAVA Part- 2: Learn Java programming and become expertPas encore d'évaluation

- Verilog BriefDocument12 pagesVerilog BriefShashin KunasegaranPas encore d'évaluation

- JavaScript Patterns JumpStart Guide (Clean up your JavaScript Code)D'EverandJavaScript Patterns JumpStart Guide (Clean up your JavaScript Code)Évaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Verilog Interview QuestionsDocument41 pagesVerilog Interview QuestionsrAM100% (17)

- Hacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesD'EverandHacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesÉvaluation : 5 sur 5 étoiles5/5 (1)

- Icarus Verilog Installation and Usage GuideDocument6 pagesIcarus Verilog Installation and Usage GuideunagarjunaPas encore d'évaluation

- 21-CP-6 (Report14) DLDDocument17 pages21-CP-6 (Report14) DLDAlmaas ChaudryPas encore d'évaluation

- Verilog ModuleDocument14 pagesVerilog ModuleMuskan YadavPas encore d'évaluation

- Verilog HDL Lectuer 5Document36 pagesVerilog HDL Lectuer 5Nilesh GulvePas encore d'évaluation

- ORACLE PL/SQL Interview Questions You'll Most Likely Be AskedD'EverandORACLE PL/SQL Interview Questions You'll Most Likely Be AskedÉvaluation : 5 sur 5 étoiles5/5 (1)

- DIGITAL SYSTEM DESIGN Manual1Document20 pagesDIGITAL SYSTEM DESIGN Manual1Muhammad shehr yarPas encore d'évaluation

- Verilog FAQ TIDBITSDocument31 pagesVerilog FAQ TIDBITSrAM100% (4)

- Java Multithreading Interview Questions And AnswersD'EverandJava Multithreading Interview Questions And AnswersPas encore d'évaluation

- Lec3Document38 pagesLec3love639111Pas encore d'évaluation

- Programming FPGAsDocument38 pagesProgramming FPGAssayuri8910Pas encore d'évaluation

- Verilog For PrintDocument15 pagesVerilog For PrintrppvchPas encore d'évaluation

- Implement Randc Function Using Rand in System Verilog ?Document22 pagesImplement Randc Function Using Rand in System Verilog ?ankurPas encore d'évaluation

- Eda Unit-1Document58 pagesEda Unit-1Prasanth VarasalaPas encore d'évaluation

- Lab 1Document5 pagesLab 1sean_bostic7193Pas encore d'évaluation

- Advanced Verilog CodingDocument76 pagesAdvanced Verilog Coding1234GAURAVPas encore d'évaluation

- Topic 5 Procedures and AssignmentsDocument3 pagesTopic 5 Procedures and AssignmentsECE TheivanayakiPas encore d'évaluation

- Gate-Level Simulation of GCD Circuit using Synopsys VCSDocument5 pagesGate-Level Simulation of GCD Circuit using Synopsys VCSVijay Kumar NPas encore d'évaluation

- System Verilog Interview QuestionDocument16 pagesSystem Verilog Interview QuestionAviraj GhanekarPas encore d'évaluation

- UNIT2Document59 pagesUNIT2YashwanthReddyPas encore d'évaluation

- VHDL Interview Question(s)Document8 pagesVHDL Interview Question(s)Sudheer AcharyaPas encore d'évaluation

- System Verilog: Question 1. What Is Callback ?Document15 pagesSystem Verilog: Question 1. What Is Callback ?Shreyas S R100% (1)

- Verilog Tutorial for Beginners - Learn the Essentials of this Hardware Description LanguageDocument4 pagesVerilog Tutorial for Beginners - Learn the Essentials of this Hardware Description LanguageNovelyn RabinoPas encore d'évaluation

- Verilog Basics in 15 PagesDocument14 pagesVerilog Basics in 15 PagesUday KumarPas encore d'évaluation

- Ver I Log TutorialDocument18 pagesVer I Log Tutorialritam yadavPas encore d'évaluation

- Snug Boston2013 Paper56 SlidesDocument31 pagesSnug Boston2013 Paper56 Slidesjupiter8053Pas encore d'évaluation

- Verilog Prep MaterialDocument11 pagesVerilog Prep MaterialSangeetha BajanthriPas encore d'évaluation

- Lab 4aDocument12 pagesLab 4awajeehaadeel57Pas encore d'évaluation

- VerilogDocument80 pagesVeriloggenx142Pas encore d'évaluation

- 10 - Behavioral ModelingDocument19 pages10 - Behavioral ModelingRashmi SinghPas encore d'évaluation

- EECS 151/251A ASIC Lab 2: RTL-level simulation of FIR filterDocument12 pagesEECS 151/251A ASIC Lab 2: RTL-level simulation of FIR filterNguyen Van ToanPas encore d'évaluation

- 2) Difference Between Blocking and Non-Blocking? (Verilog Interview Questions That Is MostDocument39 pages2) Difference Between Blocking and Non-Blocking? (Verilog Interview Questions That Is MostRAGUL RAJ SPas encore d'évaluation

- Vlsi Lab Manual 2010Document88 pagesVlsi Lab Manual 2010Karthik V KalyaniPas encore d'évaluation

- Verilog HDL Abstraction Levels ExplainedDocument17 pagesVerilog HDL Abstraction Levels Explainedhimanshu111100Pas encore d'évaluation

- Verilog VHDL vs. Verilog: Process BlockDocument3 pagesVerilog VHDL vs. Verilog: Process Blocksundar_mohan_2Pas encore d'évaluation

- Introduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual LabDocument4 pagesIntroduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual Labdeepakk_alpinePas encore d'évaluation

- 11 - Behavioral ModelingDocument14 pages11 - Behavioral ModelingRashmi SinghPas encore d'évaluation

- VerilogTutorial 2Document80 pagesVerilogTutorial 2Manjinder Singh BaathPas encore d'évaluation

- TSIU03: A Fairly Small VHDL Guide: Petter K Allstr Om, Mario Garrido (Petterk, Mariog) @isy - Liu.seDocument18 pagesTSIU03: A Fairly Small VHDL Guide: Petter K Allstr Om, Mario Garrido (Petterk, Mariog) @isy - Liu.seMB Fazli NisarPas encore d'évaluation

- Basic Verilog Programming: LAB KDocument11 pagesBasic Verilog Programming: LAB KKhawar RiazPas encore d'évaluation

- Verilog Lecture 3 - NoopurDocument64 pagesVerilog Lecture 3 - NoopurMonis KhanPas encore d'évaluation

- Resolve Infinite Loop Zero Delay GLSDocument9 pagesResolve Infinite Loop Zero Delay GLSJagadish KgPas encore d'évaluation

- Deepak Kumar Tala, Verilog Ver 2005Document279 pagesDeepak Kumar Tala, Verilog Ver 2005Truong Phong TuyenPas encore d'évaluation

- Procedural and Concurrent Blocks in Verilog 1706091941Document15 pagesProcedural and Concurrent Blocks in Verilog 1706091941Purna satya srinivas VempalaPas encore d'évaluation

- VLSI Lab MannualDocument107 pagesVLSI Lab MannualSadananda KrrishPas encore d'évaluation

- You Could Download File D - FF.VDocument133 pagesYou Could Download File D - FF.VPradeep BabuPas encore d'évaluation

- Fpga ApplicationsDocument6 pagesFpga ApplicationsBHEEMANPALLY SRIMANNARAYANA R2527004Pas encore d'évaluation

- DVCon Europe 2015 TA5 1 PaperDocument7 pagesDVCon Europe 2015 TA5 1 PaperJon DCPas encore d'évaluation

- Chapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)Document6 pagesChapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)amitpatel1991Pas encore d'évaluation

- Lab 4Document6 pagesLab 4Somil N SwarnaPas encore d'évaluation

- Average Waiting Time at Dental ClinicDocument12 pagesAverage Waiting Time at Dental ClinicJonas Ciabis100% (1)

- Padlock Sharper Image FingerprintDocument1 pagePadlock Sharper Image FingerprintHenryW.CampbellJr.Pas encore d'évaluation

- DBX DriveRack PA 2 BrochureDocument2 pagesDBX DriveRack PA 2 BrochureSound Technology LtdPas encore d'évaluation

- Monocrystalline - 50Wp - 200Wp: 50W - 200W 17.20V - 30.10V 27.5A - 7.85A 21.10V - 36.10V 2.95A - 8.34ADocument2 pagesMonocrystalline - 50Wp - 200Wp: 50W - 200W 17.20V - 30.10V 27.5A - 7.85A 21.10V - 36.10V 2.95A - 8.34ARia IndahPas encore d'évaluation

- Sabri Toyyab Resume Spring 2019Document2 pagesSabri Toyyab Resume Spring 2019api-457400663Pas encore d'évaluation

- Jumeirah Group Future IssuesDocument3 pagesJumeirah Group Future Issueshaelstone100% (1)

- Huffman & ShannonDocument30 pagesHuffman & ShannonDhamodharan SrinivasanPas encore d'évaluation

- Wireless DoorbellDocument20 pagesWireless Doorbellmujahed1987Pas encore d'évaluation

- My Ideal Week PDFDocument1 pageMy Ideal Week PDFAnonymous QE45TVC9e3Pas encore d'évaluation

- Critical Reading As ReasoningDocument18 pagesCritical Reading As ReasoningKyle Velasquez100% (3)

- Range and Angle Tracking Techniques for Moving Target EstimationDocument34 pagesRange and Angle Tracking Techniques for Moving Target Estimationmykingboody2156Pas encore d'évaluation

- Aggregate Crushing Value Test Lab ReportDocument2 pagesAggregate Crushing Value Test Lab ReportComr A Y ZarginaPas encore d'évaluation

- Complete Checklist for Manual Upgrades to Oracle Database 12c R1Document27 pagesComplete Checklist for Manual Upgrades to Oracle Database 12c R1Augustine OderoPas encore d'évaluation

- HRIS1Document24 pagesHRIS1UMESH VINAYAK ARVINDEKARPas encore d'évaluation

- Ludwig Von Bertalanffy-General System Theory-Braziller (1968) PDFDocument153 pagesLudwig Von Bertalanffy-General System Theory-Braziller (1968) PDFM_Eddie0% (1)

- 7 Strategies For Developing Your Own Curriculum As A New TeacherDocument5 pages7 Strategies For Developing Your Own Curriculum As A New TeacherKhusnul KhotimahPas encore d'évaluation

- Technology in Supply Chain ManagementDocument8 pagesTechnology in Supply Chain ManagementjasminePas encore d'évaluation

- 64-2103 Tweco Pistolas WeldskillDocument6 pages64-2103 Tweco Pistolas WeldskillcarlosPas encore d'évaluation

- L .. Eee - .: Distribution Voltage RegulatorsDocument11 pagesL .. Eee - .: Distribution Voltage RegulatorsSirajulPas encore d'évaluation

- Google Earth y Civil CadDocument3 pagesGoogle Earth y Civil CadRodneyPas encore d'évaluation

- Net HSMDocument4 pagesNet HSMJosé Tudela de la RosaPas encore d'évaluation

- Datasheet - SP 275K INH String InvDocument1 pageDatasheet - SP 275K INH String Invsharib26Pas encore d'évaluation

- Eye Comfort Testing by TUeV Rheinland PDFDocument11 pagesEye Comfort Testing by TUeV Rheinland PDFevangelos!Pas encore d'évaluation

- EZSkin v3 User GuideDocument16 pagesEZSkin v3 User GuidePg1978Pas encore d'évaluation

- Gordon M. Pugh Davidg - RasmussenDocument2 pagesGordon M. Pugh Davidg - RasmussenKuroKy KrausserPas encore d'évaluation

- Definitions of CEC2017 Benchmark Suite Final Version UpdatedDocument34 pagesDefinitions of CEC2017 Benchmark Suite Final Version Updatedpc100% (1)

- Centrifugal PumpsDocument20 pagesCentrifugal PumpsPiccollo640780% (5)

- Bowing Styles in Irish Fiddle Playing Vol 1 - David LythDocument58 pagesBowing Styles in Irish Fiddle Playing Vol 1 - David LythEmma Harry100% (1)

- Mapping UCLA Network DrivesDocument2 pagesMapping UCLA Network DriveswebscalePas encore d'évaluation

- Transistor InfoDocument3 pagesTransistor InfoErantha SampathPas encore d'évaluation

- Ultimate Guide to LinkedIn for Business: Access more than 500 million people in 10 minutesD'EverandUltimate Guide to LinkedIn for Business: Access more than 500 million people in 10 minutesÉvaluation : 5 sur 5 étoiles5/5 (5)

- How to Create Cpn Numbers the Right way: A Step by Step Guide to Creating cpn Numbers LegallyD'EverandHow to Create Cpn Numbers the Right way: A Step by Step Guide to Creating cpn Numbers LegallyÉvaluation : 4 sur 5 étoiles4/5 (27)

- How to Do Nothing: Resisting the Attention EconomyD'EverandHow to Do Nothing: Resisting the Attention EconomyÉvaluation : 4 sur 5 étoiles4/5 (421)

- The Ultimate LinkedIn Sales Guide: How to Use Digital and Social Selling to Turn LinkedIn into a Lead, Sales and Revenue Generating MachineD'EverandThe Ultimate LinkedIn Sales Guide: How to Use Digital and Social Selling to Turn LinkedIn into a Lead, Sales and Revenue Generating MachinePas encore d'évaluation

- Web Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyD'EverandWeb Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyÉvaluation : 4 sur 5 étoiles4/5 (13)

- Ultimate Guide to YouTube for BusinessD'EverandUltimate Guide to YouTube for BusinessÉvaluation : 5 sur 5 étoiles5/5 (1)

- A Great Online Dating Profile: 30 Tips to Get Noticed and Get More ResponsesD'EverandA Great Online Dating Profile: 30 Tips to Get Noticed and Get More ResponsesÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- The Social Media Bible: Tactics, Tools, and Strategies for Business SuccessD'EverandThe Social Media Bible: Tactics, Tools, and Strategies for Business SuccessÉvaluation : 3.5 sur 5 étoiles3.5/5 (19)

- Branding: What You Need to Know About Building a Personal Brand and Growing Your Small Business Using Social Media Marketing and Offline Guerrilla TacticsD'EverandBranding: What You Need to Know About Building a Personal Brand and Growing Your Small Business Using Social Media Marketing and Offline Guerrilla TacticsÉvaluation : 5 sur 5 étoiles5/5 (32)

- Linux: The Ultimate Beginner's Guide to Learn Linux Operating System, Command Line and Linux Programming Step by StepD'EverandLinux: The Ultimate Beginner's Guide to Learn Linux Operating System, Command Line and Linux Programming Step by StepÉvaluation : 4.5 sur 5 étoiles4.5/5 (9)

- Azure DevOps Engineer: Exam AZ-400: Azure DevOps Engineer: Exam AZ-400 Designing and Implementing Microsoft DevOps SolutionsD'EverandAzure DevOps Engineer: Exam AZ-400: Azure DevOps Engineer: Exam AZ-400 Designing and Implementing Microsoft DevOps SolutionsPas encore d'évaluation

- Monitored: Business and Surveillance in a Time of Big DataD'EverandMonitored: Business and Surveillance in a Time of Big DataÉvaluation : 4 sur 5 étoiles4/5 (1)

- The Internet Con: How to Seize the Means of ComputationD'EverandThe Internet Con: How to Seize the Means of ComputationÉvaluation : 5 sur 5 étoiles5/5 (6)

- TikTok Algorithms 2024 $15,000/Month Guide To Escape Your Job And Build an Successful Social Media Marketing Business From Home Using Your Personal Account, Branding, SEO, InfluencerD'EverandTikTok Algorithms 2024 $15,000/Month Guide To Escape Your Job And Build an Successful Social Media Marketing Business From Home Using Your Personal Account, Branding, SEO, InfluencerÉvaluation : 4 sur 5 étoiles4/5 (4)

- The Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpireD'EverandThe Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpirePas encore d'évaluation

- Get Into UX: A foolproof guide to getting your first user experience jobD'EverandGet Into UX: A foolproof guide to getting your first user experience jobÉvaluation : 4.5 sur 5 étoiles4.5/5 (5)

- The Linux Command Line Beginner's GuideD'EverandThe Linux Command Line Beginner's GuideÉvaluation : 4.5 sur 5 étoiles4.5/5 (23)

- Ten Arguments for Deleting Your Social Media Accounts Right NowD'EverandTen Arguments for Deleting Your Social Media Accounts Right NowÉvaluation : 4 sur 5 étoiles4/5 (388)

- Photographic Rendering with VRay for SketchUpD'EverandPhotographic Rendering with VRay for SketchUpÉvaluation : 5 sur 5 étoiles5/5 (2)

- Kill All Normies: Online Culture Wars From 4Chan And Tumblr To Trump And The Alt-RightD'EverandKill All Normies: Online Culture Wars From 4Chan And Tumblr To Trump And The Alt-RightÉvaluation : 3.5 sur 5 étoiles3.5/5 (126)

- The No-Code Startup: The complete guide to building apps without codeD'EverandThe No-Code Startup: The complete guide to building apps without codePas encore d'évaluation

- Your Network Is Your Net Worth: Unlock the Hidden Power of Connections for Wealth, Success, and Happiness in the Digital AgeD'EverandYour Network Is Your Net Worth: Unlock the Hidden Power of Connections for Wealth, Success, and Happiness in the Digital AgeÉvaluation : 3.5 sur 5 étoiles3.5/5 (43)