Académique Documents

Professionnel Documents

Culture Documents

74LS174

Transféré par

Raul Sedano Lau100%(1)100% ont trouvé ce document utile (1 vote)

206 vues3 pagesThe LSTTL / MSI SN54 / 74LS174 is a high speed hex-d flip-flop. The device is used primarily as a 6-bit edge-triggered storage register. The information on the D inputs is transferred to storage during the LOW to HIGH Clock transition.

Description originale:

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentThe LSTTL / MSI SN54 / 74LS174 is a high speed hex-d flip-flop. The device is used primarily as a 6-bit edge-triggered storage register. The information on the D inputs is transferred to storage during the LOW to HIGH Clock transition.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

100%(1)100% ont trouvé ce document utile (1 vote)

206 vues3 pages74LS174

Transféré par

Raul Sedano LauThe LSTTL / MSI SN54 / 74LS174 is a high speed hex-d flip-flop. The device is used primarily as a 6-bit edge-triggered storage register. The information on the D inputs is transferred to storage during the LOW to HIGH Clock transition.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 3

5-1

FAST AND LS TTL DATA

HEX D FLIP-FLOP

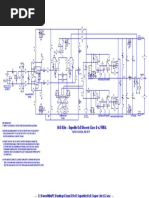

The LSTTL/ MSI SN54/ 74LS174 is a high speed Hex D Flip-Flop. The

device is used primarily as a 6-bit edge-triggered storage register. The

information on the D inputs is transferred to storage during the LOW to HIGH

clock transition. The device has a Master Reset to simultaneously clear all

flip-flops. The LS174 is fabricated with the Schottky barrier diode process for

high speed and is completely compatible with all Motorola TTL families.

Edge-Triggered D-Type Inputs

Buffered-Positive Edge-Triggered Clock

Asynchronous Common Reset

Input Clamp Diodes Limit High Speed Termination Effects

NOTE:

The Flatpak version

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

CONNECTION DIAGRAM DIP (TOP VIEW)

14 13 12 11 10 9

1 2 3 4 5 6 7

16 15

8

V

CC

MR

Q

5

D

5

D

4

Q

4

Q

3

D

3

CP

Q

0

D

0

D

1

Q

1

D

2

Q

2

GND

PIN NAMES LOADING (Note a)

HIGH LOW

D

0

D

5

CP

MR

Q

0

Q

5

Data Inputs

Clock (Active HIGH Going Edge) Input

Master Reset (Active LOW) Input

Outputs (Note b)

0.5 U.L.

0.5 U.L.

0.5 U.L.

10 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

5 (2.5) U.L.

NOTES:

a. 1 TTL Unit Load (U.L.) = 40 A HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74)

b. Temperature Ranges.

LOGIC DIAGRAM

D Q

CP

C

D

Q

5

Q

4

Q

3

Q

2

Q

1

Q

0

CP D

5

D

4

D

3

D

2

D

1

D

0

MR

14

2

6

7

3 4

5

9 11

12 10

13

15

D Q

CP

C

D

D Q

CP

C

D

D Q

CP

C

D

D Q

CP

C

D

D Q

CP

C

D

1

V

CC

= PIN 16

GND = PIN 8

= PIN NUMBERS

SN54/74LS174

HEX D FLIP-FLOP

LOW POWER SCHOTTKY

J SUFFIX

CERAMIC

CASE 620-09

N SUFFIX

PLASTIC

CASE 648-08

16

1

16

1

ORDERING INFORMATION

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

SN74LSXXXD SOIC

16

1

D SUFFIX

SOIC

CASE 751B-03

LOGIC SYMBOL

V

CC

= PIN 16

GND = PIN 8

D

5

D

4

D

3

D

2

D

1

D

0

9

1

3 4 6 11 13 14

CP

MR

Q

2

Q

1

Q

0

Q

3

Q

4

Q

5

2 5 7 10 12 15

5-2

FAST AND LS TTL DATA

SN54/74LS174

FUNCTIONAL DESCRIPTION

The LS174 consists of six edge-triggered D flip-flops with

individual D inputs and Q outputs. The Clock (CP) and Master

Reset (MR) are common to all flip-flops.

Each D inputs state is transferred to the corresponding flip-

flops output following the LOW to HIGH Clock (CP) transition.

A LOW input to the Master Reset (MR) will force all outputs

LOW independent of Clock or Data inputs. The LS174 is

useful for applications where the true output only is required

and the Clock and Master Reset are common to all storage

elements.

TRUTH TABLE

Inputs (t = n, MR = H) Outputs (t = n+1) Note 1

D Q

H H

L L

Note 1: t = n + 1 indicates conditions after next clock.

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

V

CC

Supply Voltage 54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

T

A

Operating Ambient Temperature Range 54

74

55

0

25

25

125

70

C

I

OH

Output Current High 54, 74 0.4 mA

I

OL

Output Current Low 54

74

4.0

8.0

mA

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Symbol Parameter

Limits

Unit Test Conditions Symbol Parameter Min Typ Max Unit Test Conditions

V

IH

Input HIGH Voltage 2.0 V

Guaranteed Input HIGH Voltage for

All Inputs

V

IL

Input LOW Voltage

54 0.7

V

Guaranteed Input LOW Voltage for

All Inputs

V

IL

Input LOW Voltage

74 0.8

V

Guaranteed Input LOW Voltage for

All Inputs

V

IK

Input Clamp Diode Voltage 0.65 1.5 V V

CC

= MIN, I

IN

= 18 mA

V

OH

Output HIGH Voltage

54 2.5 3.5 V

V

CC

= MIN, I

OH

= MAX, V

IN

= V

IH

or V

IL

per Truth Table

V

OH

Output HIGH Voltage

74 2.7 3.5 V

V

CC

= MIN, I

OH

= MAX, V

IN

= V

IH

or V

IL

per Truth Table

V

OL

Output LOW Voltage

54, 74 0.25 0.4 V I

OL

= 4.0 mA

V

CC

= V

CC

MIN,

V

IN

= V

IL

or V

IH

per Truth Table

V

OL

Output LOW Voltage

74 0.35 0.5 V I

OL

= 8.0 mA

V

IN

= V

IL

or V

IH

per Truth Table

I

IH

Input HIGH Current

20 A V

CC

= MAX, V

IN

= 2.7 V

I

IH

Input HIGH Current

0.1 mA V

CC

= MAX, V

IN

= 7.0 V

I

IL

Input LOW Current 0.4 mA V

CC

= MAX, V

IN

= 0.4 V

I

OS

Short Circuit Current (Note 1) 20 100 mA V

CC

= MAX

I

CC

Power Supply Current 26 mA V

CC

= MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

5-3

FAST AND LS TTL DATA

SN54/74LS174

AC CHARACTERISTICS (T

A

= 25C)

Symbol Parameter

Limits

Unit Test Conditions Symbol Parameter Min Typ Max Unit Test Conditions

f

MAX

Maximum Input Clock Frequency 30 40 MHz

V

CC

= 5.0 V

C

L

= 15 pF

t

PHL

Propagation Delay, MR to Output 23 35 ns V

CC

= 5.0 V

C

L

= 15 pF

t

PLH

t

PHL

Propagation Delay, Clock to Output

20

21

30

30

ns

CC

= 5.0 V

C

L

= 15 pF

AC SETUP REQUIREMENTS (T

A

= 25C)

Symbol Parameter

Limits

Unit Test Conditions Symbol Parameter Min Typ Max Unit Test Conditions

t

W

Clock or MR Pulse Width 20 ns

V

CC

= 5.0 V

t

s

Data Setup Time 20 ns

V

CC

= 5.0 V

t

h

Data Hold Time 5.0 ns

V

CC

= 5.0 V

t

rec

Recovery Time 25 ns

AC WAVEFORMS

Figure 1. Clock to Output Delays, Clock Pulse Width,

Frequency, Setup and Hold Times Data to Clock

Figure 2. Master Reset to Output Delay, Master Reset

Pulse Width, and Master Reset Recovery Time

*The shaded areas indicate when the input is permitted to

*change for predictable output performance.

1.3 V

1.3 V 1.3 V 1.3 V

1.3 V 1.3 V

1.3 V

1.3 V

1.3 V

1.3 V 1.3 V

1/f

max

t

w

t

s(H)

t

h(H)

t

s(L)

t

h(L)

CP

t

PHL

t

PLH

t

W

t

PHL

CP

t

rec

Q

MR

D

Q

*

1.3 V

DEFINITIONS OF TERMS

SETUP TIME (t

s

) is defined as the minimum time required

for the correct logic level to be present at the logic input prior to

the clock transition from LOW to HIGH in order to be recog-

nized and transferred to the outputs.

HOLD TIME (t

h

) is defined as the minimum time following

the clock transition from LOW to HIGH that the logic level must

be maintained at the input in order to ensure continued recog-

nition. A negative HOLD TIME indicates that the correct logic

level may be released prior to the clock transition from LOW to

HIGH and still be recognized.

RECOVERY TIME (t

rec

) is defined as the minimum time

required between the end of the reset pulse and the clock

transition from LOW to HIGH in order to recognize and transfer

HIGH Data to the Q outputs.

Vous aimerez peut-être aussi

- 74LS175Document3 pages74LS175Yesenia RojoPas encore d'évaluation

- 74164Document4 pages74164milkyway69Pas encore d'évaluation

- 74LS373Document5 pages74LS373Maurício Matos de AlmeidaPas encore d'évaluation

- 74LS74 PDFDocument3 pages74LS74 PDFDeni KhanPas encore d'évaluation

- 8-BIT SERIAL-IN PARALLEL-OUT SHIFT REGISTERDocument4 pages8-BIT SERIAL-IN PARALLEL-OUT SHIFT REGISTERCesar GutierrezPas encore d'évaluation

- 74LS75 PDFDocument4 pages74LS75 PDFDeni KhanPas encore d'évaluation

- 4 X 4 Register File Open-Collector SN54/74LS170: Low Power SchottkyDocument4 pages4 X 4 Register File Open-Collector SN54/74LS170: Low Power Schottkydistrict19Pas encore d'évaluation

- SN74LS164NDocument5 pagesSN74LS164NAlex ReyesPas encore d'évaluation

- 74AHC259 74AHCT259: 1. General DescriptionDocument17 pages74AHC259 74AHCT259: 1. General Descriptiongreentea601Pas encore d'évaluation

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocument8 pagesDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeatureshuvillamilPas encore d'évaluation

- 74LS90 Contador AsincronoDocument7 pages74LS90 Contador AsincronoFISRAELGRPas encore d'évaluation

- Datos 74LS166-2Document5 pagesDatos 74LS166-2valarconbravoPas encore d'évaluation

- 74LS76 FF JK Con Set y ClearDocument2 pages74LS76 FF JK Con Set y ClearZoy HavelPas encore d'évaluation

- BCD Decade/Modulo 16 Binary Synchronous Bi-Directional Counters SN54/74LS168 SN54/74LS169Document6 pagesBCD Decade/Modulo 16 Binary Synchronous Bi-Directional Counters SN54/74LS168 SN54/74LS169Ariel HdezPas encore d'évaluation

- 74LS151 Multiplexer Truth TableDocument3 pages74LS151 Multiplexer Truth TableJack GonPas encore d'évaluation

- 9-BIT PARITY GENERATORS AND CHECKERSDocument2 pages9-BIT PARITY GENERATORS AND CHECKERSdistrict19Pas encore d'évaluation

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601Pas encore d'évaluation

- DatasheetDocument4 pagesDatasheetMeetha ShenoyPas encore d'évaluation

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DPas encore d'évaluation

- Presettable Bcd/Decade Up/Down Counter Presettable 4-Bit Binary Up/Down Counter SN54/74LS192 SN54/74LS193Document9 pagesPresettable Bcd/Decade Up/Down Counter Presettable 4-Bit Binary Up/Down Counter SN54/74LS192 SN54/74LS193EDERTREVISANPas encore d'évaluation

- 74HCT259D 8-Bit Addressable Latch DATA SHEETDocument11 pages74HCT259D 8-Bit Addressable Latch DATA SHEETMarc BengtssonPas encore d'évaluation

- 74HC573 Octal LatchDocument13 pages74HC573 Octal LatchWonzPas encore d'évaluation

- 74LS93Document9 pages74LS93John RedwindPas encore d'évaluation

- 74LS283Document4 pages74LS283tongers23Pas encore d'évaluation

- Datasheet 74ls83 PDFDocument3 pagesDatasheet 74ls83 PDFLioni Dávila AguilarPas encore d'évaluation

- Quad D Flip-Flop SN54/74LS175: Low Power SchottkyDocument5 pagesQuad D Flip-Flop SN54/74LS175: Low Power SchottkyEddy DiazPas encore d'évaluation

- CD74HC238Document7 pagesCD74HC238roozbehxoxPas encore d'évaluation

- A6841 DABiC-5 8-Bit Serial Input Latched Sink DriversDocument10 pagesA6841 DABiC-5 8-Bit Serial Input Latched Sink DriversJennifer NealPas encore d'évaluation

- 74LS193Document8 pages74LS193Luis Alberto Villa ChávezPas encore d'évaluation

- 8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsDocument14 pages8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsskiziltoprakPas encore d'évaluation

- 74LS112Document2 pages74LS112Freddy SarabiaPas encore d'évaluation

- 74LS42 PDFDocument3 pages74LS42 PDFDeni KhanPas encore d'évaluation

- 74 Ls 175Document8 pages74 Ls 175AndrescronquePas encore d'évaluation

- 74HC193 74HCT193: 1. General DescriptionDocument29 pages74HC193 74HCT193: 1. General Descriptionsupriyo110Pas encore d'évaluation

- 1-Of-10 Decoder/Driver Open-Collector SN54/74LS145: Low Power SchottkyDocument3 pages1-Of-10 Decoder/Driver Open-Collector SN54/74LS145: Low Power SchottkyShyamsundar JenaPas encore d'évaluation

- Integrated Circuits Data Sheet: 74HC/HCT173 Quad D-Type Flip-FlopDocument11 pagesIntegrated Circuits Data Sheet: 74HC/HCT173 Quad D-Type Flip-FlopBryan Bethke IIIPas encore d'évaluation

- 74197Document8 pages74197Mary RodríguezPas encore d'évaluation

- Universal 4-Bit Shift Register SN54/74LS195A: Low Power SchottkyDocument6 pagesUniversal 4-Bit Shift Register SN54/74LS195A: Low Power SchottkyLuis Alfredo QuentaPas encore d'évaluation

- Foaie Catalog MUX 74HC153Document7 pagesFoaie Catalog MUX 74HC153Andrei MolochPas encore d'évaluation

- 4 BIT D LatchDocument5 pages4 BIT D LatchBront PaulPas encore d'évaluation

- DM 74 Ls 90Document6 pagesDM 74 Ls 90Clesio MichaelPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- 110 Waveform Generator Projects for the Home ConstructorD'Everand110 Waveform Generator Projects for the Home ConstructorÉvaluation : 4 sur 5 étoiles4/5 (1)

- Beginning Digital Electronics through ProjectsD'EverandBeginning Digital Electronics through ProjectsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142D'EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Pas encore d'évaluation

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1D'EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Évaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsD'EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsPas encore d'évaluation

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- ISA-TR88.0.03-1996: Possible Recipe Procedure Presentation FormatsDocument22 pagesISA-TR88.0.03-1996: Possible Recipe Procedure Presentation FormatsRaul Sedano LauPas encore d'évaluation

- Wiring Practices For Hazardous (Classified) Locations Instrumentation Part 1: Intrinsic SafetyDocument52 pagesWiring Practices For Hazardous (Classified) Locations Instrumentation Part 1: Intrinsic SafetyEuro Guillermo Guerrero PrietoPas encore d'évaluation

- TablasDocument1 pageTablasRaul Sedano LauPas encore d'évaluation

- 4731BDocument3 pages4731BRaul Sedano LauPas encore d'évaluation

- 74LS194Document15 pages74LS194Raul Sedano Lau100% (1)

- 74LS164Document8 pages74LS164enos_marcosPas encore d'évaluation

- 74LS165Document6 pages74LS165Raul Sedano Lau100% (1)

- WEG Automation Drives and Controls Usadrivescontrols Brochure EnglishDocument16 pagesWEG Automation Drives and Controls Usadrivescontrols Brochure EnglishAndrés NarvaezPas encore d'évaluation

- Circuit Elements (I) - Resistors (Linear) Ohm's Law Open and ShortDocument33 pagesCircuit Elements (I) - Resistors (Linear) Ohm's Law Open and ShortMichaelPas encore d'évaluation

- DMCR Technical BrochureDocument31 pagesDMCR Technical Brochuremardhiah100% (2)

- Using Labview To Measure Temperature With A ThermistorDocument18 pagesUsing Labview To Measure Temperature With A ThermistorjdaudpotoPas encore d'évaluation

- 2012 Dep of Conductivity On Charge Density and Echem Pot in Polymer SC W Ionic LiquidsDocument10 pages2012 Dep of Conductivity On Charge Density and Echem Pot in Polymer SC W Ionic LiquidsChris SmithPas encore d'évaluation

- DocumentDocument3 pagesDocumentKingsleyPas encore d'évaluation

- 9 Wireless Power Transfer Projects PDF: Accelerate Your InnovationDocument15 pages9 Wireless Power Transfer Projects PDF: Accelerate Your InnovationSouvik KolePas encore d'évaluation

- KLC 1508us1521usDocument17 pagesKLC 1508us1521usalbertec51Pas encore d'évaluation

- DPP-1 To 8 - Modern Physics - JEEDocument54 pagesDPP-1 To 8 - Modern Physics - JEEKeerthana Reddy DomaPas encore d'évaluation

- Electrical Engineering and InstrumentationDocument11 pagesElectrical Engineering and InstrumentationKrishnan DandapaniPas encore d'évaluation

- 22 MM Push Buttons XB4 Electrical Components: Table 19.89: Body/Mounting CollarDocument2 pages22 MM Push Buttons XB4 Electrical Components: Table 19.89: Body/Mounting CollarMohammed AbdelsalamPas encore d'évaluation

- Cable AmpacityDocument71 pagesCable Ampacitygovindarul0% (1)

- g5340 250kw Kohler GeneratorDocument4 pagesg5340 250kw Kohler Generatorwilliam000111Pas encore d'évaluation

- TdepDocument26 pagesTdepNitin Maurya75% (4)

- SINAMICS DriveDocument61 pagesSINAMICS Driveطه محمدPas encore d'évaluation

- CL 200Document159 pagesCL 200João Paulo CostaPas encore d'évaluation

- UcD-Super Lite V.2 FINALDocument1 pageUcD-Super Lite V.2 FINALbeytullahPas encore d'évaluation

- CPC 100 Ordering Information ENUDocument31 pagesCPC 100 Ordering Information ENUConstantPas encore d'évaluation

- 17 Dielectric Propertiesand Insulation System DesignDocument5 pages17 Dielectric Propertiesand Insulation System DesignDinesh Selvakumar100% (1)

- Tesla's Metaphysics and Cosmology (Velimir Abramovic)Document36 pagesTesla's Metaphysics and Cosmology (Velimir Abramovic)THE NIKOLA TESLA INSTITUTE90% (10)

- 2.PID6281995 - IEEE PDF Express PassedDocument6 pages2.PID6281995 - IEEE PDF Express PassedRitwik ChowdhuryPas encore d'évaluation

- A Brief Introduction To Scalar PhysicsDocument48 pagesA Brief Introduction To Scalar PhysicsmontalkPas encore d'évaluation

- List of Mandatory Documents & Check ListDocument6 pagesList of Mandatory Documents & Check ListDuraipandi RajaPas encore d'évaluation

- Operation of A DSTATCOM in Voltage Control ModeDocument7 pagesOperation of A DSTATCOM in Voltage Control Modeswathi_ammalu007Pas encore d'évaluation

- Eaton 9PX 5000-11000VA & 3kVA 3U Rack-Tower UPS Guide SpecificationDocument9 pagesEaton 9PX 5000-11000VA & 3kVA 3U Rack-Tower UPS Guide SpecificationcarlosPas encore d'évaluation

- Led Street LightDocument15 pagesLed Street LightPOLANKI RAVITEJAPas encore d'évaluation

- External SPD in Metal Enclosure: Data Sheet ENM0003 ENM0004 and ENM0005Document3 pagesExternal SPD in Metal Enclosure: Data Sheet ENM0003 ENM0004 and ENM0005junak72Pas encore d'évaluation

- Miniature Circuit BreakersDocument78 pagesMiniature Circuit BreakersIndera ArifiantoPas encore d'évaluation

- Ariston mtp1912f 81396110201 tb28656 Tech.mDocument8 pagesAriston mtp1912f 81396110201 tb28656 Tech.mHislerPas encore d'évaluation