Académique Documents

Professionnel Documents

Culture Documents

Memoria

Transféré par

Tide LinharesCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Memoria

Transféré par

Tide LinharesDroits d'auteur :

Formats disponibles

MEMRIAS SEMICONDUTORAS

*Configuraes Bsicas

*Tipos e Me!"ria

*Associaes e Me!"rias

So dispositivos utilizados em muitos sistemas digitais, principalmente nos

computadores ou perifricos e que tem a capacidade de armazenar informaes

binrias (zeros e uns).

Configuraes Bsicas

!istem vrios tipos de mem"rias, as quais possuem caracter#sticas e aplicaes

especificas, mas que podem ser representadas genericamente pelo diagrama

funcional a seguir$

%ota&se que uma mem"ria tem tr's barramentos (con(unto de lin)as)$

*arramento de endereos (address bus)$ fornece a posio da informao

(dados) que se dese(a acessar+

*arramento de dados (data bus)$ contm informao a ser lida ou

armazenado no endereo acessado+

*arramento de controle (control bus)$ formado por sinais que controlam o

funcionamento da mem"ria$ )abilitao, leitura, escrita, programao, etc.

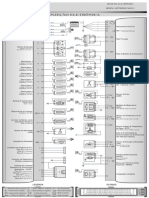

, arquitetura de mem"ria formada geralmente por uma matriz, decodificadores e

um bloco de controle como mostra a figura a seguir$

,s lin)as de endereos so direcionadas a dois decodificadores (lin)a e coluna).

- cruzamento lin)a&coluna seleciona uma posio de mem"ria, sendo que o

1

Memria

Controle

Endereos

Dados

D

E

C

L

I

N

H

A

DECODIFICADOR COLUNA

C

O

N

T

R

O

L

E

Dados

Endereos

Controle C

ROM R

n.mero de posies dado por /

n

, onde n representa o n.mero de lin)a de

endereo.

0ada posio contm uma ou vrias clulas de mem"rias, onde cada clula

responsvel pelo armazenamento da informao de um bit.

-s decodificadores fazem, portanto, a seleo da posio de mem"ria que se

dese(a acessar e o bloco de controle determina a operao que deve ser realizado

nesta posio como, por e!emplo, a leitura da informao.

1ara representar a capacidade de uma mem"ria utiliza&se a e!presso genrica

p ! b onde p representa o n.mero de posies de mem"ria e b o n.mero de bits

de dados.

E#e!p$o%

2ma mem"ria de 34!/ tem 34 posies com / bits de dados em cada posio,

perfazendo um total de 5/ clulas de mem"ria.

, figura abai!o representa a arquitetura interna de uma mem"ria 34!/ com escrita

e leitura.

1ara compreender mel)or seu funcionamento, coloca&se um valor qualquer no

barramento de endereos, por e!emplo$ ,5 ,/ ,3 ,6 7 3633.

%este e!emplo, o decodificador de lin)a contm o endereo ,3 ,6 733 (ativando a

sa#da 85) e o decodificador de coluna de endereo ,5 ,/736 (ativando a sa#da 9/)

selecionando, assim, a posio )ac)urada. %este caso, os bits de dados :3 e :6

correspondentes ficam dispon#veis para leitura ou escrita de uma informao,

dependendo dos n#veis l"gicos dos bits de controle,

CE

e

W / R

como mostra o

tabela de sinais de controle a seguir$

CE W / R stado da mem"ria

6 6 ;abilita escrita

6 3 ;abilita leitura

3 ! <em"ria desabilitada

2

D1

D0

D1 D0

D

E

C

L

I

N

H

A

DECODIFICADOR COLUNA

C

O

N

T

R

O

L

E

A3

A2

A1

A0

W / R

CE

X0

X1

X2

X3

00

01

10

11

00 01 10 11

0 1 2 3

D1 D0 D1 D0 D1 D0

D1 D0 D1 D0 D1 D0 D1 D0

D1 D0 D1 D0 D1 D0 D1 D0

D1 D0 D1 D0 D1 D0 D1 D0 D

ROM RR

RAM R

=%:

I

3

I

2

I

1

I

0

A

!

A

3

A

2

A

1

"E

A

0

O

3

O

2

O

1

O

0

Entradas de Dados

0 1 1 0

1 0 0 1

1 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

1 1 0 0

1 1 0 1

0 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

0 0 0 0 0

0 0 0 0 1

0 0 0 1 0

0 0 0 1 1

0 0 1 0 0

0 0 1 0 1

1 1 1 0 1

1 1 1 1 0

1 1 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

%ota&se que, enquanto o sinal

CE

est ativado (n#vel l"gico 6), a mem"ria est

)abilitada para uma operao de escrita (

W / R

76) ou leitura (

W / R

73), caso

contrrio (

CE

73) a mem"ria est desabilitada independente do n#vel l"gico do

sinal de

W / R

(

W / R

7irrelevante) e, portanto, as operaes de escrita e leitura

no podem ser e!ecutadas.

,s mem"rias, em geral, possuem duas caracter#sticas bsicas que devem ser

analisadas para a sua utilizao em um determinado sistema$

0apacidade$ quantidade de bits que capaz de armazenar+

>empo de ,cesso$ tempo necessrio para colocar os dados armazenados

na sa#da (ciclo de leitura).

,lm disso, cada tipo de mem"ria possui caracter#sticas pr"prias que determinam

sua aplicabilidade. %este aspecto, as mem"rias podem ser classificadas em$

<em"ria voltil$ as informaes armazenadas so perdidas ao se desligar a

alimentao.

<em"ria no voltil$ as informaes armazenadas na mem"ria

permanecem inalteradas mesmo sem alimentao.

TI&OS DE MEMRIA%

?-<$ read onl@ memor@ (mem"ria apenas de leitura) A esta mem"ria permite

somente a leitura de dados, previamente armazenados em sua fabricao.

1?-<$ programmable read onl@ memor@ (mem"ria apenas de leitura

programvel) A mediante programao permite armazenamento de informaes

pelo pr"prio usurio, porm, de modo definitivo. ,p"s esta programao a

mem"ria se transforma em uma ?-<.

1?-<$ erasable programmable read onl@ memor@ (mem"ria apenas de leitura

programvel e apagvel) A permite a programao de modo semel)ante a 1?-<,

podendo ser apagada mediante ban)o de luz ultravioleta aplicado a (anela

e!istente em seu encapsulamento.

1?-< -2

/

1?-<$ eletricall@ erasable programmable read onl@ memor@

(mem"ria apenas de leitura programvel e apagvel eletricamente) A permite

programao de maneira id'ntica a 1?-<, porm o apagamento feito atravs

de sinais eltricos aplicados em seus terminais.

?,<$ random ,ccess memor@ (mem"ria de acesso aleat"rio) A permite a escrita e

leitura de dados, com acesso Bs localidades de maneira aleat"ria. C uma mem"ria

voltil, ou se(a, perde as informaes armazenadas ao ser cortada a alimentao.

33

ROM R #arra de

endereos

$%&&

#arra de Dados #

RAM R

=%:

I

3

I

2

I

1

I

0

A

!

A

3

A

2

A

1

"E

A

0

O

3

O

2

O

1

O

0

Entradas de Dados

0 1 1 0

1 0 0 1

1 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

1 1 0 0

1 1 0 1

0 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

0 0 0 0 0

0 0 0 0 1

0 0 0 1 0

0 0 0 1 1

0 0 1 0 0

0 0 1 0 1

1 1 1 0 1

1 1 1 1 0

1 1 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

>ipos de ?,<$

sttica$ o dado inserido em uma das localidades permanece esttico.

:inDmica$ o dado inserido precisa ser regravado de tempos em tempos

atravs de operao denominada Erefres)F (refrescar). 1ossui a vantagem

de ter uma alta capacidade de armazenamento numa .nica pastil)a.

E'ERC(CIOS%

:ada uma mem"ria 5/!G e sua tabela de endereos e palavras como visto abai!o$

3 & :escreva as condies de cada entrada e sa#da quando o conte.do da posio

cu(o endereo 66366 deva ser lido.

ntrada de endereos 66366

ntrada de dados$ !!!! ( no utilizados)

W / R

$ n#vel alto

;abilitao da mem"ria (<)$ alta

Sa#da de dados$ 6663

/ A :escreva as condies de cada entrada e sa#da quando a palavra 3336 deve

ser escrita na posio de endereo 63363.

Soluo$

ntrada de endereos$ 63363

ntrada de dados$ 3336

W / R

$ n#vel bai!o

;abilidade de mem"ria (<)$ alta

Sa#da de dados$ !!!! ( no utilizados)

5 A 2ma determinada mem"ria tem uma capacidade de GH ! I.

a) quantas lin)as de entrada de dados e sa#da de dados ela temJ dados I bits

b) quantas lin)as de endereo ela temJ G6KI bits

!

A

0

A

1

A

2

D

0

A

3

A

!

D

1

A

'

A

(

D

2

A

)

A

*

D

3

A

+

"E "

A

0

A

1

A

2

D

0

A

3

A

!

D

1

A

'

A

(

D

2

A

)

A

*

D

3

A

+

"E ""

RAM R

=%:

#arra de

endereos

$%&&

#arra de Dados

Entradas de

Endereos

I

3

I

2

I

1

I

0

A

!

A

3

A

2

A

1

"E

A

0

O

3

O

2

O

1

O

0

Entradas de Dados

,a-das de Dados

Controle de

Le.t/ra / Es&r.ta

Ha0.l.ta1o de

"e23r.a

",#

0 1 1 0

1 0 0 1

1 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

1 1 0 0

1 1 0 1

0 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

C4l/la de "e23r.a

0 0 0 0 0

0 0 0 0 1

0 0 0 1 0

0 0 0 1 1

0 0 1 0 0

0 0 1 0 1

1 1 1 0 1

1 1 1 1 0

1 1 1 1 1

1 0 0 0

0 0 0 1

0 0 0 0

Endereos

c) qual a sua capacidade em b@tesJ G6KIb@tes

G A :etermine as palavras de endereo inicial e final para as mem"rias$

a) /H ! I

6666 6666 6666) inicio

6333 3333 3333) final

L M M) palavra

b) IH ! 3

6666 6666 6666) inicio

3333 3333 3333) final

M M M) palavra

c) 4G H ! G

6666 6666 6666 6666 6666 6666 ) inicio

3333 3333 3333 3333 3333 3333 ) final

M M M M M M) palavra

N A :esen)e a arquitetura interna de uma ?,< I ! /.

'

A

0

A

1

A

2

D

0

A

3

A

!

D

1

A

'

A

(

D

2

A

)

A

*

D

3

A

+

"E "

A

0

A

1

A

2

D

0

A

3

A

!

D

1

A

'

A

(

D

2

A

)

A

*

D

3

A

+

"E "

Controle C

A

0

D

0

A

11

D)

"E "

A

0

D

0

A

11

D)

"E "

A

0

D

0

A

11

D)

"E "

A

0

D

0

A

11

D)

"E "

ASSOCIA)*O DE MEMRIAS

C poss#vel fazer associaes de mem"rias a fim de se obter maior capacidade de

armazenamento total de um sistema.

!istem dois tipos bsicos de associaes$

Associaes paralelas de memrias$ para o aumento do n.mero de lin)as

de dados por posio de mem"ria.

Associao srie de memrias$ para aumento do n.mero de posies de

mem"ria.

Associa+o para$e$a e !e!"rias%

1ara aumentar o n.mero de lin)as de dados por posio de mem"ria, devem&se

ligar em paralelo as lin)as de endereo e controle mantendo&se independentes as

lin)as de dados.

0om isto, ao selecionar&se uma determinada posio (dada pelas lin)as de

endereo) todas as mem"rias estaro endereadas na mesma posio, porm

com dados independentes.

,o se manipularem as lin)as de controle, todas as mem"rias estaro no mesmo

estado (leitura, escrita, etc) multiplicando&se, assim, a capacidade de bits por

posio de mem"ria.

%este tipo de configurao, tem&se um subsistema de mem"rias com total de

lin)as de dados igual ao somat"rio das lin)as de dados das mem"rias ligadas em

paralelo.

E#e!p$o$ <ontar uma mem"ria de 3H ! I a partir de mem"rias 3H ! G.

Interligam-se as linhas de endereo e controle, mantendo as linhas de dados independentes.

(

Endereos

"e23r.a

"e23r.a

"e23r.a

Controle

Dados

A

0

A

1

A

2

D

0

A

3

A

!

D

1

A

'

A

(

D

2

A

)

A

*

D

3

A

+

"E "

A

0

A

1

A

2

D

0

A

3

A

!

D

1

A

'

A

(

D

2

A

)

A

*

D

3

A

+

"E "

D0

D1

D2

D3

D!

D'

D(

D)

Controle C

A

0

D

0

A

11

D)

"E "

A

0

D

0

A

11

D)

"E "

A

0

D

0

A

11

D)

"E "

A

0

D

0

A

11

D)

"E "

Associa+o s,rie e !e!"ria%

1ara aumentar o n.mero de posies de mem"ria devem&se ligar em paralelo as

lin)as de endereos, dados e controle, mantendo&se independentes somente as

lin)as de )abilitao de mem"ria.

stas lin)as so controladas por um circuito combinacional que deve fazer a

seleo das mem"rias de forma seqOencial ()abilitando&as uma por vez).

,ssim, o endereo inicial de uma mem"ria a posio imediatamente

subseqOente ao endereo final de mem"ria anterior, colocando as mem"rias em

srie.

- controle deste circuito combinacional que faz a seleo das mem"rias

realizado pelas lin)as de endereos que completam o endereamento total do

sistema.

!emplo$ subsistema de mem"ria 34 H (7/

3G

)! I a partir de mem"rias GH ! I (GH 7

/

3/

), interliga&se endereos, dados e controle, mantendo&se independentes apenas

os sinais de )abilitao das mem"rias.

,35 ,3/ ,33 ,36 ,K ,I ,L ,4 ,N ,G ,5 ,/ ,3 ,6

6 6 6 6 6 6 6 6 6 6 6 6 6 6

6 6 3 3 3 3 3 3 3 3 3 3 3 3

ndereo inicial da <em"ria 3

ndereo final da <em"ria 3

6 3 6 6 6 6 6 6 6 6 6 6 6 6

6 3 3 3 3 3 3 3 3 3 3 3 3 3

ndereo inicial da <em"ria /

ndereo final da <em"ria /

3 6 6 6 6 6 6 6 6 6 6 6 6 6

3 6 3 3 3 3 3 3 3 3 3 3 3 3

ndereo inicial da <em"ria 5

ndereo final da <em"ria 5

3 3 6 6 6 6 6 6 6 6 6 6 6 6

3 3 3 3 3 3 3 3 3 3 3 3 3 3

ndereo inicial da <em"ria G

ndereo final da <em"ria G

)

Endereos

"e23r.a

"e23r.a

"e23r.a

Controle C

Dados

,ele1o

A

0

D

0

A

11

D)

"E "

,ele1o

A

12

A

13

Dados

Endereos

Controle

1

A

0

D

0

A

11

D)

"E "

2

A

0

D

0

A

11

D)

"E "

3

A

0

D

0

A

11

D)

"E "

!

De&od5 26!

E#erc-cios%

.uano /ou0er associa+o S,rie1&ara$e$o fa2er pri!eira!en3e e! para$e$o44

e ap"s e! s,rie

3 A 2tilizando blocos de ?,< 3(/

36

) H ! G, forme uma de 3(/

36

) H ! I. screva as

palavras de endereos inicial e final.

/ A Pdem ao anterior, para a partir de blocos ?,< I(/

35

) ! G formar um sistemas

34(/

3G

) ! I.

5 A 1reenc)a o quadro com as mem"rias que representem as caracter#sticas

dadas.

Mais e#erc-cios%

3 & :etermine a palavra de endereos inicial e final de uma mem"ria de 3 < ! 34.

/ A 2tilizando blocos de mem"ria ?,< 3/I ! G, forme uma de /N4 ! I. screva a

palavra de endereo inicial e final de cada bloco integrado ao sistema.

5 A , partir de blocos ?,< 4G ! G, esquematize uma ?,< 4G ! I. screva as

palavras de endereamento inicial e final de cada ?,< integrada ao sistema.

G A :a mesma forma que o e!erc#cio 5, para uma ?,< N3/ ! G com blocos de

estrutura 3/I ! G.

N A Pdem, para uma ?,< 4G ! I, obtida com blocos 5/ ! G.

4 A labore um contador ass#ncrono de 3I(36) a 6. - circuito deve possuir um

terminal que, quando aterrado, estabelea o caso inicial.

L A labore o circuito de um contador s#ncrono que e!ecute a seqO'ncia mostrada

no diagrama abai!o. 0onsidere os casos no pertencentes ao diagrama, como

irrelevantes.

*

MICRO&ROCESSADORES

- que ) dentro de um computadorJ - que um microprocessadorJ - que um

microcomputadorJ - que um micro controladorJ

Co!pu3aor%

,s cinco principais sees de um computador so A entrada, mem"ria (aritmtica

e l"gica), controle e sa#da.

En3raa A consiste em todos os circuitos necessrios a introduzir

programas e dados no computador. m alguns computadores a seo de

entrada inclui um teclado de mquina de escrever que converte letras e

n.meros em cordes de dados binrios.

Me!"ria A armazena o programa e dos dados antes que comece a corrida

(processamento) no computador. la tambm pode armazenar solues

parciais durante uma corrida (processamento) no computador, de maneira

id'ntica a que usamos com uma mem"ria intermediria enquanto

resolvemos um problema.

Con3ro$e A este o centro de gravidade do computador, anlogo B parte

consciente da mente. , seo de controle comanda a operao de todas as

outras sees. 0omo o regente de uma orquestra, ela diz as outras sees

o que fazer e quando faz'&lo.

Ari3!,3ica e $"gica A esta a seo trituradora de n.meros da mquina.

la tambm pode tomar decises l"gicas com o controle dizendo o que

fazer e com a mem"ria alimentando&a co os dados, a unidade l"gica e

aritmtica (2Q,) e!trai as respostas aos problemas numricos e l"gicos.

Sa-a A esta passa as respostas e outros dados processados para o

mundo e!terior. , seo de sa#da inclui usualmente um identificador de

v#deo para permitir ao usurio ver os dados processados.

Microprocessaor A a seo de controle e a 2Q, muitas vezes so combinadas

fisicamente numa .nica unidade c)amada central de processamento (201 ou

012). ,lm disso, conveniente combinar as sees de entrada e de sa#da numa

.nica unidade c)amada de unidade de entrada&sa#da (RS ou PR-). %os

computadores primitivos a 012, a mem"ria e a unidade RS enc)iam uma sala

inteira.

0om o advento dos circuitos integrados, a 012, a mem"ria e a unidade RS

diminu#ram drasticamente. ,tualmente , 012 pode ser fabricado numa .nica

pastil)a de semicondutor c)amada microprocessador

m outras palavras, um microprocessador no nada mais do que um 012 em

uma pastil)a.

:a mesma forma, os circuitos de RS e a mem"ria podem ser fabricados em

pastil)as (Ec)ipsF). :esta maneira, os circuitos de computador que uma vez

enc)eram uma sala agora se a(ustam em algumas pastil)as.

+

MICROCOM&UTADOR

0omo o pr"prio nome indica, um microcomputador um pequeno computador.

<ais especificamente, um microcomputador um pequeno computador que usa

um microprocessador como sua 012.

- microcomputador t#pico tem tr's espcies de pastil)as$ microprocessador

(usualmente uma pastil)a), mem"ria (vrias pastil)as) e RS (uma ou mais

pastil)as).

Microco!pu3aor e u! s" c/ip$ como o nome indica, re.nem no mesmo c)ip

os diversos elementos de um microcomputador$

<icroprocessador, ?,<, ?-<, temporizadores, contadores, canal de

comunicao serial e portas de PR-.

Microcon3ro$aor% um microcomputador de um s" c)ip que pode ainda conter

elementos pra uso industria, tais como ,R: e :R,, 1S<, etc.

Es3ru3ura 5sica e u! sis3e!a e !icroprocessaor

2m microcomputador um sistema formado pro um microprocessador, uma

mem"ria e uma unidade de entradaRsa#da.

m resumo, um sistema digital com microprocessador uma estrutura )ardTare,

controlada por um softTare ou programa.

, funo bsica do microprocessador consiste em buscar instrues contidas na

mem"ria (escritas anteriormente) e e!ecut&las.

Buses de ligao

%a figura anterior podemos observar que todos os elementos do sistema se

encontram interligados atravs de canais (buses) por onde a informao circula,

10

".&ro7ro&

essador

8C9U:

"e23r.a

9ortas

I/O

,a-das

Entradas

P ROM RAM E/S

"e23r.a

P

Bus de

Endereos

Bus de

Dados

Bus de

Controle

na forma de sinais eltricos. , informao desloca&se no sentido das setas e em

alguns casos direcional.

-s principais buses de um sistema so

*uses de endereos A con(unto de tantas lin)as quantos os bits de

endereo que o sistema admita. %ele, o microprocessador emite uma

combinao binria pra selecionar alguns dos registros e!ternos situados

na mem"ria ou na unidade de entradaRsa#da.

*us de dados A tem tantas lin)as quantos os bits que apresenta a palavra

ou dado com que o sistema opera. ,travs deste canal, recebe&se no

microprocessador, o conte.do dos registros ou posies de mem"ria,

selecionados pelo *us de endereos, ou ento envia&se do

microprocessador, os dados que se dese(am armazenar. >ambm circulam

por este *us os dados que a unidade de entradaRsa#da emite ou recebe.

*us de controle A con(unto de lin)as que se utiliza para transporte os sinais

necessrios para a coordenao de todos os elementos do sistema,

sincronizao, ordens de leituraRescrita, seleo de mem"ria, unidade de

entradaRsa#da, etc.

Baixar o Softare de simulao A!acus

1odemos descrever de forma resumida o funcionamento de um sistema com

microprocessador, conforme visto na estrutura bsica representada na figura

anterior.

%uma parte da mem"ria, encontram&se escritas, na forma binria as instrues

que podem ser lidas e interpretadas pelo microprocessador e que determinam as

operaes que o sistema pode e!ecutar.

2ma vez posto em andamento o sistema, o microprocessador pode somente

dirigir&se a uma posio de mem"ria. 1ara ler o conte.do armazenado nessa

posio, o microprocessador envia uma combinao binria para a mem"ria,

atravs do *us de endereos. 1or meio de um sinal de controle, emitido tambm

pelo microprocessador, o conte.do da posio de mem"ria transfere&se para o

bus de dados e passa para o interior do microprocessador, ai interpretado ou

decodificado e posteriormente, a instruo e e!ecutada.

11

Vous aimerez peut-être aussi

- SO Perguntas e Respostas - Cap. 1Document4 pagesSO Perguntas e Respostas - Cap. 1André Campos RodovalhoPas encore d'évaluation

- 04 NuvemDocument102 pages04 NuvemWalbert Fernandes100% (1)

- Reparo Bga Microprocessador MT5561LVNTBDocument1 pageReparo Bga Microprocessador MT5561LVNTBstkzPas encore d'évaluation

- GuiadesimulacaoFlexSimv7 3v3 PDFDocument511 pagesGuiadesimulacaoFlexSimv7 3v3 PDFVictor Oliveira Miranda100% (1)

- Abnt NBR 1704 - Construcao Naval - AmarrasDocument12 pagesAbnt NBR 1704 - Construcao Naval - Amarrasrodrsilv100% (1)

- Ficha Técnica - Jeep RenegadeDocument22 pagesFicha Técnica - Jeep RenegadeHenrique RodriguezPas encore d'évaluation

- Fazer Teste: AS - Unidade I: Informações Do TesteDocument2 pagesFazer Teste: AS - Unidade I: Informações Do TesteRinaldo OliveiraPas encore d'évaluation

- Projeto de Sistemas Computacionais - Atividade Avaliativa - Semana 6 - Nota 10Document7 pagesProjeto de Sistemas Computacionais - Atividade Avaliativa - Semana 6 - Nota 10Denis MoralesPas encore d'évaluation

- Jefferson Dos SantosDocument100 pagesJefferson Dos SantosCompras VariedadesPas encore d'évaluation

- 256.08.721 - IOM Fan Coil 42B 60Hz AG C 02 22 ViewDocument32 pages256.08.721 - IOM Fan Coil 42B 60Hz AG C 02 22 ViewFlorencioMelloPas encore d'évaluation

- Omega 4.1 Injeção M2.8.1, Ar, Arrefecimento, Abs e Localização de Relés e FusíveisDocument11 pagesOmega 4.1 Injeção M2.8.1, Ar, Arrefecimento, Abs e Localização de Relés e FusíveisraposatropicalPas encore d'évaluation

- Avançado - InformáticaDocument93 pagesAvançado - InformáticaAnicely SabaraPas encore d'évaluation

- Gmail - Resumo Do Seu Atendimento Minha ClaroDocument2 pagesGmail - Resumo Do Seu Atendimento Minha Claromraimundaoliveira2023Pas encore d'évaluation

- Apostila de Mantenção de MicroDocument119 pagesApostila de Mantenção de MicroAbisson RodriguesPas encore d'évaluation

- PR-001-Insp - Receb.Equip. Materiais Elétricos ADocument10 pagesPR-001-Insp - Receb.Equip. Materiais Elétricos AJose RibeiroPas encore d'évaluation

- Manual Nobreak XNB 600 720 1200 1440 1800 Va 01-18 SiteDocument16 pagesManual Nobreak XNB 600 720 1200 1440 1800 Va 01-18 SiteJames Javé FerreiraPas encore d'évaluation

- Atividade 1 - Ped - Teoria e Prática Na Educação Infantil - 51/2024Document2 pagesAtividade 1 - Ped - Teoria e Prática Na Educação Infantil - 51/2024FRANCISCO ALMEIDAPas encore d'évaluation

- Projeto Logística 1222Document27 pagesProjeto Logística 1222Ghellem PiresPas encore d'évaluation

- Ae Mt7 Planif MP 21 22Document17 pagesAe Mt7 Planif MP 21 22Márcia Andreia dos Santos PradoPas encore d'évaluation

- Catalogo Vaporizadores Atmosfericos para GLPDocument2 pagesCatalogo Vaporizadores Atmosfericos para GLPFagner CargneluttiPas encore d'évaluation

- Componentes Básicos de Um ComputadorDocument14 pagesComponentes Básicos de Um ComputadorEliab LimaPas encore d'évaluation

- RH - Forças e FraquezasDocument1 pageRH - Forças e FraquezasIncaixe projetadosPas encore d'évaluation

- TP1 - Interrupção Simples Com Lâmpada de IncandescênciaDocument7 pagesTP1 - Interrupção Simples Com Lâmpada de IncandescênciaVítor FolgadoPas encore d'évaluation

- Teste Vazão Bicos InjetoresDocument63 pagesTeste Vazão Bicos InjetoresLuciano Mendes Dos Santos100% (1)

- desktopEbookInstagramSkills Edio03 JUL2020Document90 pagesdesktopEbookInstagramSkills Edio03 JUL2020André RoquePas encore d'évaluation

- Abisolo Anuario2021Document186 pagesAbisolo Anuario2021Salatyel SilvaPas encore d'évaluation

- Biografia PEDocument2 pagesBiografia PEaaPas encore d'évaluation

- 8.manual Computador InterativoDocument16 pages8.manual Computador InterativoCOTED Coordenadoria de Tecnologia EducacionalPas encore d'évaluation

- COMANDOS ELÉTRICOS SimbologiaDocument3 pagesCOMANDOS ELÉTRICOS SimbologiaDiego TrabalhosPas encore d'évaluation

- RT Informa N. 21 Outubro - Nota Tecnica Do Ministerio Do Trabalho Esclarece o Uso de Robos Colaborativos Frente A NR 12Document2 pagesRT Informa N. 21 Outubro - Nota Tecnica Do Ministerio Do Trabalho Esclarece o Uso de Robos Colaborativos Frente A NR 12Wander AndradePas encore d'évaluation