Académique Documents

Professionnel Documents

Culture Documents

Dispositivos Electronicos

Transféré par

miguel lazarte chavezTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Dispositivos Electronicos

Transféré par

miguel lazarte chavezDroits d'auteur :

Formats disponibles

Tema 0.

- Repaso de Teora de Circuitos

1 . - Magnit ude s e l c t ric as y c onc e pt os fundame nt ale s .

Tensin (v): Diferencia de potencial elctrico entre

dos puntos de un circuito. El punto desde donde se

comienza a medir se seala con un smbolo +. Se mide en

voltios (V).

Intensidad (i): Nmero de cargas elctricas que

circula por un elemento de circuito por unidad de tiempo.

La direccin positiva del flujo de cargas se indica con una

flecha. Se mide en amperios (A).

La tensin siempre se mide entre dos puntos y la

intensidad siempre fluye a travs de un elemento.

Dispositivo electrnico: Elemento con dos o ms terminales que establece una relacin

algebraica o diferencial entre la intensidad que circula por l y la tensin entre sus terminales.

Circuito elctrico: Conjunto de dispositivos interconectados entre s que establecen

unas determinadas relaciones entre las tensiones e intensidades elctricas que dependen tanto

de la naturaleza de los dispositivos como de la forma en que estn conectados.

1.1. Conceptos bsicos de circuitos

En un circuito se define:

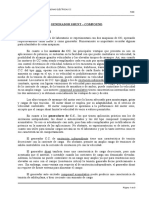

Conexin: Punto donde se unen dos terminales de elementos.

Nudo: Punto donde se unen ms

de dos terminales de elementos. Entre

dos nudos debe haber al menos un

elemento.

Rama: Conjunto de elementos

entre dos nudos.

Malla: Camino cerrado formado

por una o ms ramas que comienza y

termina en un mismo nudo.

v

i

Nudos: N1, N0 (2)

Ramas: E1-E2-E3, E4, E5-E6 (3)

Mallas: E1-E2-E3-E4, E1-E2-E3-E5-E6, E4-E5-E6 (3)

(Smbolo

de Tierra)

( Puerto )

E1

E2 E4 E6

E3 E5

vp

ip

ip

N1

N0

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 1

Tierra: Un nudo del circuito que se toma como referencia para medir todas las tensiones

del circuito. As, cuando se dice "la tensin en tal punto del circuito" se est refiriendo a la

diferencia de potencial entre dicho punto y el nudo de tierra.

Puerto: Par de terminales de un circuito tales que la intensidad que entra por uno de

ellos es igual a la que sale por el otro. En un circuito pueden existir puertos que tengan un

terminal comn; en este caso, la intensidad que circula por este terminal es igual a la suma de

las que circulan por los otros terminales de dichos puertos. Los puertos pueden ser de entrada

y/o salida.

1.2. Leyes de Kirchoff.

Gobiernan el funcionamiento de los

circuitos.

1 Ley (LKI): La Suma de las intensidades

que inciden en un nudo es nula o la suma de las

intensidades que entran en un nudo es igual a la

suma de las intensidades que salen de l.

2 Ley (LKV): La suma de las tensiones a

lo largo de una malla es nula o la tensin entre

dos puntos es la misma, independientemente del

camino que se utilice para calcularla.

1.3. Potencia Elctrica.

Todo elemento de circuito consume o aporta energa elctrica durante el funcionamiento

del circuito en que se inserta. La magnitud ms utilizada en la evaluacin del comportamiento

energtico de un elemento cualquiera es la energa consumida o aportada por unidad de

tiempo, es decir, la potencia. La potencia instantnea viene dada por la expresin:

P

i

= v i

Donde v es la tensin en los extremos del elemento e i la intensidad que circula por l.

La potencia media consumida en un intervalo de tiempo t viene dada por:

1

t

P = v () i () d

t

0

Si las magnitudes v e i son constantes a lo largo del tiempo se dice que la corriente

elctrica es continua, coincidiendo en este caso la potencia media y la potencia instantnea.

La potencia consumida o aportada por un circuito es igual a la suma de las potencias

consumidas o aportadas por sus elementos.

1 Ley: i2 + i3 - i1 = 0 i1 = i2 + i3

2 Ley: v1 + v2 - v3 = 0 v3 = v1 + v2

i1 i3

i2

v1

v2

v3

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 2

2 . - Ele me nt os bs ic os de c irc uit o.

Existen dos clasificaciones fundamentales:

Lineales: Las relaciones que establecen entre i y v estn dadas por ecuaciones

algebraicas o diferenciales lineales.

No lineales: Los que no cumplen lo anterior.

Pasivos: Almacenan o disipan energa elctrica ( P 0 )

Activos: Generan energa elctrica a partir de energa qumica (pilas), mecnica

(dinamos), o incluso elctrica (transistores). ( P < 0 ).

2.1. Elementos pasivos.

Se establece el convenio de tomar como

positiva la intensidad que entra por el terminal + de

la tensin.

Resistencia lineal u hmica.

Establece una relacin lineal entre i y v conocida como Ley de Ohm.

v = i * R

El valor de R es funcin de la temperatura

(aumenta al aumentar sta), aunque a efectos de

anlisis se considera constante. Su unidad de medida

es el ohmio ().

1 = 1 V / 1 A. [] = Kg m

2

A

-2

s

-3

Un conductor ideal es aquel cuya resistencia es 0. Por tanto, aplicando la ley de Ohm, la

tensin entre los extremos de un conductor ideal es siempre 0, es decir, no pueden existir

valores diferentes de tensin en un conductor ideal. Se considera que los terminales de

conexin de cualquier elemento se comportan como conductores ideales.

La magnitud inversa de la resistencia se denomina conductancia y se representa por la

letra g. La conductancia de un conductor ideal es infinita.

Condensador.

Establece una relacin diferencial lineal entre i y v dada por la siguiente expresin:

Smbolo de la resistencia

v

i

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 3

i = C * dv/ dt

La constante C se denomina capacidad y se

mide en Faradios (F). El valor de esta unidad es muy

alto, por lo que los condensadores reales suelen

medirse en F (10

-6

F), nF(10

-9

F) o pF (10

-12

F).

1 F = 1 C / 1 V. [F] = Kg

-1

m

-2

A s

4

Inductancia.

Establece una relacin diferencial entre i y v

dada por la siguiente expresin:

v = L * di/ dt

La constante L se denomina autoinduccin y se

mide en Henrios.

1 He nrio = 1 We be r / 1 A. [He nrio] = Kg m

2

s

-2

A

-2

2.2. Elementos activos.

Se establece el convenio de tomar como

positiva la intensidad que sale del terminal + de la

tensin

Fuentes independientes.

a) De tensin.

La tensin entre sus extremos es

independiente de la intensidad que circule por ella

y viene dada por la propia fuente.

b) De intensidad.

La intensidad que circula por ella es

independiente de la tensin entre sus extremos y

viene dada por la propia fuente.

i

v

v = cte.

i

v

i

Fuente independiente de tensin

Fuente independiente de intensidad

SIMBOLOS

Smbolo del condensador

Smbolo de la inductancia

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 4

Fuentes controladas.

a) De tensin controlada por tensin (FVCV).

La tensin entre sus extremos es independiente de la intensidad que circula por ella pero

es funcin de la tensin en otro elemento del circuito.

b) De tensin controlada por intensidad (FVCI).

La tensin entre sus extremos es independiente de la intensidad que circula por ella pero

es funcin de la intensidad a travs de otro elemento del circuito.

c) De intensidad controlada por tensin (FICV).

La intensidad que circula por ella es independiente de la tensin entre sus extremos pero

es funcin de la tensin en otro elemento del circuito.

d) De intensidad controlada por intensidad (FICI).

La intensidad que circula por ella es independiente de la tensin entre sus extremos pero

es funcin de la intensidad a travs de otro elemento del circuito.

2.3. Modelado de elementos de circuito no lineales.

Las caractersticas de los elementos de circuito mostrados hasta ahora son una

idealizacin de su comportamiento real. En la prctica, los elementos de circuito descritos no

presentan este comportamiento idealizado, sino que las relaciones que establecen entre las

magnitudes elctricas son mucho ms complejas, normalmente no lineales, y dependen de

otros factores, fundamentalmente de la temperatura.

v

vc

v = K vc

FVCV

v = rm ic

FVCI

ic

v

i = gm vc

FICV

i

vc

i = k ic

FICI

ic

i

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 5

Adems de esto, en un elemento de circuito real no se presenta un comportamiento

puramente resistivo ni capacitivo ni inductivo, sino que normalmente se da una mezcla de

todos estos comportamientos. As, por ejemplo, aunque en una resistencia real el

comportamiento que predomina claramente es el resistivo, tambin se dan, aunque en menor

grado, los comportamientos inductivo y capacitivo. Esto que significa que la ley de Ohm es

slo una aproximacin al comportamiento real de la resistencia, que puede dejar de ser vlida

en circunstancias concretas como por ejemplo cuando la frecuencia de la tensin aplicada en

sus extremos es muy elevada.

A pesar de esto, la gran ventaja que presentan estos modelos idealizados es que las

relaciones aritmticas que establecen son muy sencillas y por lo tanto fciles de utilizar para

resolver un problema, mientras que si se utilizasen expresiones ms de acuerdo con la

realidad, la mayor parte de los problemas seran irresolubles analticamente.

Una solucin intermedia a este problema

consiste en modelar los elementos reales mediante la

combinacin de elementos ideales. El modelo de un

determinado elemento puede variar segn las

condiciones en que se quiera analizar el circuito ( alta

frecuencia, baja potencia, etc.. ) o segn el grado de

aproximacin a la realidad que quiera obtenerse. Esto

permite la obtencin de resultados ms acordes con la

realidad manteniendo como base del anlisis los

elementos ideales. Un ejemplo de esto es el modelo

de alta frecuencia de una resistencia, que constara de

la resistencia ideal en serie con una inductancia ideal

y todo en paralelo con un condensador ideal.

Otro ejemplo claro de la necesidad de utilizar

modelos para los elementos reales lo constituyen las

fuentes de alimentacin, ya sean de tensin o de intensidad.

Las fuentes ideales, tal como han sido definidas son

imposibles de obtener en la realidad, ya que si existieran

podran construirse circuitos que violaran las leyes de

Kirchoff y, por tanto, las leyes de conservacin de la carga

y la energa, cosa que es imposible. Esto se mostrar en el

apartado "Circuitos imposibles" de los problemas resueltos

de este captulo. Esto no quiere decir que el modelo ideal

no sea til, sino que para representar el comportamiento de

una fuente real hay que realizar un modelo que incluya,

adems de la fuente ideal, otros elementos como

resistencias, condensadores o inductancias. El modelo ms

utilizado es el que supone que toda fuente real consta de

una fuente ideal y una resistencia denominada resistencia

interna.

Modelos de fuentes

independientes reales

Ri

Ri

Modelo para alta frecuencia de

una resistencia

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 6

El modelado es una tcnica esencial cuando se consideran dispositivos cuyo

comportamiento es claramente no lineal, como los basados en cristales semiconductores, que

son los ms importantes en la electrnica actual. La tcnica que se utiliza en este caso consiste

es dividir su funcionamiento en diferentes zonas y considerar que, en cada una de ellas, el

dispositivo puede ser modelado utilizando elementos ideales. Segn esto, al dispositivo se le

asocia un modelo diferente en cada zona de funcionamiento. Esto se ver ms adelante con el

diodo y los diferentes tipos de transistor.

3 . - Anlis is de c irc uit os . Anlis is de l punt o de ope rac in.

Consiste en dado un circuito del que se conoce el conexionado y sus elementos, calcular

todas sus tensiones e intensidades.

Para hacerlo existen varios mtodos. El ms genrico se basa en la utilizacin de las

leyes de Kirchoff y las ecuaciones de los elementos. Los pasos a seguir son los siguientes:

1.- Contabilizar el nmero de ramas (R) y el nmero de nudos (N).

2.- Las incgnitas son: En las ramas donde haya fuentes de intensidad, las tensiones de

dichas fuentes y en las ramas donde no haya ninguna fuente de intensidad, las intensidades

de dichas ramas.

3.- El nmero de ecuaciones necesarias para resolver el circuito es igual al nmero de

ramas (R) y se eligen de la forma siguiente:

4.- Se aplica la 1 Ley de Kirchoff a todos los nudos menos uno (N-1 ecuaciones)

5.- Se escogen R-(N-1) mallas de forma que estn englobadas todas las ramas y se

aplica la 2 Ley de Kirchoff.

6.- Se resuelve el sistema de ecuaciones resultante.

3.1. Mtodos alternativos de anlisis.

A veces no se requiere conocer todas las tensiones e intensidades de un circuito, sino

slo algunas de ellas. En este caso pueden aplicarse otros mtodos que simplifican el anlisis.

1.- Circuitos equivalentes.

Dados dos circuitos A y B, ambos con un puerto, se dice que son equivalentes con

respecto a dicho puerto si cuando se aplica la misma tensin en cada puerto, por ellos circula

la misma intensidad. Un ejemplo de esto lo constituye la asociacin de resistencias en paralelo

y en serie.

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 7

1.A.- Equivalente en Thvenin.

Visto desde un puerto, un circuito compuesto por

resistencias y fuentes (si son controladas no deben depender

de v ni de i del puerto) se comporta de forma anloga a una

nica fuente de tensin en serie con una nica resistencia,

cuyos valores vienen dados por:

- La tensin de la fuente V

T

es igual a la tensin que

existe en los extremos del puerto cuando no se conecta a l

ningn circuito externo.

- La R

T

es igual a la resistencia equivalente del circuito

desde los terminales del puerto obtenida mediante la

anulacin de todas las fuentes de tensin (sustituyndolas por

un conductor ideal) y de intensidad (eliminndolas

directamente) del circuito.

1.B.- Equivalente en Norton.

Visto desde un puerto, un circuito compuesto por

resistencias y fuentes (si son controladas no deben depender

de v ni de i del puerto) se comporta de forma anloga a una

nica fuente de intensidad en paralelo con una nica

resistencia, cuyos valores vienen dados por:

- La R

N

es igual a la R

T

.

- La intensidad de la fuente viene dada por:

I

N

= V

T

/ R

T

.

Equivalente de resistencias en paralelo Equivalente de resistencias en serie

1 1 1 1

= + +

R

eq

R

1

R

2

R

3

R

eq

R

1 R

2

R

3

R

eq

R

1

R

2

R

3

R

eq

= R

1

+ R

2

+ R

3

Equivalente en Thvenin

desde el puerto A-B

VT

RT

Circuito

A

B

A

B

Equivalente en Norton

desde el puerto A-B

IN RN

Circuito

A

B

A

B

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 8

2.- Principio de superposicin.

Un circuito compuesto de resistencias y fuentes independientes tiene un

comportamiento idntico a la suma de los comportamientos obtenidos por la accin de cada

fuente anulando el resto de ellas. ( Ejercicio resuelto B )

4 . - Anlis is de c irc uit os . Anlis is t rans it orios .

Cuando en un circuito se incluyen condensadores, inductancias o fuentes cuyo valor

depende del tiempo, los valores de tensiones e intensidades tambin dependen del tiempo.

Aqu slo se va a analizar un caso muy concreto de este problema, que es la carga y

descarga de condensadores.

Segn la Ley de Ohm y la expresin del condensador, se verifica:

v - v

c

d v

c

i = ; i = C

R d t

Igualando ambas expresiones se obtiene una ecuacin diferencial lineal:

d v

c

v

c

V

+ = 0

d t R C R C

La solucin de esta ecuacin es de la forma: v

c

= K e

-t

+ . Para calcular los

coeficientes y se deriva la expresin anterior y se sustituye en la ecuacin, obtenindose:

d v

c

K V

= K e

t

K e

t

+ e

t

+ = 0

d t R C R C R C

Esto debe cumplirse en todo instante t, por lo que se deduce:

K 1 V

K + = 0 = ; = 0 = V

R C R C R C R C

El valor de K se calcula de la condicin inicial: v

0

= v

c

( t = 0 ):

v

0

= K e

-0/RC

+ V = K + V K = v

0

- V

V

R

C v

c

i

c

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 9

v

c

= ( v

0

- V ) e

-t/RC

+ V

V - v

c

V - v

0

i

c

= i

c

= e

-t/RC

R R

* Casos particulares:

a) Carga del condensador.

Se considera que la tensin inicial es de 0 voltios, por lo que v

0

= 0 V y las expresiones

anteriores quedan:

v

c

= V ( 1 - e

-t/RC

)

V

i

c

= e

-t/RC

R

b) Descarga del condensador.

No existe fuente de tensin, lo que equivale a decir que vale 0 voltios ( V = 0 ) o que se

ha sustituido por un conductor ideal y la tensin inicial en el condensador es distinta de 0:

v

c

= v

0

e

-t/RC

v

0

i

c

= e

-t/RC

R

* Parmetros temporales de la carga y la descarga.

El producto de la resistencia por el condensador en un circuito de carga o descarga tiene

dimensin de tiempo, y se denomina constante de tiempo del circuito ( = RC ). En un proces

de carga o descarga se definen los siguientes parmetros:

Tiempo de subida ( t

r

).- En un condensador inicialmente descargado, es el tiempo

transcurrido desde que la tensin en sus extremos tiene un valor igual al 10 % del valor de la

tensin de la fuente hasta que alcanza el 90 % de dicho valor.

Tiempo de caida ( t

f

).- En un proceso de descarga de un condensador, se define como

el tiempo transcurrido desde que su tensin tiene un valor igual al 90 % de la tensin inicial

hasta que alcanza el 10 % de dicho valor.

Los retrasos que se dan en los circuitos digitales tienen su origen fundamentalmente en

fenmenos capacitivos equivalentes a la carga y descarga de condensadores, por lo que estos

parmetros son muy tiles para modelar dichos retrasos.

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 10

* Clculo de los tiempos de subida y cada.

a) En el proceso de carga:

v

c

= V ( - e

-t/

) .

En el 10 % del valor de V se cumple:

0,1 V = V ( - e

-t

1

/

) 0,1 = 1 - e

-t

1

/

e

-t

1

/

= 0,9

t

1

= ln 0,9 t

1

= - ln 0,9 0,1

En el 90 % del valor de V se cumple:

0,9 V = V ( - e

-t

2

/

) t

2

= - ln 0,1 2,3

t

r

= t

2

- t

1

= 2,3 - 0,1 t

r

= 2,2

Puede comprobarse que en t = 3 , la carga alcanza el 95 % del total y en t = 5 el 99 %.

b) En el proceso de descarga:

v

c

= v

0

e

-t/

90 % 0,9 v

0

= v

0

e

-t

1

/

e

-t

1

/

= 0,9 t

1

= - ln 0,9 0,1

10 % 0,1 v

0

= v

0

e

-t

2

/

t

2

= - ln 0,1 2,3

t

f

= t

2

- t

1

t

f

= 2,2 ; Se comprueba que t

f

= t

r

5 . - Eje rc ic ios re s ue lt os .

* Circuitos bsicos con resistencias.

1.- DIVISOR DE TENSION.

a) Se aplica la Ley de Ohm a R1 y R2 y la LKV.

v

o

= i R

2

; v

i

- v

o

= i R

1

b) Se despeja i en funcin de v

i

v

i

v

i

- i R

2

= i R

1

i =

R

1

+ R

2

R

2

R

1

i

v

i

v

o

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 11

c) Se calcula v

o

sustituyendo el valor de i:

R

2

v

o

= v

i

R

1

+ R

2

2.- DIVISOR DE INTENSIDAD

a) Ley de Ohm:

v v

i

1

= ; i

2

=

R

1

R

2

b) Despeje y sustitucin:

R

1

v = i

1

R

1

i

2

= i

1

R

2

c) LKI:

R

1

R

2

R

1

i = i

1

+ i

2

= i

1

( 1 + ) i

1

= i ; i

2

= i

R

2

R

1

+ R

2

R

1

+ R

2

* Circuitos imposibles

El hecho de contemplar modelos idealizados de los elementos de circuito, en concreto

de las fuentes de alimentacin, puede dar lugar a construcciones de circuitos imposibles, ya

que violan alguna de las leyes de Kirchoff. Las siguientes figuras muestran cuatro

construcciones de circuito imposibles.

Circuito 1:

R = 0 v

o

= 0 . Por LKV, V = v

o

V = 0

Cualquier valor de V distinto de 0 hace que no se

verifique la 2 Ley de Kirchoff, es, decir, hace que el circuito

sea imposible. Esto tambin puede verse de la forma

siguiente:

V

Si V 0 i = IMPOSIBLE.

0

Circuito 2:

Aplicando LKV, V

1

- V

2

= 0 para todo valor de

V

2

distinto de V

1

no se cumple esta ley, por lo que el

circuito es imposible.

R

2

R

1

i i

2

i

1

v

R = 0

i

v

o

V

V

2

V

1

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 12

Circuito 3:

Por LKI, i = I, pero por causa del circuito abierto, i = 0,

por lo que este circuito es imposible para todo valor de I

diferente de 0.

Otra forma de ver esto es que si I 0, entonces se dara

que v

o

= I R IMPOSIBLE.

Circuito 4:

Al no existir ningn nudo en la conexin

de I

1

con I

2

, por LKI, I

1

= I

2

para todo

valor de I

2

distinto de I

1

no se cumple esta ley,

por lo que el circuito es imposible.

* Anlisis de circuitos

A.- Mtodo general

A1.- Circuito con fuentes independientes.

0.- Homogeneidad dimensional.

Todos los valores de las resistencias y fuentes deben expresarse en unidades del Sistema

Internacional o derivadas de forma correcta para que puedan ser ignoradas al establecer las

ecuaciones. As, si la tensin se expresa en voltios y la intensidad en amperios, el valor de las

resistencias debe darse en ohmios, pero si las intensidades se expresan en miliamperios, la

resistencia habr que expresarla en kiloohmios para que los resultados sean correctos. Las

unidades que mejor se adaptan a la mayora de los circuitos son:

Tensin : voltios ( V )

Intensidad : miliamperios ( mA )

Resistencia : kiloohmios ( K )

R

i

v

o

I

I

2

I

1

V

A

R

1

R

3

R

2

V

B

N

0

N

1

I

1 0 K 1 6 K

1 2 K

3 V

2 V

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 13

1.- Nudos, ramas y mallas.

n ramas = 4 ( V

A

- R

1

, I, R

3

y R

2

- V

B

) son necesarias 4 ecuaciones

n nudos = 2 ( N

0

y N

1

) 1 ecuacin de nudos y 4 - 1 = 3 ecuaciones de mallas.

Hay que elegir las mallas de forma que incluyan a todas las ramas. Una posible

eleccion es:

M

1

( V

A

- I - R

1

)

M

2

( I - R

3

)

M

3

( R

3

- V

B

- R

2

)

2.- Incgnitas : i

1

, i

2

, i

3

, v

1

Tanto el sentido de las intensidades como la polaridad de las tensiones se eligen

arbitrariamente. Lo que vara de elegirlas de una forma u otra es el signo del resultado final.

3.- LKI al nudo N

1

:

i

1

+ 1 + i

2

- i

3

= 0 (1)

4.- LKV a las 3 mallas:

M

1

3 - v

1

- 10 i

1

= 0 (2)

M

2

v

1

+ 12 i

2

= 0 (3)

M

3

-12 i

2

- 2 - 16 i

3

= 0 (4)

5.- Solucin del sistema por cualquiera de los mtodos usuales.

i

1

- 0,280 mA

i

2

- 0,483 mA

i

3

0,237 mA

v

1

5,8 V

R

1

R

3

V

B

N

0

N

1

I V

A

v

1

i

1

R

2

i

2

i

3

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 14

A2.- Circuito con fuentes controladas.

1.- Nudos, ramas y mallas.

n ramas = 3 3 ecuaciones

n nudos = 2 1 ecuacin de nudos y 2 ecuaciones de mallas.

M

1

( V

A

- I - R

2

- R

1

)

M

2

( V

A

- V

B

- R

3

- R

1

)

2.- Incgnitas : i

B

, v

1

, i

1

En este caso, la intensidad por la rama VA - R1 es la que controla a la fuente I, por lo

que conviene tomarla como incgnita tal como est.

3.- LKI al nudo N

1

:

i

1

- i

B

- 50 i

B

= 0 (1)

4.- LKV a las dos mallas:

M

1

0,7 - v

1

- 50 i

B

+ 2 i

B

= 0 (2)

M

2

0,7 - 5 + 0,8 i

1

+ 2 i

B

= 0 (3)

R

1

R

3

V

B

N

0

N

1

I

V

A

R

2

2 K 0 , 8 K

5 V

1 K

0 . 7 V

i

B

5 0 i

B

R

1

R

3

N

0

N

1

I

V

A

R

2

V

B

i

B

i

1

v

1

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 15

5.- Solucin.

(1) i

1

= 51 i

B

; Sustituyendo en (3):

4,3

- 4,3 + 0,8 51 i

B

+ 2 i

B

= 0 i

B

= 0,1 mA ;

42,8

4,3

i

1

= 51 5,12 mA;

42,8

Sustituyendo en (2):

4,3

v

1

= 0,7 - 48 - 4,12 V

42,8

En resumen : v

1

= - 4,12 V ; i

1

= 5,12 mA ; i

B

= 0,1 mA

A3.- Circuito con fuentes controladas.

n nudos = 1

2 ecuaciones de mallas y ninguna de nudos.

n ramas = 2

No hay fuentes de intensidad incgnitas: i

B

, i

1

Ecuaciones:

M

1

( V

A

- V

B

- R

1

) 2 - 0,7 - 0,96 i

B

= 0 (1)

M

2

( V

D

- V

C

- R

2

) 5 i

B

- 37,5 + 7,25 i

1

= 0 (2)

Solucin:

1,3

(1) i

B

= 1,35 mA

0,96

- 5i

B

+ 37,5

(2) i

1

= 4,24 mA

7,25

R

1

N

0

R

2

0 , 9 6 K 7 , 2 5

0 . 7 V

i

B

5 i

B

V

A

V

B

V

C

V

D

3 7 , 5 V 2 V

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 16

B.- Mtodo de Superposicin.

Se considera el mismo circuito que en el ejercicio A1, pero ahora no se pide que se

resuelva completamente, sino slo que se calcule la tensin v

1

y la intensidad i

1

. Esto puede

hacerse mediante el mtodo de superposicin siguiendo los pasos que se describen a

continuacin:

1.- Se anulan las fuentes I y V

B

, quedando el siguiente circuito:

Se reduce el circuito de forma que no queden afectadas las magnitudes que se

quieren medir. En este caso se quiere medir v

1

por lo que las conexiones entre las que se

mide no pueden desaparecer con la reduccin. Esto significa que pueden reducirse las

resistencias R

2

y R

3

, pero no la R

1

, ya que desaparecera una de las conexiones donde se mide

v

1

. El circuito equivalente queda:

1 1 1

= + R

eq

= 6,86 K

R

eq

R

2

R

3

6,86

v

1

= 3 (divisor de tensin)

10 + 6,86

v

1

= 1,22 V (1)

3

i1 = 0,18 mA (2)

10 + 6,86

2.- Se anulan V

A

y V

B

, quedando:

6,86

i

1

= -1 (divisor de intensidad) i

1

= - 0,41 mA (3)

10 + 6,86

v

1

= - i

1

R

1

v

1

= 4,07 V (4)

i

1

1 0 K

6 , 8 6

K

v

1

1 mA

R

1

R

3

V

B

V

A

v

1

i

1

R

2

R

1

V

A

v

1

i

1

R

e q

R

1

R

3

I

v

1

i

1

R

2

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 17

3.- Se anulan V

A

e I, quedando:

1 1 1

= + R

eq

= 5,45 K

R

eq

R

1

R

3

5,45

v

1

= 2 v

1

= 0,51 V (5)

16 + 5,45

- v

1

i

1

= i

1

= - 0,05 mA (6)

R

1

4.- Se calcula el resultado final sumando los resultados parciales.

v

1

= (1) + (4) + (5) v

1

= 5,8 V

i

1

= (2) + (3) + (6) i

1

= - 0,28 mA

Puede comprobarse que estos resultados coinciden con los del ejercicio A.1.

C.- Mtodo de clculo de equivalentes.

En gran cantidad de circuitos, el clculo del equivalente en Thvenin o Norton

simplifica en gran medida el anlisis. Esto tambin suele utilizarse cuando se quiere calcular

una nica tensin o intensidad en el circuito.

C.1.- Clculo del equivalente en Thvenin.

Se debe calcular el valor de la tensin v

c

(t) en el circuito de la figura considerando que

en t = 0, v

c

(t = 0 ) = v

0

= 0 V.

1 6 K

R

e q

v

1

2 V

R

1

R

3

V

B

v

1

i

1

R

2

5 0 F

v

C

2 , 5 V

5 mA

1 0 K

1 K 0 , 2 5 K

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 18

1.- Conviene calcular el equivalente en Thvenin del siguiente circuito, que es el

circuito original en el que se ha eliminado el condensador, quedando un puerto de salida cuya

tensin es precisamente la que se quiere calcular, v

c

. De esta forma, el circuito puede

reducirse al que ya se ha visto anterormente, que contiene nicamente una fuente de tensin,

una resistencia y un condensador, pudindose aplicar directamente las expresiones halladas

para dicho circuito.

a) Clculo de la R

T

.

Se anulan todas las fuentes y se calcula la resistencia equivalente.

1 1 1

= + R

eq

= 0,2 K

R

T

1 0,25

b) Clculo de la V

T

.

Se calcular mediante el mtodo de Superposicin.

b1.- Se anula la fuente de tensin:

El circuito resultante es un divisor de intensidad, de lo que se deduce:

V

T

R

T

5 mA

1 0 K

1 K 0 , 2 5 K

2 , 5 V

V

T

1 0 K

1 K 0 , 2 5 K 0 , 2 5 K 1 K

R

T

5 mA

1 0 K

1 K 0 , 2 5 K V

T

i

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 19

1

i = 5 = 4 mA ; V

T

= 0,25 i V

T

= 1 V (1)

1 + 0,25

b2.- Se anula la fuente de intensidad:

Teniendo en cuenta que la resistencia de 10 K tiene un terminal desconectado, lo que

equivale a que no existe, el circuito es un divisor de tensin, por lo que el valor de V

T

puede

determinarse directamente a partir de su expresin.

0,25

V

T

= - 2,5 = - 0,5 V (2)

1 + 0,25

b3.- El resultado final es V

T

= (1) + (2) = 1 - 0,5 = 0,5 V

El circuito que resulta una vez se ha sustituido por el equivalente en Thvenin es:

RC = 0,2 K 50 F = 0,2 10

3

50 10

-6

F = 10 10

-3

s RC = 10 ms ;

v

0

= 0 V es un proceso de carga

v

c

(t) = 0,5 ( 1 - e

-t/10

) ( t expresado en ms )

C2.- Equivalente en Norton.

Se quiere calcular el valor de la tensin v

o

en el circuito de la figura.

2 , 5 V

0 , 2 5 K V

T

1 K

1 0 K

0 , 5 V

0 , 2 K

5 0 F

v

c

3 V

1 K

0 , 5 K

v

o

1 , 5 K

2 K v

R

2 v

R

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 20

1.- Se calcula el equivalente en Thvenin de una parte del circuito:

1

V

T

= 3 (divisor de tensin)

1 + 0,5

V

T

= 2 V

0,5 1 1

R

T

= = K

0,5 + 1 3

2.- A partir del equivalente en Thvenin se obtiene el equivalente en Norton y se

sustituye en el circuito.

1 V

T

R

N

= R

T

= K ; I

N

= = 6 mA

3 R

T

El circuito es un divisor de intensidad, por lo que se tiene:

1/3 6 + 2 v

R

I = 6 + 2 v

R

; i = I = ;

1/3 + 1,5 + 2 11,5

6 + 4 i 6

Por otra parte: v

R

= 2 i ( Ley de Ohm ) i = = = 0,8 mA ;

11,5 7,5

v

o

= i ( 1,5 + 2 ) v

o

= 2,8 V

3 V

1 K

0 , 5 K

v

o

1 K

0 , 5 K

R

T

2 K 1/3 K

v

o

1,5 K

v

R

2 v

R

6 mA 6 mA

2 v

R

v

R

1,5 K

v

o

1/3 K

2 K

I

i

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 21

5 . - Eje rc ic ios propue s t os .

1.- Encontrar la expresin general del condensador e inductancia equivalentes a la

asociacin de n elementos en serie y en paralelo.

1 1

Solucin: Condensador paralelo: C

eq

=

i=1

n

C

i

; Condensador serie: =

i=1

n

;

C

eq

C

i

1 1

Inductancia paralelo: =

i=1

n

; Inductancia serie: L

eq

=

i=1

n

L

i

L

eq

L

i

2.- Resolver los siguientes circuitos.

Datos: V

1

= 7 V; V

2

= 6 V; I

1

= 5 mA; R

1

= 1 K; R

2

= 2 K; R

3

= 3 K;

R

4

= 2 K; R

5

= 1 K.

Soluciones (en valor absoluto ): (a) i(V

1

) = 2,44 mA; i(V

2

) = 1,9 mA; i(R

2

) = 2,28 mA;

i(R

3

) = 0,15 mA; i(R

4

) = 2,05 mA. (b) i(V

1

) = 6,57 mA; i(R

1

) = 7 mA; i(R

2

) = 0,43 mA;

i(R

3

) = 0,43 mA; i(R

4

) = 4,57 mA; V(I

1

) = 9,14 V.

3.- Calcula el valor de R

X

en el circuito de la figura sabiendo que I = 0,65 mA. ( Los

datos restantes son los mismos del problema anterior.

Solucin: R

X

= 2,5 K

4. a) Considera tres fuentes reales de tensin, todas con la misma V = 5 V y diferentes

resistencias internas: R

i1

= 1 ; R

i2

= 500 ; R

i3

= 100 K. Calcula la tensin en los

extremos de la fuente cuando se conecta una resistencia R

L

de 500 . Analiza los resultados y

explica qu valores de Ri son los que ms se aproximan al comportamiento ideal.

R4 I1 V1

R1

R2

R3

V2

V1

R5

R4 R2

R3 R1

(a) (b)

R

1

R

2

R

3

V

2

R

X

I

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 22

b) El mismo ejercicio anterior pero considerando ahora una fuente real de intensidad de

5 mA, los mismos valores de resistencia interna y se trata de calcular la intensidad que aporta

la fuente a la resistencia R

L

de 500 .

Soluciones: a) v

1

= 4,99 V ; v

2

= 2,5 V ; v

3

= 0,0249 V ; i

1

= 0,00998 mA ;

i

2

= 2,5 mA ; i

3

= 4,975 mA

5.- Calcula la V

I

del circuito (a) y la I

v

del circuito (b).

Solucin: V

I

= 4,48 V; I

v

= 3,61 mA

6.- En el circuito de la figura, en t = 0 se cierra el interruptor S

1

y comienza la carga del

condensador ( v

c

(t=0) = 0 V). En t = 4 ms. se vuelve a abrir S

1

. Calcular el valor de v

c

(t).

Solucin: Para 0 t 4 ms. v

c

(t) = 3 ( 1 - e

-t/12

). Para t 4 ms. v

c

(t) = 0,85 e

-t/30

.

(t expresado en ms.)

5 V

0,7 V

10 V

3 V

10iB

0,7 V

10K

(a) (b)

15 mA

5iB

IV

iB

2,4K

2,4K

1,6K

6K 2,5K

2,5K

VI

5 V

6 K

1 0 mA

v

c

1 0 F

3 K

2 K

4 K

S1

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 0

Departamento de Electrnica Pag 23

Tema 1.-Conceptos bsicos de circuitos

digitales.

1 . - Se ale s e l c t ric as

Seal elctrica: Representacin de la variacin de una magnitud elctrica (tensin o

intensidad) frente al tiempo. La magnitud ms utilizada es la tensin. Este concepto es

interesante en tanto en cuanto es susceptible de representar una informacin.

Desde este punto de vista puede establecerse la siguiente clasificacin:

Seal analgica: Todos los valores de tensin comprendidos entre un mximo y un

mnimo son significativos a la hora de interpretar la informacin que representa la seal.

Seal digital binaria: Slo son significativos los valores de tensin comprendidos en

dos intervalos de tensin diferentes. A todos los valores dentro de cada uno de los intervalos

se les asocia un mismo valor lgico, normalmente uno y cero.

Segn lo anterior, en un mismo intervalo de tiempo, una seal analgica porta una

mayor cantidad de informacin que una seal digital, pero esta informacin es mucho menos

inmune a fenmenos externos como el ruido que la seal digital.

2 . - Familias lgic as .

Puerta lgica: Circuito electrnico con uno o varios puertos de entrada y uno o varios

puertos de salida que proporciona seales digitales en sus salidas cuando a sus entradas se

aplican seales digitales, de forma que cada salida representa una funcin booleana de las

seales de entrada.

Normalmente, los circuitos digitales toman la energa de una fuente independiente de

tensin continua, denominada fuente de alimentacin, de forma que el terminal de masa del

V

t

Seal analgica

V

t

Seal digital binaria

V(1)

V(0)

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 1

circuito coincide con el polo negativo de dicha fuente y es un terminal comn a todos los

puertos de entrada y salida.

Existen distintas posibilidades de implementar una misma funcin lgica, es decir,

diferentes circuitos pueden realizar la misma funcin pero normalmente tendrn

caractersticas elctricas diferentes.

Un conjunto de circuitos, cada uno de los cuales implementa una funcin booleana

diferente, pertenece a una misma FAMILIA LOGICA si tienen en comn las siguientes

caractersticas:

- Tipo de elemento activo (transistores) con que est realizado.

- Estructura de circuito caracterstica. Una parte del circuito, normalmente la de entrada

o la de salida tiene una topologa comn.

- Tecnologa utilizada en la fabricacin.

Una familia siempre debe incluir una puerta NAND o una puerta NOR.

3 . - Carac t e rizac in de familias lgic as .

Para poder comparar las prestaciones de los diferentes circuitos que realizan una misma

funcin lgica o lo que es lo mismo, para poder comparar las diferentes familias lgicas, hay

que establecer una serie de criterios que permitan realizar dicha comparacin. Los ms

importantes son:

- Caracterstica de transferencia.

- Caractersticas de entrada-salida.

- Inmunidad al rudo.

- Consumo de energa.

- Velocidad de operacin.

- Flexibilidad lgica.

- Capacidad de integracin.

a) Caracterstica de transferencia.

Dado un circuito con un puerto de entrada

y otro de salida, la caracterstica de transferencia

consiste en representar grficamente la tensin

de salida Vo en funcin de la tensin de entrada

Vi cuando sta toma todos los valores de su

rango de variacin. Dicho rango de variacin

coincide normalmente con el valor de tensin de

la fuente de alimentacin.

V

o

V

in

Vcc VIH VIL

VOL

VOH

Vcc

Vin Vo

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 2

Para comparar la caracterstica de transferencia de dos familias lgicas se elige como

representante de cada una al circuito que realice la inversin lgica. Una caracterstica tpica

de un inversor se representa en la figura de la pgina anterior. A partir de esta caracterstica se

deducen los rangos de tensin correspondientes a los valores de 0 y 1 lgicos de la forma

siguiente:

Se trazan las dos lneas tangentes a la curva cuya pendiente sea -1. Las tensiones de

entrada y salida correspondientes a esos puntos reciben la denominacin siguiente:

V

OL

: Mxima tensin de salida correspondiente a 0 lgico que proporciona la puerta.

V

OH

: Mnima tensin de salida correspondiente a 1 lgico que proporciona la puerta.

V

IL

: Mxima tensin correspondiente a 0 lgico que acepta la puerta en su entrada.

V

IH

: Mnima tensin correspondiente a 1 lgico que acepta la puerta en su entrada.

Por tanto, el rango de tensiones correspondiente a 1 lgio es viene dado por V

cc

- V

IH

,

siendo V

cc

la tensin de la fuente de alimentacin, y el rango de tensiones correspondiente al

0 lgico es V

IL

- 0 = V

IL

.

Se define el ancho de transicin (TW) como V

IH

- V

IL

y la excursin lgica (LS) como

V

OH

- V

OL

.

Para que una familia lgica tenga un funcionamiento lgico correcto, sus niveles no

deben degenerarse cuando se conectan varias puertas en cascada (la entrada de una conectada

a la salida de la anterior), para ello, debe cumplirse:

V

IH

< V

OH

V

IL

> V

OL

De esta forma la tensin de salida de una puerta siempre estar dentro de los rangos de 0

o 1 lgicos de la familia.

b) Caractersticas de entrada-salida.

El nmero de entradas que puede tener

una puerta lgica no es indefinido, est

limitado por un nmero mximo. A ese

nmero se le denomina FAN-IN de la puerta.

En algunos circuitos, a la salida de una

puerta deben conectarse varias entradas de

otras puertas. El nmero de entradas que

pueden conectarse a una misma salida est

limitado por un nmero mximo denominado

1

2

3

n

.

.

.

FAN-IN = n

1

2

m

.

.

.

FAN-OUT = m

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 3

FAN-OUT. El fan-out debe calcularse siempre conectando puertas pertenecientes a una

misma familia.

c) Inmunidad al ruido.

Una seal elctrica de ruido consiste en una perturbacin aleatoria, cuyo origen puede

ser diverso, que puede mezclarse con una seal elctrica portadora de informacin, pudiendo

provocar la prdida de parte de esa informacin.

Las seales digitales son mucho ms inmunes al ruido que las analgicas, no obstante,

tambin pueden verse afectadas por este

factor.

Para evaluar la inmunidad al ruido de

una familia lgica se definen los mrgenes de

ruido, de la forma siguiente:

1.- Margen de ruido de 1 lgico o alto.

NM

H

= V

OH

- V

IH

2.- Margen de ruido de 0 lgico o bajo.

NM

L

= V

IL

- V

OL

De lo que se vi en el apartado de caracterstica de transferencia se deduce que ambos

deben ser positivos. El valor ms pequeo de los dos es el que determina la inmunidad al

ruido de una familia lgica. Es evidente que cuanto ms alto sea dicho valor, mejor ser la

inmunidad al ruido de dicha familia.

d) Consumo de energa.

Se evala calculando la potencia elctrica consumida por una puerta en dos situaciones:

- Cuando no se producen cambios en las entradas (potencia esttica).

- Cuando las entradas cambian a una frecuencia determinada (potencia dinmica a esa

frecuencia).

Cuanto ms consume un circuito, mayor es el calor generado por el mismo, de forma

que si no es disipado convenientemente, la temperatura puede elevarse por encima del lmite

tolerado y provocar un funcionamiento incorrecto del circuito.

NMH

TW LS

NML

V V

SALIDA ENTRADA

VOL

VOH

VIL

VIH

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 4

Es fundamental tener en cuenta este factor a la hora de disear un sistema integrado en

un chip y tambin en el diseo de sistemas porttiles que requieran gran autonoma.

e) Velocidad de operacin.

En las seales digitales, las transiciones entre los valores de 0 y 1 lgicos no se

producen de forma instantnea, sino que transcurre un determinado intervalo de tiempo que

depende del circuito que genere dichas seales. De la misma forma, la variacin de la seal de

salida siempre se produce despus de que haya cambiado la seal de entrada. Estos tiempos

influyen de forma trascendental en la frecuencia mxima a que puede operar una determinada

puerta lgica. Se miden de la forma siguiente:

Tiempo de subida (t

r

): Tiempo transcurrido entre el paso de la seal de salida de una

puerta por el valor de tensin correspondiente al 10% de la diferencia entre los valores alto y

bajo de tensin de la seal y el paso de la misma seal por el 90% de dicha diferencia.

Tiempo de bajada (t

f

): Tiempo transcurrido entre el paso de la seal de salida de una

puerta por el valor de tensin correspondiente al 90% de la diferencia entre los valores alto y

bajo de tensin de la seal y el paso de la misma seal por el 10% de dicha diferencia.

Tiempo de propagacin alto-bajo (t

PHL

): Tiempo transcurrido entre el cambio de

estado de la seal de entrada y el de la de salida cuando sta pasa del estado alto al bajo,

medido al paso de las seales por el 50% de la diferencia entre sus valores alto y bajo de

tensin.

Tiempo de propagacin bajo-alto (t

PLH

): Tiempo transcurrido entre el cambio de

estado de la seal de entrada y el de la de salida cuando sta pasa del estado bajo al alto,

medido al paso de las seales por el 50% de la diferencia entre sus valores alto y bajo de

tensin.

Se define el tiempo medio de propagacin (t

PD

) como el valor medio entre el t

PHL

y el

t

PLH

.

100%.................................................................

90%................................................................

10%...................................................................

0%.................................................................

t

r

t

f

0%.................................................................

50%................................................................

100%.................................................................

t

PHL

t

PLH

SEAL DE

ENTRADA

SEAL DE

SALIDA

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 5

Estos tiempos determinan la frecuencia mxima a la que puede operar un sistema

digital realizado con una familia lgica dada. Cuanto ms pequeos sean mayor podr ser

dicha frecuencia de operacin.

En las puertas lgicas, el consumo y los tiempos de retardo estn relacionados, de forma

que si se modifican algunos parmetros para disminuir el consumo se suele producir un

aumento en los valores de dichos tiempos y viceversa. Por ello, un factor de calidad

importante a la hora de caracterizar una familia lgica es el producto consumo * t

PD

.

f) Flexibilidad lgica.

Existen dos conceptos diferentes de flexibilidad lgica en la bibliografa.

El primer concepto se refiere a que una familia lgica es ms flexible cuanto ms

puertas que implementen funciones booleanas diferentes contenga.

El segundo concepto est basado en

que existen familias lgicas que son capaces

de realizar algunas funciones booleanas sin

necesidad de utilizar puertas, simplemente

uniendo las salidas de otras puertas. Estas

funciones son denominadas funciones

cableadas y son, normalmente, la AND y la

OR (WIRED-AND y WIRED-OR). Segn

esto, una familia presenta flexibilidad lgica

si puede realizar funciones cableadas.

g) Capacidad de integracin.

Depende fundamentalmente de dos factores:

- El AREA ocupada por cada puerta, que depende a su vez del tipo y del nmero de

transistores utilizados para realizarla. Cuanto menor sea este rea mayor ser la capacidad de

integracin a gran escala.

- El CONSUMO de potencia. En un circuito integrado se realizan muchas puertas en un

espacio reducido. El consumo total del chip es igual al consumo de cada puerta por el nmero

de puertas. Si el consumo de cada puerta es elevado se generar mucho calor en el chip

debido al efecto Joule, de forma que si esta calor no es disipado convenientemente se

producir un aumento de temperatura que puede provocar un funcionamiento anmalo de los

circuitos. Esta es la cuasa por la que para que una familia pueda ser integrada a gran escala

debe tener un consumo de potencia reducido.

Segn el nmero de puertas que puedan integrarse, pueden distinguirse los siguientes

niveles o escalas de integracin:

WIRED-AND

WIRED-OR

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 6

- SSI (Pequa escala): menor de 10 puertas

- MSI (Media escala): entre 10 y 100 puertas.

- LSI (Alta escala): entre 100 y 10.000 puertas.

- VLSI (Muy alta escala): a partir de 10.000 puertas.

La familia lgic a ide al.

Las caractersticas que debera tener una familia lgica ideal son las siguientes:

V

OH

= V

cc

; V

OL

= 0

V

IH

= V

IL

= V

cc

/ 2

LS = V

cc

; TW = 0

FAN-IN ; FAN-OUT

NM

H

= NM

L

= V

cc

/ 2

Consumo de potencia esttica = 0

Consumo de potencia dinmica 0

t

r

0 ; t

f

0 ; t

PHL

0 ; t

PLH

0

Cue s t ione s

1.- Explica razonadamente por qu una seal digital presenta mayor inmunidad al ruido

que un seal analgica.

2.- Por qu un CD de audio digital debe girar a mayor velocidad que un disco

analgico de vinilo (LP) para oir el mismo pasaje musical ?

3.- Por qu toda familia lgica debe incluir al menos una puerta NAND o una puerta

NOR ?

4.- Qu error puede ocurrir en una familia lgica cuyo V

IH

> V

OH

?

5.- Se desea implementar la siguiente funcin booleana:

Vcc

V

in Vcc

V

o

Caracterstica de transferencia ideal

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 7

f (a,b,c,d) = a b c + a b c + a d + c d (+ indica funcin OR)

Se dispone de una familia lgica con FAN-IN = 2 y de otra con FAN-IN = 4. Disea el

circuito ptimo para ambas familias e indica las principales diferencias entre ambos diseos.

6.- Se desea implemetar las siguientes funciones lgicas:

f

1

(a,b,c) = a b + a c ; f

2

(a,b,c,d) = a b + c d ; f

3

(a,b,d) = a b + b d

Se dispone de una familia lgica con FAN-OUT = 1 y de otra con FAN-OUT = 5.

Disea el circuito ptimo para ambas familias e indica las principales diferencias entre ambos

diseos.

7.- Las caractersticas de 2 familias lgicas son:

a) FA : V

OH

= 4,7 V ; V

OL

= 0,4 V ; V

IH

= 1,7 V ; V

IL

= 0,9 V

Potencia esttica = 2 mW ; Potencia dinmica = 0,01 mW/MHz ; t

PD

= 8 ns.

a) FB : V

OH

= 4,2 V ; V

OL

= 0,3 V ; V

IH

= 2,7 V ; V

IL

= 1,8 V

Potencia esttica = 0 mW ; Potencia dinmica = 0,05 mW/MHz ; t

PD

= 1 ns.

Cul ser la ms apropiada para disear un sistema digital que controle procesos

industriales ?

Y para un sistema digital de adquisicin de datos porttil que funcione a 20 MHz ? y

a 100 MHz ?

Y para un sistema de procesamiento paralelo de muy alta potencia de clculo ?

8.- De las dos caractersticas de transferencia que se muestran en la figura, indica cul

presenta mayor inmunidad al ruido y por qu.

Vo

3,5V

0,5V

2V 2,5V

Carac t e rs t ic a

A

Vi

Vo

5V

0,5V

1V 1,5V

Carac t e rs t ic a

B

Vi

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 8

9.- Las dos grficas adjuntas representan las seales de entrada y salida de inversores de

2 familias lgicas diferentes. Calcula grficamente los tiempos de subida, bajada y

propagacin de cada uno de los inversores. Si el consumo total del inversor A es de 3 mW y

el del inversor B 12 mW, indica qu familia ser ptima en cuanto al producto consumo * t

PD

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 1

Departamento de Electrnica Pag 9

Tema 2.- Semiconductores. El diodo de

unin.

1 . - Es t ruc t ura c ris t alina y c onduc t ividad.

Un cristal est formado por un conjunto de tomos muy prximos entre s dispuestos

espacialmente de forma ordeanada de acuerdo con un determinado patrn geomtrico.

La gran proximidad entre los tomos del cristal hace que los electrones de su ltima

capa sufran la interaccin de los tomos vecinos. El nivel energtico de cada uno de estos

electrones puede estar situado en la "banda de valencia" o en la "banda de conduccin" del

cristal. Un electrn que ocupe un nivel dentro de la banda de valencia est ligado a un tomo

del cristal y no puede moverse libremente por l mientras que si el nivel ocupado pertenece a

la banda de conduccin, el electrn puede moverse libremente por todo el cristal, pudiendo

formar parte de una corriente elctrica.

Entre la banda de valencia y la de conduccin existe una "banda prohibida", cuyos

niveles no pueden ser ocupados por ningn electrn del cristal. Segn la magnitud de esta

banda, los cristales pueden clasificarse en aislantes, conductores y semiconductores.

Aislantes.

La magnitud de la banda prohibida es muy grande ( 6 eV ), de forma que todos los

electrones del cristal se encuentran en la banda de valencia incluso a altas temperaturas por lo

que, al no existir portadores de carga libres, la conductividad elctrica del cristal es nula.

Un ejemplo es el diamante.

Conductores.

No existe banda prohibida, estando solapadas las bandas de valencia y conduccin. Esto

hace que siempre haya electrones en la banda de conduccin, por lo que su conductividad es

muy elevada. Esta conductividad disminuye lentamente al aumentar la temperatura, por efecto

de las vibraciones de los tomos de la red cristalina.

Un ejemplo son todos los metales.

Semiconductores.

La magnitud de la banda prohibida es pequea ( 1 eV ), de forma que a bajas

temperaturas son aislantes, pero conforme aumenta la temperatura algunos electrones van

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 1

alcanzando niveles de energa dentro de la banda de conduccin, aumentando la

conductividad. Otra forma de aumentar la conductividad es aadiendo impurezas que

habiliten niveles de energa dentro de la banda prohibida.

El germanio y el silicio son semiconductores.

2 . - Se mic onduc t ore s int rns e c os y e xt rns e c os .

En un semiconductor como el silicio

(Si), que tiene 4 electrones en su ltima

capa, los tomos estn unidos por enlace

covalente formando una red cristalina

tetradrica. A temperaturas cercanas al cero

absoluto (-273

o

C) todos los electrones

ocupan sus enlaces y el cristal se comporta

como un perfecto aislante, pero a

temperatura ambiente (25

o

C) y ms

elevadas, algunos electrones (e

_

) adquieren

energa y se "escapan" de su enlace. El

enlace desocupado se denomina "hueco"

(h

+

) y tambin contribuye a la

conductividad del cristal comportndose

como un portador de carga positiva.

Si se aplica un campo elctrico externo al cristal, los electrones libres se mueven en

direccin opuesta al campo, formando una corriente elctrica y los electrones de valencia van

saltando hacia los huecos, de forma que es como si stos se moviesen en la misma direccin

del campo, formando una corriente de cargas positivas que se suma a la anterior. En

EG 6 eV

EG 1 eV

Banda de

Conduccin

Banda de

Valencia

Banda de

Conduccin

Banda de

Valencia

Banda

Prohibida

electrones

libres

huecos

(a) (b) (c)

Estructura de bandas de energa de: (a) un aislante, (b) un semiconductor, (c) un conductor

Si Si

Si Si Si

Si Si

e

_

Generacin de un par electrn-hueco

por efecto de la temperatura

energa

Si

h

+

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 2

definitiva, los semiconductores poseen dos

portadores de carga "libres", los electrones

(negativa) y los huecos (positiva).

Semiconductores intrnsecos.

Son los cristales semiconductores

puros. En ellos, el nmero de huecos es

igual al nmero de electrones y es funcin

de la temperatura del cristal.

La conductividad a temperatura

ambiente no suele ser muy alta.

Semiconductores extrnsecos.

Son cristales semiconductores a los que se han aadido impurezas, es decir, otro tipo de

tomos que ocupan nudos en la red critalina. La concentracin de estas impurezas en el cristal

es muy pequea ( como mucho es de un tomo de impureza por cada 10

12

tomos de

semiconductor ) pero su efecto en el aumento de la conductividad es muy grande.

Se consideran dos tipos de impurezas:

Donadoras: Tienen 5 electrones en su ltima capa ( P, As y Sb ).

Aceptoras: Tienen 3 electrones en su ltima capa ( B, Ga e In ).

Segn esto, hay dos tipos de semiconductores extrnsecos, los dopados con impurezas

donadoras o tipo N y los dopados con impurezas aceptoras o tipo P.

Semiconductores tipo N.

El electrn que sobra en la ltima capa necesita muy poca energa para abandonar el

tomo al que pertenece y convertirse en un electrn libre, de forma que a temperatura

ambiente, todos los electrones de los tomos de impurezas estn libres, aumentando

enormemente la conductividad del cristal.

El nmero de electrones libres es mucho mayor que el nmero de huecos, por lo que la

corriente elctrica en estos cristales es debida mayoritariamente a los electrones.

Semiconductores tipo P.

Las impurezas slo tienen 3 electrones en su ltima capa, de forma que dejan un enlace

sin llenar. Cualquien electrn de un tomo de silicio vecino necesita muy poca energa para

Movimiento de huecos bajo un campo elctrico

E

(Movimiento aparente del hueco)

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 3

dejar su enlace y ocupar el que tiene libre la impureza, originando un hueco. A temperatura

ambiente, todos los enlaces de las impurezas estn llenos, existiendo un gran nmero de

huecos que hace que la conductividad del cristal aumente en gran magnitud.

El nmero de huecos es mucho mayor que el nmero de electrones libres, por lo que la

corriente elctrica en estos cristales es debida mayoritariamente a los huecos.

3 . - Corrie nt e e l c t ric a e n un s e mic onduc t or.

En un semiconductor, la corriente elctrica puede ser de dos tipos, de arrastre y de

difusin.

Corriente de arrastre.

Es la que se da en los conductores y est originada por la presencia de un campo

elctrico externo que hace que tanto los electrones como los huecos se muevan

ordenadamente con velocidad proporcional a la intensidad del campo ( Ley de Ohm ).

Corriente de difusin.

Es tpica de los semiconductores y se produce cuando los portadores ( electrones o

huecos ) no estn distribuidos de forma homognea en el cristal, ocasionando un

desplazamiento de cargas que tiende a equilibrar dicha distribucin, es decir, tanto los huecos

como electrones tienden a desplazarse desde donde son ms numerosos hacia donde son

menos numerosos.

4 . - La unin P-N.

El diodo de unin P-N es el dispositivo semiconductor ms elemental. Consiste en el

dopado de una barra de cristal semiconductor en una parte con impurezas donadoras (tipo N)

y en la otra con impurezas aceptoras (tipo P). De esta forma, en la parte P existe mucha mayor

concentracin de huecos que de electrones libres y en la parte N ocurre lo contrario.

La conductividad del diodo es

diferente segn sea el sentido en que se

aplique un campo elctrico externo. Existen

dos posibilidades de aplicacin de este

campo: polarizacin inversa y

polarizacin directa.

Polarizacin inversa.

Consiste en aplicar a la parte N del

diodo una tensin ms positiva que a la

parte P. De esta forma, el campo elctrico

ID

+

VD

h

+

e

_

Zona P Zona N

Estructura fsica de un diodo y

smbolo de circuito

P N

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 4

estar dirigido de la parte N a la parte P y los huecos tendern a circular en ese sentido

mientras que los electrones tendern a circular en sentido contrario. Esto significa que

circularan huecos de la parte N (donde son muy minoritarios) a la parte P (donde son

mayoritarios), por lo que esta corriente se ve contrarrestada por una corriente de difusin que

tiende a llevar a los huecos de donde son mayoritarios (parte P) hacia donde son minoritarios

(parte N). Por consiguiente, la corriente global de huecos es prcticamente nula. Algo

totalmente anlogo ocurre con la corriente de electrones, la corriente de arrastre va en sentido

contrario a la de difusin, contrarrestndose ambas y produciendo una corriente total

prcticamente nula.

La corriente total es la suma de la de huecos ms la de electrones y se denomina

corriente inversa de saturacin ( I

s

). En la prctica, el valor de esta corriente es muy pequeo

(del orden de nA en el Silicio) y depende de la temperatura de forma que aumenta al aumentar

sta.

Polarizacin directa.

Consiste en aplicar a la parte P del diodo una tensin ms positiva que a la parte N. De

esta forma, el campo elctrico estar dirigido de la parte P a la parte N. Esto significa que

circularan huecos de la parte P (donde son mayoritarios) a la parte N (donde son

minoritarios) por lo que esta corriente tiene el mismo sentido que la corriente de difusin. De

esta forma, la corriente total de huecos es muy alta. Un proceso anlogo ocurre para la

corriente de electrones. La corriente total es la suma de la de huecos y la de electrones y toma

un valor elevado a partir de un determinado valor de tensin (tensin umbral, V

) que

depende del tipo de semiconductor (en el Silicio es aproximadamente de 0,7 V y en el

Germanio de 0,2 V).

Puede considerarse que el diodo es el dispositivo binario ms elemental, ya que permite

el paso de corriente en un sentido y lo rechaza en sentido contrario.

5 . - Curva c arac t e rs t ic a y mode los de c irc uit o de l diodo.

La curva caracterstica de un

dispositivo de dos terminales es la

representacin grfica de la intensidad que

circula por l frente a la tensin que existe

entre sus extremos.

Si esta expresin es una lnea recta, el

dispositivo es lineal y en caso contrario no

lineal.

El diodo es un dispositivo no lineal,

siendo su curva caracterstica la

representada en la figura. En polarizacin

inversa, la intensidad que circula por el

ID

VD

iD = Is (e

VD/VT

- 1)

(VT = kT/q ; k = cte. de Boltzmann; T =

temperatura en

o

K; q = carga del electrn)

Curva caracterstica del diodo

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 5

diodo es prcticamente nula y en polarizacin directa la intensidad es una funcin exponencial

de la tensin.

Este modelo no es adecuado para el anlisis manual de circuitos ya que al ser no lineal,

la resolucin de las ecuaciones se hace muy compleja, por lo que en la prctica se utilizan

modelos aproximados.

Modelo ideal.

El diodo se comporta como un

circuito abierto en polarizacin inversa y

como un cortocircuito en polarizacin

directa.

Modelo con tensin umbral.

El diodo se comporta como un

circuito abierto en polarizacin inversa y

como una fuente de tensin igual a la

umbral en polarizacin directa.

Modelo linealizado general.

El diodo se comporta como un

circuito abierto en polarizacin inversa y

como una fuente de tensin igual a la

umbral en serie con una resistencia Rd en

polarizacin directa.

6 . - El diodo Ze ne r.

El diodo Zener es un tipo especial de

diodo que se caracteriza porque conduce en

zona inversa a partir de una tensin

negativa V

Z

. Esto significa que el diodo

Zener tiene tres zonas de funcionamiento.

La zona de polarizacin directa tiene las

mismas caractersticas que la del diodo

bsico, mientras que en polarizacin

inversa se diferencian dos zonas, una en la

que el diodo no conduce intensidad y otra

en la que circula intensidad ( en sentido

Polarizacin inversa (V

D

< 0) : i

D

-I

s

Polarizacin directa (V

D

>> V

T

) : i

D

I

s

e

VD/VT

Modelo ideal:

vD 0 iD = 0

iD 0 vD = 0

Modelo con V:

vD V iD = 0

iD 0 vD = V

Modelo linealizado:

vD V iD = 0

vD V

iD = (VD - V) / RD

vD

iD

vD

iD

V

V vD

iD

1/RD

iD

vD

Curva caracterstica del diodo Zener

VZ

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 6

contrario a como circula en conduccin directa ) y la tensin tiene un valor menor o igual a

V

Z

.

El modelo del diodo Zener se forma a partir de cualquiera de los modelos del diodo

bsico aadiendo una nueva zona de operacin, la de conduccin inversa. La expresin en

polarizacin directa permanece sin cambios, pero en la zona inversa hay que introducir una

modificacin en la condicin, que queda: V

Z

V

D

0 para el modelo ideal y V

Z

V

D

V

para los otros modelos. La expresin general para la zona de conduccin inversa es:

I

D

= (V

D

- V

) / R

Z

V

D

V

Z

, siendo R

Z

el inverso de la pendiente de la caracterstica en

dicha zona.

El modelo ms utilizado del diodo Zener es el que supone que las resistencias RD y RZ

tienen un valor nulo, quedando:

i

D

0 v

D

= V

V

Z

v

D

V

i

D

= 0

i

D

0 v

D

= V

Z

7 . - Ot ros t ipos de diodos .

a) Diodos emisores de luz ( LED ).

Estn fabricados con un compuesto semiconductor, el Arseniuro de Galio ( AsGa ) y se

caracterizan porque emiten fotones de luz visible o infrarroja cuando conducen en

polarizacin directa. En polarizacin inversa se comportan como un diodo bsico, aunque se

diferencian en que la tensin umbral V

es aproximadamente igual a 1,6 voltios. La intensidad

de la radiacin luminosa es proporcional a la intensidad de corriente que circula por el diodo.

En ciertas condiciones, la luz emitida puede ser monocromtica y coherente ( LASER ),

conocindose en este caso como LASER de estado slido.

b) Fotodiodos.

Cuando se ilumina una unin P-N polarizada inversamente se produce un aumento de la

corriente inversa que es proporcional a la intensidad de luz aplicada. Este fenmeno se da

porque los fotones de luz generan nuevos pares electrn-hueco en las dos zonas, de forma

que los portadores minoritarios ( h

+

en la N y e

-

en la P ) pueden atravesar la unin por la

accin del potencial inverso, contribuyendo a un aumento apreciable de la corriente inversa.

Este hecho es el que se aprovecha en la fabricacin de fotodiodos, cuya estructura est

formada por un diodo en cuyo encapsulado se ha practicado una abertura sobre la zona de la

unin por la se permite que la luz incida sobre ella. La banda de luz ms utilizada para activar

al fotodiodo es la del infrarrojo.

Smbolo del diodo Zener

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 7

c) Diodos Schottky.

Estos diodos estn formados por la unin de un metal, normalmente aluminio, y un

cristal semiconductor de tipo N cuyo dopado ( bastante dbil ) hace que el comportamiento de

la unin sea de tipo rectificador, es decir, similar al de una unin P-N en la que el aluminio

tiene un comportamiento anlogo al de la zona P. Cuando el dopado del cristal es fuerte, se

dice que la unin es de tipo hmico ya que su comportamiento se asemeja al de un elemento

resistivo. Este ltimo tipo de unin es la que se utiliza para conectar los terminales metlicos

de los dispositivos semiconductores .

Las principales diferencias con los diodos P-N son las siguientes:

La corriente directa es producida por el paso de electrones del silicio tipo N al metal,

donde stos son mayoritarios, por lo que no se produce difusin de portadores

minoritarios, ya que el metal slo tiene un tipo de portadores ( los electrones ).

En polarizacin inversa, los electrones no pueden pasar del aluminio al silicio N

debido a la existencia de una barrera de potencial de contacto que lo impide.

Los tiempos de conmutacin de la zona de conduccin a la de no conduccin son

ms pequeos.

La tensin umbral est comprendida entre 0,3 V y 0,4 V.

8 . - Eje rc ic ios Re s ue lt os .

A.- Ejercicios de clculo del punto de trabajo.

El mtodo a seguir es el siguiente:

1.- Teniendo en cuenta que cada diodo bsico puede estar en dos estados diferentes y

cada diodo Zener en tres, se calcula el nmero total de estados en que puede estar el circuito,

que es: n estados = 2

(n diodos bsicos)

3

(n diodos Zener)

2.- Se va resolviendo cada configuracin hasta encontrar la correcta, que es nica y es

la que cumple las leyes de Kirchoff y las condiciones del diodo.

Smbolo del diodo LED Smbolo del fotodiodo Smbolo del diodo Schottky

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 8

A1.- Calcular v

D

e i

D

en el circuito de la figura considerando el modelo ideal del diodo.

a) Se calcula el equivalente en Thvenin en ambos lados del circuito

El circuito equivalente queda como sigue:

b) Se supone que el diodo est en conduccin ( D ON ), es decir, se debe verificar:

v

D

= 0 ; i

D

0

6 K

2 K

0,8 K

1,6 K

vD

iD

+

1 mA

3 V

6 K

2 K

0,8 K

1,6 K

1 mA

3 V

2

V

T1

= 3 = 0,75 V

2 + 6

2 6

R

T1

= + 0,8 = 2,3 K

2 + 6

V

T2

= 1,6 V

R

T2

= 1,6 K

2,3 K

1,6 K

vD

iD

+

1,6 V

0,75 V

E.T.S.I. Informtica Dispositivos Electrnicos. Tema 2

Departamento de Electrnica Pag 9

El circuito queda como sigue:

i

D

= - 0,218 mA < 0 ; pero la condicin era que i

D

0, luego, al no cumplirse, este

estado no puede darse, es INCORRECTO.

c) Se supone que el diodo no conduce ( D OFF ), es decir, se debe verificar: