Académique Documents

Professionnel Documents

Culture Documents

Dell Inspiron n4030 - Wistron Dj1 Calpella Uma 10212-Sb - Rev SB

Transféré par

Renato AraujoTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Dell Inspiron n4030 - Wistron Dj1 Calpella Uma 10212-Sb - Rev SB

Transféré par

Renato AraujoDroits d'auteur :

Formats disponibles

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Cover Page

A3

1 90 Monday, April 26, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Cover Page

A3

1 90 Monday, April 26, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Cover Page

A3

1 90 Monday, April 26, 2010

<Core Design>

Intel PCH

2010-04-23

REV : X01

DJ1 Calpella UMA Schematics Document

Arrandale

DY : Nopop Component

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA

X01

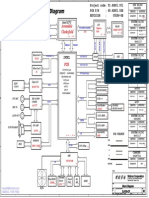

Block Diagram

2 90 Monday, April 19, 2010

<Core Design>

A3

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA

X01

Block Diagram

2 90 Monday, April 19, 2010

<Core Design>

A3

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA

X01

Block Diagram

2 90 Monday, April 19, 2010

<Core Design>

A3

Thermal

KBC

Int.

KB

INPUTS

SYSTEM DC/DC

+PWR_SRC

OUTPUTS

26

LPC Bus

TPS51611

256kB

+CPU_GFX_CORE

Flash ROM

Intel CPU

DDRIII

800/1066

Slot 0

DDRIII 800/1066 Channel A

Slot 1

8,9,10,11,12,13,14

19

18

DJ1 UMA Block Diagram

+0.75V_DDR_VTT

+3.3V_RTC_LDO

ISL62882

INPUTS

+VCC_CORE

OUTPUTS

SYSTEM DC/DC

RT8207GQW

+V_DDR_REF

OUTPUTS

CPU DC/DC

+PWR_SRC

+1.5V_SUS

INPUTS

RT8205BGQW

+PWR_SRC

+5V_ALW

OUTPUTS

+3.3V_ALW

TPS51218

OUTPUTS

SYSTEM DC/DC

INPUTS

+PWR_SRC

INPUTS

SYSTEM DC/DC

+1.5V_RUN

OUTPUTS

BQ24745

INPUTS

MAXIM CHARGER

+PWR_SRC

+PBATT

+5V_ALW2

+DC_IN

Bluetooth

73

USB 2.0 x 1

76

PCIE

63

54

CAMERA

Right Side:

USB x 2

USB 2.0 x 1

USB 2.0 x 2

USB 2.0

CRT

LVDS(Dual Channel)

LCD

Arrandale

RGB CRT

Intel

59 59

S

A

T

A

ODD

14 USB 2.0/1.1 ports

PCH

S

A

T

A

High Definition Audio

SATA ports (6)

LPC I/F

ACPI 1.1

HDD

PCI/PCI BRIDGE

32

CardReader

Realtek

RTS5138

SD/MMC/MS/

MS Pro/xD

USB2.0

Azalia

CODEC

AZALIA

2CH SPEAKER

30

HP1

Internal Analog MIC

55

NPCE781BA0DX

NUVOTON

SPI

39

PCIE ports (8)

39,40

INPUTS

SYSTEM DC/DC

+5V_RUN

OUTPUTS

26

+5V_ALW

APL5930

+3.3V_ALW

+3.3V_RUN +3.3V_ALW

+1.8V_RUN

USB 2.0 x 2

L6: Bottom

L5 GND

+PWR_SRC

Fan

DDRIII 800/1066 Channel B

DDRIII

800/1066

Clock Generator

54

7

37

SLG8SP585

62

25 68

20,21,22,23,24,25,26,27,28

68

Touch

PAD

PCB LAYER

L3: Signal

L4: Signal

L2: VCC

L1: Top

Project code : 91.4EK01.001

PCB P/N : 48.4EK19.0SB

Revision : 10212-SB

92HD79B1

EMC2102

DMIx4

71

58

S

P

I

4MB

Flash ROM

62

+1.5V_SUS

SYSTEM DC/DC

Switches

INPUTS OUTPUTS

+1.05V_VTT

+15V_ALW

10/100 NIC

PCIE x 1

ATHEROS

RJ45

CONN

I

/

O

B

o

a

r

d

C

o

n

n

e

c

t

o

r

Left Side:

USB x 1

AR8152/AR8151

PCIE x 1

47,48

49

46

50

53

51

42

MIC IN

802.11a/b/g

Mini-Card

FDIx4x2(UMA)

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Power Block Diagram

A3

3 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Power Block Diagram

A3

3 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Power Block Diagram

A3

3 90 Friday, April 16, 2010

<Core Design>

Charger

BQ24745

+PBATT

Adapter

Battery

TPS51125

+5V_ALW2

Regulator LDO Switch

+5V_ALW

+3.3V_RTC_LDO

AO4468

+5V_RUN

G547F2P81U-GP

+5V_USB1

+3.3V_ALW

ISL62882

+VCC_CORE

TPS51218

+PWR_SRC TPS51116

+0.75V_DDR_VTT +V_DDR_REF +1.5V_SUS

Power Shape

AO4407A

+15V_ALW

+1.05V_VTT

APL5930

+1.8V_RUN

AO4468

+1.5V_RUN

G547F2P81U-GP

+5V_USB2

AO3403

+3.3V_LAN

AO4468

+3.3V_RUN

RTS5159

+3.3V_RUN_CARD

SI3456DDV

+LCDVDD

2000mA 2000mA 6330mA

10330mA 82mA

2000mA 300mA

6661mA

300mA 1761mA

11145mA

48000mA 24800mA

1000mA

3500mA

16825mA

TPS51611

+CPU_GFX_CORE

22000mA

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

SMBUS Block Diagram

A2

4 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

SMBUS Block Diagram

A2

4 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

SMBUS Block Diagram

A2

4 90 Friday, April 16, 2010

<Core Design>

LDDC_CLK

LDDC_DATA

+3.3V_RUN

TPDATA

TPCLK

+5V_RUN

TouchPad Conn.

TPDATA

TPCLK PSCLK1

PSDAT1

LCD CONN

PCH SMBus Block Diagram

PCH

SMBCLK

SMBDATA

GPIO62/SDA2

GPIO61/SCL2

KBC

CLK_SMB

Thermal

SCL

SDA

+3.3V_RUN

SRN2K2J-1-GP

+3.3V_ALW

SRN2K2J-1-GP

+3.3V_RUN

DMN66D0LDW-7-GP

DAT_SMB

KBC_SCL1

KBC_SDA1

Minicard

WLAN

SMB_DATA

SMB_CLK

SCL1

SDA1

BAT_SCL

BAT_SDA

SMBus address:D2

SMBus Address:A0

SMBus Address:A4

DIMM 1

SCL

SDA

+KBC_PWR

DIMM 2

SCL

SDA

SMBus address:16

PCH_SMB_CLK

PCH_SMB_DATA

PCH_SMBCLK

PCH_SMBDATA

PBAT_SMBCLK1

PBAT_SMBDAT1

KBC SMBus Block Diagram

Battery Conn.

PCH_SMBCLK

PCH_SMBDATA

Clock

Generator

SCLK

SDATA

PCH_SMBCLK

PCH_SMBDATA

BQ24745

SCL

SDA

TPDATA

TPCLK

+3.3V_RUN

DMN66D0LDW-7-GP

THERM_SCL

THERM_SDA

SMBus address:7A

PCH_SMBDATA

PCH_SMBCLK

SMBus address:12

+3.3V_RUN

+3.3V_RUN

DMN66D0LDW-7-GP

+3.3V_RUN

SRN2K2J-1-GP

+5V_CRT_RUN

SRN2K2J-1-GP

CRT CONN

DDC_CLK_CON

DDC_DATA_CON

GMCH_DDCCLK

GMCH_DDCDATA

SRN10KJ-5-GP

SRN4K7J-8-GP

SRN4K7J-8-GP

SRN2K2J-1-GP

NPCE781BA0DX

SRN100J-3-GP

XDP

SML0CLK

SML0DATA

SML0_CLK

SML0_DATA

18

19

7

76

23

SRN4K7J-8-GP

+3.3V_ALW

23

PCH

SML1CLK/GPIO58

SML1DATA/GPIO75

L_DDC_CLK

L_DDC_DATA

CRT_DDC_CLK

CRT_DDC_DATA

+3.3V_ALW

SRN2K2J-1-GP

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA

X01

Thermal/Audio Block Diagram

Custom

5 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA

X01

Thermal/Audio Block Diagram

Custom

5 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA

X01

Thermal/Audio Block Diagram

Custom

5 90 Friday, April 16, 2010

<Core Design>

Thermal Block Diagram

Thermal

EMC2102

DP1

DN1

SC470P50V3JN-2GP

DP2

DN2

DP3

DN3

Audio Block Diagram

Codec

ALC269Q_VB5

HP

OUT

MIC

IN

SPEAKER

HP0_PORT_A_L

HP0_PORT_A_R

VREFOUT_A_OR_F

SPKR_PORT_D_L-

SPKR_PORT_D_R+

EMC2102_DP3

EMC2102_DN3

MMBT3904-3-GP

HP1_PORT_B_L

HP1_PORT_B_R

Analog

MIC

PORTC_L

PORTC_R

VREFOUT_C

SC470P50V3JN-2GP

Put under CPU.

EMC2102_DP1

EMC2102_DN1

MMBT3904-3-GP

SC470P50V3JN-2GP

Place near CPU

and PCH.

MMBT3904-3-GP

System Sensor(UMA only)

EMC2102_DP1

EMC2102_DN1

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Table of Content

A3

6 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Table of Content

A3

6 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Table of Content

A3

6 90 Friday, April 16, 2010

<Core Design>

SPKR

Name Schematics Notes

HAD_DOCK_EN#

/GPIO[33]

Low (0):

High (1) :

HDA_SDO Weak internal pull-down. Do not pull high.

HDA_SYNC

CFG[0]

CFG[7]

Calpella Schematic Checklist Rev.0_7

INIT3_3V# Weak internal pull-down. Do not pull high.

GNT3#/

GPIO55

Default Mode:

Low (0) = Top Block Swap Mode

GNT0#,

GNT1#/GPIO51

Weak internal pull-down. Do not pull high.

Weak internal pull-down. Do not pull high.

Weak internal pull-up. Do not pull low.

Processor Strapping PCH Strapping

Default (SPI):

GNT2#/

GPIO53

Default - Internal pull-up.

Low (0)

GPIO33 Default:

Disable ME in Manufacturing Mode:

SPI_MOSI

CFG[4] Disabled - No Physical Display Port attached to

Embedded DisplayPort.

CFG[3]

Internal weak Pull-down.

Connect to Vcc3_3 with

8.2-k- 10-k weak pull-up resistor.

Enable iTPM:

Disable iTPM:

NV_ALE Enable Danbury:

Disable Danbury:

Pin Name

USB Table PCIE Routing

LANE3 LAN

NC_CLE Weak internal pull-up. Do not pull low.

Strap Description Configuration (Default value for each bit is

1 unless specified otherwise)

1: Embedded

DisplayPort

Presence

Calpella Schematic Checklist Rev.0_7

0: Enabled - An external Display Port device is

connected to the Embedded Display Port.

PCI-Express Static

Lane Reversal

1:

0:

Normal Operation.

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

Default

Value

PCI-Express

Configuration

Select

1:

0:

Single PCI-Express Graphics

Bifurcation enabled

Reserved -

Temporarily used

for early

Clarksfield

samples.

Clarksfield (only for early samples pre-ES1) -

Connect to GND with 3.01K Ohm/5% resistor

Note: Only temporary for early CFD samples

(rPGA/BGA) [For details please refer to the WW33

MoW and sighting report].

For a common motherboard design (for AUB and CFD),

the pull-down resistor should be used. Does not

impact AUB functionality.

1

1

1

0

GPIO15

GPIO8

Reboot option at power-up

Default Mode:

No Reboot Mode with TCO Disabled:

Internal pull-up.

(Connect to ground with 4.7-k weak

pull-down resistor).

INTVRMEN High (1) = Integrated VRM is enabled

Low (0) = Integrated VRM is disabled

Left both GNT0# and GNT1# floating. No pull up

required.

Boot from PCI: Connect GNT1# to ground with 1-k

pull-down resistor. Leave GNT0# Floating.

Boot from LPC: Connect both GNT0# and GNT1# to ground with

1-k pull-down resistor.

= Configures DMI for ESI compatible operation (for servers

only. Not for mobile/desktops).

Do not pull low.

Connect to ground with 1-k

pull-down resistor.

Connect to Vcc3_3 with 8.2-k weak pull- up resistor.

Left floating, no pull-down required.

Connect to Vcc3_3 with 8.2-k weak pull-up

resistor.

Connect to ground with 4.7-k weak pull-down

resistor.

Flash Descriptor Security will be overridden.

Flash Descriptor Security will be in effect.

GPIO27 Default = Do not connect (floating)

High(1) = Enables the internal VccVRM to have a clean supply for

analog rails. No need to use on-board filter circuit.

Low (0) = Disables the VccVRM. Need to use on-board filter

circuits for analog rails.

LANE2 MiniCard WLAN

13 X

X

12 X

WLAN (I/O Board)

USB0 (I/O Board)

10

0

11

USB3

Pair

4

USB

5

2

3

1

Device

X 6

7

8

9

X

BLUETOOTH

USB2

CARD READER

X

CAMERA

X

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

FSC

CK_PWRGD

CLK_XTAL_OUT CLK_XTAL_IN

CPU_STOP#

CLK_CPU_BCLK1

CLK_CPU_BCLK1#

CLK_IN_DMI

CLK_IN_DMI#

CLK_PCIE_SATA1

CLK_PCIE_SATA1#

CLK_MCH_DREFCLK1

CLK_MCH_DREFCLK1#

CLK_XTAL_IN

CLK_XTAL_OUT

CK_PWRGD

CPU_STOP#

FSC

PCH_SMBCLK

PCH_SMBDATA

+3.3V_RUN

+3.3V_RUN_SL585 +1.05V_VTT

+1.05V_RUN_SL585_IO

+1.05V_VTT

+3.3V_RUN_SL585

+3.3V_RUN

+3.3V_RUN_SL585 +1.05V_RUN_SL585_IO

CLKIN_DMI# 23

CLKIN_DMI 23

CLK_CPU_BCLK 23

CLK_CPU_BCLK# 23

CLK_PCIE_SATA 23

CLK_PCIE_SATA# 23

DREFCLK# 23

DREFCLK 23

CLK_PCH_14M 23

PCH_SMBDATA 18,19,23,76

PCH_SMBCLK 18,19,23,76

VR_CLKEN# 47

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Clock Generator SLG8SP585

7 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Clock Generator SLG8SP585

7 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

Clock Generator SLG8SP585

7 90 Thursday, April 22, 2010

<Core Design>

FSC 0 1

133MHz

100MHz

(Default)

SPEED

SSID = CLOCK

1

2

C715

SC12P50V2JN-3GP

C715

SC12P50V2JN-3GP

1 2

R701

2K2R2J-2-GP

R701

2K2R2J-2-GP

1 2

X701

X-14D31818M-37GP

82.30005.901

X701

X-14D31818M-37GP

82.30005.901

1

2

EC701

SC4D7P50V2CN-1GP

DY

EC701

SC4D7P50V2CN-1GP

DY

V

D

D

_

D

O

T

1

V

S

S

_

D

O

T

2

DOT_96

3

DOT_96#

4

V

D

D

_

2

7

5

27MHZ

6

27MHZ_SS

7

V

S

S

_

2

7

8

V

S

S

_

S

A

T

A

9

SRC_1/SATA

10

SRC_1/SATA#

11

V

S

S

_

S

R

C

1

2

SRC_2

13

SRC_2#

14

V

D

D

_

S

R

C

_

I

O

1

5

CPU_STOP#

16

V

D

D

_

S

R

C

1

7

V

D

D

_

C

P

U

_

I

O

1

8

CPU_1#

19

CPU_1

20

V

S

S

_

C

P

U

2

1

CPU_0#

22

CPU_0

23

V

D

D

_

C

P

U

2

4

CKPWRGD/PD#

25

V

S

S

_

R

E

F

2

6

XTAL_OUT

27

XTAL_IN

28

V

D

D

_

R

E

F

2

9

REF_0/CPU_SEL

30

SDA

31

SCL

32

G

N

D

3

3

U701

SLG8SP585VTR-GP

U701

SLG8SP585VTR-GP

1

2

C701

S

C

1

U

1

0

V

2

K

X

-

1

G

P

DY

C701

S

C

1

U

1

0

V

2

K

X

-

1

G

P

DY

1

2 3

4

R

N

0R4P2R-PAD

RN702

R

N

0R4P2R-PAD

RN702

1

2 3

4

R

N

0R4P2R-PAD

RN703

R

N

0R4P2R-PAD

RN703

1

2 3

4

R

N

0R4P2R-PAD

RN704

R

N

0R4P2R-PAD

RN704

1

2

C703

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

C703

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

1

2

C707

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

C707

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

1

2

R705

10KR2J-3-GP

R705

10KR2J-3-GP

1

2

C702

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

DY

C702

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

DY

1

2

C711

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

C711

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

1 2 R709

0R0603-PAD-1-GP

R709

0R0603-PAD-1-GP

G

S

D

...

.

.

Q701

2N7002E-1-GP

...

.

.

Q701

2N7002E-1-GP

1

2

C705

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

C705

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

1

2

R704

4K7R2J-2-GP

DY

R704

4K7R2J-2-GP

DY

1 2 R708

0R0603-PAD-1-GP

R708

0R0603-PAD-1-GP

1

2

R707

10KR2J-3-GP

R707

10KR2J-3-GP

1

2

C704

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

C704

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

1

2

C709

S

C

1

U

1

0

V

2

K

X

-

1

G

P

DY

C709

S

C

1

U

1

0

V

2

K

X

-

1

G

P

DY

1

2 3

4

R

N

0R4P2R-PAD

RN701

R

N

0R4P2R-PAD

RN701

1

2

C708

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

C708

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

1

2

C710

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

C710

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

1

2

C712

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

C712

S

C

D

1

U

1

6

V

2

Z

Y

-

2

G

P

1 2

R703

33R2J-2-GP

R703

33R2J-2-GP

1

2

C714

SC12P50V2JN-3GP

C714

SC12P50V2JN-3GP

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

EXP_RBIAS

PEG_IRCOMP_R

DMI_PTX_CRXN0 22

DMI_CTX_PRXN0 22

DMI_PTX_CRXN1 22

DMI_PTX_CRXN2 22

DMI_PTX_CRXN3 22

DMI_PTX_CRXP0 22

DMI_PTX_CRXP1 22

DMI_PTX_CRXP2 22

DMI_PTX_CRXP3 22

DMI_CTX_PRXN1 22

DMI_CTX_PRXN2 22

DMI_CTX_PRXN3 22

DMI_CTX_PRXP0 22

DMI_CTX_PRXP1 22

DMI_CTX_PRXP2 22

DMI_CTX_PRXP3 22

FDI_TXN0 22

FDI_TXN1 22

FDI_TXN2 22

FDI_TXN3 22

FDI_TXN4 22

FDI_TXN5 22

FDI_TXN6 22

FDI_TXN7 22

FDI_TXP0 22

FDI_TXP1 22

FDI_TXP2 22

FDI_TXP3 22

FDI_TXP4 22

FDI_TXP5 22

FDI_TXP6 22

FDI_TXP7 22

FDI_FSYNC0 22

FDI_FSYNC1 22

FDI_LSYNC0 22

FDI_LSYNC1 22

FDI_INT 22

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (PCIE/DMI/FDI)

8 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (PCIE/DMI/FDI)

8 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (PCIE/DMI/FDI)

8 90 Thursday, April 22, 2010

<Core Design>

Main:62.10053.601

2nd :62.10040.611

3rd :62.10055.321

SSID = CPU

1 2 R801 49D9R2F-GP R801 49D9R2F-GP

1 2 R802 750R2F-GP R802 750R2F-GP

DMI_RX0#

A24

DMI_RX1#

C23

DMI_RX2#

B22

DMI_RX3#

A21

DMI_RX0

B24

DMI_RX1

D23

DMI_RX2

B23

DMI_RX3

A22

DMI_TX0#

D24

DMI_TX1#

G24

DMI_TX2#

F23

DMI_TX3#

H23

DMI_TX0

D25

DMI_TX1

F24

DMI_TX3

G23

DMI_TX2

E23

FDI_TX0#

E22

FDI_TX1#

D21

FDI_TX2#

D19

FDI_TX3#

D18

FDI_TX4#

G21

FDI_TX5#

E19

FDI_TX6#

F21

FDI_TX7#

G18

FDI_TX0

D22

FDI_TX1

C21

FDI_TX2

D20

FDI_TX3

C18

FDI_TX4

G22

FDI_TX5

E20

FDI_TX6

F20

FDI_TX7

G19

FDI_FSYNC0

F17

FDI_FSYNC1

E17

FDI_INT

C17

FDI_LSYNC0

F18

FDI_LSYNC1

D17

PEG_ICOMPI

B26

PEG_ICOMPO

A26

PEG_RBIAS

A25

PEG_RCOMPO

B27

PEG_RX0#

K35

PEG_RX1#

J34

PEG_RX2#

J33

PEG_RX3#

G35

PEG_RX4#

G32

PEG_RX5#

F34

PEG_RX6#

F31

PEG_RX7#

D35

PEG_RX8#

E33

PEG_RX9#

C33

PEG_RX10#

D32

PEG_RX11#

B32

PEG_RX12#

C31

PEG_RX13#

B28

PEG_RX14#

B30

PEG_RX15#

A31

PEG_RX0

J35

PEG_RX1

H34

PEG_RX2

H33

PEG_RX3

F35

PEG_RX4

G33

PEG_RX5

E34

PEG_RX6

F32

PEG_RX7

D34

PEG_RX8

F33

PEG_RX9

B33

PEG_RX10

D31

PEG_RX11

A32

PEG_RX12

C30

PEG_RX13

A28

PEG_RX14

B29

PEG_RX15

A30

PEG_TX0#

L33

PEG_TX1#

M35

PEG_TX2#

M33

PEG_TX3#

M30

PEG_TX4#

L31

PEG_TX5#

K32

PEG_TX6#

M29

PEG_TX7#

J31

PEG_TX8#

K29

PEG_TX9#

H30

PEG_TX10#

H29

PEG_TX11#

F29

PEG_TX12#

E28

PEG_TX13#

D29

PEG_TX14#

D27

PEG_TX15#

C26

PEG_TX0

L34

PEG_TX1

M34

PEG_TX2

M32

PEG_TX3

L30

PEG_TX4

M31

PEG_TX5

K31

PEG_TX6

M28

PEG_TX7

H31

PEG_TX8

K28

PEG_TX9

G30

PEG_TX10

G29

PEG_TX11

F28

PEG_TX12

E27

PEG_TX13

D28

PEG_TX14

C27

PEG_TX15

C25

P

C

I

E

X

P

R

E

S

S

-

-

G

R

A

P

H

I

C

S

D

M

I

I

n

t

e

l

(

R

)

F

D

I

1 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1A

P

C

I

E

X

P

R

E

S

S

-

-

G

R

A

P

H

I

C

S

D

M

I

I

n

t

e

l

(

R

)

F

D

I

1 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1A

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

PEG_CLK#_R

PEG_CLK_R

VDDPWRGOOD_R

BCLK_CPU_P_R

BCLK_CPU_N_R

H_COMP3

H_COMP2

H_COMP1

H_COMP0

SKTOCC#_R

H_CATERR#

H_CATERR#

H_CPURST#

PLT_RST#_R

BCLK_ITP_P

BCLK_ITP_N

SM_DRAMRST#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

H_PWRGD_XDP

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

PM_EXTTS#1_C

XDP_TDI_R

XDP_TDO_M

XDP_TDI_M

XDP_TDO_R

XDP_TDI

XDP_TDO

XDP_TRST#

XDP_TCLK

XDP_PREQ#

XDP_TDI_R

XDP_TMS

H_CPURST#

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

H_DBR#_R

XDP_TRST#

XDP_DBRESET#

XDP_OBS0

XDP_OBS1

XDP_OBS3

XDP_OBS2

XDP_OBS5

XDP_OBS4

XDP_OBS7

XDP_OBS6

XDP_OBS1

XDP_OBS5

H_CPUPWRGD_XDP

XDP_TDI

XDP_RST#_R

XDP_TDO

XDP_OBS2

XDP_TMS

BCLK_ITP_N

XDP_OBS6

H_PWRGD

PM_PWRBTN#_XDP

XDP_PRDY#

XDP_OBS3

XDP_OBS7

PCIE_CLK_XDP_P

BCLK_ITP_P

XDP_TRST#

XDP_OBS0

H_PWRGD_XDP

XDP_OBS4

H_CPURST# XDP_RST#_R

XDP_PREQ#

PM_EXTTS#0_C

XDP_TCLK

VCCPWRGOOD

H_PROCHOT#

SM_DRAMRST#

VTT_PWRGD_R3 VDDPWRGOOD_R

VDDPWRGOOD_R

+1.05V_VTT

+1.05V_VTT

+1.05V_VTT

+1.05V_VTT

+1.05V_VTT

+3.3V_RUN

+1.5V_RUN

+1.5V_SUS

CLK_EXP_N 23

CLK_EXP_P 23

H_PM_SYNC 22

PM_DRAM_PWRGD 22

BCLK_CPU_P 25

BCLK_CPU_N 25

H_PECI 25

H_PWRGD 25,42

PLT_RST# 21,37,70,76

H_VTTPWRGD 49

PM_EXTTS#1 19

SML0_DATA 23

XDP_DBRESET# 22

PM_PWRBTN#_R 22

PLT_RST# 21,37,70,76

H_THERMTRIP# 25,37,42

PM_EXTTS#0 18

SML0_CLK 23

VTT_PWRGD 37,42,49

H_PROCHOT# 47

PM_EXTTS#0_C 53

DDR3_DRAMRST# 18,19

DDR_RST_GATE 25

VDDPWRGOOD_KBC 37

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (THERMAL/CLOCK/PM )

9 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (THERMAL/CLOCK/PM )

9 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (THERMAL/CLOCK/PM )

9 90 Thursday, April 22, 2010

<Core Design>

Processor Compensation Signals

Processor Pullups

DDR3 Compensation Signals

Scan Chain

(Default)

Stuff --> R921, R924, R926

No Stuff --> R922, R925

CPU Only

GMCH Only

Stuff --> R921, R922

No Stuff --> R924, R926, R925

Stuff --> R926, R925

No Stuff --> R921, R922, R924

JTAG MAPPING

SSID = CPU

1119

No Stuff

1.27k 3k

0.75k S3 circuit

R920 R919

1.1k

Normal

1 2 R910 24D9R2F-L-GP R910 24D9R2F-L-GP

1

2

C915

SCD047U16V2ZY-1GP

C915

SCD047U16V2ZY-1GP

1

2 3

4

R

N

0R4P2R-PAD

RN906

R

N

0R4P2R-PAD

RN906

1 2

R903 20R2F-GP R903 20R2F-GP

1

2

C902

SCD1U16V2KX-3GP

DY

C902

SCD1U16V2KX-3GP

DY

1

2 3

4

RN905

SRN10KJ-5-GP

RN905

SRN10KJ-5-GP

1 2 R933 68R2-GP R933 68R2-GP

1 2 R911 130R2F-1-GP R911 130R2F-1-GP

1 2

R921 0R2J-2-GP

DY

R921 0R2J-2-GP

DY

G

S

D

. . .

.

.

Q901

2N7002E-1-GP

. . .

.

.

Q901

2N7002E-1-GP

1 2 R902 49D9R2F-GP R902 49D9R2F-GP

1 2

R925 0R2J-2-GP

DY

R925 0R2J-2-GP

DY

1

2

R919

1K1R2F-GP

DY

R919

1K1R2F-GP

DY

1 2

R914 51R2J-2-GP

DY

R914 51R2J-2-GP

DY

1

2 3

4

R

N

0R4P2R-PAD

RN903

R

N

0R4P2R-PAD

RN903

1 2

R930 0R2J-2-GP

DY

R930 0R2J-2-GP

DY

1

2

R937

750R2F-GP

R937

750R2F-GP

1 2

R931 1KR2J-1-GP

DY

R931 1KR2J-1-GP

DY

1 2 R907 100R2F-L1-GP-U R907 100R2F-L1-GP-U

1 2 R926

0R0402-PAD

R926

0R0402-PAD

1 2

R977

1K6R2F-GP

R977

1K6R2F-GP

1 2

R917 51R2J-2-GP

DY

R917 51R2J-2-GP

DY

1 2

R918 51R2J-2-GP

DY

R918 51R2J-2-GP

DY

1 2

R935 0R2J-2-GP

DY

R935 0R2J-2-GP

DY

B

1

A

2

GND

3

Y

4

VCC

5

U927

74LVC1G08GW-1-GP

U927

74LVC1G08GW-1-GP

1 2

R932 0R2J-2-GP

DY

R932 0R2J-2-GP

DY

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49 50

51 52

53 54

55 56

57 58

59 60

64

61

NP1

NP2

62

63

XDP1

PAD-60P-GP

DY

XDP1

PAD-60P-GP

DY

1 2

R913

1K6R2F-GP

R913

1K6R2F-GP

1 2

R906 49D9R2F-GP R906 49D9R2F-GP

1 2 R908

0R0402-PAD

R908

0R0402-PAD

SM_RCOMP1

AM1

SM_RCOMP2

AN1

SM_DRAMRST#

F6

SM_RCOMP0

AL1

BCLK#

B16

BCLK

A16

BCLK_ITP#

AT30

BCLK_ITP

AR30

PEG_CLK#

D16

PEG_CLK

E16

DPLL_REF_SSCLK#

A17

DPLL_REF_SSCLK

A18

CATERR#

AK14

COMP3

AT23

PECI

AT15

PROCHOT#

AN26

THERMTRIP#

AK15

RESET_OBS#

AP26

VCCPWRGOOD_1

AN14

VCCPWRGOOD_0

AN27

SM_DRAMPWROK

AK13

VTTPWRGOOD

AM15

RSTIN#

AL14

PM_EXT_TS0#

AN15

PM_EXT_TS1#

AP15

PRDY#

AT28

PREQ#

AP27

TCK

AN28

TMS

AP28

TRST#

AT27

TDI

AT29

TDO

AR27

TDI_M

AR29

TDO_M

AP29

DBR#

AN25

BPM0#

AJ22

BPM1#

AK22

BPM2#

AK24

BPM3#

AJ24

BPM4#

AJ25

BPM5#

AH22

BPM6#

AK23

BPM7#

AH23

COMP2

AT24

PM_SYNC

AL15

TAPPWRGOOD

AM26

COMP1

G16

COMP0

AT26

SKTOCC#

AH24

C

L

O

C

K

S

M

I

S

C

T

H

E

R

M

A

L

P

W

R

M

A

N

A

G

E

M

E

N

T

D

D

R

3

M

I

S

C

J

T

A

G

&

B

P

M

2 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1B

C

L

O

C

K

S

M

I

S

C

T

H

E

R

M

A

L

P

W

R

M

A

N

A

G

E

M

E

N

T

D

D

R

3

M

I

S

C

J

T

A

G

&

B

P

M

2 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1B

1 2

R978

1K6R2F-GP

DY

R978

1K6R2F-GP

DY

1

2

R928

51R2J-2-GP

R928

51R2J-2-GP

1

2

R934

1KR2J-1-GP

R934

1KR2J-1-GP

1 2

R901 20R2F-GP R901 20R2F-GP

1 2 R909

0R0402-PAD

R909

0R0402-PAD

1 2 R912

0R0402-PAD

R912

0R0402-PAD

1 2 R904 68R2-GP

DY

R904 68R2-GP

DY

1 2

R929 0R2J-2-GP

DY

R929 0R2J-2-GP

DY

1 2

R927 1KR2J-1-GP

DY

R927 1KR2J-1-GP

DY

1

2

C901

SCD1U16V2KX-3GP

DY

C901

SCD1U16V2KX-3GP

DY

1

2 3

4

R

N

0R4P2R-PAD

RN901

R

N

0R4P2R-PAD

RN901

1

2

C903

SCD1U10V2KX-5GP

C903

SCD1U10V2KX-5GP

1

2

R924

0R0402-PAD

R924

0R0402-PAD

1

2

R915

750R2F-GP

R915

750R2F-GP

1 2

R916 51R2J-2-GP

DY

R916 51R2J-2-GP

DY

1

2

R923

51R2J-2-GP

R923

51R2J-2-GP

1 TP901 TPAD14-GP TP901 TPAD14-GP

1 2

R905 49D9R2F-GP R905 49D9R2F-GP

1 2

R922 0R2J-2-GP

DY

R922 0R2J-2-GP

DY

1 2

R988

100KR2J-1-GP

R988

100KR2J-1-GP

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

M_A_DQ44

M_A_DQ36

M_A_DQ47

M_A_DQ40

M_A_DQ39

M_A_DQ37

M_A_DQ35

M_A_DQ34

M_A_DQ59

M_A_DQ54

M_A_DQ53

M_A_DQ63

M_A_DQ60

M_A_DQ61

M_A_DQ58

M_A_DQ51

M_A_DQ48

M_A_DQ57

M_A_DQ55

M_A_DQ49

M_A_DQ50

M_A_DQ62

M_A_DQ52

M_A_DQ56

M_A_DQ[63..0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ7

M_A_DQ5

M_A_DQ4

M_A_DQ6

M_A_DQ12

M_A_DQ10

M_A_DQ13

M_A_DQ9

M_A_DQ8

M_A_DQ11

M_A_DQ15

M_A_DQ14

M_A_DQ27

M_A_DQ25

M_A_DQ20

M_A_DQ19

M_A_DQ30

M_A_DQ18

M_A_DQ16

M_A_DQ28

M_A_DQ17

M_A_DQ26

M_A_DQ31

M_A_DQ29

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ21

M_A_DQ46

M_A_DQ42

M_A_DQ38

M_A_DQ32

M_A_DQ45

M_A_DQ33

M_A_DQ43

M_A_DQ41

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_A0

M_A_A6

M_A_A3

M_A_A5

M_A_A7

M_A_A1

M_A_A2

M_A_A4

M_A_A10

M_A_A8

M_A_A13

M_A_A11

M_A_A9

M_A_A12

M_A_A14

M_A_A15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ15

M_B_DQ13

M_B_DQ12

M_B_DQ14

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ23

M_B_DQ21

M_B_DQ20

M_B_DQ22

M_B_DQ28

M_B_DQ26

M_B_DQ29

M_B_DQ25

M_B_DQ31

M_B_DQ24

M_B_DQ27

M_B_DQ30

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ39

M_B_DQ37

M_B_DQ36

M_B_DQ38

M_B_DQ44

M_B_DQ42

M_B_DQ45

M_B_DQ41

M_B_DQ47

M_B_DQ40

M_B_DQ43

M_B_DQ46

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ55

M_B_DQ53

M_B_DQ52

M_B_DQ54

M_B_DQ60

M_B_DQ58

M_B_DQ61

M_B_DQ57

M_B_DQ63

M_B_DQ56

M_B_DQ59

M_B_DQ62

M_B_DQ[63..0]

M_B_A12

M_B_A9

M_B_A11

M_B_A13

M_B_A8

M_B_A10

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_A14

M_A_DQS#0

M_A_DQS#3

M_A_DQS#6

M_A_DQS#4

M_A_DQS#1

M_A_DQS#2

M_A_DQS#5

M_A_DQS#7

M_A_DQS5

M_A_DQS7

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS0

M_A_DQS1

M_A_DQS6

M_B_A15

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_A_DQ[63..0] 18

M_B_DQ[63..0] 19

M_CLK_DDR0 18

M_CLK_DDR#0 18

M_CKE0 18

M_CS#1 18

M_CS#0 18

M_CLK_DDR1 18

M_CLK_DDR#1 18

M_CKE1 18

M_ODT1 18

M_ODT0 18

M_CLK_DDR2 19

M_CLK_DDR#2 19

M_CKE2 19

M_CS#3 19

M_CS#2 19

M_ODT3 19

M_ODT2 19

M_CLK_DDR3 19

M_CLK_DDR#3 19

M_CKE3 19

M_A_BS0 18

M_A_BS1 18

M_A_BS2 18

M_B_BS0 19

M_B_BS1 19

M_B_BS2 19

M_A_CAS# 18

M_A_RAS# 18

M_A_WE# 18

M_B_CAS# 19

M_B_RAS# 19

M_B_WE# 19

M_A_DM[7..0] 18

M_A_DQS#[7..0] 18

M_A_DQS[7..0] 18

M_A_A[15..0] 18

M_B_DQS#[7..0] 19

M_B_DM[7..0] 19

M_B_DQS[7..0] 19

M_B_A[15..0] 19

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (DDR)

10 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (DDR)

10 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (DDR)

10 90 Thursday, April 22, 2010

<Core Design>

SSID = CPU

SA_BS0

AC3

SA_BS1

AB2

SA_BS2

U7

SA_CAS#

AE1

SA_RAS#

AB3

SA_WE#

AE9

SA_CK0

AA6

SA_CK1

Y6

SA_CK0#

AA7

SA_CK1#

Y5

SA_CKE0

P7

SA_CKE1

P6

SA_CS0#

AE2

SA_CS1#

AE8

SA_ODT0

AD8

SA_ODT1

AF9

SA_DM0

B9

SA_DM1

D7

SA_DM2

H7

SA_DM3

M7

SA_DM4

AG6

SA_DM5

AM7

SA_DM6

AN10

SA_DM7

AN13

SA_DQS0

C8

SA_DQS0#

C9

SA_DQS1

F9

SA_DQS1#

F8

SA_DQS2

H9

SA_DQS2#

J9

SA_DQS3

M9

SA_DQS3#

N9

SA_DQS4

AH8

SA_DQS4#

AH7

SA_DQS5

AK10

SA_DQS5#

AK9

SA_DQS6

AN11

SA_DQS6#

AP11

SA_DQS7

AR13

SA_DQS7#

AT13

SA_MA0

Y3

SA_MA1

W1

SA_MA2

AA8

SA_MA3

AA3

SA_MA4

V1

SA_MA5

AA9

SA_MA6

V8

SA_MA7

T1

SA_MA8

Y9

SA_MA9

U6

SA_MA10

AD4

SA_MA11

T2

SA_MA12

U3

SA_MA13

AG8

SA_MA14

T3

SA_MA15

V9

SA_DQ0

A10

SA_DQ1

C10

SA_DQ2

C7

SA_DQ3

A7

SA_DQ4

B10

SA_DQ5

D10

SA_DQ6

E10

SA_DQ7

A8

SA_DQ8

D8

SA_DQ9

F10

SA_DQ10

E6

SA_DQ11

F7

SA_DQ12

E9

SA_DQ13

B7

SA_DQ14

E7

SA_DQ15

C6

SA_DQ16

H10

SA_DQ17

G8

SA_DQ18

K7

SA_DQ19

J8

SA_DQ20

G7

SA_DQ21

G10

SA_DQ22

J7

SA_DQ23

J10

SA_DQ24

L7

SA_DQ25

M6

SA_DQ26

M8

SA_DQ27

L9

SA_DQ28

L6

SA_DQ29

K8

SA_DQ30

N8

SA_DQ31

P9

SA_DQ32

AH5

SA_DQ33

AF5

SA_DQ34

AK6

SA_DQ35

AK7

SA_DQ36

AF6

SA_DQ37

AG5

SA_DQ38

AJ7

SA_DQ39

AJ6

SA_DQ40

AJ10

SA_DQ41

AJ9

SA_DQ42

AL10

SA_DQ43

AK12

SA_DQ44

AK8

SA_DQ45

AL7

SA_DQ46

AK11

SA_DQ47

AL8

SA_DQ48

AN8

SA_DQ49

AM10

SA_DQ50

AR11

SA_DQ51

AL11

SA_DQ52

AM9

SA_DQ53

AN9

SA_DQ54

AT11

SA_DQ55

AP12

SA_DQ56

AM12

SA_DQ57

AN12

SA_DQ58

AM13

SA_DQ59

AT14

SA_DQ60

AT12

SA_DQ61

AL13

SA_DQ62

AR14

SA_DQ63

AP14

D

D

R

S

Y

S

T

E

M

M

E

M

O

R

Y

A

3 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1C

D

D

R

S

Y

S

T

E

M

M

E

M

O

R

Y

A

3 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1C

SB_BS0

AB1

SB_BS1

W5

SB_BS2

R7

SB_CAS#

AC5

SB_RAS#

Y7

SB_WE#

AC6

SB_CK0

W8

SB_CK1

V7

SB_CK0#

W9

SB_CK1#

V6

SB_CKE0

M3

SB_CKE1

M2

SB_CS0#

AB8

SB_CS1#

AD6

SB_ODT0

AC7

SB_ODT1

AD1

SB_DM0

D4

SB_DM1

E1

SB_DM2

H3

SB_DM3

K1

SB_DM4

AH1

SB_DM5

AL2

SB_DM6

AR4

SB_DM7

AT8

SB_DQS4

AG2

SB_DQS4#

AH2

SB_DQS5

AL5

SB_DQS5#

AL4

SB_DQS6

AP5

SB_DQS6#

AR5

SB_DQS7

AR7

SB_DQS7#

AR8

SB_DQS0

C5

SB_DQS0#

D5

SB_DQS1

E3

SB_DQS1#

F4

SB_DQS2

H4

SB_DQS2#

J4

SB_DQS3

M5

SB_DQS3#

L4

SB_MA0

U5

SB_MA1

V2

SB_MA2

T5

SB_MA3

V3

SB_MA4

R1

SB_MA5

T8

SB_MA6

R2

SB_MA7

R6

SB_MA8

R4

SB_MA9

R5

SB_MA10

AB5

SB_MA11

P3

SB_MA12

R3

SB_MA13

AF7

SB_MA14

P5

SB_MA15

N1

SB_DQ0

B5

SB_DQ1

A5

SB_DQ2

C3

SB_DQ3

B3

SB_DQ4

E4

SB_DQ5

A6

SB_DQ6

A4

SB_DQ7

C4

SB_DQ8

D1

SB_DQ9

D2

SB_DQ10

F2

SB_DQ11

F1

SB_DQ12

C2

SB_DQ13

F5

SB_DQ14

F3

SB_DQ15

G4

SB_DQ16

H6

SB_DQ17

G2

SB_DQ18

J6

SB_DQ19

J3

SB_DQ20

G1

SB_DQ21

G5

SB_DQ22

J2

SB_DQ23

J1

SB_DQ24

J5

SB_DQ25

K2

SB_DQ26

L3

SB_DQ27

M1

SB_DQ28

K5

SB_DQ29

K4

SB_DQ30

M4

SB_DQ31

N5

SB_DQ32

AF3

SB_DQ33

AG1

SB_DQ34

AJ3

SB_DQ35

AK1

SB_DQ36

AG4

SB_DQ37

AG3

SB_DQ38

AJ4

SB_DQ39

AH4

SB_DQ40

AK3

SB_DQ41

AK4

SB_DQ42

AM6

SB_DQ43

AN2

SB_DQ44

AK5

SB_DQ45

AK2

SB_DQ46

AM4

SB_DQ47

AM3

SB_DQ48

AP3

SB_DQ49

AN5

SB_DQ50

AT4

SB_DQ51

AN6

SB_DQ52

AN4

SB_DQ53

AN3

SB_DQ54

AT5

SB_DQ55

AT6

SB_DQ56

AN7

SB_DQ57

AP6

SB_DQ58

AP8

SB_DQ59

AT9

SB_DQ60

AT7

SB_DQ61

AP9

SB_DQ62

AR10

SB_DQ63

AT10

D

D

R

S

Y

S

T

E

M

M

E

M

O

R

Y

-

B

4 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1D

D

D

R

S

Y

S

T

E

M

M

E

M

O

R

Y

-

B

4 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1D

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CFG0

CFG0

CFG4

CFG7

CFG3

SA_DIMM_VREF#

SB_DIMM_VREF#

CFG3

CFG7

CFG4

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (RESERVED)

11 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (RESERVED)

11 90 Friday, April 16, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (RESERVED)

11 90 Friday, April 16, 2010

<Core Design>

PCI-Express Configuration Select

CFG0

1:Single PEG

0:Bifurcation enabled

CFG4 - Display Port Presence

CFG4

1:Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

VSS (AP34) can be left NC is

CRB implementation; EDS/DG

recommendation to GND.

CFG7(Reserved) - Temporarily used for early

Clarksfield samples.

CFG7 Clarksfield (only for early samples pre-ES1) -

Connect to GND with 3.01K Ohm/5% resistor.

Note: Only temporary for early CFD sample

(rPGA/BGA) [For details please refer to the

WW33 MoW and sighting report].

For a common M/B design (for AUB and CFD),

the pull-down resistor shouble be used. Does

not impact AUB functionality.

CFG3 - PCI-Express Static Lane Reversal

CFG3

1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

SSID = CPU

1

2

R1102

3KR2J-2-GP

DY

R1102

3KR2J-2-GP

DY

1

2

R1104

3KR2F-GP

DY

R1104

3KR2F-GP

DY

1

2

R1101

3KR2F-GP

DY

R1101

3KR2F-GP

DY

1

2

R1103

3KR2F-GP

DY

R1103

3KR2F-GP

DY

CFG0

AM30

CFG1

AM28

CFG2

AP31

CFG3

AL32

CFG4

AL30

CFG5

AM31

CFG6

AN29

CFG7

AM32

CFG8

AK32

CFG9

AK31

CFG10

AK28

CFG11

AJ28

CFG12

AN30

CFG13

AN32

CFG14

AJ32

CFG15

AJ29

CFG16

AJ30

CFG17

AK30

RSVD#AH25

AH25

RSVD#AK26

AK26

RSVD#AJ26

AJ26

RSVD#AJ27

AJ27

RSVD_TP#H16

H16

RSVD#AL28

AL28

RSVD#AL29

AL29

RSVD#AP30

AP30

RSVD#AP32

AP32

RSVD#AL27

AL27

RSVD#AT31

AT31

RSVD#AT32

AT32

RSVD#AP33

AP33

RSVD#AR33

AR33

RSVD#AR32

AR32

RSVD#J28

J28

RSVD#J29

J29

RSVD#A19

A19

RSVD#B19

B19

RSVD#A20

A20

RSVD#B20

B20

RSVD#T9

T9

RSVD#U9

U9

RSVD#AB9

AB9

RSVD#AC9

AC9

RSVD_TP#AA5

AA5

RSVD_TP#AA4

AA4

RSVD_TP#R8

R8

RSVD_TP#AA2

AA2

RSVD_TP#AA1

AA1

RSVD_TP#R9

R9

RSVD_TP#AD3

AD3

RSVD_TP#AG7

AG7

RSVD_TP#AD2

AD2

RSVD_TP#AE3

AE3

RSVD_TP#V4

V4

RSVD_TP#V5

V5

RSVD_TP#N2

N2

RSVD_TP#W3

W3

RSVD_TP#W2

W2

RSVD_TP#N3

N3

RSVD_TP#AD5

AD5

RSVD_TP#AE5

AE5

RSVD_TP#AD7

AD7

RSVD_TP#AD9

AD9

RSVD#AL26

AL26

RSVD#AP25

AP25

RSVD#AL25

AL25

RSVD#AL24

AL24

RSVD#AL22

AL22

RSVD#AJ33

AJ33

RSVD#AG9

AG9

RSVD#M27

M27

RSVD#L28

L28

SA_DIMM_VREF#

J17

SB_DIMM_VREF#

H17

RSVD#G25

G25

RSVD#G17

G17

RSVD#E31

E31

RSVD#E30

E30

RSVD#AJ13

AJ13

RSVD#AJ12

AJ12

RSVD_TP#E15

E15

RSVD_TP#F15

F15

KEY

A2

RSVD#D15

D15

RSVD#C15

C15

RSVD#AJ15

AJ15

RSVD#AH15

AH15

VSS

AP34

RSVD_NCTF#AR2

AR2

R

E

S

E

R

V

E

D

5 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1E

R

E

S

E

R

V

E

D

5 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1E

1 TP1116 TP1116

1 TP1117 TP1117

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

H_VID6

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VTTVID1

TP_VSS_SENSE_VTT

+VCC_CORE

+1.05V_VTT

+1.05V_VTT

+1.05V_VTT

+VCC_CORE

+VCC_CORE

H_VID[6..0] 47

VCC_SENSE 47

VSS_SENSE 47

PSI# 47

PM_DPRSLPVR 47

IMVP_IMON 47

VTT_SENSE 49

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (VCC_CORE)

12 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (VCC_CORE)

12 90 Thursday, April 22, 2010

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DJ1 Calpella UMA X01

CPU (VCC_CORE)

12 90 Thursday, April 22, 2010

<Core Design>

PROCESSOR CORE POWER

The decoupling capacitors, filter

recommendations and sense resistors on the

CPU/PCH Rails are specific to the CRB

Implementation. Customers need to follow the

recommendations in the Calpella Platform

Design Guide.

Please note that the VTT Rail

Values are Auburndale

VTT=1.05V; Clarksfield

VTT=1.1V

H_VTTVID1 = Low, 1.1V

H_VTTVID1 = High, 1.05V

48A

SSID = CPU

2010/04/19

X01

1

2

C1214

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1214

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1206

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

C1206

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

1

2

C1238

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

C1238

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

1

2

C1221

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1221

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

R1201

100R2F-L1-GP-U

R1201

100R2F-L1-GP-U

1

2

C1209

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1209

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1212

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

C1212

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

1

2

C1234

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

DY

C1234

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

DY

1

2

C1218

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1218

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

R1204

100R2F-L1-GP-U

R1204

100R2F-L1-GP-U

1

2

C1211

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1211

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1237

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

C1237

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

1

2

C1240

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1240

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1226

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

DY

C1226

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

DY

1

2

C1210

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1210

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1217

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1217

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1224

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1224

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1236

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1236

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1235

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1235

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1230

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1230

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1205

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1205

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1223

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1223

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1202

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1202

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1222

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

DY

C1222

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

DY

1

2

C1229

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

C1229

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

1

2

C1220

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

C1220

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

1

2

C1243

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1243

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1227

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1227

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1201

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1201

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1213

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1213

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1219

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

DY

C1219

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

DY

1

2

C1241

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

C1241

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

1

2

C1231

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

C1231

S

C

1

0

U

6

D

3

V

5

M

X

-

3

G

P

1

2

C1232

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1232

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1225

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1225

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1216

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1216

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1 TP1201TPAD14-GP TP1201TPAD14-GP

1

2

C1208

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1208

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1233

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1233

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1203

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

DY

C1203

S

C

1

0

U

1

0

V

5

Z

Y

-

1

G

P

DY

ISENSE

AN35

VTT_SENSE

B15

PSI#

AN33

VID0

AK35

VID1

AK33

VID2

AK34

VID3

AL35

VID4

AL33

VID5

AM33

VID6

AM35

PROC_DPRSLPVR

AM34

VTT_SELECT

G15

VCC_SENSE

AJ34

VSS_SENSE_VTT

A15

VCC

AG35

VCC

AG34

VCC

AG33

VCC

AG32

VCC

AG31

VCC

AG30

VCC

AG29

VCC

AG28

VCC

AG27

VCC

AG26

VCC

AF35

VCC

AF34

VCC

AF33

VCC

AF32

VCC

AF31

VCC

AF30

VCC

AF29

VCC

AF28

VCC

AF27

VCC

AF26

VCC

AD35

VCC

AD34

VCC

AD33

VCC

AD32

VCC

AD31

VCC

AD30

VCC

AD29

VCC

AD28

VCC

AD27

VCC

AD26

VCC

AC35

VCC

AC34

VCC

AC33

VCC

AC32

VCC

AC31

VCC

AC30

VCC

AC29

VCC

AC28

VCC

AC27

VCC

AC26

VCC

AA35

VCC

AA34

VCC

AA33

VCC

AA32

VCC

AA31

VCC

AA30

VCC

AA29

VCC

AA28

VCC

AA27

VCC

AA26

VCC

Y35

VCC

Y34

VCC

Y33

VCC

Y32

VCC

Y31

VCC

Y30

VCC

Y29

VCC

Y28

VCC

Y27

VCC

Y26

VCC

V35

VCC

V34

VCC

V33

VCC

V32

VCC

V31

VCC

V30

VCC

V29

VCC

V28

VCC

V27

VCC

V26

VCC

U35

VCC

U34

VCC

U33

VCC

U32

VCC

U31

VCC

U30

VCC

U29

VCC

U28

VCC

U27

VCC

U26

VCC

R35

VCC

R34

VCC

R33

VCC

R32

VCC

R31

VCC

R30

VCC

R29

VCC

R28

VCC

R27

VCC

R26

VCC

P35

VCC

P34

VCC

P33

VCC

P32

VCC

P31

VCC

P30

VCC

P29

VCC

P28

VCC

P27

VCC

P26

VTT0

AF10

VTT0

AE10

VTT0

AC10

VTT0

AB10

VTT0

Y10

VTT0

W10

VTT0

U10

VTT0

T10

VTT0

J12

VTT0

J11

VTT0

AH14

VTT0

AH12

VTT0

AH11

VTT0

AH10

VTT0

J14

VTT0

J13

VTT0

H14

VTT0

H12

VTT0

G14

VTT0

G13

VTT0

G12

VTT0

G11

VTT0

F14

VTT0

F13

VTT0

F12

VTT0

F11

VTT0

E14

VTT0

E12

VTT0

D14

VTT0

D13

VTT0

D12

VTT0

D11

VTT0

C14

VTT0

C13

VTT0

C12

VTT0

C11

VTT0

B14

VTT0

B12

VTT0

A14

VTT0

A13

VTT0

A12

VTT0

A11

VSS_SENSE

AJ35

VTT0

J16

VTT0

J15

P

O

W

E

R

C

P

U

C

O

R

E

S

U

P

P

L

Y

1

.

1

V

R

A

I

L

P

O

W

E

R

S

E

N

S

E

L

I

N

E

S

C

P

U

V

I

D

S

6 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1F

P

O

W

E

R

C

P

U

C

O

R

E

S

U

P

P

L

Y

1

.

1

V

R

A

I

L

P

O

W

E

R

S

E

N

S

E

L

I

N

E

S

C

P

U

V

I

D

S

6 OF 9

A

U

B

U

R

N

D

A

L

E

CPU1F

1

2

C1215

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

C1215

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

1

2

C1242

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

C1242

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

1

2

C1207

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

C1207

S

C

1

0

U

6

D

3

V

5

K

X

-

1

G

P

DY

1

2

C1204

S

C

1

0

U

1