Académique Documents

Professionnel Documents

Culture Documents

Data Sheet

Transféré par

w32yCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Data Sheet

Transféré par

w32yDroits d'auteur :

Formats disponibles

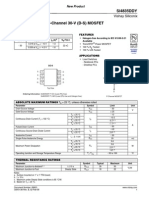

N-CHANNEL 30V - 0.050 - 3.

5A SO-8

P-CHANNEL 30V - 0.140 - 3A SO-8

STripFET II POWER MOSFET

1/10 February 2002

.

STS3C3F30L

I TYPICAL R

DS

(on) (N-Channel) = 50 m

I TYPICAL R

DS

(on) (P-Channel) = 140 m

I STANDARD OUTLINE FOR EASY

AUTOMATED SURFACE MOUNT ASSEMBLY

I LOW THRESHOLD DRIVE

DESCRIPTION

This application specific Power MOSFET is the second

generation of STMicroelectronis unique "Single Feature

Size" strip-based process. The resulting transistor

shows extremely high packing density for low on-resis-

tance, rugged avalanche characteristics and less critical

alignment steps therefore a remarkable manufacturing re-

producibility.

APPLICATIONS

I DC/DC CONVERTERS

I BATTERY MANAGEMENT IN NOMADIC

EQUIPMENT

I POWER MANAGEMENT IN CELLULAR

PHONES

TYPE V

DSS

R

DS(on)

I

D

STS3C3F30L(N-Channel)

STS3C3F30L(P-Channel)

30 V

30 V

< 65 m

< 165 m

3.5 A

3 A

SO-8

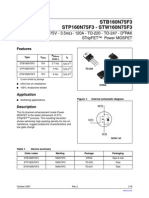

ABSOLUTE MAXIMUM RATINGS

() Pulse width limited by safe operating area. Note: P-CHANNEL MOSFET actual polarity of voltages and current

has to be reversed

Symbol Parameter N-CHANNEL P-CHANNEL Unit

V

DS

Drain-source Voltage (V

GS

= 0) 30 V

V

DGR

Drain-gate Voltage (R

GS

= 20 k) 30 V

V

GS Gate- source Voltage 16 V

I

D

Drain Current (continuos) at T

C

= 25C

Single Operating

3.5 2.7 A

I

D

Drain Current (continuos) at T

C

= 100C

Single Operating

2.2 1.7 A

I

DM

() Drain Current (pulsed) 14 11 A

P

tot

Total Dissipation at T

C

= 25C Dual Operating

Total Dissipation at T

C

= 25C Single Operating

1.6

2

W

W

T

stg Storage Temperature -60 to 150 C

T

j Max. Operating Junction Temperature 150 C

INTERNAL SCHEMATIC DIAGRAM

STS3C3F30L

2/10

THERMAL DATA

(1) when mounted on 0.5 in

2

pad of 2 oz. copper

ELECTRICAL CHARACTERISTICS (T

case

= 25 C unless otherwise specified)

OFF

ON

DYNAMIC

Rthj-amb(1)

T

l

Thermal Resistance Junction-ambient Single Operation

Dual Operating

Maximum Lead Temperature For Soldering Purpose

62.5

78

300

C/W

C/W

C

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

(BR)DSS

Drain-source

Breakdown Voltage

I

D

= 250 A, V

GS

= 0 30

V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating T

C

= 125C

1

10

A

A

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

GS

= 16 V 100 nA

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

GS(th)

Gate Threshold Voltage V

DS

= V

GS

I

D

= 250 A n-ch

p-ch

1

1

V

V

R

DS(on) Static Drain-source On

Resistance

V

GS

= 10 V I

D

= 1.75 A

V

GS

= 10 V I

D

= 1.5 A

V

GS

= 4.5 V I

D

= 1.75 A

V

GS

= 4.5 V I

D

= 1.5 A

n-ch

p-ch

n-ch

p-ch

50

140

60

160

65

165

90

200

m

m

m

m

Symbol Parameter Test Conditions Min. Typ. Max. Unit

g

fs

(*)

Forward Transconductance V

DS

= 15 V I

D

= 1.75 A

V

DS

= 15 V I

D

= 1.5 A

n-ch

p-ch

5.5

4

S

S

C

iss

C

oss

C

rss

Input Capacitance

Output Capacitance

Reverse Transfer

Capacitance

V

DS

= 25V, f = 1 MHz, V

GS

= 0

n-ch

p-ch

n-ch

p-ch

n-ch

p-ch

320

420

90

95

40

30

pF

pF

pF

pF

pF

pF

3/10

STS3C3F30L

SWITCHING ON

SWITCHING OFF

SOURCE DRAIN DIODE

() Pulsed: Pulse duration = 300 s, duty cycle 1.5 %.

() Pulse width limited by safe operating area.

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(on)

t

r

Turn-on Delay Time

Rise Time

N-CHANNEL

V

DD

= 15 V I

D

= 1.75 A

R

G

= 4.7 V

GS

= 4.5 V

P-CHANNEL

V

DD

= 15 V I

D

= 1.5 A

R

G

= 4.7 V

GS

= 4.5 V

(Resistive Load, Figure 1)

n-ch

p-ch

n-ch

p-ch

27

14.5

40

37

ns

ns

ns

ns

Qg

Q

gs

Q

gd

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

N-CHANNEL

V

DD

=24V I

D

=3.5A

V

GS

=4.5V

P-CHANNEL

V

DD

= 24V I

D

= 3A V

GS

= 4.5V

(see test circuit, Figure 2)

n-ch

p-ch

n-ch

p-ch

n-ch

p-ch

8.5

4.8

2

1.7

4

2

12

7

nC

nC

nC

nC

nC

nC

Symbol Parameter Test Conditions Min. Typ. Max. Unit

t

d(off)

t

f

Turn-off Delay Time

Fall Time

N-CHANNEL

V

DD

= 15 V I

D

= 1.75 A

R

G

= 4.7 V

GS

= 4.5 V

P-CHANNEL

V

DD

= 15 V I

D

= 1.5 A

R

G

= 4.7 V

GS

= 4.5 V

(Resistive Load, Figure 1)

n-ch

p-ch

n-ch

p-ch

30

90

20

23

ns

ns

ns

ns

Symbol Parameter Test Conditions Min. Typ. Max. Unit

I

SD

I

SDM

()

Source-drain Current

Source-drain Current (pulsed)

n-ch

p-ch

n-ch

p-ch

3.5

3

14

12

A

A

A

A

V

SD

() Forward On Voltage I

SD

= 3.5 A V

GS

= 0

I

SD

= 3 A V

GS

= 0

n-ch

p-ch

1.2

1.2

V

V

t

rr

Q

rr

I

RRM

Reverse Recovery Time

Reverse Recovery Charge

Reverse Recovery Current

N-CHANNEL

I

SD

= 3.5 A di/dt = 100A/s

V

DD

= 15 V T

j

=150

o

C

P-CHANNEL

I

SD

= 3 A di/dt = 100A/s

V

DD

= 15 V T

j

=150

o

C

(see test circuit, Figure 3)

n-ch

p-ch

n-ch

p-ch

n-ch

p-ch

28

35

18

25

1.3

1.5

ns

ns

nC

nC

A

A

ELECTRICAL CHARACTERISTICS (continued)

STS3C3F30L

4/10

Safe Operating Area n-ch Thermal Impedance n-ch

Output Characteristics n-ch Transfer Characteristics n-ch

Transconductance n-ch Static Drain-source On Resistance n-ch

5/10

STS3C3F30L

Gate Charge vs Gate-source Voltage n-ch Capacitance Variations n-ch

Normalized Gate Threshold Voltage vs Temperature n-ch Normalized on Resistance vs Temperature n-ch

Source-drain Diode Forward Characteristics n-ch

STS3C3F30L

6/10

Safe Operating Area p-ch Thermal Impedance p-ch

Output Characteristics p-ch Transfer Characteristics p-ch

Transconductance p-ch Static Drain-source On Resistance p-ch

7/10

STS3C3F30L

Gate Charge vs Gate-source Voltage p-ch Capacitance Variations p-ch

Normalized Gate Threshold Voltage vs Temperature p-ch Normalized on Resistance vs Temperature p-ch

Source-drain Diode Forward Characteristics p-ch

STS3C3F30L

8/10

Fig. 2: Gate Charge test Circuit

Fig. 3: Test Circuit For Diode Recovery Behaviour

Fig. 1: Switching Times Test Circuits For Resistive

Load

9/10

STS3C3F30L

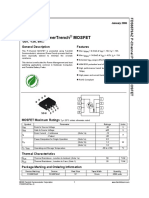

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 1.75 0.068

a1 0.1 0.25 0.003 0.009

a2 1.65 0.064

a3 0.65 0.85 0.025 0.033

b 0.35 0.48 0.013 0.018

b1 0.19 0.25 0.007 0.010

C 0.25 0.5 0.010 0.019

c1 45 (typ.)

D 4.8 5.0 0.188 0.196

E 5.8 6.2 0.228 0.244

e 1.27 0.050

e3 3.81 0.150

F 3.8 4.0 0.14 0.157

L 0.4 1.27 0.015 0.050

M 0.6 0.023

S 8 (max.)

0016023

SO-8 MECHANICAL DATA

STS3C3F30L

10/10

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is registered trademark of STMicroelectronics

2002 STMicroelectronics - All Rights Reserved

All other names are the property of their respective owners.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com

Vous aimerez peut-être aussi

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- W15NB50Document9 pagesW15NB50G Ivan Torres RPas encore d'évaluation

- 110 Waveform Generator Projects for the Home ConstructorD'Everand110 Waveform Generator Projects for the Home ConstructorÉvaluation : 4 sur 5 étoiles4/5 (1)

- P6NA60FIDocument11 pagesP6NA60FIvigalPas encore d'évaluation

- STH15NA50/FI STW15NA50: N - Channel Enhancement Mode Fast Power Mos TransistorDocument11 pagesSTH15NA50/FI STW15NA50: N - Channel Enhancement Mode Fast Power Mos Transistoras135qPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- p9nb50 PDFDocument9 pagesp9nb50 PDFceftv1Pas encore d'évaluation

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1D'EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Évaluation : 4.5 sur 5 étoiles4.5/5 (3)

- P 9 NC 60 FPDocument9 pagesP 9 NC 60 FPJulian PascuPas encore d'évaluation

- Irfp460: N - Channel 500V - 0.22 - 20 A - To-247 Powermesh MosfetDocument8 pagesIrfp460: N - Channel 500V - 0.22 - 20 A - To-247 Powermesh MosfetAngelescuOPas encore d'évaluation

- STP6NA80 Stp6Na80Fi: N - Channel Enhancement Mode Fast Power Mos TransistorDocument11 pagesSTP6NA80 Stp6Na80Fi: N - Channel Enhancement Mode Fast Power Mos Transistorz01loPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Évaluation : 2.5 sur 5 étoiles2.5/5 (3)

- General Description Product Summary: 30V Dual P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V Dual P-Channel MOSFETshibilvPas encore d'évaluation

- Irf S40Document10 pagesIrf S40Kishor YennamPas encore d'évaluation

- SFR/U9120: Advanced Power MOSFETDocument7 pagesSFR/U9120: Advanced Power MOSFETJavier BendekPas encore d'évaluation

- Irfp 450 RDocument8 pagesIrfp 450 Rpisy74Pas encore d'évaluation

- N - Channel 500V - 0.22 - 20A - To-247 Powermesh Mosfet: Stw20Nb50Document8 pagesN - Channel 500V - 0.22 - 20A - To-247 Powermesh Mosfet: Stw20Nb50La Tienda del PatínPas encore d'évaluation

- Datasheet IRFBC40Document8 pagesDatasheet IRFBC40Henry BarbozaPas encore d'évaluation

- IRFP450Document9 pagesIRFP450roozbehxoxPas encore d'évaluation

- N - Channel 800V - 1.8 - 5A - To-220/To-220Fp Powermesh MosfetDocument10 pagesN - Channel 800V - 1.8 - 5A - To-220/To-220Fp Powermesh MosfetHerpadianaPas encore d'évaluation

- Strh80P6Fsy3: P-Channel 60V - 0.021 - To-254Aa Rad-Hard Low Gate Charge Stripfet™ Power MosfetDocument12 pagesStrh80P6Fsy3: P-Channel 60V - 0.021 - To-254Aa Rad-Hard Low Gate Charge Stripfet™ Power MosfetNegru P. PlantatiePas encore d'évaluation

- Irf 830Document9 pagesIrf 830Ehb ErglocPas encore d'évaluation

- STP55NE06 STP55NE06FP: N - Channel Enhancement Mode " Single Feature Size " Power MosfetDocument9 pagesSTP55NE06 STP55NE06FP: N - Channel Enhancement Mode " Single Feature Size " Power MosfetLiliana Nadia MarchisPas encore d'évaluation

- IRF740Document8 pagesIRF740lukasz_b7Pas encore d'évaluation

- Si4835DDY: Vishay SiliconixDocument10 pagesSi4835DDY: Vishay SiliconixRoberto Celedón AguileraPas encore d'évaluation

- Buz 10Document8 pagesBuz 10k_goulasPas encore d'évaluation

- STP2NA50 Stp2Na50Fi: N - Channel Enhancement Mode Power Mos TransistorDocument6 pagesSTP2NA50 Stp2Na50Fi: N - Channel Enhancement Mode Power Mos TransistorMatei LaurentiuPas encore d'évaluation

- Obsolete Product(s) - Obsolete Product(s)Document10 pagesObsolete Product(s) - Obsolete Product(s)patopickPas encore d'évaluation

- 30A, 50V, 0.040 Ohm, N-Channel Power Mosfet Features: June 1999 File Number 2253.2 Data SheetDocument7 pages30A, 50V, 0.040 Ohm, N-Channel Power Mosfet Features: June 1999 File Number 2253.2 Data SheetArturo LaynaPas encore d'évaluation

- Datasheet 2SK3797 Mosfet Fuente Proyector Viewsonic PJD5123Document6 pagesDatasheet 2SK3797 Mosfet Fuente Proyector Viewsonic PJD5123Rubén Nicanor Sandoval BascuñanPas encore d'évaluation

- P3NA80FI DatasheetDocument10 pagesP3NA80FI DatasheetAnonymous RCPxaonfvPas encore d'évaluation

- STP6NA60 Stp6Na60Fi: N - Channel Enhancement Mode Fast Power Mos TransistorDocument10 pagesSTP6NA60 Stp6Na60Fi: N - Channel Enhancement Mode Fast Power Mos TransistorAlejandro Borrego DominguezPas encore d'évaluation

- Stw45Nm50Fd: N-Channel 500 V, 0.07, 45 A, To-247 Fdmesh™ Power Mosfet (With Fast Diode)Document12 pagesStw45Nm50Fd: N-Channel 500 V, 0.07, 45 A, To-247 Fdmesh™ Power Mosfet (With Fast Diode)Djzedamendoa Jose LopesPas encore d'évaluation

- FET - Inverter12v - IRF740Document9 pagesFET - Inverter12v - IRF740Macuco CamPas encore d'évaluation

- STP33N10 STP33N10FI: N - Channel Enhancement Mode Power Mos TransistorDocument10 pagesSTP33N10 STP33N10FI: N - Channel Enhancement Mode Power Mos Transistorjovares2099Pas encore d'évaluation

- IRF630 IRF630FP: N - CHANNEL 200V - 0.35 - 9A - TO-220/FP Mesh Overlay MosfetDocument10 pagesIRF630 IRF630FP: N - CHANNEL 200V - 0.35 - 9A - TO-220/FP Mesh Overlay MosfetAlex OrePas encore d'évaluation

- Ntmfs4119n DDocument5 pagesNtmfs4119n DRafael HurtadoPas encore d'évaluation

- STP80NF70: N-Channel 68 V, 0.0082, 98 A, TO-220 Stripfet™ Ii Power MosfetDocument13 pagesSTP80NF70: N-Channel 68 V, 0.0082, 98 A, TO-220 Stripfet™ Ii Power MosfetAsif IqbalPas encore d'évaluation

- P4NC60Document9 pagesP4NC60Gabino OrtizPas encore d'évaluation

- 600V N-Channel Enhancement Mode Fast Power MOS TransistorDocument10 pages600V N-Channel Enhancement Mode Fast Power MOS TransistorLuis Granadillo OjedaPas encore d'évaluation

- Fds 4435Document5 pagesFds 4435Rommel LoayzaPas encore d'évaluation

- P6NA60FP DatasheetDocument5 pagesP6NA60FP DatasheetJess AJPas encore d'évaluation

- Stx30N65M5: N-Channel 650 V, 0.130, 21 A, Mdmesh™ V Power Mosfet D Pak, I Pak, To-220Fp, To-220, To-247Document15 pagesStx30N65M5: N-Channel 650 V, 0.130, 21 A, Mdmesh™ V Power Mosfet D Pak, I Pak, To-220Fp, To-220, To-247Oscar PortelaPas encore d'évaluation

- Stp60nf03l - N-Channel 30v - 0.008 Ohm - 60a To-220 Stripfet Power Mosfet - StmicroelectronicsDocument6 pagesStp60nf03l - N-Channel 30v - 0.008 Ohm - 60a To-220 Stripfet Power Mosfet - StmicroelectronicsJulio César Rosas GonzálezPas encore d'évaluation

- 900V 7A N-Channel Power MOSFET TO-247/ISOWATT218 DatasheetDocument9 pages900V 7A N-Channel Power MOSFET TO-247/ISOWATT218 DatasheetAngel Simo MoralesPas encore d'évaluation

- mbrx0540 Schottky Barrier DiodeDocument5 pagesmbrx0540 Schottky Barrier DiodeMochammad SofyanPas encore d'évaluation

- 2SK3667Q DatasheetzDocument6 pages2SK3667Q DatasheetzИегҵ ГемасснеPas encore d'évaluation

- Fet 60NF06Document9 pagesFet 60NF06Anh Nguyễn HoàngPas encore d'évaluation

- BTW 69Document6 pagesBTW 69Alfredo Valencia RodriguezPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryAnais Cullon BermejoPas encore d'évaluation

- 9NM60NDocument16 pages9NM60NAlbert GTPas encore d'évaluation

- MOCD207M, MOCD208M Dual-Channel Phototransistor Small Outline Surface Mount OptocouplersDocument9 pagesMOCD207M, MOCD208M Dual-Channel Phototransistor Small Outline Surface Mount Optocouplershunter73100% (1)

- P-Channel Logic Level Enhancement MOSFETDocument5 pagesP-Channel Logic Level Enhancement MOSFETsilasmateusPas encore d'évaluation

- AP4506GEM - 30V/6.4A N-Channel and -30V/-6A P-Channel Power MOSFET in SO-8Document7 pagesAP4506GEM - 30V/6.4A N-Channel and -30V/-6A P-Channel Power MOSFET in SO-8yokonakagimaPas encore d'évaluation

- Stb160N75F3 Stp160N75F3 - Stw160N75F3: N-Channel 75V - 3.5M - 120A - To-220 - To-247 - D Pak Stripfet™ Power MosfetDocument16 pagesStb160N75F3 Stp160N75F3 - Stw160N75F3: N-Channel 75V - 3.5M - 120A - To-220 - To-247 - D Pak Stripfet™ Power MosfetmoabdolyPas encore d'évaluation

- Stw57N65M5-4: N-Channel 650 V, 0.056 Typ., 42 A, Mdmesh™ V Power Mosfet in A To247-4 PackageDocument14 pagesStw57N65M5-4: N-Channel 650 V, 0.056 Typ., 42 A, Mdmesh™ V Power Mosfet in A To247-4 PackageCristiano BruschiniPas encore d'évaluation

- SM4319PSK Datasheet PDFDocument11 pagesSM4319PSK Datasheet PDFban4444Pas encore d'évaluation

- Motorola Bipolar Power Transistor Technical Data SheetDocument6 pagesMotorola Bipolar Power Transistor Technical Data SheetpabloPas encore d'évaluation

- MJ 15003 (NPN)Document3 pagesMJ 15003 (NPN)Johanes StPas encore d'évaluation

- 9N50CDocument10 pages9N50CtecjotaPas encore d'évaluation

- 15N41CLGDocument11 pages15N41CLGssarbani720Pas encore d'évaluation

- 10NK80Document15 pages10NK80Abubakar SidikPas encore d'évaluation

- NPN 2N3773, PNP 2N6609 Complementary Silicon Power TransistorsDocument7 pagesNPN 2N3773, PNP 2N6609 Complementary Silicon Power TransistorsmaneaviorelPas encore d'évaluation

- MJL3281ADocument7 pagesMJL3281ARaduPas encore d'évaluation

- U2 L7 Switching Limits PDFDocument8 pagesU2 L7 Switching Limits PDFBright Tendai ChingwenaPas encore d'évaluation

- Semiconductor Technical Data: 50 Ampere NPN Silicon Power Darlington Transistors 400 AND 500 VOLTS 250 WATTSDocument6 pagesSemiconductor Technical Data: 50 Ampere NPN Silicon Power Darlington Transistors 400 AND 500 VOLTS 250 WATTSjoelpalzaPas encore d'évaluation

- SAP16N: Absolute Maximum Ratings Electrical CharacteristicsDocument1 pageSAP16N: Absolute Maximum Ratings Electrical CharacteristicsLoic TrocmePas encore d'évaluation

- Silicon Power Transistor: NPN Silicon Epitaxial Transistor For High-Speed SwitchingDocument6 pagesSilicon Power Transistor: NPN Silicon Epitaxial Transistor For High-Speed SwitchingYüksel DoğrulPas encore d'évaluation

- 04 Power SCD 2Document82 pages04 Power SCD 2riajulPas encore d'évaluation

- STR-W6000S Series: Off-Line PWM Controllers With Integrated Power MOSFETDocument26 pagesSTR-W6000S Series: Off-Line PWM Controllers With Integrated Power MOSFETJulian Andres RozoPas encore d'évaluation

- Insulated Gate Bipolar Transistors (Igbts) : Lecture NotesDocument17 pagesInsulated Gate Bipolar Transistors (Igbts) : Lecture NotesTe NgPas encore d'évaluation

- FDS6679AZ DatasheetDocument6 pagesFDS6679AZ DatasheetMarivaldo NascimentoPas encore d'évaluation

- En CD00168872 PDFDocument16 pagesEn CD00168872 PDFLeonel ValençaPas encore d'évaluation

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument13 pagesN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataEdson CostaPas encore d'évaluation

- STV9302B: Vertical Deflection Booster For 2-A TV (50-60 HZ) Applications With 70-V Flyback GeneratorDocument15 pagesSTV9302B: Vertical Deflection Booster For 2-A TV (50-60 HZ) Applications With 70-V Flyback GeneratorJunior LopezPas encore d'évaluation

- pld10k CHDocument24 pagespld10k CHPer PersoPas encore d'évaluation

- Control Techniques Drives and Controls Handbook by 3ADocument348 pagesControl Techniques Drives and Controls Handbook by 3AFatih YamanPas encore d'évaluation

- Datasheet Modulo IgbtDocument8 pagesDatasheet Modulo IgbtJaime MendozaPas encore d'évaluation

- TIP140, TIP141, TIP142, (NPN) TIP145, TIP146, TIP147, (PNP) Darlington Complementary Silicon Power TransistorsDocument8 pagesTIP140, TIP141, TIP142, (NPN) TIP145, TIP146, TIP147, (PNP) Darlington Complementary Silicon Power TransistorsroozbehxoxPas encore d'évaluation

- TIP110, T IP115: Darlington TransistorsDocument5 pagesTIP110, T IP115: Darlington Transistorsمحمدعبدالخالق العلوانيPas encore d'évaluation

- Multiple Choice QuestionsDocument39 pagesMultiple Choice QuestionsSunil Gadekar80% (20)

- 11NM60NDocument20 pages11NM60NPedro GabrielPas encore d'évaluation

- Dsa00534608 PDFDocument8 pagesDsa00534608 PDFHugo ApontePas encore d'évaluation

- FQB11P06 / FQI11P06: 60V P-Channel MOSFETDocument9 pagesFQB11P06 / FQI11P06: 60V P-Channel MOSFETlion_staPas encore d'évaluation

- Ece-Vii-Power Electronics (10ec73) - Notes PDFDocument264 pagesEce-Vii-Power Electronics (10ec73) - Notes PDFafzal646100% (3)

- Mje 15030Document6 pagesMje 15030Ahmed ZagharyPas encore d'évaluation

- H25R1202Document12 pagesH25R1202Alejandro Borrego DominguezPas encore d'évaluation