Académique Documents

Professionnel Documents

Culture Documents

Two Stage

Transféré par

ty391988Description originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Two Stage

Transféré par

ty391988Droits d'auteur :

Formats disponibles

April 15, 2014 1

ECE 3274

Two-Stage Amplifier Project

1. Objective

The objective of this lab is to design and build a two-stage amplifier, including a

common-source gain stage and a common-collector buffer stage.

2. Components

Qty Device

1 2N2222 BJT Transistor

1 2N7000 MOSFET Transistor

3. Introduction

Multistage amplifiers are made up of single transistor amplifiers connected in cascade.

The first stage usually provides a high input impedance to minimize loading the source

(transducer). The middle stages usually account for most of the desired voltage gain.

The final stage provides a low output impedance to prevent loss of signal (gain), and to

be able to handle the amount of current required by the load.

When analyzing multistage amplifiers, the loading effect of the each stage must be

considered, since the input impedance of the next stage acts as the load impedance for

the previous stage. Therefore, the ac analysis of a multistage amplifier is usually done

starting with the final stage. The individual stages are usually coupled either with a

capacitor, or by direct coupling. Capacitive coupling is most often used when the signals

being amplified are ac signals. With capacitive coupling, the stages are separated by a

capacitor, which blocks the dc voltages between each stage. This dc blocking prevents

the bias point of each stage from being upset. DC coupling requires more attention to

detail in the bias network, but allow for good low-frequency response (usually down to

dc).

The CS-CC cascade two-stage amplifier is a good multistage configuration

because the CS and CC amplifiers together provide some very desirable characteristics.

The CS amplifier makes up the first stage and is capable of providing high voltage gain.

The input impedance of the CS is a function of RG1 and RG2 and is generally very high.

The output impedance of the CS is approximately equal to Rd || r0, which is usually in the

k range. The CC amplifier makes up the second stage and has the characteristics of

high input impedance, very low output impedance, and high current gain.

In a cascade configuration, the overall voltage and current gains are given by:

AV overall =AV first stage * AV second stage

AI overall = AI first stage * AI second stage

In designing this amplifier, it is highly recommend that you take advantage of the work

you did in the Common-Collector and CS MOSFET amplifier labs. You may need to make

minor modifications to your work, but on the whole these amplifier should be very good

April 15, 2014 2

starting places. You need not show your work on the bias points, but you should show

how you calculate all overall values in this lab.

You should refer to your lab lecture notes, your Electronics II Lecture notes, your textbook,

the course website, and other reference material to determine how best to design your

amplifier. This lab is intended as a design project and not as a step-by-step guide.

4. Requirements

Your amplifier design must meet the following requirements.

Requirement Specification

Voltage Gain (Source Fully Bypassed) |Av| > 5 V/V

Low Frequency Cutoff Between 100 Hz and 200 Hz

High Frequency Cutoff Between 50 kHz and 150 kHz

Overall Input Impedance Greater than 100 k

Output Voltage Swing Greater than 3 Vpk-pk

Load Resistance 1.0 k

Power Supply Voltage (Vcc) 12 Vdc

Table 1. Two-stage amplifier requirements.

5. Prelab Design Project

You will design one two-stage in this prelab design project. You should start with your

previous designs for a common-collector and common-source amplifier, and modify them

(if necessary) to meet the requirements for this lab. (The DC bias should not need to

change but you capacitors may need to change). Then calculate values for the new

components, such as C12.

You may use a MATLAB (or similar) program to run calculations if you would like, but

your code and output must be included, and you must comment your code to indicate

where all equations came from and any assumptions you made. You should also show

all work in handwriting. Units must be included as well, and it is recommend that you

generate a table of final values. Use the following fixed component values in your circuit:

Component Value

Ri 10K

Cbyp 0.1F

Table 2. Fixed component

values.

April 15, 2014 3

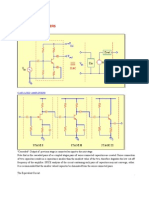

Vcc

50

1k

Rload

Rb1

Rb2

Re

Rs

Rd

Rg1

Rg2

Cs

Cout

Cin

0.1uF

0.1uF

CC-

Chi

0.01uF

Rgen

Ri

Vgen

C12

Vin

Vout

2N7000

2N2222

CS-

Chi

Figure 1. Two-stage amplifier circuit.

5.1. DC Bias

Begin by designing the DC bias for the amplifier stages. Note that the location and value

of the capacitors do not affect the biasing, so the values you calculate here will be valid

for all three amplifier designs. Once you have designed the DC bias, use the transistor

characteristics for the 2N2222 and 2N7000 transistors to determine the transistor

parameters for where you are operating. Note that there is no single correct answer and

that your design may differ significantly from your colleagues. You must show all work

and walk through all calculations.

Component Values Amplifier Parameters Voltages and Currents

RG1, RG2 Beta ac and dc (2N2222) Vce, Vbe, Ve

RD, RS r, ro, (2N2222) Ib, Ic

RB1, RB2 VTN, ro, gm (2N7000) VGS, VDS, VS

Re ID

Table 3. DC Bias and Amplifier Parameters

5.2. AC Analysis

Once you have designed the bias network and determined the transistor parameters, you

are ready to begin the ac analysis. Table 4 shows all of the values you need to calculate.

Be sure to show all work. You may use equations given in the lab lecture, class lecture,

or from a textbook (i.e., you do not need to derive the voltage gain). Be sure you

understand how to use the equations, thoughif assumptions are included, you must

April 15, 2014 4

state these and show that you meet them. Do not simply copy equations out of the book

and use them, because they probably wont work.

To determine the capacitor value for C12, by seting the time constant to a frequency that

is one tenth the low cutoff frequency. Determine the capacitor value for CC-Chi, and CS-

Chi by setting each time constant to a frequency of 100kHz. Use the Short-Circuit Time

Constant method to determine the capacitor value.

Component

Values

Amplifier Parameters Voltages, Currents, and

Power

Cin Overall Voltage Gain vin

Cout Overall Current Gain vout

Cs Overall Power Gain (in dB) iin

C12 Overall Low Frequency

Cutoff

iout

CC-Chi Overall High Frequency

Cutoff

pin

CS-Chi Overall Input Resistance pout

Overall Output Resistance

Table 4. Small Signal (ac) Amplifier Parameters

5.3. Computer-aided Analysis

Once you have completed your amplifier design, use PSpice or LTspice to analyze their

performance. Generate the following plots for each amplifier design: include PSpice

schematics.

(a) A time-domain plot of the input and output, with the output voltage of 3Vpk-pk or

greater at 10 kHz. The output should not have any distortion or clipping. Calculate

the midband gain and indicate it on the plot. Compare this to your calculated

values.

(b) An FFT of your time-domain waveform. Circle and indicate the height of any strong

harmonics, in dB relative to your fundamental frequency at 10 kHz.

(c) A frequency sweep of the amplifier from 10 Hz to 1 MHz. Indicate the high and low

frequencies on the plot (these should correspond to the half-power, or -3dB points).

Compare these to your calculated values.

5.4. Prelab Questions

(a) What would happen if you swapped the order of the transistors?

(b) Could you use a CE amplifier in place of a CS amplifier, and/or a CD amplifier in

place of a CC amplifier? Why or why not?

(c) What would be the advantages and disadvantages of replacing the CC output

stage amplifier with a push-pull amplifier stage?

April 15, 2014 5

6. Lab Procedure

6.1. Construct the amplifier shown in Figure 1. Remember that RGEN is internal to the

function generator and the shunt Ri = 10k. Also remember to use two emitter resistors of

approximately the same value, as shown in the schematic. Record the values of the bias

network resistors and the capacitors you used in the circuit.

6.2. Measure the following values:

(a) Q-point: Vce, Vbe, VE, VC, VB, and Ic (2N2222), and VDS, VGS, VS, VD, VG, and

ID (2N7000).

(b) Voltage gain each stage

(c) Overall voltage, current, and power gains.

(d) Maximum undistorted peak-to-peak output voltage (Vout).

(e) Overall Input and output resistance.

(f) Low and high cutoff frequencies (half power point).

Recall that input impedance is given by Rin = vin/iin , output impedance is given by Rout =

(vocvload)/iout, voltage gain is given by Av = vout/vin , and current gain is given by Ai = iout/iin.

Additionally, plot the following:

(a) Input and output waveform at the maximum undistorted value.

(b) FFT showing the fundamental and first few harmonics.

(c) Frequency response from 10 Hz to 1 MHz (set the input voltage to a value that

does not cause distortion across the entire passband of the amplifier).

6.3. Postlab Questions

(a) Compare the voltage gains of each stage AV1 and AV2 to the voltage gains of the

previous labs. Why are the gains the same or different?

(b) For the cascade configuration, can the output impedance of the first stage be

matched to the input impedance of the second stage when the cascade amplifier

is a CS-CC?

April 15, 2014 6

ECE 3274

Two-Stage Amplifier Lab

Data Sheet

Name: Lab Date: Bench:

Partner:

Remember to include units for all answers and to label all printouts. There are a total of

three (3) printouts in this lab. Only one set of printouts is required per group.

6.1. Component Values

RG1: RG2: RS: RD:

RB1: RB2: RE: Ri: 1K

6.2. Two-stage amplifier. There are three printouts here.

Capacitor Values: Cin: Cout: CS-Chi:

Cs: C12: CC-Chi:

Q-Point: Vce: Vbe: IC:

VE: VB: VC:

VGS: VDS: ID:

VS: VG: VD:

Gain each stage: Av CS Av CC

Overall Gain: Voltage: Current: Power:

Voltage Output Vpp: Max:

Resistance: Input Output

Frequency

Response:

Low: High: BW:

6.3 Postlab Questions

(a) Compare the voltage gains of each stage AV1 and AV2 to the voltage gains of the

previous labs. Why are the gains the same or different?

(b) For the cascade configuration, can the output impedance of the first stage be

matched to the input impedance of the second stage when the cascade amplifier

is a CS-CC?

Vous aimerez peut-être aussi

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- A1Document2 pagesA1ty391988Pas encore d'évaluation

- Full Version HereDocument2 pagesFull Version Herety391988Pas encore d'évaluation

- List 3: Nilsson, 4Document1 pageList 3: Nilsson, 4ty391988Pas encore d'évaluation

- Full Version HereDocument4 pagesFull Version Herety391988Pas encore d'évaluation

- Multi Stage AmpsDocument3 pagesMulti Stage Ampsty391988Pas encore d'évaluation

- The Study of Hybrid Parameters of A Transistor: FeaturesDocument1 pageThe Study of Hybrid Parameters of A Transistor: Featuresty391988Pas encore d'évaluation

- DataSheet 2n222Document6 pagesDataSheet 2n222evhyajahPas encore d'évaluation

- BDocument1 pageBty391988Pas encore d'évaluation

- The Study of Hybrid Parameters of A Transistor: FeaturesDocument1 pageThe Study of Hybrid Parameters of A Transistor: Featuresty391988Pas encore d'évaluation

- Actual Test 4n4 TOEIC 520 - Split - 50Document1 pageActual Test 4n4 TOEIC 520 - Split - 50ty391988Pas encore d'évaluation

- Section 6 Appendix Euclidean AlgorithmDocument9 pagesSection 6 Appendix Euclidean Algorithmty391988Pas encore d'évaluation

- BDocument1 pageBty391988Pas encore d'évaluation

- BDocument1 pageBty391988Pas encore d'évaluation

- BDocument1 pageBty391988Pas encore d'évaluation

- Omni 2Document1 pageOmni 2ty391988Pas encore d'évaluation

- According To The WomaDocument1 pageAccording To The Womaty391988Pas encore d'évaluation

- Jim Read Split 8Document30 pagesJim Read Split 8ty391988Pas encore d'évaluation

- According To The WomaDocument1 pageAccording To The Womaty391988Pas encore d'évaluation

- Estimated Costs For Georgia University 2005-06: Questions 191-195 Refer To The Following Information and EmailDocument1 pageEstimated Costs For Georgia University 2005-06: Questions 191-195 Refer To The Following Information and Emailty391988Pas encore d'évaluation

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (120)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Fast Nearly ML Estimation of The Parameters of Real or Complex Single Tones or Resolved Multiple TonesDocument9 pagesFast Nearly ML Estimation of The Parameters of Real or Complex Single Tones or Resolved Multiple Tonessaygun123Pas encore d'évaluation

- Manual MicroBass3Document5 pagesManual MicroBass3zhaihaijunPas encore d'évaluation

- Zytx (Taoxian) R (23oct15) PDFDocument26 pagesZytx (Taoxian) R (23oct15) PDFnabatmanPas encore d'évaluation

- Jm-137-Dca-Kit For Noaa Poes Apt: 137 MHZ Double Cross AntennaDocument8 pagesJm-137-Dca-Kit For Noaa Poes Apt: 137 MHZ Double Cross AntennaSasha PkhidenkoPas encore d'évaluation

- LDPC and Turbo Code Blind DetectionDocument3 pagesLDPC and Turbo Code Blind DetectionEyal LeizerovichPas encore d'évaluation

- E Terragridcom MSEDocument4 pagesE Terragridcom MSEthlsatheesh100% (1)

- DB - NoiseDocument81 pagesDB - Noisehappy girl100% (1)

- ADC + InterruptDocument43 pagesADC + InterruptResheta Ahmed SmrityPas encore d'évaluation

- TX ExciterDocument4 pagesTX ExciterRizky RahmawatiPas encore d'évaluation

- SPST-S&T-Telecom On Indian RailwaysDocument66 pagesSPST-S&T-Telecom On Indian RailwayslvsaruPas encore d'évaluation

- Mca 203Document3 pagesMca 203kola0123100% (1)

- Lte DCL App 030940 App-Std Lncme Le6Document273 pagesLte DCL App 030940 App-Std Lncme Le6Waqas AhmedPas encore d'évaluation

- Coaxial Cables: Types of Computer Network CablesDocument9 pagesCoaxial Cables: Types of Computer Network CablesedrisPas encore d'évaluation

- ADC Unit 1S1, S2, S3Document31 pagesADC Unit 1S1, S2, S3CHANDRAKANT TRIPATHI (RA2011053010028)Pas encore d'évaluation

- DB 420 Assembly Mounting InstructionsDocument2 pagesDB 420 Assembly Mounting InstructionsDaniel BelmontePas encore d'évaluation

- Far2117 27 37SDocument8 pagesFar2117 27 37Ssuper_mishukov100% (1)

- Global Navigation Satellite System: ScheduleDocument7 pagesGlobal Navigation Satellite System: ScheduleAboody AL-ghamdyPas encore d'évaluation

- Peerless SLS P830667Document1 pagePeerless SLS P830667Alexander ShivaPas encore d'évaluation

- Wireless Ommunication and Internet of ThingsDocument139 pagesWireless Ommunication and Internet of Thingsrohan bawadkarPas encore d'évaluation

- Cavity Resonators: Microwave Engineering EE 172Document20 pagesCavity Resonators: Microwave Engineering EE 172alberteinstein407Pas encore d'évaluation

- Kathreinâ S Remote Electrical Tilt System RETDocument69 pagesKathreinâ S Remote Electrical Tilt System RETMojo CratPas encore d'évaluation

- Etisalat FTTH (Released)Document9 pagesEtisalat FTTH (Released)Luc Vu TienPas encore d'évaluation

- 5G Signaling Analysis GuideDocument94 pages5G Signaling Analysis GuideJitendra Asati100% (1)

- 34 Lte Eran7.0 Icic FeatureDocument49 pages34 Lte Eran7.0 Icic FeaturePhan AnPas encore d'évaluation

- How To Program An Arduino Based Metal DetectorDocument18 pagesHow To Program An Arduino Based Metal DetectorSarah HadjadjPas encore d'évaluation

- NH360QM DG 2XRDocument3 pagesNH360QM DG 2XRJosueMancoBarrenecheaPas encore d'évaluation

- IC7410 - I Nstruction ManualDocument124 pagesIC7410 - I Nstruction ManualLoco Soy Loco SoyPas encore d'évaluation

- Nova233 Gen 2 Data SheetDocument2 pagesNova233 Gen 2 Data SheetThan Htun OoPas encore d'évaluation

- Kratos DataDefender Network Packet Loss Protection Data SheetDocument2 pagesKratos DataDefender Network Packet Loss Protection Data SheetarzeszutPas encore d'évaluation

- AntennaDocument73 pagesAntennaShubham ChaudharyPas encore d'évaluation