Académique Documents

Professionnel Documents

Culture Documents

6ES5998-2PR42 Programmieranleitung CPU928B-3UB21 S OCR PDF

Transféré par

deja_vu824600 évaluation0% ont trouvé ce document utile (0 vote)

179 vues562 pagesTitre original

6ES5998-2PR42_Programmieranleitung_CPU928B-3UB21_s_OCR.pdf

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

179 vues562 pages6ES5998-2PR42 Programmieranleitung CPU928B-3UB21 S OCR PDF

Transféré par

deja_vu82460Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 562

SIEMENS

Instrucciones para el uso del

manual, lndice

Introduccin

Programa de usuario

Procesamiento del programa

S5-135U

CPU 928B-3UB21

Estados operativos y niveles de

procesamiento

Tratamiento de interrupciones y

errores

Funciones especiales integradas

Instrucciones de programacin

Mdulo de datos ampliado DX O

Ocupacin y organizacin de la

memoria

Accesos a la memoria a travs

de direcciones absolutas

Comunicacin en

multiprocesamiento

Interfaces y funciones del aparato

de programacin

Anexo

Bibliografa

Lista de abreviaturas

Glosario, lndice alfabtico

La lista de operaciones

CPU 928/CPU 928B/CPU 948,

no de re f. 6ES5 997-3UA43

est incluida en este manual.

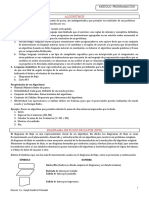

Consignas de Este manual contiene las informaciones necesarias para la seguridad personal as como para la pre-

seguridad para el vencin de daos materiales. Las informaciones estn puestas de relieve mediante seales de pre-

usuario caucin. Las seales que figuran a continuacin representan distintos grados de peligro:

A

Peligro

Significa que, si no se adoptan las medidas preventivas adecuadas, se producir la muerte,

o bien lesiones corporales graves o daos materiales considerables.

A

Precaucin

Significa que, si no se adoptan las medidas preventivas adecuadas, puede producirse la muerte,

lesiones corporales graves o daos materiales considerables.

A

Cuidado

Significa que, si no se adoptan las medidas preventivas adecuadas, pueden producirse lesiones cor-

porales o daos materiales.

Nota

Se trata de una informacin importante, sobre el producto o sobre una parte determinada del manual,

sobre la que se desea llamar particularmente la atencin.

Personal cualificado La puesta en funcionamiento y el servicio del equipo slo deben ser llevados a cabo conforme a lo

descrito en este manual.

Slo est autorizado a intervenir en este equipo el personal cualificado. En el sentido del manual se

trata de personas que disponen de los conocimientos tcnicos necesarios para poner en funciona-

miento, conectar a tierra y marcar los aparatos, sistemas y circuitos de acuerdo con las normas estn-

dar de seguridad.

Uso conforme Considere lo siguiente:

A

Precaucin

El equipo o los componentes del sistema slo se podrn utilizar para los casos de aplicacin previstos

en el catlogo y en la descripcin tcnica, y slo con los equipos y componentes de proveniencia

tercera recomendados y homologados por Siemens.

El funcionamiento correcto y seguro del producto presupone un transporte, un almacenamiento, una

instalacin y un montaje conforme a las prcticas de la buena ingeniera, as como un manejo y un

mantenimiento rigurosos.

Marca registrada SIMATIC@ y SINEC@ son marcas registradas por SIEMENS AG

Los restantes nombres y designaciones contenidos en el presente documento pueden ser marcas regis-

tradas cuya utilizacin por terceros para sus propiosfines puede violar los derechos de los proprietarios.

Copyright O Siemens AG 1996 All rights reserved

Ladivulgacin y reproduccin de este documento, ascomo el uso y

lacomunicacindesu contenido, no estn autorizados,anoserque

se obtenga el consentimiento expreso para ello. Los infractores

quedan obligados a la indemnizacin de los daos. Se reservan

todos los derechos, en particular para el caso de concesin de

patentes o de modelos de utilidad.

Siemens AG

Grupo Automatizacin

Divisin Sistemas de Automatizacin Industriales

Postfach 4848, D-90327 Nrnberg

Exencin de responsabilidad

Hemos probado el contenidodeesta publicacin con laconcordan-

ciadescrita para el hardware y el software. Sin embargo, es posible

que se den algunas desviaciones que nos impiden tomar garanta

completa de esta concordancia. El contenido de esta publicacin

est sometido a revisiones regularmente y en caso necesario se

incluyen las correcciones en la siguiente edicin. Agradecemos

sugerencias.

O Siemens AG 1996

Sujeto a cambios sin previo aviso.

Siemens Aktiengesellschaft 6 ~ ~ 5 9 9 8 - 2 ~ ~ 4 2

lnstrucciones para el uso del manual

Campo de

aplicacin

Estas instrucciones de programacin describen las funciones de la

CPU 928B-3UB21 as como el software de sistema correspondiente.

lnstrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

lnstrucciones Dara el uso del manual

Informaciones El captulo 1 contiene informaciones acerca de los campos de aplicacin del

referentes a los autmata programable S5-135U con la CPU 928B.

distintos Explica el funcionamiento tpico de una CPU y el modo en que est estructurado

captulos un programa de CPU.

Este captulo da adems algunos consejos sobre cmo proceder a la hora de

programar y tambin informa sobre los datos caractersticos importantes que

posee la CPU 928B-3UB21.

Si ya ha trabajado anteriormente con la CPU 928B-3UB12 y desea saber en qu

aspectos se diferencia la CPU 928B-3UB21, consulte este captulo.

El captulo 2 describe los componentes que integran un programa de usuario

STEP 5 y el modo en que puede ser estructurado.

El captulo 3 se dirige a aquellos lectores que no tengan gran experiencia en la

aplicacin del lenguaje de programacin STEP 5. Introduce al lector en los

conocimientos bsicos de la programacin STEP 5 y describe las operaciones

STEP 5 ms detalladamente (con ejemplos).

El apartado 3.5 puede servir de apartado de consulta a aquellos lectores que

tengan muy buenos conocimientos del sistema y que no les basten las

informaciones que figuran en la lista de operaciones, referentes a una operacin

STEP 5 concreta.

El captulo 4 ofrece una visin de conjunto de los distintos estados operativos y

niveles de procesamiento del programa de la CPU 928B. Adems da

informaciones detalladas acerca de los distintos modos de arranque y los

consiguientes mdulos de organizacin, en los que se podr programar el

programa en cuestin para los distintos modos de arranque.

Tambin se exponen las caractersticas en las que se distinguen los niveles de

procesamiento: "procesamiento cclico", "procesamiento controlado por tiempo"

y "procesamiento controlado por alarma", as como los mdulos disponibles para

el programa de usuario.

El captulo 5 explica cmo pueden evitarse errores a la hora de planificar y

programar los programas STEP 5.

Tambin informa acerca de las ayudas que ofrece el programa de sistema a fin de

diagnosticar errores y de cmo reaccionar ante stos. Adems se indican los

mdulos en los que se pueden programar reacciones ante determinados errores.

El captulo 6 expone las funciones especiales integradas del programa de

sistema. Asimismo explica en qu campos se pueden aplicar las funciones

especiales y cmo se llaman y parametrizan los OBs de funciones especiales.

Tambin indica cmo detectar errores durante el procesamiento de una funcin

especial y cmo tratarlos mediante el programa.

lnstrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

lnstrucciones Dara el uso del manual

El captulo 7 explica en qu casos se puede utilizar el mdulo de datos DX 0, cmo

est estructurado y cul es el significado de los distintos parmetros DX O. Por medio

de ejemplos el usuario aprender cmo generar un mdulo de datos DX O o cmo

parametrizarlo mediante una mscara.

El captulo 8 sirve de captulo de consulta a los usuarios expertos en este

sistema. En l se encuentran explicaciones acerca de la organizacin de la

memoria de la CPU 928B y de algunas palabras de datos del sistema que

contienen informaciones a las que puede acceder el usuario.

Adems, se indica cmo activar y desactivar la proteccin del software de la

CPU mediante una palabra de datos del sistema.

El captulo 9 tambin est dirigido a los usuarios que tengan experiencia en este

sistema: aqu podrn consultar cmo acceder mediante direcciones absolutas a

datos que se encuentran en determinadas zonas de memoria.

El captulo 10 explica en primer lugar cundo utilizar el modo multiprocesador y

qu posibilidades de intercambio de datos existen entre las CPUs y los CPs

(procesadores de comunicacin).

Tambin explica lo que se debe hacer y tener en cuenta a la hora de programar en

modo multiprocesador.

Finalmente da instrucciones detalladas con ejemplos de aplicacin para el

intercambio de grandes cantidades de datos en modo multiprocesador

(comunicacin en multiprocesamiento).

El captulo 11 informa sobre cmo acoplar la CPU a un aparato de programacin

(PG) y sobre las ayudas que ofrece el software del aparato de programacin a fin

de comprobar el programa STEP 5.

El anexo A contiene una comparacin de los datos tcnicos caractersticos de las

CPUs 928A, 928 B y 948.

El anexo B contiene una lista con bibliograa complementaria.

El anexo C es una ayuda para orientarse a travs del manual; contiene una lista

de las abreviaturas utilizadas as como un ndice alfabtico.

lnstrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

lnstrucciones Dara el uso del manual

Ayudas de Apartados de segundo orden

orientacin en

el manual Los apartados de segundo orden (p.ej. 4.3) se destacan mediante ttulos en

negrita al comienzo de una pgina y aparecen en el ndice del captulo.

Notas maeinales

Las notas marginales que aparecen en negrita del lado izquierdo del texto

permiten localizar rpidamente las descripciones tcnicas.

Las informaciones importantes se destacan de este modo.

l

Tablas de consulta

Tabla 1-1 Operaciones binarias de combinacin

Ejemplos

Operacin

U

O

Los ejemplos, sean largos o cortos -tambin de varias pginas - estn destacados

por un margen reticulado. En los ejemplos que abarquen varias pginas, las pginas

siguientes a la primera estn claramente distinguidas.

Modo de representacin AWL

Operando

E 0.0 a 127.7

......

lnstrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Funcin

Combinacin AND con consulta si el estado lgico es "1"

Combinacin OR con consulta si el estado lgico es "1"

de una entrada en el PAE

. . . . . . . .

lndice

Introduccin .................................................................. 1-1

Campos de aplicacin del S5-135U con la CPU 928B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Funcionamiento tpico de una CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Los programas de una CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Programa de sistema . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Programa de usuario . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . De qu operandos dispone el programa de usuario? 1-9

Accesos a zonas de operandos y de memoria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Cmo proceder a la hora de programar? 1-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Herramientas de programacin 1-16

Qu novedades presenta la CPU 928B.3UB21? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

Programa de usuario ........................................................... 2-1

Lenguaje de programacin STEP 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Modos de representacin KOP. FUP y AWL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Programacin estructurada . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Operaciones STEP 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Representacin numrica . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Mdulos STEP 5 y su registro en la memoria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Mdulos de programa. de organizacin y de pasos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Mdulos de organizacin para interfaces con el usuario . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

Mdulos de organizacin de funciones especiales . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

Mdulos de funciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

Estructura de los mdulos de funciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

Programacin de los mdulos de funciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Llamada y parametrizacin de mdulos de funciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

Mdulos de funciones especiales . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

Mdulos de datos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

Crear mdulos de datos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

Abrir mdulos de datos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

Mdulos de datos especiales . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-39

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Procesamiento del programa .................................................... 3-1

Principios fundamentales del procesamiento del programa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Organizacin del programa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Almacenamiento de mdulos de programa y de datos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Procesamiento del programa de usuario . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Definiciones terminolgicas en cuanto al procesamiento del programa . . . . . . . . . . . . . . . . . . . 3-11

Operaciones STEP 5 con ejemplos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

Operaciones bsicas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

Ejemplos de programacin en los modos de representacin AWL. KOP y FUP . . . . . . . . . . . . 3-32

Operaciones complementarias . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-47

Operaciones de organizacin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-54

Operaciones semforo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-67

Estados operativos y niveles de procesamiento ..................................... 4-1

Introduccin y resumen sinptico . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Niveles de procesamiento del programa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Estado operativo STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Caractersticas e indicadores del estado operativo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Solicitar y ejecutar un BORRADO TOTAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

Estado operativo ARRANQUE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

NUEVO ARRANQUE MANUAL Y AUTOMATICO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

REARRANQUE MANUAL Y AUTOMATICO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Comparativa de los modos de arranque . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

Interfaces con el usuario para el arranque . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

Interrupciones en el ARRANQUE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

Estado operativo RUN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

Procesamiento cclico del programa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

Procesamiento controlado por tiempo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

Alarma de reguladores: procesamiento de reguladores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-35

Alarma de proceso: procesamiento controlado por alarmas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-36

Procesamiento anidado de programas controlados por alarma o por tiempo . . . . . . . . . . . . . . . 4-39

Tratamiento de interrupciones y errores ........................................... 5-1

Errores frecuentes en el programa de usuario . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Informaciones sobre errores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Bits de control y pila de interrupciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Bits de control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Contenido de la pila de interrupciones (USTACK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Ejemplo de diagnstico de errores mediante USTACK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

Tratamiento de errores mediante mdulos de organizacin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ErroresenelARRANQUE 5-25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DBO-FE (error DB O) 5-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DB1-FE (error DB 1) 5-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DB2-FE (error DB 2) 5-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . DXO-FE (error DX O DX 2) 5-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . MOD-FE (error de Memory Card) 5-31

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Errores en RUN y en el ARRANQUE 5-32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . BCF (error en cdigo de instruccin) 5-34

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . LZF (error en tiempo de ejecucin) 5-37

ADF (error de direccionamiento) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . QVZ (retardo en acuse de recibo) 5-46

ZYK (error de tiempo de ciclo) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-48

WECK-FE (colisin de alarmas temporizadas) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . REG-FE (error de regulador) 5-50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ABBR (aborto) 5-52

FE-3 (errores de comunicacin) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-53

.................................................. Funciones especiales integradas 6-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Introduccin 6-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 110: Acceso al byte indicador 6-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 11 1: Borrar AKKU 1.2. 3 y 4 6-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 1121113: AKKU rol1 up1AKKU rol1 down 6-9

. . . . . . . . . . . . . . . . . . . . . . . . . . OB 120: Activarldesactivar "bloquear alarmas conjuntamente" 6-11

OB 121: Activarldesactivar "bloquear alarmas temporizadas individualmente" . . . . . . . . . . . . . 6-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . OB 122: Activaddesactivar "retardar alarmas conjuntamente" 6-16

. . . . . . . . . . . . . . OB 123: Activarldesactivar "retardar alarmas temporizadas individualmente" 6-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 150: Ajustadleer la hora del sistema 6-23

OB 151: Ajustarfleer la hora para la alarma temporizada controlada por reloj . . . . . . . . . . . . . . 6-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 152: Estadstica de ciclo 6-35

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 153: Ajustadleer la hora para la alarma de retardo 6-42

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 160 a 163: Bucles contadores 6-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 170: Leer pila de mdulos (BSTACK) 6-47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 180: Acceso variable a mdulos de datos 6-52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 181: Comprobar mdulos de datos (DBPX) 6-56

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 182: Copiar zona de datos 6-58

............................. OB 185 : Activaddesactivar la proteccin contra escritura 6-61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 186: Comprimir memoria 6-62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . OB 1901192: Transferir marcas a un mdulo de datos 6-63

. . . . . . . . . . . . . . . . . . . . . . . . . . OB 1911193: Transferir bloques de datos a la zona de marcas 6-65

. . . . . . . . . . . . . . . . . . . . . . . . OB 200 y OB 202 a 205: Comunicacin en multiprocesamiento 6-70

Instrucciones de programacin CPU 9288-311821

C79000-G8578-C870-01

lndice

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.24 OB 216 a 218: Accesos a pginas 6-71

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.24.1 OB 216: Escritura en pgina 6-74

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.24.2 OB 217: Lectura de pgina 6-76

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.24.3 OB 218: Ocupacin de pgina 6-78

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.24.4 Ejemplo de programacin 6-80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.25 OB 220: Ampliacin del signo 6-82

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.26 OB 221: Ajustar el tiempo de supervisin de ciclo 6-83

6.27 OB 222: Nuevo arranque del tiempo de supervisin de ciclo . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.28 OB 223: Comparar los modos de arranque 6-84

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.29 OB 224: Transferir marcas de acoplamiento en bloques 6-85

. . . . . . . . . . . . . . . . . . . . 6.31 OB 228: Leer la informacin de status de un nivel de procesamiento 6-87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.32 OB 230 a 237: Funciones para FBs estndar 6-89

. . . . . . . . . . . . . . . . . . . 6.33 OB 240 a 242: Funciones especiales para registros de desplazamiento 6-90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.34 OB 240: Inicializar registro de desplazamiento 6-94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.35 OB 241: Procesar registro de desplazamiento 6-97

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.36 OB 242: Borrar registro de desplazamiento 6-98

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.37 OB 250125 1 : Regulacin/Algoritmo PID 6-99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.37.1 Descripcin de las funciones del regulador PID 6-99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.37.2 Algoritmo PID 6-101

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.38 OB 250: Inicializar algoritmo PID 6-106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.39 OB 251: Procesar algoritmo PID 6-107

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6.40 OB 2541255. DesplazarJduplicar mdulos de datos 6-113

................................................. 7 Mdulo de datos ampliado DX O 7-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7.1 Aplicacin 7-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7.2 Estructura del DX O 7-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7.3 Parmetros del DX O 7-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7.4 Ejemplos de parametrizacin 7-10

.......................................... 8 Ocupacin y organizacin de la memoria 8-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8.1 Estructura de la zona de memoria 8-2

. . . . . . . . . . . . . . . . . . . . . . . . . . 8.2 Distribucin de la zona de direcciones de la CPU 928B.3UB21 8-3

8.2.1 Distribucin de la zona de direcciones de la RAM de sistema . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

8.2.2 Distribucin de la zona de direcciones de la periferia . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

. . . . . . . . . . . . . . . . . . . . . . . . . 8.3 Organizacin de la memoria de usuario de la CPU 928B.3UB21 8-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8.3.1 Cabezas de mdulos en la memoria de usuario 8-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . 8.3.2 Listas de direcciones de mdulos en el mdulo de datos DB O 8-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8.3.3 Zona BA/BB 8-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8.3.4 Zona BS/BT 8-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8.3.5 Ocupacin de los bits de las palabras de datos de sistema 8-16

Instrucciones de programacin CPU 9288-311821

C79000-G8578-C870-01

.............................. 9 Accesos a la memoria a travs de direcciones absolutas 9-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Introduccin 9-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . Accesos a la memoria a travs de la direccin de AKKU 1 9-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . LIRRIR: Cargaltransferencia indirecta de registros de 16 bits 9-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Ejemplos de aplicacin de registros

9-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Transferir bloques de memoria 9-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Ejemplo de transferencia de bloques de memoria 9-19

Operaciones con el registro base de direcciones (registro BR) . . . . . . . . . . . . . . . . . . . . . . . . . . 9-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Operaciones de transferencia entre registros 9-25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Accesos a la memoria local 9-27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Accesos a la memoria global 9-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Accesos a la memoria de pginas 9-31

...................... 10 Modo multiprocesador y comunicacin en multiprocesamiento 10-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.1 Modo multiprocesador 10-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.1.1 Intercambio de datos a travs de marcas de acoplamiento 10-4

10.1.2 Asignacin de periferia y marcas de acoplamiento en modo multiprocesador (DB 1) . . . . . . . . 10-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.1.3 Cmo se crea el mdulo de datos DB l ? 10-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.2 Comunicacin en multiprocesamiento 10-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.2.1 Cmo se identifica el emisor y el receptor? 10-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.2.2 Por qu se almacenan datos de forma intermedia? 10-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.2.3 Cmo se procesa y administra la memoria intermedia? 10-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.2.4 Aspectos a tener en cuenta durante el arranque del sistema 10-20

. . . . . . . . . . . . . . . . . . . . 10.2.5 Lo que debe tenerse en cuenta al llamar a los OBs de comunicacin 10-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.2.6 Cmo se parametrizan los OBs de comunicacin? 10-22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.2.7 Cmo se evalan los parmetros de salida? 10-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.3 Tiempos de ejecucin de los OBs de comunicacin 10-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.4 Funcin INICIALIZAR (OB 200) 10-30

10.4.1 Funcin 10-30

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.4.2 Parmetros de llamada 10-32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.4.3 Parmetros de entrada 10-33

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.4.4 Parmetros de salida 10-36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.5 Funcin EMITIR (OB 202) 10-38

10.5.1 Funcin 10-38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.5.2 Parmetros de llamada 10-38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.5.3 Parmetros de entrada 10-39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.5.4 Parmetros de salida 10-41

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.6 Funcin TEST DE EMISION (OB 203) 10-43

10.6.1 Funcin 10-43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.6.2 Parmetros de llamada 10-43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.6.3 Parmetros de entrada 10-43

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.6.4 Parmetros de salida 10-44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.7 Funcin RECIBIR (OB 204) 10-45

10.7.1 Funcin 10-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.7.2 Parmetros de llamada 10-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.7.3 Parmetros de entrada 10-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10.7.4 Parmetros de salida 10-46

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

10.8 Funcin TEST DE RECEPCION (OB 205) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-48

10.8.1 Funcin 10-48

10.8.2 Parmetros de llamada . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-48

10.8.3 Parmetros de entrada . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-48

10.8.4 Parmetros de salida . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-49

10.9 Aplicaciones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-50

10.9.1 Llamada a los OBs de funciones especiales por medio de mdulos de funciones . . . . . . . . . . 10-50

10.9.2 Transferencia de mdulos de datos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-58

10.9.3 Ampliacin de la zona de marcas de acoplamiento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-64

................................ 11 Interfaces y funciones del aparato de programacin 11-1

11.1 Panormica . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

11.2 Funciones del aparato de programacin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

11.2.1 Informacin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.2.2 Funciones de memorizacin y transferencia . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.2.3 Test del programa . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7

11.3 Actividades en los puntos de control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . 11.4 Acoplamiento PG . AG a travs de la 1" 2" interfaz serie 11-16

11.5 Funcionamiento paralelo de dos interfaces serie de PG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-17

11.5.1 Puesta en funcionamiento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-19

11.5.2 Funcionamiento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-19

11.5.3 Ejecucin en determinados modos operativos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

A Anexo ........................................................................ A-1

A.l Comparacin de los tiempos de ejecucin de las CPUs 928.3UA21. 928B-3UB21 y 948 . . . . . A-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A.2 Identificadores de error A-5

A.3 Operaciones STEP 5 no disponibles en la CPU 928B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-13

A.4 Identificaciones de los niveles de procesamiento . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A.5 Ejemplo de "evaluacin de la pila USTACK" A-15

B Bibliografa ................................................................... B-1

C Lista de abreviaturas ........................................................... C-1

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

Resumen breve Este captulo contiene informaciones acerca de los campos de aplicacin del

autmata programable S5-135U con la CPU 928B y sobre su estructura interna.

Explica el funcionamiento tpico de una CPU y el modo en que est estructurado

un programa de CPU.

Tambin ofrece algunos consejos sobre cmo proceder a la hora de programar e

informa asimismo sobre los datos caractersticos importantes que posee la

CPU 928B (-3UB21).

Si ya ha trabajado anteriormente con la CPU 928B (-3UBll -3UB12) y desea

saber en qu aspectos se diferencia la CPU 928B (-3UB21), consulte el

captulo 1.8.

lndice del captulo

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Captulo

1.1

1.2

1.3

1.3.1

1.3.2

1.4

1.5

1.6

1.7

1.8

Tema

Campos de aplicacin del S5-135U con la CPU 928B

Funcionamiento tpico de una CPU

Los programas de una CPU

Programa de sistema

Programa de usuario

De qu operandos dispone el programa de usuario?

Accesos a zonas de operandos y de memoria

Cmo proceder a la hora de programar?

Herramientas de programacin

Qu novedades presenta la CPU 928B-3UB21?

Pgina

1-2

1-3

1-5

1-5

1-7

1-9

1-12

1-13

1-16

1-17

Introduccin

1.1 Campos de aplicacin del S5-135U con la CPU 928B

Clasificacin El autmata programable S5-135U pertenece a la familia de los controladores de

dentro de la memoria programable SIMATIC S5. Junto con la CPU 928B constituye un

familia potente multiprocesador para la automatizacin de procesos industriales (mando,

avisos, supervisin, regulacin, protocolizado).

Puede ser utilizado para componer mandos simples con seales binarias as como

para solucionar tareas de automatizacin complejas y de gran envergadura.

Campos de

aplicacin

El autmata programable S5-135U con la CPU 928B es especialmente apropiado

para:

Tareas que requieran un procesamiento ultrarrpido de bits y de palabras, es

decir, con mando y regulacin muy rpidos.

Ejemplos de este tipo de tareas se encuentran en los procesos rpidos de la

ingeniera mecnica (instalaciones embotelladoras, empaquetadoras y similares).

Tareas que requieran una comunicacin rpida con otras CPUs incorporadas

en el autmata programable en modo multiprocesador y con tarjetas CPs

(procesadores de comunicacin) (por ejemplo, conexiones con sistemas de

bus, visualizaciones, etc.).

Tareas de regulacin fciles de resolver con el software de regulacin R 64

as como para su mando y observacin a travs de imgenes estndar con el

sistema PMC.

Estructuras de automatizacin que requieran una comunicacin directa con

una computadora de control, otros autmatas programables o una impresora,

a travs de la segunda interfaz integrada o bien a travs de una conexin

SINEC L1.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

1.2 Funcionamiento tpico de una CPU

Funcionamiento Una CPU ofrece los siguientes modos de operacin:

de una CPU

1.

Procesamiento

controlado por alarma

Procesamiento cclico

2.

Procesamiento La mayor parte de los procesos que tienen lugar en una CPU se

cclico efectan de este modo. Como su propio nombre indica, en un ciclo continuo se

va repitiendo el mismo proceso una y otra vez.

O

Procesamiento

controlado por tiempo

El procesamiento cclico se divide en tres fases principales:

CPU

Proceso

Fase

1

2

3

Leer la imagen de

Entrada E 1.3

proceso de las entradas

Entrada E 1.4

Ejecucin

Todas las tarjetas de entrada asignadas a

la CPU son consultadas por el programa

de sistema y los valores ledos son

memorizados de forma intermedia en la

imagen de proceso de entradas (PAE).

Los valores que contiene la PAE son

procesados por el programa de usuario y

los valores a emitir son registrados en la

imagen de proceso de salidas (PAA).

El programa de sistema transfiere los

valores que contiene la PAA a las tarjetas

de salida asignadas a la CPU.

l I

' Entrada E 1.5

Evaluar las seriales de entrada,

definir las seriales de salida

Salida A 2.0

Emitir la imagen de

proceso de las salidas

Salida A 3.1

Salida A 4.7

I nst rucci ones d e pr ogr amaci n CP U 928B- 3UB21

C79000- G8578- C870- 01

Introduccin

Procesamiento Para procesos que requieran seales de control en intervalos de tiempo

controlado constantes se pueden procesar determinadas tareas de forma controlada por

por tiempo tiempo - adems de la ejecucin cclica - tales como funciones de supervisin

que no dependen de tiempo, en intervalos de segundos.

Procesamiento A una seal de proceso a la que se deba reaccionar con gran rapidez se le asigna una

controlado fase de procesamiento controlada por alarma. Por ejemplo, el usuario puede

por alarma activar en su programa una secuencia determinada mediante una alarma de proceso

disparada por una tarjeta que genere alarmas.

Procesamiento Los modos de procesamiento mencionados son tratados por la CPU segn su

segn prioridad grado de importancia. Este grado de importancia se denomina prioridad.

Puesto que es necesario reaccionar con rapidez ante un suceso de tiempo o

alarma, la CPU interrumpe el procesamiento cclico a fin de tratar estos sucesos.

De ah que el procesamiento cclico tenga una prioridad inferior a las dems.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

1.3 Los programas de una CPU

Introduccin El programa que contiene cada una de las CPUs se divide en

programa de sistema

Y

programa de usuario.

1.3.1 Programa de sistema

Panormica El programa de sistema organiza todas las funciones y procesos de la CPU que

no estn relacionados con una tarea de mando especfica (vase fig. 1-1).

Ejecutar arranque

al programa

A A ..nmmn.:..

in Establecer comunicacin Tratar errores

Establecer comunicacin

con PG

Fig. 1-1 Funciones del programa de sistema

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

Funciones Las funciones son las siguientes :

nuevo arranque y rearranque,

actualizacin de la imagen de proceso de las entradas y emisin de la imagen

de proceso de las salidas,

llamada a los programas cclico, procesado por tiempo y por alarma,

deteccin y tratamiento de errores,

administracin de la memoria,

comunicacin con el aparato de programacin,

comunicacin a travs de la segunda interfaz serie.

lnterfaces con el En determinados estados operativos y casos de error el usuario tiene la

usuario posibilidad de modificar el comportamiento de la CPU a travs de interfaces

especiales con el programa de sistema.

Ajuste por Los siguientes captulos, a excepcin del captulo 7, describen el

defecto del comportamiento preajustado del sistema en reacciones ante sucesos del

comportamiento proceso o errores. De acuerdo con el preajuste, la CPU pasa por ejemplo al

del sistema estado STOP cuando en caso de un error de cdigo de instruccin no est

cargado el correspondiente mdulo de organizacin de error.

Modificacin del El comportamiento del sistema puede ser modificado parametrizando el mdulo

ajuste de datos DX O.

por defecto En el captulo 7 se puede consultar cul es el comportamiento del sistema una

vez modificado el ajuste por defecto!

l) En funcionamiento con varias CPUs (modo multiprocesador) se incorporan otras funciones.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

1.3.2 Programa de usuario

Estructura La figura 1-2 muestra la estructura bsica de un programa de usuario de STEP 5.

Mdulos de

organizacin

OB

Operaciones

STEP 5

E 1 3 A 3 1

Mdulos de Mdulos de Mdulos de

programa funciones pasos

PB FBIFX SB

Operaciones Operaciones Operaciones

STEP 5 STEP 5 STEP 5

FB 8

SEGMENTO 1

NOMB. :TRANS

E 1 3

0005 :L EB 3

0006 :T MW 200

0007 :A DE 5

0008 :B MW 200

0009 :L DW O

OOOA :T AW 6

0006 :BE

Mdulos de cdigo

DB 1: KH=0101;

Datos estticos o dinmicos 2: KF = 1120:

(bits, bytes, palabras, palabras dobles)

3: KC = xy;

4: KY = 4.5;

5: KG =

6: KM =

7:

Mdulos de datos

DX 1: KH = FFFF;

Datos estticos o dinmicos

2: KH = FFFF;

3: KH = FFFF:

(bits, bytes, palabras, palabras dobles) 4: KH = FFFF:

5: KH = FFFF:

6: KH = FFFF:

7:

Fig. 1-2 Estructura de un programa de usuario STEP 5

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

Funciones El programa de usuario contiene todas las funciones necesarias para procesar una

tarea de mando especfica. Estas funciones - clasificndolas de forma

aproximada - pueden ser asignadas directamente a las interfaces que el programa

de sistema pone a disposicin para los distintos modos de procesamiento:

Almacenamiento En la CPU 928B se dispone de dos zonas para grabar los mdulos:

del programa de

usuario La memoria de usuario: mx. 64 Kbyte

Modo de procesamiento

Nuevo arranque y

rearranque

Procesamiento cclico

Procesamiento controlado

por tiempo

Procesamiento controlado

por alarma

Reaccin ante errores

La memoria de usuario se encuentra en la tarjeta (CPU).

Funcin

Se crean las condiciones para que en caso de un nuevo

arranque del mando o un rearranque, el resto del

procesamiento pueda partir de un estado definido (p. ej.

prefijar seales con un valor determinado).

Procesamiento reiterativo de seales @. ej. combinacin

de seales binarias, lectura y evaluacin de valores

analgicos, definicin de seales binanas para la

emisin, emisin de valores analgicos)

Procesamientos especiales en funcin de tiempo bajo las

circunstancias que se indican:

-

ms rpido que el ciclo medio, en una escala de

tiempo mayor que el tiempo medio de ciclo,

-

en un tiempo regulable determinado

Reacciones especiales y rpidas ante determinadas

seales de proceso

Tratamiento de anomalas en el desarrollo habitual del

programa

La RAM de mdulos de datos (DB-RAM): mx. 46 Kbyte

La DB-RAM es una zona de memoria adicional que sirve para registrar

mdulos de datos. La DB-RAM se encuentra en la tarjeta (CPU).

lnterfaces con el Como interfaces con el programa de sistema se dispone de mdulos de

programa organizacin para los distintos modos de procesamiento.

de sistema

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

1.4 De qu operandos dispone el programa de usuario?

Panormica La CPU 928B ofrece las siguientes zonas de operandos para la programacin:

Imagen de proceso y periferia

Marcas (marcas M y marcas S)

Temporizadores/contadores

Mdulos de datos

Imagen de proceso de

las entradas y salidas

PAEIPAA

Zona de periferia

(zona P)

Caractersticas

El programa de usuario puede acceder muy deprisa a la imagen

de proceso, es decir, a los siguientes tipos de datos:

- bits,

- bytes,

- palabras,

- palabras dobles.

Tamao

128 byte para las

entradas y salidas

respectivamente

Zona de periferia ampliada

(zona Q)

Caractersticas

El programa de usuario puede acceder directamente a las tarjetas

de E/S (perifricas) a travs del bus S5.

Son vlidos los siguientes tipos de datos:

- bytes,

- palabras.

Tamao

256 byte para las

entradas y salidas

respectivamente

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Caractersticas

El programa de usuario puede acceder directamente a las tarjetas

E/S @erifricas) a travs del bus S5.

Son vlidos los siguientes tipos de datos:

- bytes,

- palabras.

Tamao

256 byte para las

entradas y salidas

respectivamente

Introduccin

Marcas M

Marcas S (zona

de marcas

ampliada)

Caractersticas

La zona de marcas es una zona de memoria a la que el programa

de usuario puede acceder con mucha rapidez con operaciones

correspondientes.

La zona de marcas debe utilizarse preferentemente para datos de

trabajo que se requieran frecuentemente.

Se puede acceder a los siguientes tipos de datos:

- bits,

- bytes,

- palabras,

- palabras dobles.

Los bytes de marcas pueden ser empleados como marcas de

acoplamiento para el intercambio de datos entre las CPUs en

modo multiprocesador (vase captulo 10).

Al final del ciclo, el programa de sistema actualiza las marcas de

acoplamiento a travs de una memoria intermedia del coordinador

o CPAP.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Tamao

2048 bits

(256 bytes)

Caractersticas

La CPU 928B contiene una zona de marcas adicional, la zona de

marcas S. Al igual que a las marcas M, el programa de usuario

puede acceder a esta zona a gran velocidad.

Sin embargo, las marcas S no se pueden emplear como

operandos actuales en las llamadas a mdulos de funciones y

tampoco como marcas de acoplamiento para el intercambio de

datos entre las CPUs.

Para poder utilizarlas es imprescindible disponer del software de

sistema del aparato de programacin "SS-DOS" a partir de la

versin 3.0 o "SS-DOSIMT "a partir de la versin 1.0.

Tamao

8192 bits

(1024 bytes)

Introduccin

Temporizadores T

Caractersticas

Contadores Z

Tamao

El programa de usuario carga temporizadores con un valor entre

10 ms y 9990 s. Mediante una operacin de arranque y a partir del

valor indicado, stas van decrementando en la escala de tiempo

establecida hasta alcanzar el valor O.

256

temporizadores

Palabras de datos en el

mdulo de datos actual

Caractersticas

El programa de usuario carga contadores con un valor inicial

(mx. 999) siendo incrementados o decrementados a continuacin.

Tamao

256 contadores

l)

Si existen mdulos de datos de una longitud mayor que 256 palabras slo se podr acceder a las

palabras de datos con un nmero > 255 con operaciones para accesos absolutos a la memoria

(vase captulo 9) o con el OB 180 (vase captulo 6).

Caractersticas

Un mdulo de datos contiene constantes y10 variables en formato

de byte, palabra o palabra doble. Con las operaciones STEP 5 el

usuario siempre puede acceder al mdulo de datos "actual"

(vase captulo 2.4).

Se puede acceder a los siguientes tipos de datos:

- bits,

- bytes,

- palabras,

- palabras dobles.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Tamao

256 palabras

1)

Introduccin

1.5 Accesos a zonas de operandos y de memoria

Introduccin Para acceder a estas zonas de operandos y a la totalidad de la memoria, las

instrucciones STEP 5 utilizan dos mecanismos diferentes:

direccionamiento relativo,

direccionamiento absoluto.

Direccionamiento La mayor parte de las instrucciones STEP 5 direcciona una clula de memoria de

relativo forma relativa al principio de una zona de operandos. Si se opera exclusivamente

con este tipo de instrucciones, las zonas de cdigo y de datos del programa de

usuario estn protegidas de sobreescrituras accidentales. A la vez, el programa de

usuario no depende de la CPU utilizada, siempre que sta disponga de la zona de

operandos correspondiente.

Direccionamiento Algunas instrucciones STEP 5 operan con direccionamiento absoluto. Estas

absoluto instrucciones permiten acceder a la totalidad de la zona de memoria. Solamente

pueden ser utilizadas en mdulos de funciones. Debido al riesgo de que se

destruyan datos slo debern utilizarse con la mayor cautela. Estas instrucciones

dependen de la CPU utilizada.

Mdulo de datos Los mdulos de datos son cargados por el programa de sistema en la memoria de

actual usuario o en la DB-RAM. Su posicin depender del espacio de memoria

disponible. La longitud se determina al programar el mdulo y puede variar.

El mdulo de datos actual es el mdulo cuya direccin inicial y longitud estn

depositadas en registros especiales. El registro se efecta con una operacin

STEP 5 especial para llamar o "abrir" mdulos de datos (como la pgina de un

libro). El programa de usuario slo puede acceder al mdulo de datos actual,

siempre que no se utilicen instrucciones con direccionamiento absoluto. Se

admiten los siguientes tipos de datos: bits individuales, bytes, palabras y palabras

dobles.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

1.6 Cmo proceder a la hora de programar?

Introduccin Si Vd. es un usuario experto, seguramente ya habr desarrollado un mtodo

propio para crear programas. Si es as, no necesitar leer este captulo.

A aquellos lectores que tengan menos experiencia en este tema queremos darles

algunos consejos sobre cmo proceder a la hora de esbozar, programar,

comprobar y poner en marcha su programa STEP 5.

Fases de

realizacin

La realizacin de un programa de mando STEP 5 puede ser dividida en tres fases:

1" Establecer el planteamiento tecnolgico.

2" Esbozar el programa.

3" Crear, comprobar y poner en marcha el programa.

Procedimiento La practica demostrara que es necesario repetir ciertos pasos ("procedimiento

recursivo recursivo"), por ejemplo, cuando al definir con mayor exactitud la tarea a

resolver el usuario se d cuenta de que precisa mayor nmero de seales.

Fase 1 Establecer el ~lanteamiento tecnolpico

La primera fase se puede dividir en los pasos siguientes:

1" Crear un diagrama de bloques aproximativo de las tareas de mando que

requiera el proceso.

2" Crear una lista de las seales de entradas y salidas que requiera la tarea

a resolver.

3" Perfeccionar el diagrama de bloques asignando a cada uno de los bloques

las seales y, dado el caso, las circunstancias de tiempo y10 estados de los

contadores que sean necesarios.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

Fase 2 -

Para la segunda fase se recomienda el siguiente procedimiento:

1" Sirvindose del diagrama de bloques esbozar los modos de procesamiento

necesarios para el programa (procesamiento cclico, procesamiento

controlado por tiempo, etc.) y asignar nombres a los OBs utilizados.

2" Dividir los modos de procesamiento en bloques tecnolgicos y10 funcionales.

3" Comprobar si se pueden asignar los bloques a un mdulo de programa o de

funciones y asignar nombres a los mdulos a utilizar (PB x, FB y etc.)

4" Determinar qu temporizadores, contadores y datos o memorias de

resultados se requieren.

5" Determinar las tareas para cada mdulo de cdigo previsto y los datos para

las marcas y mdulos de datos que se puedan necesitar.

Dibujar organigramas para los mdulos de cdigo.

Nota sobre la dimensin del procesamiento cclico

Es necesario tener en cuenta las siguientes condiciones a la hora de determinar

los modos de procesamiento.

El ciclo debe desarrollarse a una velocidad suficiente. Los estados del

proceso no deben modificarse ms deprisa de lo que pueda reaccionar la

CPU. De lo contrario podra perderse el control sobre el proceso.

El tiempo mximo de reaccin debe equivaler al doble del tiempo de ciclo.

El tiempo de ciclo est determinado por el procesamiento cclico del

programa de sistema y por la clase y dimensin del programa de usuario. Este

tiempo no suele ser constante, ya que, en determinadas circunstancias, el

programa de usuario cclico es interrumpido varias veces por los programas

controlados por tiempo y por alarma.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

Fase 3

En la tercera fase se deben ejecutar los pasos siguientes:

1" Determinar el modo de representacin para los mdulos de cdigo (KOP,

FUP o AWL, consultar a este respecto el captulo 2).

Tener en cuenta que los mdulos de funciones slo se pueden crear en el

modo de representacin AWL.

2" Programar todos los mdulos de cdigo y de datos (consultar a este respecto

el manual STEP 5).

3" Poner los mdulos sucesivamente en funcionamiento (para ello, a veces es

necesario programar por cada paso un OB 1 distinto que llame a los mdulos

de cdigo en cuestin):

- cargar elllos mdulo(s),

- comprobar elllos mdulo(s).

(Consultar a este respecto el manual del aparato de programacin y el

captulo 11.)

4" Si es seguro que todos los mdulos de cdigo se estn ejecutando

correctamente y que todos los datos se estn calculando y memorizando de

forma correcta, entonces puede ponerse en funcionamiento todo el programa.

Nota sobre la estrategia de comprobacin

Cul es el momento ms apropiado para hacer funcionar su programa por

primera vez en modo "caliente", es decir, con seales de entrada y sobretodo de

salida reales, lo deber decidir el usuario mismo, o bien un equipo de expertos.

Cuanto ms complejo sea el proceso y cuanto ms graves los riesgos de

seguridad tanto mayor deber ser la cautela a la hora de poner el programa en

funcionamiento.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

1.7 Herramientas de programacin

Aparatos de Para crear un programa de usuario propio se dispone de los aparatos de

programacin programacin PG 685, PG 710, PG 730, PG 750 y PG 770. En el catlogo ST 59

apropiados (bibliografa 190 puede consultarse la capacidad y las caractersticas de estos

aparatos.

Software

apropiado

Nota

- Para poder utilizar asimismo un PG 615 o un OP 3xx hay que registrar

en el dato de sistema BS 29 (vase captulo 8) la identificacin de la

CPU 922 (0010B). En este caso no se podrn utilizar las marcas S.

Si no se modifica la identificacin, los indicadores visualizados sern

errneos, por ejemplo, activando "SALIDA AG-INFOKJSTACK" (pila

de interrupciones). Asimismo, algunas funciones de test no sern posibles.

- En todos los PGs la funcin de test STATUS puede operar de forma

ilimitada solamente con tiempos de ciclo 2,5 s. En funcionamiento

paralelo de 2 interfaces de PG (vase captulo 11) este valor se reduce

a la mitad.

Los programas de usuario para autmatas programables SIMATIC S5

pueden ser creados

con el lenguaje de programacin STEP 5 en los modos de representacin

KOP/FUP/AWL:

Para ello se requiere el paquete de programacin STEP 5 junto con el

software de sistema STEP 51ST o STEP 51MT (descripcin vase 131 en el

apartado de bibliografa)

con un lenguaje de programacin de alto nivel:

Si el usuario est acostumbrado a escribir programas con un lenguaje de alto

nivel puede formular su programa STEP 5 para la CPU 928B tambin en el

lenguaje:

- SCL (vase 1121 en el apartado de bibliografa; el compilador SCL est

incluido en el software de PG "SS-DOSIMT" a partir de la versin 6).

Los programas para mandos secuenciales pueden crearse asimismo en

representacin grafica con el paquete de programacin GRAPH 5 (descripcin

vase 141 en el apartado de bibliografa).

Segn la tarea a resolver tambin se pueden incluir en el programa de usuario

mdulos de funciones estndar acabados. En el catlogo ST 57 (bibliografa /11/)

se puede consultar su capacidad y caractersticas.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

1.8 Qu novedades presenta la CPU 928B-3UB21?

Introduccin La versin -3UB21 de la CPU 928B ofrece las siguientes funciones y

caractersticas nuevas frente a la versin -3UB12:

Ocupacin de slots

RAM integrada

Memory Card

Estructuracin

del DB O

Aritmtica en coma

flotante

Estadstica de Las funciones de la estadstica de ciclo (OB 152) se han ampliado frente a la

ciclo ampliada versin -3UB12, habiendo aumentado p.ej. la resolucin de los temporizadores.

CPU 928B (-3UB21)

La CPU requiere slo un slot.

RAM integrada en la CPU (RAM interna)

con una capacidad de 64 KB

Memory Card SIMATIC (Flash EPROM)

Para la ejecucin del programa de usuario,

ste se copia de la Memory Card en la

RAM interna, quedando entonces

protegido contra escritura.

Slo despus del borrado total de la CPU

Mantisa de 24 bits

Proteccin del

software

CPU 928B (-3UB12)

La CPU requiere dos slots.

Cartuchos RAM enchufables, de diferente

capacidad

Cartuchos RAM enchufables

El programa de usuario permanece en el

cartucho EPROM para su ejecucin.

Despus de la conexin a la red o del

borrado total de la CPU

Mantisa de 16 24 bits

Programar la

Memory Card

Mediante el BS 139 se puede ajustar una contrasea para evitar que se lea o se

modifique el programa de usuario contenido en la CPU.

Para programar las Memory Cards Flash EPROM se requiere un PG 7xx con

S5DOS a partir de la versin 6.x. Un programa contenido en un cartucho de

memoria antiguo se puede reprogramar en una Memory Card.

Copiar el Si al efectuarse un borrado total est insertada una Memory Card Flash EPROM,

contenido de la el sistema operativo copia el contenido de la misma en la RAM interna y

Memory Card estructura el DB O. La Memory Card no se necesita ms durante el servicio

normal.

Modo EPROM Una vez copiado el contenido de la Memory Card (al efectuarse un borrado

total), la memoria de usuario (direcciones OOOOHa 7FFFH) se protege contra

accesos de escritura desde el PG y por parte del programa de usuario. Esto

equivale al comportamiento de una CPU 928B con cartucho EPROM insertado.

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Introduccin

Activar/desactivar La proteccin contra escritura se puede activar o desactivar directamente. A tal

la proteccin efecto existen dos posibilidades:

contra escritura

(OB 138) Activando/desactivando el BS 138 antes de finalizar el nuevo arranque de la

(OB 185) CPU (se evala al final del OB 20).

Llamando al OB 185 en el OB 20 (slo es posible allj se activa o desactiva

inmediatamente la proteccin contra escritura.

Comprimir Llamando al OB 186 se puede iniciar la funcin del aparato de programacin

mediante el (PG) que comprime la memoria mediante el programa de usuario. Puesto que

programa de dicha funcin podra colisionar con peticiones actuales del PG, el OB 186 y las

usuario funciones del PG se bloquean mutuamente.

(OB 186)

Estadstica de

ciclo La estadstica de ciclo ya no est acoplada al temporizador de vigilancia. Por

consiguiente, no se puede afectar redisparando la vigilancia del ciclo.

Como alternativa a la resolucin de 1 ms, mediante un nuevo nmero de

funcin se puede aumentar ahora la resolucin a 10 ms.

Accesos al byte El OB 110 se puede utilizar ahora con mayor frecuencia, puesto que el registro

indicador OB 11 0 de indicadores ya no se sobreescribe cuando se llama al bloque (como era el caso

anteriormente).

Comprobacin El sistema operativo comprueba ahora siempre la memoria EPROM al

de la memoria conectarse la alimentacin. Por lo tanto, ya no se requieren ni el OB 226 (Leer

EPROM palabra del sistema operativo) ni el OB 227 (Leer suma de verificacin). Dichos

mdulos existen an por motivos de compatibilidad, pero retornan slo el valor O.

Nuevos OBs con La CPU 928B-UB21 dispone de las siguientes funciones especiales nuevas:

funciones

especiales OB 134 para la instruccin: *D

OB 135 para la instruccin: /D

OB 136 para la instruccin: MOD

OB 139 para la instruccin: PUSH

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Programa de usuario

Resumen breve El captulo siguiente explica los componentes que integran un programa de

usuario STEP 5 para la CPU 928B y la forma en que puede ser estructurado.

lndice del captulo

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Captulo

2.1

2.1.1

2.1.2

2.1.3

2.1.4

2.1.5

2.2

2.2.1

2.2.2

2.3

2.3.1

2.3.2

2.3.3

2.3.4

2.4

2.4.1

2.4.2

2.4.3

Tema

Lenguaje de programacin STEP 5

Modos de representacin KOP, FUP y AWL

Programacin estructurada

Operaciones STEP 5

Representacin numrica

Mdulos STEP 5 y su registro en la memoria

Mdulos de programa, de organizacin y de pasos

Mdulos de organizacin para interfaces con el usuario

Mdulos de organizacin de funciones especiales

Mdulos de funciones

Estructura de los mdulos de funciones

Programacin de los mdulos de funciones

Llamada y parametnzacin de mdulos de funciones

Mdulos de funciones especiales

Mdulos de datos

Crear mdulos de datos

Abnr mdulos de datos

Mdulos de datos especiales

Pgina

2-2

2-2

2-4

2-5

2-6

2-10

2-14

2-16

2-19

2-21

2-22

2-24

2-26

2-31

2-33

2-35

2-36

2-39

Proarama de usuario

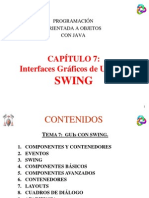

2.1 Lenguaje de programacin STEP 5

Introduccin Con el lenguaje de programacin STEP 5 se transforman las tareas de

automatizacin en programas ejecutables en autmatas programables

SIMATIC S5.

Con STEP 5 se pueden programar tanto funciones binarias simples como

funciones digitales complejas y operaciones aritmticas as como las operaciones

aritmticas en coma flotante.

Operaciones El conjunto de operaciones del lenguaje de programacin STEP 5 se divide en

operaciones bsicas:

- aplicables en todos los mdulos de cdigo,

- modos de representacin: esquema de contactos (KOP), esquema de

funciones (FUP) y lista de instrucciones (AWL).

y operaciones complementarias y de sistema:

- aplicables solamente en mdulos de funciones,

- modo de representacin: solamente lista de instrucciones (AWL),

- operaciones de sistema: slo para usuarios con muy buenos

conocimientos del sistema.

2.1.1 Modos de representacin KOP, FUP y AWL

Resumen En la programacin con STEP 5 se puede optar, para cada mdulo de cdigo,

entre los tres modos de representacin: esquema de contactos (KOP), esquema

de funciones (FUP) y lista de instrucciones (AWL), lo que significa que el

mtodo de programacin puede ser adaptado a cada tarea en particular.

El cdigo de mquina MC 5 generado por los aparatos de programacin (PG) es

idntico en los tres modos de representacin.

Si se respetan determinadas reglas al programar con el lenguaje STEP 5 (vase

bibliografa /3/), el aparato de programacin podr traducir los programas de

usuario de una forma de representacin a cualquier otra!

Instrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Proarama de usuario

Representacin Mientras que en los modos de representacin esquema de funciones (FUP) y

grfica o lista de esquema de contactos (KOP) se tiene la posibilidad de apreciar el programa en su

instrucciones forma grfica, en la lista de instrucciones (AWL) es necesario conocer las

instrucciones STEP 5.

Fig. 2-1 Modos de representacin del lenguaje de programacin STEP 5

ESQUEMA DE

CONTACTOS(K0P)

Programacin con

smbolos grficos,

como diagrama

secuencia1

corresponde

a la norma

DIN 19239

Representacin GRAPH 5 es un lenguaje de programacin para la representacin grfica de

grfica de mandos secuenciales. Es de orden superior a los modos de representacin KOP,

mandos FUP y AWL. Los programas escritos en la forma de representacin grfica

secuenciales GRAPH 5 son traducidos automticamente por el aparato de programacin a

programas en lenguaje STEP 5.

Instrucciones de programacin CPU 9288-311821

C79000-G8578-C870-01

LISTA DE INSTRUCCIONES

(AWL)

Programacin con

abreviaturas mnemo-

tcnicas de las funciones

corresponde

a la norma

DIN 19239

AWL

U E

UN E

U E

ON E

O E

= A

ESQUEMA DE

FUNCIONES (FUP)

Programacin con

smbolos grficos

corresponde

a las normas

ICE 117-15

DIN 40700

DIN 40719

DIN 19239

FUP

Proarama de usuario

2.1.2 Programacin estructurada

Resumen El lenguaje de programacin STEP 5 permite estructurar el programa de usuario.

sinptico Para ello se subdivide el programa de usuario en unidades independientes

(mdulos).

De este modo, la misma estructura del programa de usuano aclara a simple vista

sus partes esenciales o resalta elementos coherentes de la instalacin segn la

tcnica de programacin.

Ventajas

Qu es un

mdulo?

El procedimiento de la "programacin estructurada" ofrece las siguientes

ventajas:

programacin simple y ordenada, tambin para tareas de gran envergadura,

posibilidad de estandanzacin de programas parciales,

organizacin clara y simple de los programas,

facilidad de modificacin,

test simple del programa (por partes),

fcil puesta en funcionamiento.

Un mdulo es un elemento del programa de usuario que se distingue por su

funcin, estructura o finalidad. Cabe hacer distincin entre los mdulos que

contienen instrucciones (cdigos) tales como: mdulos de organizacin,

mdulos de programa, mdulos de funciones, mdulos de pasos, y los mdulos

que contienen datos (mdulos de datos).

Instrucciones de programacin CPU 9288-311821

C79000-G8578-C870-01

Proarama de usuario

2.1.3 Operaciones STEP 5

Definicin Una operacin STEP 5 es la menor unidad independiente del programa de

usuario. Es la orden de trabajo para la CPU. Una operacin STEP 5 se compone

de un elemento operante y de un elemento operando.

Ejemplo

Operandos

absolutos y

simblicos

Cdigo de operacin Parmetro

Elemento Elemento operando

operante (con qu operandos?)

('qu operacin

se debe efectuar?)

El elemento operando puede ser introducido de manera absoluta o simblica

(mediante la lista de asignaciones).

Ejemplo de representacin absoluta: :U E 1.4

Ejemplo de representacin simblica: :U -motor1

Para ms informacin respecto a la programacin absoluta y simblica, vase el

manual del correspondiente aparato de programacin.

Aplicacin de las El conjunto de operaciones que ofrece STEP 5 permite

operaciones

STEP 5 combinar, activar o rearmar valores binanos,

cargar y transferir valores,

comparar valores entre s y procesarlos antmticamente,

definir valores de tiempo y de contaje,

transformar representaciones numricas,

llamar mdulos y efectuar saltos dentro de un mdulo, e

influir sobre el procesamiento del programa.

Resultado de El bit central para el mando del programa es el resultado de combinacin VKE

combinacin VKE (resultado lgico). Se genera mediante combinaciones binanas y a veces es

alterado por algunas operaciones.

En el captulo 3.5 se encuentra una descripcin del conjunto total de operaciones

STEP 5, as como informaciones ms detalladas sobre el modo de generar el VKE.

lnstrucciones de programacin CPU 928B-3UB21

C79000-G8578-C870-01

Proarama de usuario

2.1.4 Representacin numrica

Resumen Para que la CPU pueda combinar, modificar o comparar valores numricos, stos

tienen que ser cargados en representacin binaria en los acumuladores (registros

de trabajo de la CPU).

Dependiendo de la operacin a ejecutar, STEP 5 acepta las siguientes

representaciones numricas:

Nmeros duales: 16 bit, coma fija

32 bit, coma fija

32 bit, coma flotante (con mantisa 16 24 bit)

Nmeros decimales: en BCD (signo y 3 dgitos decimales)