Académique Documents

Professionnel Documents

Culture Documents

Cont Adores

Transféré par

Crespi120Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Cont Adores

Transféré par

Crespi120Droits d'auteur :

Formats disponibles

_______________________________________________________________ ELECTRNICA GENERAL II

CONTADORES

Las aplicaciones de los contadores electrnicos digitales son numerosas. Incluyen los circuitos de control en

computadoras digitales, aplicaciones industriales tales como contar el nmero de revoluciones de un motor en un

intervalo de tiempo dado y la divisin de frecuencia necesaria para producir las seales de horas, minutos y

segundos en los relojes digitales.

Los contadores digitales pueden ser asincrnicos o sincrnicos y suelen estar implementados con biestables JK.

s obvio !ue los contadores digitales generan ceros y unos. "in embargo, no siempre cuentan en lo !ue se considera

la secuencia num#rica binaria normal $, %, %$, %%, %$$, %$%, &, sino !ue a menudo emplean alguna secuencia

arbitraria !ue debe ser decodificada. 'or ejemplo, un contador capa( de cuatro estados )$ a *+ puede contar de

acuerdo con la siguiente secuencia,

%% $

$$ % "ecuencia

completa %$ -

$% *

%% $

"i se !uiere una cuenta decimal real, se deber. incluir un circuito decodificador. n el ejemplo anterior el contador

pasa por cuatro estados antes de su reciclado y este nmero representa el mdulo del contador. "e lo denomina

tambi#n contador de mdulo cuatro. /omo cada biestable tiene dos estados posibles, un contador con 0 biestables

tiene un m.1imo de -

0

estados, siendo cada estado una combinacin diferente de los ceros y unos almacenados en

los biestables individuales. 2s3, el mdulo m.1imo de un contador de 0 biestables es -

0

. 4eneralmente se usa un

nmero de estados menor !ue el m.1imo, como, por ejemplo, en un contador de cuatro biestables utili(ado para

contar hasta %$ )contador de una d#cada o de mdulo %$+. 2!u3 solo se utili(an %$ de los %5 estados posibles.

Contador asincrnico

ste contador consiste en dos o m.s 676 8 interconectados de manera tal !ue la salida de cada 676 est. conectada a

la entrada de reloj del siguiente 676.

La denominacin 9asincrnico: se debe a !ue los estados de salida de cada 676 no cambian simult.neamente con

cada pulso de reloj.

stos contadores, tambi#n llamados contadores serie, pueden ser implementados para contar en forma ascendente o

descendente. La direccin de la cuenta puede invertirse utili(ando la salida complementaria de cada 676. /ada 676 es

disparado independientemente uno a la ve(.

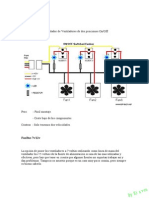

n la figura siguiente se puede ver un contador asincrnico ascendente de cuatro bits.

/omo se puede observar, cada 676 est. conectado para operar como 676 8 )J ; K ; %+. La salida Q de cada 676 se

conecta a la entrada /< del siguiente 676.

1

2

=

/

>

_______________________________________________________________ ELECTRNICA GENERAL II

n este ejemplo los biestables son disparados en el flanco descendente del pulso aplicado en /<. 2s3, cada 676

divide la frecuencia de entrada al mismo por dos, como se observa en el diagrama de tiempos. >e esta forma, el

nmero de estados o cuentas !ue se pueden lograr es -

n

, donde n es el nmero de 676. por lo tanto, con cuatro 676

se puede obtener la siguiente tabla.

Entrada Salidas Cuenta

/loc< > / = 2

$ $ $ $ $ $

% $ $ $ % %

- $ $ % $ -

* $ $ % % *

? $ % $ $ ?

@ $ % $ % @

5 $ % % $ 5

A $ % % % A

B % $ $ $ B

C % $ $ % C

%$ % $ % $ %$

%% % $ % % %%

%- % % $ $ %-

%* % % $ % %*

%? % % % $ %?

%@ % % % % %@

%5 $ $ $ $ $

>e la tabla se desprende !ue la cuenta m3nima binaria es -

n

7%. 2dem.s, como se observa en el circuito, la salida >

ser. el bit m.s significativo y la salida 2 el bit menos significativo de la cuenta.

'ara anali(ar en detalle el funcionamiento del contador se deber. observar el diagrama de tiempos y suponer !ue

inicialmente todos los 676 est.n 9limpios: o sea, sus salidas Q ; $.

Los 676 del ejemplo cambian el estado de sus salidas en el flanco descendente del pulso de reloj. /on el primer

flanco descendente Q2 pasar. a % por lo !ue en la entrada de reloj del segundo 676 se presentar. un flanco

ascendente por lo !ue la salida de este no cambiar.. n el siguiente flanco descendente del pulso de reloj la salida

Q2 pasar. a $ lo !ue representa un flanco descendente en la entrada de reloj del segundo 676 por lo !ue su salida

)Q=+ pasar. a %. s decir, cada ve( !ue la salida de un 676 cambia de % a $ se dispara el siguiente 676.

Daciendo algunos cambios en las cone1iones del circuito anterior se puede implementar un contador descendente

segn se muestra en la figura siguiente.

8ambi#n se puede implementar un contador descendente de la siguiente manera,

/on el empleo de un sistema de control en base a compuertas se puede implementar un contador

ascendenteEdescendente. 8ambi#n es posible, usando un sistema con compuertas adicionales, detener la cuenta del

contador en un estado cual!uiera inhibiendo la entrada de reloj o, tambi#n empleando compuertas adicionales hacer

!ue el contador se resetee cuando alcan(a un determinado estado de cuenta.

2

_______________________________________________________________ ELECTRNICA GENERAL II

Contador sincrnico

8ambi#n denominado contador paralelo, consiste en dos o m.s 676 J7K en donde en el primer 676 las entradas J y K

se conectan como 676 8 mientras !ue las entradas J y K de los siguientes son controladas por las salidas de los 676

precedentes.

s sincrnico por!ue los estados de las salidas cambian simult.neamente con cada pulso de reloj. 2simismo estos

contadores pueden ser ascendentes o descendentes.

2 diferencia del contador asincrnico la velocidad de operacin del contador sincrnico est. solamente limitado por el

tiempo de propagacin de un 676 y no por la suma de los tiempos de propagacin de todos los 676. por ello los

contadores sincrnicas se utili(an donde se necesita una velocidad de trabajo importante.

n la figura siguiente se muestra un contador sincrnico de cuatro bits.

Las entradas del primer 676 siempre est.n en % por lo !ue este 676 cambiar. de estado con cada pulso de reloj )en el

flanco descendente+, mientras !ue las entradas J y K de los restantes 676 dependen de los estados de salida del 676

precedente. 2s3, cuando Q2 sea % cambiar. el estado de Q= al presentarse el pulso de reloj )al mismo tiempo cambia

Q2+, Q/ cambiar. cuando Q2 y Q= sean % y F> lo har. cuando F2, F= y F/ sean %.

3

Vous aimerez peut-être aussi

- Prueba 2011Document13 pagesPrueba 2011Crespi120Pas encore d'évaluation

- Rutina 1 - Adaptacion MuscularDocument3 pagesRutina 1 - Adaptacion MuscularCrespi120Pas encore d'évaluation

- Resumen 1Document5 pagesResumen 1Crespi120Pas encore d'évaluation

- Prueba 2005Document10 pagesPrueba 2005Crespi120Pas encore d'évaluation

- Plan de Estudios Ingeniería Mecánica 2010 - FIUBADocument11 pagesPlan de Estudios Ingeniería Mecánica 2010 - FIUBAneodymioPas encore d'évaluation

- Plan de Estudios Ingeniería Mecánica 2010 - FIUBADocument11 pagesPlan de Estudios Ingeniería Mecánica 2010 - FIUBAneodymioPas encore d'évaluation

- Presupuesto de Accecorios Pieza de ArribaDocument1 pagePresupuesto de Accecorios Pieza de ArribaCrespi120Pas encore d'évaluation

- Prueba 1Document3 pagesPrueba 1Crespi120Pas encore d'évaluation

- Apuntes Basicos de AstronomiaDocument96 pagesApuntes Basicos de AstronomiaPedro LarregainPas encore d'évaluation

- Apunte SensoresDocument27 pagesApunte SensoresCrespi120Pas encore d'évaluation

- Electrónica I - Guia de Problemas 3 - Amplificador MultietapaDocument8 pagesElectrónica I - Guia de Problemas 3 - Amplificador MultietapaCrespi120Pas encore d'évaluation

- B3-Campos Magneticos Dinamicos - HDocument16 pagesB3-Campos Magneticos Dinamicos - HCrespi120Pas encore d'évaluation

- Tabla Periódica, Configuración Electrónica y Enlace Químico de Los ElementosDocument4 pagesTabla Periódica, Configuración Electrónica y Enlace Químico de Los Elementosvladimir divasPas encore d'évaluation

- Othello Sample in PascalDocument7 pagesOthello Sample in PascalYonaton_1Pas encore d'évaluation

- Funciones y Responsabilidades Del Personal Del Laboratorio de MetrologiaDocument3 pagesFunciones y Responsabilidades Del Personal Del Laboratorio de Metrologiacastmatamoros30% (10)

- Documento Final Presa IpaDocument235 pagesDocumento Final Presa IpaGonzalo Chocala Bellido100% (1)

- El Mayorista 16-06-22Document74 pagesEl Mayorista 16-06-22My BikersPas encore d'évaluation

- Explosivos ModernosDocument44 pagesExplosivos ModernosLUISPas encore d'évaluation

- Evidencia 3 de Producto RAP5 EV03 Propuesta Escrita de Acciones Preventivas y Correctivas A No Conformidad DetectadaDocument1 pageEvidencia 3 de Producto RAP5 EV03 Propuesta Escrita de Acciones Preventivas y Correctivas A No Conformidad DetectadaMiguel BenavidesPas encore d'évaluation

- Diseño y Construccion de CapacitoresDocument5 pagesDiseño y Construccion de CapacitoresUsuarioPas encore d'évaluation

- Análisis de Costos UnitariosDocument34 pagesAnálisis de Costos UnitariosPaola Salvador Serrano100% (1)

- Pruebas de Pulsos A Mosfet PDFDocument113 pagesPruebas de Pulsos A Mosfet PDFchicotec1Pas encore d'évaluation

- Hidraloy 300Document3 pagesHidraloy 300Jessica Arratea MoránPas encore d'évaluation

- Conf 2 Vías Vérreas. Componentes de Las Vías FérreasDocument63 pagesConf 2 Vías Vérreas. Componentes de Las Vías FérreasFabián FerroPas encore d'évaluation

- Ensayo Soldadura de Gas Inerte de TungstenoDocument3 pagesEnsayo Soldadura de Gas Inerte de TungstenoJuan Daniel Felix PalominoPas encore d'évaluation

- Comportamiento de Estructuras de Acero Durante Los Sismos de Septiembre de 2017Document6 pagesComportamiento de Estructuras de Acero Durante Los Sismos de Septiembre de 2017Pablo MuñizPas encore d'évaluation

- Manual CFS-1 2G OzonadorDocument91 pagesManual CFS-1 2G OzonadorErik Vazquez Ulloa100% (2)

- Laboratorio9 Hidraulica TerminadoDocument15 pagesLaboratorio9 Hidraulica TerminadoBruno Polanco PezoPas encore d'évaluation

- Baybus - FanBus - RheoBus - ElectroBus - PWM - 220VDocument17 pagesBaybus - FanBus - RheoBus - ElectroBus - PWM - 220VanimalenlataPas encore d'évaluation

- Caudal de AIREDocument6 pagesCaudal de AIREBETTY HUAMAN CUSIPas encore d'évaluation

- Hoja - Seguridad TRABASIL VA3 PDFDocument5 pagesHoja - Seguridad TRABASIL VA3 PDFMartin SoPas encore d'évaluation

- Central HidroeléctricaDocument3 pagesCentral HidroeléctricaMiguelulaPas encore d'évaluation

- Coeficientes y Porcentajes de DesperdicioDocument3 pagesCoeficientes y Porcentajes de Desperdiciojoserod1770% (10)

- Trabajo de Investigación de Canales Hidráulicos y Aplicacion en HcanalesDocument17 pagesTrabajo de Investigación de Canales Hidráulicos y Aplicacion en HcanalesAdolfoDavidPas encore d'évaluation

- El Efecto de La Presión AtmosféricaDocument3 pagesEl Efecto de La Presión AtmosféricaKarlita DazaPas encore d'évaluation

- Laboratorio 03 Condensador ElectricoDocument20 pagesLaboratorio 03 Condensador ElectricoFrank Jr Sangay CorralesPas encore d'évaluation

- Trabajo de Investigacion # 3 (Sensores)Document3 pagesTrabajo de Investigacion # 3 (Sensores)Jimena Encinas López0% (1)

- AerosolesDocument15 pagesAerosolesalexqaPas encore d'évaluation

- Distribucion ElectronicaDocument2 pagesDistribucion Electronicael_travieso100% (1)

- Mapa Conceptual OperatoriaDocument1 pageMapa Conceptual OperatoriaLeonardo Manuel VillegasPas encore d'évaluation

- Cuadro Sinóptico de Tipos de Actuadores RodrigoDocument24 pagesCuadro Sinóptico de Tipos de Actuadores RodrigoRodrigo Raziel Bernal ChulinPas encore d'évaluation

- Tipos y Ejemplos de Sistemas de Información en Una EmpresaDocument2 pagesTipos y Ejemplos de Sistemas de Información en Una EmpresajanojimenezPas encore d'évaluation

- Manual técnico para la interpretación de análisis de suelos y fertilización de cultivosD'EverandManual técnico para la interpretación de análisis de suelos y fertilización de cultivosÉvaluation : 4 sur 5 étoiles4/5 (1)

- Influencia. La psicología de la persuasiónD'EverandInfluencia. La psicología de la persuasiónÉvaluation : 4.5 sur 5 étoiles4.5/5 (14)

- Excel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másD'EverandExcel para principiantes: Aprenda a utilizar Excel 2016, incluyendo una introducción a fórmulas, funciones, gráficos, cuadros, macros, modelado, informes, estadísticas, Excel Power Query y másÉvaluation : 2.5 sur 5 étoiles2.5/5 (3)

- 7 tendencias digitales que cambiarán el mundoD'Everand7 tendencias digitales que cambiarán el mundoÉvaluation : 4.5 sur 5 étoiles4.5/5 (87)

- Clics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaD'EverandClics contra la humanidad: Libertad y resistencia en la era de la distracción tecnológicaÉvaluation : 4.5 sur 5 étoiles4.5/5 (117)

- Excel 2021 y 365 Paso a Paso: Paso a PasoD'EverandExcel 2021 y 365 Paso a Paso: Paso a PasoÉvaluation : 5 sur 5 étoiles5/5 (12)

- Guía de cálculo y diseño de conductos para ventilación y climatizaciónD'EverandGuía de cálculo y diseño de conductos para ventilación y climatizaciónÉvaluation : 5 sur 5 étoiles5/5 (1)

- Proyectos Arduino con Tinkercad: Diseño y programación de proyectos electrónicos basados en Arduino con TinkercadD'EverandProyectos Arduino con Tinkercad: Diseño y programación de proyectos electrónicos basados en Arduino con TinkercadÉvaluation : 5 sur 5 étoiles5/5 (1)

- La causa raiz de los accidentes: Historias de accidentes en la industriaD'EverandLa causa raiz de los accidentes: Historias de accidentes en la industriaÉvaluation : 5 sur 5 étoiles5/5 (1)

- Inteligencia artificial: Análisis de datos e innovación para principiantesD'EverandInteligencia artificial: Análisis de datos e innovación para principiantesÉvaluation : 4 sur 5 étoiles4/5 (3)

- EL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.D'EverandEL PLAN DE MARKETING EN 4 PASOS. Estrategias y pasos clave para redactar un plan de marketing eficaz.Évaluation : 4 sur 5 étoiles4/5 (51)

- Todo Sobre Tecnología Blockchain: La Guía Definitiva Para Principiantes Sobre Monederos BlockchainD'EverandTodo Sobre Tecnología Blockchain: La Guía Definitiva Para Principiantes Sobre Monederos BlockchainPas encore d'évaluation

- Excel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteD'EverandExcel y SQL de la mano: Trabajo con bases de datos en Excel de forma eficienteÉvaluation : 1 sur 5 étoiles1/5 (1)

- Guía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaD'EverandGuía para la crianza en un mundo digital: Cómo educar para un uso sano y seguro de la tecnologíaÉvaluation : 3.5 sur 5 étoiles3.5/5 (2)

- Manual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasD'EverandManual Técnico del Automóvil - Diccionario Ilustrado de las Nuevas TecnologíasÉvaluation : 4.5 sur 5 étoiles4.5/5 (14)

- Lógica de programación: Solucionario en pseudocódigo – Ejercicios resueltosD'EverandLógica de programación: Solucionario en pseudocódigo – Ejercicios resueltosÉvaluation : 3.5 sur 5 étoiles3.5/5 (7)

- Comunicaciones industriales y WinCCD'EverandComunicaciones industriales y WinCCÉvaluation : 5 sur 5 étoiles5/5 (4)

- LAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.D'EverandLAS VELAS JAPONESAS DE UNA FORMA SENCILLA. La guía de introducción a las velas japonesas y a las estrategias de análisis técnico más eficaces.Évaluation : 4.5 sur 5 étoiles4.5/5 (54)