Académique Documents

Professionnel Documents

Culture Documents

Computer Architreture Sylabus and Two Mark Questions

Transféré par

ammapet0 évaluation0% ont trouvé ce document utile (0 vote)

50 vues9 pagesComputer architretue sylabus and contains important two mark questions with answers

Titre original

computer architreture sylabus and two mark questions

Copyright

© © All Rights Reserved

Formats disponibles

DOC, PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentComputer architretue sylabus and contains important two mark questions with answers

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOC, PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

50 vues9 pagesComputer Architreture Sylabus and Two Mark Questions

Transféré par

ammapetComputer architretue sylabus and contains important two mark questions with answers

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme DOC, PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 9

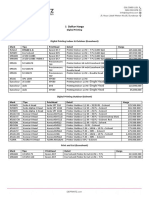

CS6303 COMPUTER ARCHITECTURE L T P C

UNIT I OVERVIEW & INSTRUCTIONS 9

Eight ideas Components of a computer system Technology Performance Power wall

Uniprocessors to multiprocessors; Instructions operations and operands representing

instructions Logical operations control operations Addressing and addressing modes.

UNIT II ARITHMETIC OPERATIONS 7

ALU Addition and su!traction "ultiplication #i$ision %loating Point operations

&u!word parallelism.

UNIT III PROCESSOR AND CONTROL UNIT 11

'asic "IP& implementation 'uilding datapath Control Implementation scheme

Pipelining Pipelined datapath and control (andling #ata ha)ards * Control ha)ards

E+ceptions.

UNIT IV PARALLELISM 9

Instructionle$elparallelism Parallel processing challenges %lynn,s classification

(ardware multithreading "ulticore processors

UNIT V MEMORY AND I/O SYSTEMS 9

"emory hierarchy "emory technologies Cache !asics "easuring and impro$ing cache

performance -irtual memory. TL's Input/output system. programmed I/0. #"A and

interrupts. I/0

processors.

TOTAL: 45 PERIODS

OUTCOMES:

At t! !"# $% t! &$'()!* t! )t'#!"t )$'+# ,! -,+! t$:

#esign arithmetic and logic unit.

#esign and anlayse pipelined control units

E$aluate performance of memory systems.

Understand parallel processing architectures.

TE.T /OO0:

1. #a$id A. Patterson and 2ohn L. (ennessey. 3Computer organi)ation and design4. "organ

5auffman / Else$ier. %ifth edition. 6718.

RE1ERENCES:

1. -.Carl (amacher. 9$on:o ;. -aranesic and &afat ;. 9a:y. 3Computer 0rganisation3.

-I th edition. "c ;raw(ill Inc. 6716.

6. <illiam &tallings 3Computer 0rgani)ation and Architecture= . &e$enth Edition . Pearson

Education. 677>.

?. -incent P. (euring. (arry %. 2ordan. 3Computer &ystem Architecture=. &econd Edition.

Pearson Education. 677@.

8. ;o$indaraAalu. 3Computer Architecture and 0rgani)ation. #esign Principles and

ApplicationsB. first edition. Tata "c;raw (ill. Cew #elhi. 677@.

@. 2ohn P. (ayes. 3Computer Architecture and 0rgani)ation=. Third Edition. Tata "c ;raw

(ill. 1DDE.

1.Define Computer Architecture

Computer Architecture Is Defined As The Functional Operation Of The Individual H/W Unit

In A Computer System And The Flo Of Information Amon! The Control Of Those Units

2.Define Computer H/W

Computer H/W Is The "lectronic Circuit And "lectro #echanical "$uipment That

Constitutes The Computer

3. What Is Meant By Cache Memory ?

A #emory That Is Smaller And Faster Than #ain #emory And That Is Interposed %eteen

The Cpu And #ain #emory& The Cache Acts As A %uffer For 'ecently Used #emory

(ocation

4.hat is !oca!ity of reference?

#any instruction in locali)ed area of the pro!ram are e*ecuted repeatedly durin! some time

period and the remainder of the pro!ram is accessed relatively infre$uently &this is referred as

locality of reference&

".hat is I# mappe$ input output?

A memory reference instruction activated the '"AD # +or,W'IT" # control line and does

not affect the IO device& Separate IO instruction are re$uired to activate the '"AD IOand

W'IT" IO lines -hich cause a ord to .e transferred .eteen the address aio port and the

C/U& The memory and IO address space are 0ept separate&

%.specify the three types of the DMA transfer techni&ues?

Sin!le transfer mode+cyclestealin! mode,

%loc0 Transfer #ode+%rust #ode,

Demand Transfer #ode

Cascade #ode

'. hy is memory refreshin( circuit nee$e$ ?

al cells on the correspondin! yo to .e read and refreshed durin! .oth read and rite

operation &the contents of the d ram are maintained each ro of cell must .e accessed

periodically once every 1 2 34 ms& refresh circuit usually performs this function &

automatically

) hat are the functions of contro! unit ?

the memory arithmetic and lo!ic -and input and output units store and process information

and perform i/p and o/p operation- the operation of these unit must .e co ordinate in some

ay this is the tas0 of control unit the cu is effectively the nerve center that sends the control

si!nal to other units and sence their states&

*.What is an interrupt?

An interrupt is an event that causes the e*ecution of one pro!ram to .e suspended and

another pro!ram to .e e*ecuted&

1+.What are the uses of interrupts?

5 'ecovery from errors

5 De.u!!in!

5 Communication .eteen pro!rams

5 Use of interrupts in operatin! system

11.Define ,ectore$ interrupts.

In order to reduce the overhead involved in the pollin! process- a device re$uestin! an

interrupt may identify itself directly to the C/U& Then- the C/U can immediately start

e*ecutin! the correspondin! interrupt6service routine& The term vectored interrupts refers to

all interrupt6handlin! schemes .ase on this approach&

12. What is the nee$ for re$uce$ instruction chip?

3& 'elatively fe instruction types and addressin! modes&

1& Fi*ed and easily decoded instruction formats&

7& Fast sin!le6cycle instruction e*ecution&

8& Hardired rather than micropro!rammed control&

13. -ame any three of the stan$ar$ I/# interface.

3& SCSI +small computer system interface,-.us standards

1& %ac0 plane .us standards

7& I""" 9:4 .us +multi.us si!nals,

8& ;U%US

<& I""" 8== .us standard

1"../p!ain the pipe!ine types.

3& Instruction pipeline

1& Arithmetic pipeline

1%. ./p!ain the ,arious c!assifications of para!!e! structures.

3& SISD +sin!le instruction stream sin!le data stream

1& SI#D+sin!le instruction stream multiple data stream

7& #I#D+multiple instruction stream multiple data stream

8& #ISD+multiple instruction stream sin!le data stream

1'. What is a0so!ute a$$ressin( mo$e?

The address of the location of the operand is !iven e*plicitly as a part of the instruction&

"!& #ove a - 1>>>

1). 1pecify three types of $ata transfer techni&ues&

3& Arithmetic data transfer

1& (o!ical data transfer

7& /ro!rammed control data transfer

1*. What is the ro!e of MA2 an$ MD2?

The #A' +memory address re!ister, is used to hold the address of the location to or from

hich data are to .e transferred and the #D'+memory data re!ister, contains the data to .e

ritten into or read out of the addressed location&

2+. What are the ,arious types of operations re&uire$ for instructions?

3& Data transfers .eteen the main memory and the C/U re!isters

1& Arithmetic and lo!ic operation on data

7& /ro!ram se$uencin! and control

8& I/O transfers

21. What is the ro!e of I2 an$ 3C?

Instruction 'e!ister +I', contains the instruction .ein! e*ecuted& Its output is availa.le to the

control circuits- hich !enerate the timin! si!nals for controllin! the processin! circuits

needed to e*ecute the instructions& The /ro!ram Counter +/C, re!ister 0eeps trac0 of the

e*ecution of the pro!ram& It contains the memory address of the instruction currently .ein!

e*ecuted & Durin! the e*ecution of the current instruction- the contents of the /C are updated

to correspond to the address of the ne*t instructions to .e e*ecuted&

22.Define memory access time?

The time that elapses .eteen the initiation of an operation and completion of that

operation -for e*ample -the time .eteen the '"AD and the #FC si!nals &This is 'eferred to

as memory access time&

23. Define memory cyc!e time.

The minimum time delay re$uired .eteen the initiations of to successive memory

operations- for e*ample- the time .eteen to successive '"AD operations&

24.Define 1tatic Memories.

#emories that consist of circuits capa.le of retainin! the state as lon! as poer is applied are

0non as static memories&

2".Distin(uish Beteen 1tatic 2AM an$ Dynamic 2AM?

Static 'A# are fast- .ut they come at hi!h cost .ecause their cells re$uire several transistors&

(ess e*pensive 'A# can .e implemented if simpler cells are used& Hoever such cells do

not retain their state indefinitely@ Hence they are called Dynamic 'A#&

2%.Disti(uish 0eteen asynchronies D2AM an$ synchronous 2AM.

The speciali)ed memory controller circuit provides the necessary control si!nals- 'AS And

CAS -that !overn the timin!& The processor must ta0e into account the delay in the response

of the memory& Such memories are referred to as asynchronous D'A#S& The D'A# hose

operations is directly synchroni)ed ith a cloc0 si!nal& Such #emories are 0non as

synchronous D'A#

2'.hat are the ,arious units in the computer?

3-input unit

1&output unit

7&control unit

8&memory unit

<&arithmetic and lo!ical unit

2).hat is an I/# channe!?

An i/o channel is actually a special purpose processor- also called peripheral processor& The

main processor initiates a transfer .y passin! the re$uired information in the input output

channel& the channel then ta0es over and controls the actual transfer of data&

2*.hat is a 0us?

A collection of ires that connects several devices is called a .us&

3+.Define or$ !en(th?

"ach !roup of n .its is referred to as a ord of information and n is called the ord len!th&

31.e/p!ain the fo!!oin( the a$$ress instruction?

3&three6address instruction6it can .e represented as

add a-.-c

Operands a-. are called source operand and c is called destination operand&

1&to6address instruction6it can .e represented as

add a-.

7&one address instruction6it can .e represented as

add a

8&3 3/1 address instruction

it can .e represented the type of instruction in hich one address alays refers to a location

in the main memory and the other- shorter address alays refers to a cpu re!ister- is

intermediate to the one6to6address formats .ecause of this property is called I A address

format&

<&)ero address instruction&

It is also possi.le to use instruction here the location s of all operand are defined implicitly&

This operand of the use of the method for storin! the operand in hich called push don

stac0& Such instructions are sometimes referred to us )ero address instruction&

32.hat is the strai(ht4!ine se&uencin(?

the cpu control circuitry automatically proceed to fetch and e*ecute instruction- one at a time

in the order of the increasin! addresses& This is called strai!ht line se$uencin!&

33.hat is the ro!e of pc?

The cpu contains a re!ister called the pro!ram counter- hich holds the address of instruction

to .e e*ecuted ne*t&& to .e!in the e*ecution of the pro!ram the address of its First instruction

must .e placed into the pc&

34.hat are steps for e/ecution of a comp!ete instruction?

3&fetch the instruction&

1&fetch the first operand +the contents of the memory location pointed .y the address field of

the instruction&,

7&perform the calculation&

8&load the result&

3".hat is a a 0it s!ice?

A .it slice is BsliceC throu!h the data path of the typical processor& It contains all Circuits

necessary to provide alu function- re!ister transfer and control function for only a fe .its of

the data path&

3%.hat is DMA?

A special control unit may .e provided to ena.le transfer a .loc0 of data directly .eteen an

e*ternal device and memory ithout conti!uous intervention .y the cpu& This approach is

called D#A&

3'.hy pro(ram contro!!e$ I/# is unsuita0!e for hi(h4spee$ $ata transfer?

3& in pro!ram controlled i/o considera.le overhead is incurred&& .ecause several pro!ram

instruction have to .e e*ecuted for each data ord transferred .eteen the e*ternal devices

and ##&

1& many hi!h speed peripheral@ devices have a synchronous modes of operation& that is data

transfer are controlled .y a cloc0 of fi*ed fre$uency- independent of the cpu&

3).hat is the function of i/o interface?

The function is to coordinate the transfer of data .eteen the cpu and e*ternal devices&

3*.hat is -5B51?

A ;U%US is a processor independent- synchronous .us standard intended for use in 71 .it

micro processor system& It defines a .ac0plane into hich upto 34 devices may .e plu!!ed

each in the form of circuit .oard of standard dimensions&

4+. hat $o you mean associati,e mappin( techni&ue?

The ta! of an address received from the C/U is compared to the ta! .its of each .loc0 of the

cache to see if the desired .loc0 is present& This is called associative mappin! techni$ue&

41. What is 625 rep!acement a!(orithm?

When a .loc0 is to .e overritten it is sensi.le to overrite the one that has !one the lar!est

time ithout .ein! referenced& This .loc0 is called (east 'ecently Used .loc0 and the

techni$ue is called ('U replacement al!orithm&

42. ./p!ain ,irtua! memory techni&ue.

Techni$ues that automatically move pro!ram and data .loc0s into the physical memory hen

they are re$uired for e*ecution are called virtual memory techni$ue&

43. What are ,irtua! an$ !o(ica! a$$resses?

The .inary addresses that the processor issues for either instruction or data are called virtual

or lo!ical addresses&

44. Define trans!ation 0uffer.

#ost commercial virtual memory systems incorporate a mechanism that can avoid the .ul0

of the main memory access called for .y the virtual to physical addresses translation .uffer&

This may .e done ith a cache memory called a translation .uffer- hich retains the results

of the recent translation&

4". -ame some of the I# $e,ices.

3& Dideo terminals

1& Dideo displays

7& Alphanumeric displays

8& Eraphics displays

<& Flat panel displays

4& /rinters

9& /lotters

4%. What is 0ranch $e!ay s!ot?

The location containin! an instruction that may .e fetched and then discarded .ecause of the

.ranch is called .ranch delay slot&

4'. What is optica! memory?

Optical or li!ht .ased techni$ues for data stora!e- such memories usually employ optical dis0

hich resem.le ma!netic dis0 in that they store .inary information in concentric trac0s on an

electromechanically rotated dis0s& The information is read as or ritten optically- hoever

ith a laser replacin! the read rite arm of a ma!netic dis0 drive& Optical memory offer hi!h

stora!e capacities .ut their access rate is are !enerally less than those of ma!netic dis0&

4). What is micropro(ramme$ contro!?

#icropro!rammed control in hich control si!nals are !enerated .y a pro!ram similar to

machine lan!ua!e pro!ram& A se$uence of one +or, more microoperation- such as addition-

multiplication is called a micro pro!ram& The address here these microinstructions are

stored in C# is !enerated .y micropro!rammed control&

4*. What is micropro(rammin(?

A se$uence of Control Words correspondin! to the control se$uence of a machine instruction

constitutes the micro routine for that instruction- and the individual control ords in this

micro routine are referred to as microinstructions& #icropro!rammin! is a method of control

unit desi!n in hich the control si!nal selection and se$uencin! information is stored in a

'O# +or, 'A# called a control memory C#&

"+.What are static an$ $ynamic memories?

Static memory are memories hich re$uire periodic no refreshin!& Dynamic memories are

memories- hich re$uire periodic refreshin!&

"1. What are the steps re&uire$ for a pipe!inene$ processor to process the instruction?

3& F FetchF read the instruction from the memory

1& D DecodeF decode the instruction and fetch the source operand+s,&

7& " "*ecuteF perform the operation specified .y the instruction&

8& W WriteF store the result in the destination location&

"2. What are the steps ta7en hen an interrupt occurs?

3& Source of the interrupt

1& The memory address of the re$uired IS/

7& The pro!ram counter G cpu information saved in su.routine

8& Transfer control .ac0 to the interrupted pro!ram

"3 Define instruction pipe!ine.

The transfer of instructions throu!h various sta!es of the cpu instruction cycle&- includin!

fetch opcode-decode opcode-compute operand addresses& Fetch operands- e*ecute

instructions and store results& This amounts to reali)in! most +or, all of the cpu in the form of

multifunction pipeline called an instruction pipelinin!&

"4. Define !atency.

The term memory latency is used to refer to the amount of time it ta0es to transfer a ord of

data to or from the memory& The term latency is used to denote the time it ta0es to transfer the

first ord of data& This time is usually su.stantially lon!er than the time needed to transfer

each su.se$uent ord of a .loc0&

"". Define 0an$i$th.

%andidth is a product of the rate at hich the data are transferred +and accessed, and the

idth of the data .us&

"%. Define hit rate.

A successful access to data in a cache is called a hit& ;um.er of hits stated as a fraction of all

attempted accesses is called the hit rate&

"'. Define miss rate.

A miss rate is the num.er of misses stated as a fraction of attempted accesses& "*tra time

needed to .rin! the desired information into the cache is called the miss penalty&

"). Distin(uish 0eteen system space an$ user space.

assem.lin! the operatin! system routine into a virtual address space - is called system space

that is separate from the virtual space in hich user application pro!ram reside& The latter

space is called user space&

"*.Define

3& Si!nal 6 The .inary information is represented in di!ital computers .y physical $uantities

called si!nals&

1& Eates 2 The manipulation of .inary information is done .y lo!ic circuits called !ates&

Eates are .loc0s of hardare that produce si!nals of .inary 3 or > here input lo!ic

re$uirements are satisfied&

7& Flip flop 2 The stora!e elements employed in cloc0ed se$uential circuits are called flip

flops& A flip flop is a .inary cell capa.le of storin! 3 .it of information&

%+. Define com0inationa! circuit.

A com.inational circuit is a connected arran!ement of lo!ic !ates ith the set of inputs and

outputs& A com.inational circuit transforms .inary information from the !iven input data to

the re$uired output data& Com.inational are employed in di!ital computers re$uired for

!eneratin! .inary control decisions and for providin! di!ital components re$uired for data

processin!&

%1. Define se&uentia! circuits.

A se$uential circuit is an interconnectin of flip6flops and !ates& The !ates .y themselves

constitute a com.inational circuit- .ut hen included ith the flip flops- the overall circuit is

classified as a se$uential circuit&

%2. Define interface.

The ord interface refers to the .oundary .eteen to circuits or devices&

%3. Define pipe!inin(.

/ipelinin! is a techini$ue of decomposin! a se$uential process into su. operations ith each

su.process .ein! e*ecuted in a special dedicated se!ment that operates concurrently ith all

other se!ments&

%4. Define para!!e! processin(.

/arallel processin! is a term used to denote a lar!e class of techni$ues that are used to

provide simultaneous data6processin! tas0s for the purpose of increasin! the computational

speed of a computer system& Instead of processin! each instruction se$uentially as in a

conventional computer- a parallel processin! system is a.le to perform concurrent data

processin! to achieve faster e*ecution time&

%". What are the components of memory mana(ement unit?

3& A facility for dynamic stora!e relocation that maps lo!ical memory references into physical

memory addresses&

1 A provision for sharin! common pro!rams stored in memory .y different users &

&7& /rotection of information a!ainst unauthori)ed access .eteen users and preventin! users

from chan!in! operatin! system functions&

%%. What is pro(ramme$ I/#?

Data transfer to and from peripherals may .e handled usin! this mode& /ro!rammed I/O

operations are the result of I/O instructions ritten in the computer pro!ram&

Vous aimerez peut-être aussi

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (120)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- BK4A-001-TS-IA2-SP-01 - B - Specification For Safety Integrated System SIS - FGS-SDS - MarkupDocument61 pagesBK4A-001-TS-IA2-SP-01 - B - Specification For Safety Integrated System SIS - FGS-SDS - MarkupmuthoiPas encore d'évaluation

- Introduction To International Legal English2Document12 pagesIntroduction To International Legal English2BeaBurgos Aquí Tetuán100% (4)

- Artificial Intelligence QuizDocument4 pagesArtificial Intelligence QuizammapetPas encore d'évaluation

- GX Work 3 Manual BasicoDocument156 pagesGX Work 3 Manual BasicoAlexPas encore d'évaluation

- CS7103 Multi Core Architreture Cycle TestDocument20 pagesCS7103 Multi Core Architreture Cycle TestammapetPas encore d'évaluation

- CS6303 Leature NotesDocument23 pagesCS6303 Leature NotesammapetPas encore d'évaluation

- CS6303 Leature Notes 1Document18 pagesCS6303 Leature Notes 1ammapetPas encore d'évaluation

- Computer Networks Toplogys1Document9 pagesComputer Networks Toplogys1ammapetPas encore d'évaluation

- CS6303 Leature NotesDocument23 pagesCS6303 Leature NotesammapetPas encore d'évaluation

- Business LawDocument7 pagesBusiness LawammapetPas encore d'évaluation

- Commercial Law: Title 13. Consumer Protection Act Subtitle 3. Unfair or Deceptive Trade PracticesDocument3 pagesCommercial Law: Title 13. Consumer Protection Act Subtitle 3. Unfair or Deceptive Trade PracticesammapetPas encore d'évaluation

- Business LawDocument7 pagesBusiness LawammapetPas encore d'évaluation

- Social AuditDocument111 pagesSocial AuditnasitbhavikPas encore d'évaluation

- 3BSE020925R301 S800 IO Fieldbus Communication Interface For Advant Fieldbus 100 Users GuideDocument86 pages3BSE020925R301 S800 IO Fieldbus Communication Interface For Advant Fieldbus 100 Users GuideMatringePas encore d'évaluation

- Computer Organization andDocument50 pagesComputer Organization andSowmiya SplendiferousPas encore d'évaluation

- Major Project Document PDFDocument74 pagesMajor Project Document PDFPrathyusha Choudary ArumandlaPas encore d'évaluation

- Field Service Tool Kit Hyperformance Plasma (HPR)Document13 pagesField Service Tool Kit Hyperformance Plasma (HPR)Aung Naing OoPas encore d'évaluation

- CSVTU Operating System Unit 1Document43 pagesCSVTU Operating System Unit 1Kapil NagwanshiPas encore d'évaluation

- S2N Gyro Interface ManualDocument20 pagesS2N Gyro Interface ManualAfrizal Setiawan100% (1)

- Air University: ObjectiveDocument5 pagesAir University: ObjectiveUsman KhanPas encore d'évaluation

- Unit 4 - Io SystemsDocument37 pagesUnit 4 - Io Systemsneela kl100% (1)

- Chap 04Document22 pagesChap 04Zerihun Bekele100% (1)

- Motherboard Failure and Maintenance BasicsDocument3 pagesMotherboard Failure and Maintenance Basicsragav1234Pas encore d'évaluation

- Lesson Plan-2014Document74 pagesLesson Plan-2014ManishShilu100% (6)

- C1102 Introduction To Computer Systems and ProgrammingDocument5 pagesC1102 Introduction To Computer Systems and ProgrammingMuhammad Yusril Jr.0% (1)

- COA Unit-1Document284 pagesCOA Unit-1Amanuel DagetPas encore d'évaluation

- Embedded Systems Lecture 2Document29 pagesEmbedded Systems Lecture 2migadPas encore d'évaluation

- 3 MicrocontrollersDocument28 pages3 MicrocontrollersRynefel EloprePas encore d'évaluation

- CSC 203 Week 1-3Document22 pagesCSC 203 Week 1-3seyiPas encore d'évaluation

- S2 MPC: Sen2Cor Configuration and User ManualDocument53 pagesS2 MPC: Sen2Cor Configuration and User ManualCarlos CordovaPas encore d'évaluation

- PM H010WACå ÅDocument2 pagesPM H010WACå ÅAlfian AhkamPas encore d'évaluation

- XXXXXXXXXXXXXXXXXXXXXXXXXXXXX PDFDocument113 pagesXXXXXXXXXXXXXXXXXXXXXXXXXXXXX PDFPauloRobertoRobertoPas encore d'évaluation

- Computer Organization May 2008 Question PaperDocument4 pagesComputer Organization May 2008 Question Paperelimelek100% (1)

- Diploma in CS 3rd Year SyllabusDocument54 pagesDiploma in CS 3rd Year SyllabusHabiba NadeemPas encore d'évaluation

- 1 Daftar Harga: Digital PrintingDocument4 pages1 Daftar Harga: Digital PrintingfajarPas encore d'évaluation

- Schneider Indonesia April 13, 2005: Ge MultilinDocument40 pagesSchneider Indonesia April 13, 2005: Ge MultilinMarioPas encore d'évaluation

- Chapter 16 - Files and StreamsDocument53 pagesChapter 16 - Files and StreamsArul Kumar VenugopalPas encore d'évaluation

- Swat Io 2009Document662 pagesSwat Io 2009Suhaidi AliasPas encore d'évaluation

- Overview of CISCO FIREWALLDocument42 pagesOverview of CISCO FIREWALLAlo ChayaPas encore d'évaluation

- 07 Array Processing - SlideDocument51 pages07 Array Processing - SlideRakaBetaPas encore d'évaluation

- 16MT6201 Industrial Automation and Control QBDocument10 pages16MT6201 Industrial Automation and Control QBsindhusssPas encore d'évaluation