Académique Documents

Professionnel Documents

Culture Documents

210 Exp1

Transféré par

Purab RanjanTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

210 Exp1

Transféré par

Purab RanjanDroits d'auteur :

Formats disponibles

DEPARTMENT OF ELECTRICAL & ELECTRONIC ENGINEERING

BANGLADESH UNIVERSITY OF ENGINEERING & TECHNOLOGY

COURSE NO.: EEE 210

EXPERIMENT NO. 01

Name ! "#e E$%e&'me(": STUDY OF DIODES AND ITS APPLICATIONS.

OB)ECTIVE

The objective of this experiment is to simulate

I-V characteristics of diodes.

Clipper and clamper circuits.

Diode bridge rectifier.

Regulated power supplies using diodes.

THEORY

p-n junction diode is a two-terminal device that acts as a one-wa! conductor. "hen a diode is

forward biased as shown in #ig. $%a&' current ID flows through the diode and current is given b!

= $

T

a

nV

V

S D

e I I

%$&

where' n is the idealit! factor and $ n (. I) is the reverse-saturation current and VT *+T,- is

the thermal voltage. VT is about ...(/V at room temperature.

Va

D$

0 $12..$

$3

V R

-

"hen it is reverse biased as shown in #ig. $%b&' ID * -I) %for see e-n. %(&&. s it is generall! in p

%pico-amp& range' in man! applications this current is neglected and diode is considered open.

S

V

V

S D

I e I I

T

R

=

=

$

for 4V4 55VT %(&

The material for p-n junction diode is silicon semiconductor. )emiconductors are a group of

materials having electrical conductivit! intermediate between metals and insulators.

6etals7 l %aluminum&' Cu%copper&'u%gold&.

Insulators7 Ceramic' "ood ' rubber.

)emiconductor7 )i %silicon&' 8e %germanium&' 8as %gallium-arsenide&.

P*"+%e S','-(:

"hen an intrinsic silicon semiconductor is doped with l impurities' it becomes p-t!pe. t

thermal e-uilibrium'

po*1 and no * ni

(

,1

where' po is the hole concentration ' no is the electron concentration ' 1 is the doping densit! of

impurities%acceptor atoms&'

ni is the intrinsic concentration. ni * $.9x$.

$.

cm

-:

for )i at room

temperature .

N*"+%e .','-(:

"hen an intrinsic silicon semiconductor is doped with ;%phosphorous& impurities it becomes n-

t!pe . t thermal e-uilibrium' no*1D and ;o* ni

(

,1D. <ere' 1D is the doping densit! of

impurities %donor atoms&.

In semiconductor both holes and electrons contribute to current.

;age $ of =

#ig.$%a&

C/&&e("*V,"a0e C#a&a-"e&'."'-.

Vin is the cut-in voltage. Its value is usuall! ..9V. t this voltage' diode is forward biased but

even then I is ver! small and it is usuall! neglected. "hen diode is reverse biased and V> V3'

diode drives into brea+down and a large current will flow. The current can be limited b! using

resistor in diode circuit. If the slope %dI,dV& is ver! steep' the brea+down mechanism is called

?ener brea+down. ?ener diode can be used in regulator circuit.

P'e-e1'.e*L'(ea& 2& Ba""e&+*P,/.*Re.'."a(-e3 m4e,:

RD@...(9An,ID

Sma,, .'0(a, a- m4e,

The previous models represent the dc behaviour of the diode

"hen there are small changes of current through the diode need a small signal or ac model

small change in forward current through the diode will give rise to a corresponding change

in forward voltage

;age ( of =

V

in

*..9V

Reverse Brea+down

V

I

#ig. $%b&

I,V * %-,+BT&I.exp%-V,+BT& -I,+BT

This gives rise to an effective resistance of the diode to small currents

- the DC16IC #DR"RD RE)I)T1CE of the diode

&D 5 V6I 5 7BT68I

t room temp rD ...(9,I * $,2.I

D!namic resistance onl! changes slightl! for small changes in temp.

Dhmic resistance decreases with increase in T -(.9 mV,3

C,'%%e& a(4 -,am%e& -'&-/'".:

Fimiter or clippers are used to cut-off or eliminate a portion of an ac signal. limiter can be

realiGed b! using diode and resistor as shown in #ig $.

Input to a limiter Dutput

The clamper circuit is one that will clamp a signal to a different dc level.

Input to a clamper Dutput

PIV2

Pea7 I(9e&.e V,"a0e3

;IV is the pea+ reverse voltage that appears across the diode when it is reverse-biased.

;IV * Vm

;age : of =

V

0

I

dV

dI

t

V

i

t

V

o

t

Vi

V

o

$.V

t

2V

-/V

D'4e Re-"'!'e&.

Diodes can be used to RECTI#C D,; from ac suppl! to produce a dc suppl!

on 0ve half c!cle of I,; wave

diode is fwd. biased

diode conducts

on -ve half' diode rev. biased

diode is rev. biased

diode does not conduct

<F#-"VE RECTI#IER

o

V R

L

V

i

V

o

V

i

t

t

C

HW Rectified O/P

HW Rectifier

I

(without C)

verage voltage %as seen on dc voltmeter&

Va9e 5 V%6

rms voltage %as seen on ac voltmeter&

V&m. 5 V%62

Smoothing

V

o

t

HW Rectified O/P

Ripple voltage

Charging

i!charging

Pea" Voltage

dc Voltage

V

p

V

dc

#$oothed

V

r

Output Voltage

If a capacitor is placed across output

capacitor charges on rising edge of 0ve half-c!cle

discharges on falling edge

D,; is smoothed

ctual pea+ D,; will be reduced from pea+ I,; b! value of forward. bias

Vp%out& * Vp%in& - ..H V

Ripple voltage

finite load current I causes capacitor voltage to drop b! V

r

during ac c!cle

ripple in D,; is approx. sawtooth in shape neglect charging time

assume discharge ta+es one complete period %T&

Charge flowing from capacitor in time T

I * IT

;age 2 of =

#all in capacitor voltage * p+-p+ ripple

Vr * I,C * IT,C

But T * $,f %f is ac fre-uenc!&

V&2H:3 5 I6C! H: R'%%,e V,"a0e

s the ripple voltage increases the average %dc& D,; voltage decreases

Vdc * Vp -$,(%Vr&

V4- 5 V% ; 0.<C! H: 4- V,"a0e

Ripple factor defines magnitude of smoothing effect

& 5 2V&6V4-3 100= R'%%,e !a-"&

Full Wave Rectifier

Better rectification is obtained if circuit conducts on both I,; half-c!cles

Dn first half-c!cle

"hen terminal is 0ve' D$ conducts to ma+e top end of load 0ve

t same time terminal B is -ve' D: conducts to lower end of load

Dn next half c!cle

Terminal is -ve and B is 0ve' D( conducts to top end of load' D2 conducts to lower end

Va9e 5 2V%6 %without smoothing capacitor&

#or #" rectification' ripple fre-uenc! is twice ac I,; fre-uenc!

V&2F:3 5 0.< C! R'%%,e 9,"a0e

V4- 5 V% ; 0.2< C! 4- V,"a0e %as seen on dc voltmeter&

%

&

'

(

R

L

)

*

ac

Input !ignal

Output !ignal

t

t

C

N. B. Ripple Voltage*)IRT%%R6)%V%R$7(&&JR6)%V%R$7(&&-V8%V%R$7(&&JV8%V%R$7(&&&&

;age 9 of =

0 V

V

dc

V

p

V

r

PROCEDURE

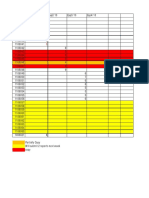

I*V C#a&a-"e&'."'-. ! D'4e 1N>001

F'0.1. DC a(a,+.'. ! D1N>001

D&a1 "#e -'&-/'" .#1( '( F'0. 1 '( PS%'-e .-#ema"'-.. U.e a(+ ! "#e 1N>001?1N>00@ a.

4'4e m4/,e.

He&eA !& 4e"e&m'('(0 "#e I*V -#a&a-"e&'."'-. a DC S1ee% ! V1 !&m ;<V " B10 9,". 1',,

Ce (ee4e4. Se" "#e '(-&eme(" ! V1 " 0.1 9,". '( ,'(ea& .1ee% m4e.

R/( "#e .'m/,a"'(.

OC"a'( I*V -#a&a-"e&'."'- ! "#e 4'4e '( "#e %&Ce.

B+ -#a(0'(0 "#e DC .1ee% 4e"e&m'(e "#e !,,1'(0:

a& Reverse saturation current.

b& Diode brea+down voltage.

OC"a'( P'e-e1'.e ,'(ea& m4e, !& "#e 4'4e 1#e( V1510V 2Hme :&73.

To obtain this choose B'a. P'(" De"a', from Se"/% A(a,+.'..

Run the simulation and clic+ on the Enable Bias Current Displa!.

1ote the diode current %ID&.

Determine RD.

#or finding VTD from the I-V curve' clic+ on the T00,e C/&.& button. )elect one

point near ID' right-clic+ on the same point. Clic+ another point near the first one.

Dbtain voltage and current magnitudes at two selected points %V$' I$' V(' I(& from the

P&Ce C/&.& menu. Then use the following formula7

VTD * V$-I$J %V$-V(& , %I$-I(&

Re%,a-e "#e 4'4e '( F'0. 1 1'"# a De(e& 4'4e 2D1N@<03 a(4 &e%ea" ."e%. 1 " <2C3 2Hme

:&73.

;age / of =

C,'%%e& C'&-/'"

F'0.2. C,'%%e& C'&-/'"

2.1. D&a1 "#e -'&-/'" .#1( '( F'0. 2 '( PS%'-e .-#ema"'-. /.'(0 1N>001 2& a(+

"#e&3 a. 4'4e m4/,e.

2.2. He&eA !& 4e"e&m'('(0 "#e '(%/" 9.. /"%/" -#a&a-"e&'."'-. V1 '. .e" " 1EHF a(4

10V 2%ea73. C((e-" 9,"a0e ma&7e&. a. '(4'-a"e4 '( F'0. 2. Se" "&a(.'e(" a(a,+.'. /%"

<m..

2.G. R/( "#e .'m/,a"'(.

2.>. OC.e&9e "#e '(%/" 2V13 a(4 /"%/" 2a" D1H. A(4e "e&m'(a,3 9,"a0e. '( "#e

%&Ce.

2.<. C#a(0e V2 !&m ;1V " >V '( 1V ."e%. OC.e&9e a(4 ("'!+ 1#a" #a%%e(..

2.I. E$%,a'( "#e 9a,/e ! /"%/" 9,"a0e '! V2 '. .e" " ;<V.

C,am%e& C'&-/'"

F'0.G. C,am%e& C'&-/'"

:.$. Draw the circuit shown in #ig. : in ;)pice schematics using $12..$ %or an! other&

as diode module.

:.(. <ere' for determining the input vs. output characteristics V$ is set to $3<G and $.V

%pea+&. )et R$ * $6' C$ * $# and V( * 9V. Connect voltage mar+ers as indicated in #ig.

:. )et transient anal!sis upto 9ms.

:.:. Run the simulation.

:.2. Dbserve the input %V$& and output %across R$& voltages in the probe.

:.9. Change V( from K2V to 2V in (V step. Dbserve and notif! what happens.

:./. )et R$ * (9.' C$ * $# and V( * .V. Dbserve the output voltage waveform and

explain it.

;age H of =

:.H. Lsing s-uare wave' repeat steps ( to / and notif! if there is an! difference source is

changed from sinusoidal to s-uare.

:.A. Change the polarit! of Diode and using sinusoidal source' repeat steps ( to /.

D'4e B&'40e Re-"'!'e& a(4 Re0/,a"e4 P1e& S/%%,+

F'0.>. D'4e C&'40e &e-"'!'e&

Draw the bridge rectifier circuit as in #ig. 2. Lse $12..$ as diode module. TM$ is a transformer

having part name NM#R6OFI1ERP. Double-clic+ it and set F$ and F( to $..m<.

)et V$ to $.V' 9. <G. Run )imulation.

Dbserve the waveform across R(.

1otif! the average voltage across R( %Vdc& and ripple voltage across the same. lso find the

R6) value of the ripple voltage %Vac&. Compare with theoretical values. Q#or finding the average

and R6) values of an! signal use V8 and R6) functions. Clic+ Ndd traceP icon. Then select

Nnalog operators and functionsP from the N#unction and 6acrosP pop-up menu. )elect

appropriate functions as necessar!.R

Connect a capacitor across R( and use values of ((#' 2H# and $..#. Repeat step : and 2 in

each case. Comment on the results.

F'0.<. Re0/,a"e4 DC P1e& S/%%,+

The final stage is to remove the ripples and get a better DC voltage using a ?ener regulator.

Draw the circuit of #ig. 9' using RF * 9.. and C( * $..#. Configure the ?ener diode model

%)elect the Gener diode' then go to Edit 6odel& with V? * 9V %Bv in the Edit Instant model&.

Chose value of R: properl! %around (..&. "ith the load RF disconnected' design the circuit for

a ripple level of ..$V and a maximum diode current of $.m.

#or the circuit of #ig. 9 with a load RF*9..' estimate the change in output voltage due to the

load. "hat is the maximum load %minimum load resistance& that can be tolerated b! the designed

suppl! circuitS

;age A of =

P&e%a&e4 C+ : Yea.'& A&a!a"A A#ma4 E#"e.#am/, I.,amA S#a'7# A.'! Ma#m4

;age = of =

Vous aimerez peut-être aussi

- Lecture: Static ILP: Topics: Predication, Speculation (Sections C.5, 3.2)Document26 pagesLecture: Static ILP: Topics: Predication, Speculation (Sections C.5, 3.2)Purab RanjanPas encore d'évaluation

- Update Oct 29Document12 pagesUpdate Oct 29Purab RanjanPas encore d'évaluation

- Mil J Kovic 2010Document8 pagesMil J Kovic 2010Purab RanjanPas encore d'évaluation

- Once Again, It's BlankDocument1 pageOnce Again, It's BlankPurab RanjanPas encore d'évaluation

- Road to Freedom from BUETDocument2 pagesRoad to Freedom from BUETMohammad Khairul Halim Rimon50% (2)

- This Is Absolute GarbageDocument1 pageThis Is Absolute GarbagePurab RanjanPas encore d'évaluation

- To The Moon - Piano (Ending Version) r359Document7 pagesTo The Moon - Piano (Ending Version) r359xjp9210Pas encore d'évaluation

- Abstract Near Field ObfDocument2 pagesAbstract Near Field ObfPurab RanjanPas encore d'évaluation

- Ref 7 PDFDocument5 pagesRef 7 PDFPurab RanjanPas encore d'évaluation

- I Have Nothing To OfferDocument1 pageI Have Nothing To OfferPurab RanjanPas encore d'évaluation

- TAX Guideline July 2015Document3 pagesTAX Guideline July 2015Purab RanjanPas encore d'évaluation

- IED Modelling For Triple Frequency Capacitive Sheath: EEE 400: Project/ThesisDocument34 pagesIED Modelling For Triple Frequency Capacitive Sheath: EEE 400: Project/ThesisPurab RanjanPas encore d'évaluation

- This Is A Garbage Doc. SorryDocument1 pageThis Is A Garbage Doc. SorryPurab RanjanPas encore d'évaluation

- Ashraful Islam Résumé for PhD in EEDocument2 pagesAshraful Islam Résumé for PhD in EEPurab RanjanPas encore d'évaluation

- Blank BeautyDocument1 pageBlank BeautyPurab RanjanPas encore d'évaluation

- Evolution of Management TheoriesDocument5 pagesEvolution of Management Theoriesoptimistic07100% (1)

- ApplicationDocument4 pagesApplicationPurab RanjanPas encore d'évaluation

- Operations Management: - ForecastingDocument96 pagesOperations Management: - ForecastingPurab RanjanPas encore d'évaluation

- Questionvlsi 4yearDocument15 pagesQuestionvlsi 4yearPurab RanjanPas encore d'évaluation

- Undergraduate Resume Writing Guide PDFDocument9 pagesUndergraduate Resume Writing Guide PDFPurab RanjanPas encore d'évaluation

- New Microsoft PowerPoint PresentationDocument25 pagesNew Microsoft PowerPoint PresentationPurab RanjanPas encore d'évaluation

- 07 CmosDocument10 pages07 CmosPurab RanjanPas encore d'évaluation

- Waltz in B Minor Op.69 No 2Document4 pagesWaltz in B Minor Op.69 No 2tincho9Pas encore d'évaluation

- JoinedDocument1 pageJoinedPurab RanjanPas encore d'évaluation

- Input Port A: Hex To Bin EncoderDocument1 pageInput Port A: Hex To Bin EncoderPurab RanjanPas encore d'évaluation

- Routine 23Document1 pageRoutine 23Purab RanjanPas encore d'évaluation

- Cover LetterDocument1 pageCover LetterPurab RanjanPas encore d'évaluation

- 2.1 Definition of PlasmaDocument31 pages2.1 Definition of PlasmaPurab RanjanPas encore d'évaluation

- Diagram 2hhmmDocument1 pageDiagram 2hhmmPurab RanjanPas encore d'évaluation

- Eee402 A2Document1 pageEee402 A2Purab RanjanPas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5782)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Sharqiyah Region Site IssuesDocument6 pagesSharqiyah Region Site IssueskabeelarunnPas encore d'évaluation

- Uv Physics Academy: Part-ADocument16 pagesUv Physics Academy: Part-ASubhankar HowladerPas encore d'évaluation

- Tank DesignDocument2 pagesTank DesignkamleshyadavmoneyPas encore d'évaluation

- Em HW4Document2 pagesEm HW4林廉恩Pas encore d'évaluation

- Aircraft Electrical SystemsDocument14 pagesAircraft Electrical SystemsBarnister OngaroPas encore d'évaluation

- Unit Homework Momentum Its Conservation Ans KeyDocument6 pagesUnit Homework Momentum Its Conservation Ans KeyKristyne Olicia100% (1)

- EMF (Electromagnetic) Pollution and RemediationDocument53 pagesEMF (Electromagnetic) Pollution and RemediationEcopolitan - your Eco-Health Network100% (3)

- Development of A Numerical Model of The CECO Wave Energy Con - 2021 - Ocean EngiDocument9 pagesDevelopment of A Numerical Model of The CECO Wave Energy Con - 2021 - Ocean EngiIchlebe FurdichPas encore d'évaluation

- Governor: Er. Subodh Kumar GhimireDocument13 pagesGovernor: Er. Subodh Kumar GhimireRohit NewarPas encore d'évaluation

- Alternator E1C10M L: Technical Data SheetDocument6 pagesAlternator E1C10M L: Technical Data SheetBaraPas encore d'évaluation

- Chapter 2 - Hydrodynamics of Pumps - Christopher E. BrennenDocument14 pagesChapter 2 - Hydrodynamics of Pumps - Christopher E. Brennenmete2009Pas encore d'évaluation

- Tutorial Question Chap 1-2018Document4 pagesTutorial Question Chap 1-2018ElijahPas encore d'évaluation

- Mxz-2a20na & Mxz-3a30na Ob444aDocument77 pagesMxz-2a20na & Mxz-3a30na Ob444aSLAMET PAMBUDIPas encore d'évaluation

- Variable Frequency Drive Manual: Safety GuideDocument183 pagesVariable Frequency Drive Manual: Safety GuideVOL EngineerPas encore d'évaluation

- Thermo ExperimentDocument6 pagesThermo ExperimentZain Ul Abedin100% (2)

- Factors Affecting Internal Resistance of a CellDocument17 pagesFactors Affecting Internal Resistance of a CellModi JiPas encore d'évaluation

- Earthing PracticesDocument16 pagesEarthing PracticesSubu ManiPas encore d'évaluation

- PD ManualDocument17 pagesPD ManualMURTHYPas encore d'évaluation

- Study of Cross Flow Heat ExchangerDocument11 pagesStudy of Cross Flow Heat Exchangerandrew munyiva100% (1)

- Review of Sdof ConceptsDocument7 pagesReview of Sdof ConceptskalpanaadhiPas encore d'évaluation

- PA-4000 Series (Single-Phase) : Power ControllerDocument4 pagesPA-4000 Series (Single-Phase) : Power ControllerhamzaPas encore d'évaluation

- High-efficiency 310W Mono Crystalline Solar ModuleDocument1 pageHigh-efficiency 310W Mono Crystalline Solar ModulelatifahPas encore d'évaluation

- 1 s2.0 S187661021735453X Main PDFDocument6 pages1 s2.0 S187661021735453X Main PDFDexter Asprin DulayPas encore d'évaluation

- VELASCO - Prelim Activity 1Document2 pagesVELASCO - Prelim Activity 1KRISHEEN VELASCOPas encore d'évaluation

- AECOMDocument8 pagesAECOMmarcelo3e3Pas encore d'évaluation

- 3RD TERM SS1 PHYSICS Scheme of WorkDocument15 pages3RD TERM SS1 PHYSICS Scheme of WorkloveandreverbPas encore d'évaluation

- Lecture 1 Introduction To Power Distribution SystemsDocument53 pagesLecture 1 Introduction To Power Distribution SystemsMohammed ShifulPas encore d'évaluation

- Atmospheric Stability and Cloud DevelopmentDocument23 pagesAtmospheric Stability and Cloud DevelopmentEvan Sugiarto AfilPas encore d'évaluation

- SCD-XB940 Service Manual - Comprehensive Guide to Repairing Sony Super Audio CD PlayerDocument73 pagesSCD-XB940 Service Manual - Comprehensive Guide to Repairing Sony Super Audio CD PlayerPietertje58Pas encore d'évaluation

- Tube Banks Single-Phase Heat Transfer inDocument22 pagesTube Banks Single-Phase Heat Transfer inarif aktaşPas encore d'évaluation